Изобретение относится к электротехнике и может быть использовано в системах электропитания устройств .автоматики, вычислительной и изиери тельной техншси и средств связи.

Целью изобретения является эффективное использование по энергопотреблению выходных каналов за счет отклго- чения нагрузок, находящихся в нерабочих режимах.,

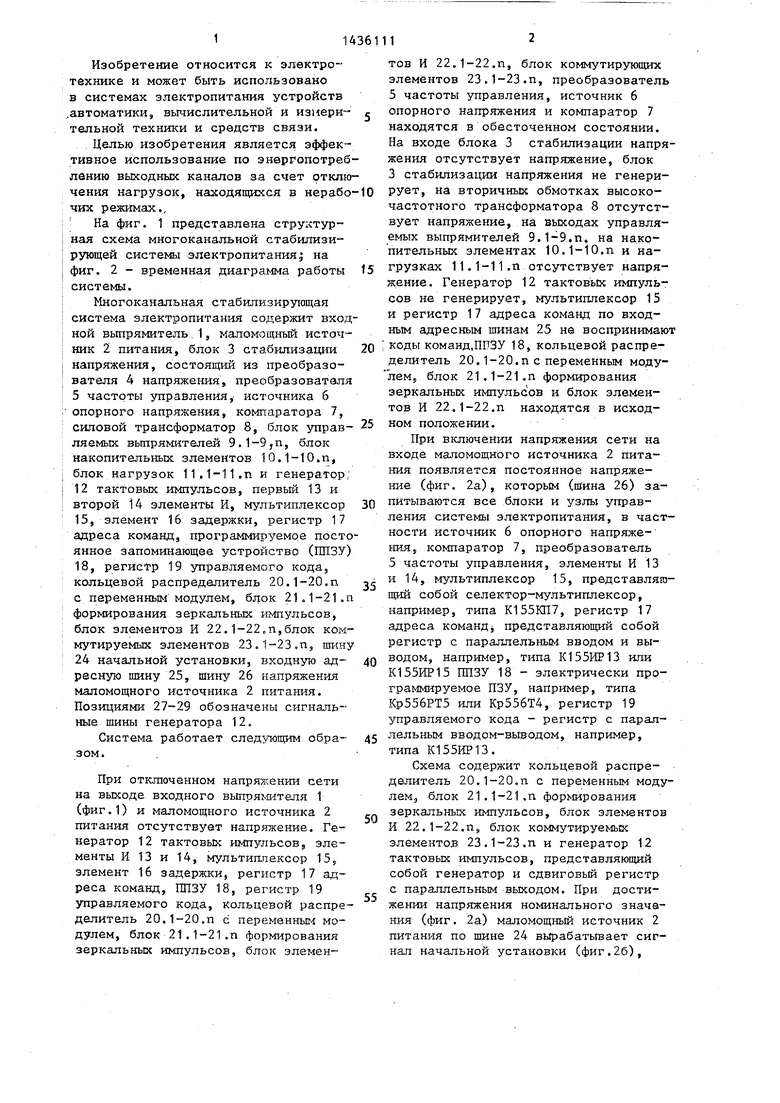

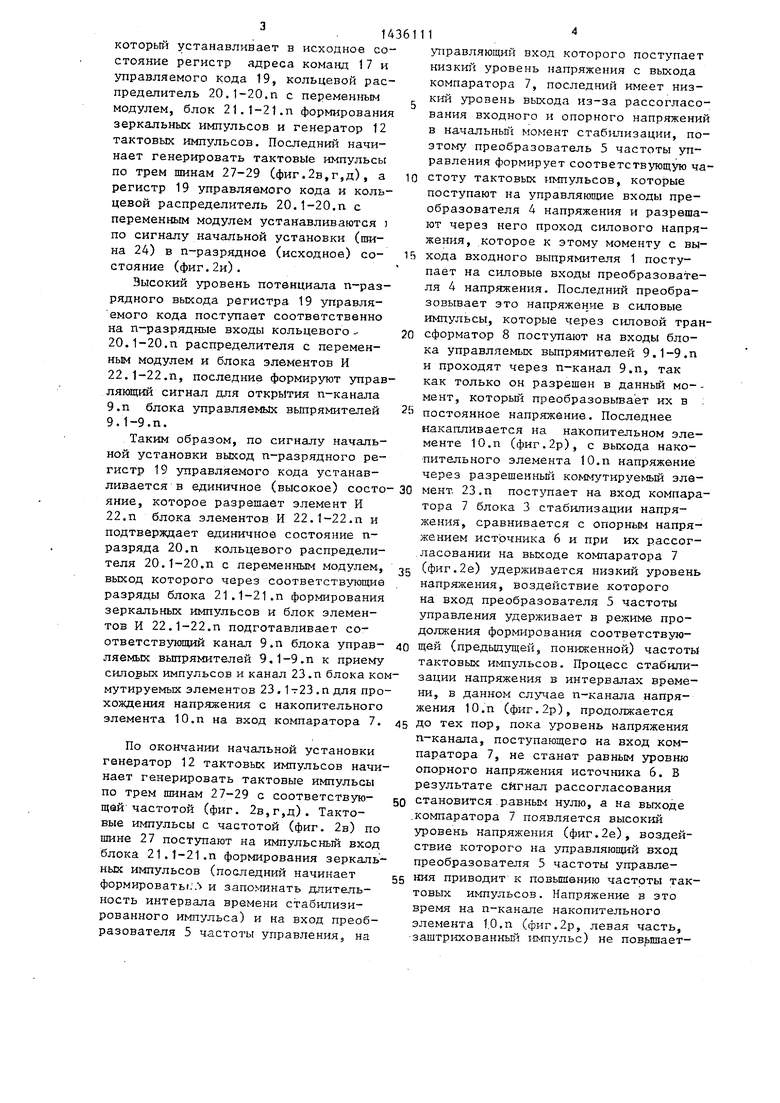

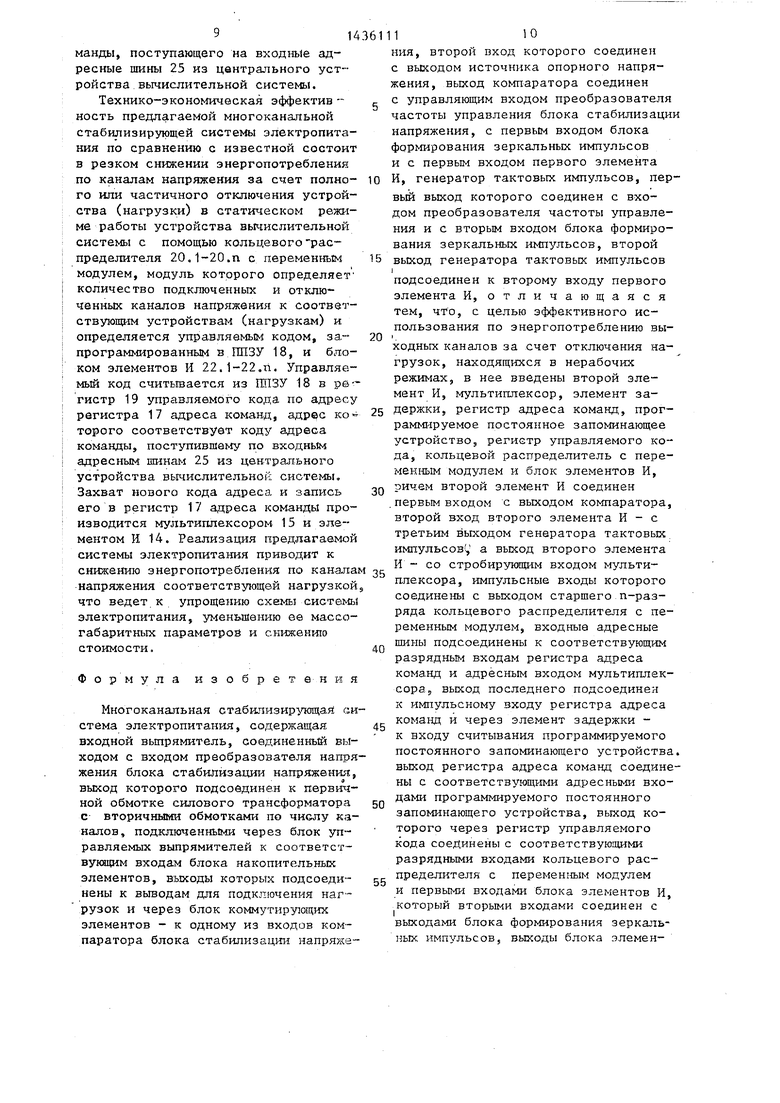

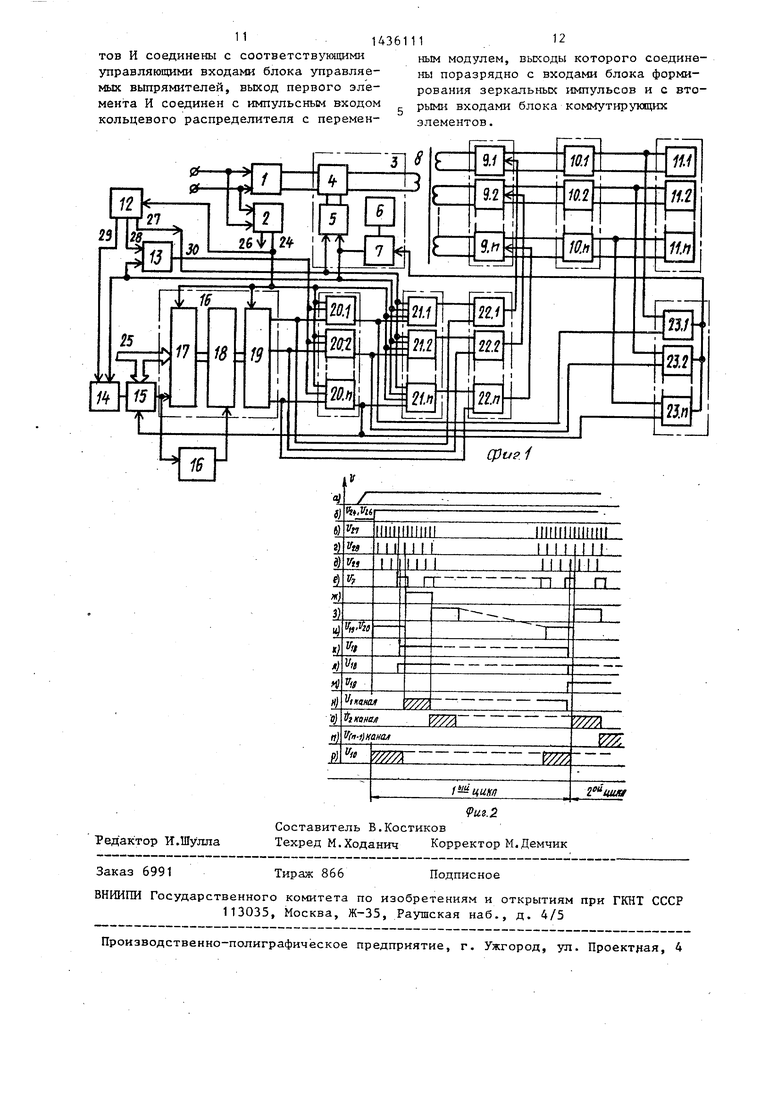

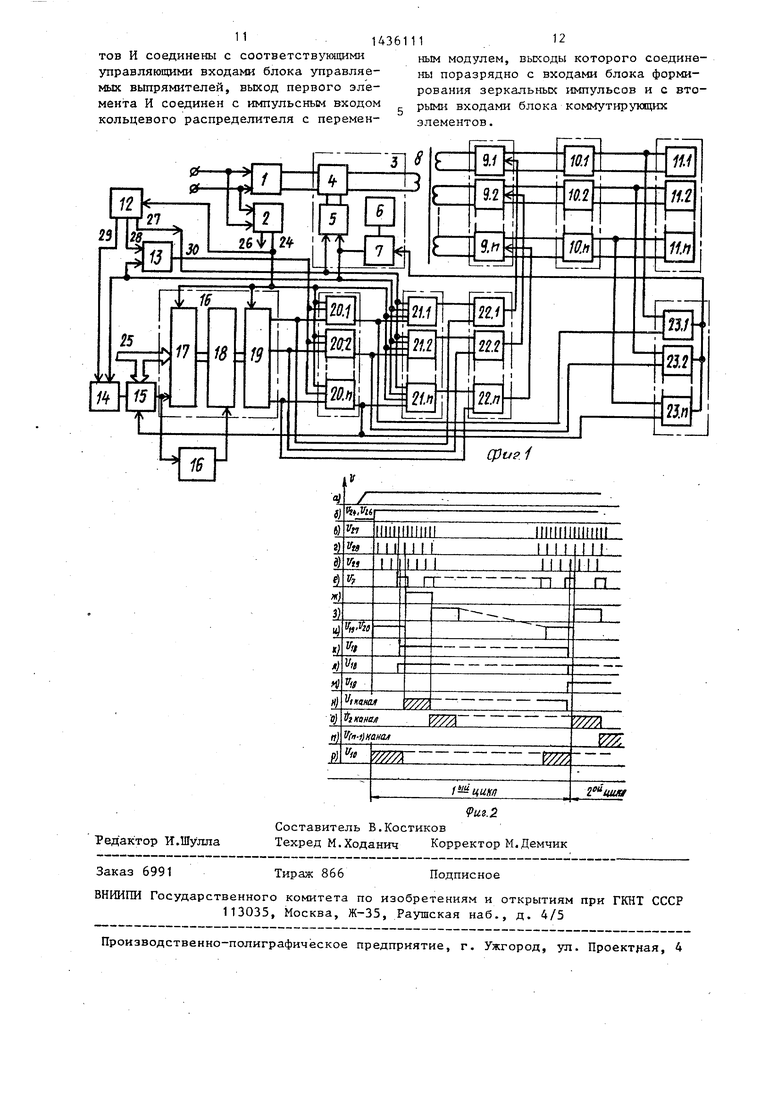

На фиг. 1 представлена структурная схема многоканальной стабилизирующей системы электропитанияJ на фиг. 2 - временная диаграмма работы системы.

Многоканальная cтaбилизиpyюп aя система электропитания содержит входной вьтрямитель.1, маломощнъй источник 2 питания, блок 3 стабилизации напряжения, состоящий из преобразователя 4 напряжения, преобразователя 5 частоты управления,- источника б опорного напряжения, компаратора 7, силовой трансформатор 8, блок управ- ляемых вьтрямителей 9.1-9,п, блок накопительных элементов 10.1-IO.n, блок нагрузок 11.1-11.п и генератор; 12 тактовых импульсов, первьй 13 и второй 14 элементы И, мультиплексор 15, элемент 16 задержки, регистр 17 адреса команд, программируемое постоянное запоминающее устройство (ШЗУ) 18, регистр 19 управляемого кода, кольцевой распределитель 20.1-20.П с переменным модулем, блок 21,1-21 ,ri формирования зеркальных импульсов, блок элементов И 22.1-22„п,блок KOixt- мутируемых элементов 23.1-23.п, шину 24 начальной установки, входную ад- ресную шину 25, шину 26 напряжения маломощного источника 2 питаьшя. Позициями 27-29 обозначены сигнальные шины генератора 12,

Система работает следующим обра- зом.

При отключенном напряжении сети на выходе входного вьптоя штеля 1 (фиг.1) и маломощного источника 2 питания отсутствует напряжение. Генератор 12 тактовь х импульсов, элементы И 13 и 14, мультиплексор 15, элемент 16 задержки, регистр 17 адреса команд, ППЗУ 18, регистр 19 управляемого кода, кольцевой распределитель 20.1-20.п с переменным модулем, блок 21.1-21.п формирования зеркальных импульсов, блок элемен

0

5

0

5

тов и 22.1-22.п, блок коммутирующих элементов 23.1-23.п, преобразователь 5 частоты управления, источник 6 опорного напряжения и компаратор 7 находятся в обесточенном состоянии. На входе блока 3 стабилизации напряжения отсутствует напряжение, блок 3 стабилизации напряжения не генерирует, на вторичных обмотках высокочастотного трансформатора 8 отсутствует напряжение, на выходах управля- выпрямителей 9.1-9,п. на накопительных элементах 10.1-IO.n и нагрузках 11.1-11.п отсутствует напряжение. Генератор 12 тактовых импульсов не генерирует, мультиплексор 15 и регистр 17 адреса команд по входным адресньвд шинам 25 на воспринимают

I коды команд.ППЗУ 18, кольцевой распределитель 20.1-20.П с переменным моду лем, блок 21.1-21.п формирования зеркальных импульс ов и блок элементов И 22.1-22.п находятся в исходном положении.

При включении напряжения сети на входе маломощного источника 2 питания появляется постоянное напряжение (фиг. 2а), которым (шина 26) за- питываются все блоки и узлы управления системы электропитания, в частности источник 6 опорного напряжения, компаратор 7, преобразователь 5 частоты управления, элементы И 13 и 14, мультиплексор 15, представляющий собой селектор-мультиплексор, например, типа К155КП7, регистр 17 адреса командj представляющий собой регистр с параллельным вводом и выводом, например, типа К155ИР13 или К155ИР15 ППЗУ 18 - электрически программируемое ПЗУ, например, типа Кр55бРТ5 или Кр55бТ4, регистр 19 управляемого кода - регистр с параллельным вводом-выводом, например, типа К155ИР13.

Схема содержит кольцевой распределитель 20.1-20.п с переменным моду- леМэ блок 21.1-21.п формирования зеркальных импульсов, блок элементов И 22.1-22.п, блок коммутируемьвс элементов 23.1-23.п и генератор 12 тактовых импульсов, представляющий собой генератор и сдвиговый регистр с параллельным выходом. При достижении напряжения номинального значения (фиг. 2а) маломощный источник 2 питания по шине 24 вырабатывает сигнал начальной установки (фиг.26),

/ . 14 который устанавливает в исходное состояние регистр адреса команд 17 и управляемого кода 19, кольцевой распределитель 20.1-20.п с переменным модулем, блок 21.1-21.п формирования зеркальных импульсов и генератор 12 тактовых импульсов. Последний начинает генерировать тактовые импульсы по трем шинам 27-29 (фиг.2в,г,д), а регистр 19 управляемого кода и кольцевой распределитель 20.1-20.п с переменным модулем устанавливаются i по сигналу начальной установки (шина 24) в п-разрядное (исходное) со- стояние (фиг.2и).

Высокий зфовень потенциала п-раз- рядного выхода регистра 19 управляемого кода поступает соответственно на п-разрядные входы кольцевого - 20.1-20.п распределителя с переменным модулем и блока элементов И 22.1-22.п, последние формируют управляющий сигнал для открытия п-канала 9.П блока управляемых выпрямителей 9.1-9.п.

Таким образом, по сигналу начальной установки выход п-разрядного регистр 19 управляемого кода устанавливается в единичное (высокое) состо яние, которое разрешает элемент И 22.п блока элементов И 22.1-22.п и подтверждает единичное состояние п- разряда 20.п кольцевого распределителя 20.1-20.п с переменным модулем, выход которого через соответствующие разряды блока 21.1-21.п формирования зеркальных импульсов и блок элементов И 22.1-22.п подготавливает соответствующий канал 9.П блока управ- ляемых выпрямителей 9,1-9.п к приему силовых импульсов и канал 23,п блока комутируемых элементов 23,1 -23 . п для прохождения напряжения с накопительного элемента lO.n на вход компаратора 7.

По окончании начальной установки генератор 12 тактовых импульсов начинает генерировать тактовые импульсы по трем шинам 27-29 с соответствую- щей частотой (фиг. 2в,г,д). Тактовые импульсы с частотой (фиг. 2в) по шине 27 поступают на импульсный вход блока 21.1-21.п формирования зеркальных импульсов (последний начинает формироваты. Л и запоминать длительность интервала времени стабилизированного импульса) и на вход преобразователя 5 частоты управления, на

1

управляющий вход которого поступает низкий уровень напряжения с выхода компаратора 7, последний имеет низкий уровень выхода из-за рассогласования входного и опорного напряжений в начальньп момент стабилизации, поэтому преобразователь 5 частоты управления формирует соответствующую частоту тактовых импульсов, которые поступают на управляюпще входы преобразователя 4 напряжения и разрешают через него проход силового напряжения, которое к этому моменту с выхода входного выпрямителя 1 поступает на силовые входы преобразователя 4 напряжения. Последний преобразовывает это напряжение в силовые импульсы, которые через силовой трансформатор 8 поступают на входы блока управляемых выпрямителей 9.1-9.П и проходят через п-канал 9.п, так как только он разрешен в данный мо- мент, которьй преобразовывает их в постоянное напряжение. Последнее накапливается на накопительном элементе 10.п (фиг.2р), с выхода накопительного элемента 10.п напряжение через разрешенньй коммутируемый элемент. 23.п поступает на вход компаратора 7 блока 3 стабилизации напряжения, сравнивается с опорнь1М напряжением источника 6 и при их рассогласовании на выходе компаратора 7 (фиг.2е) удерживается низкий уровень напряжения, воздействие которого на вход преобразователя 5 частоты управления удерживает в режиме продолжения формирования соответствующей (предьщущей, пониженной) частоты тактовых импульсов. Процесс стабилизации напряжения в интервалах времени, в данном случае п-канала напряжения 10.П (фиг.2р), продолжается до тех пор, пока уровень напряжения п-канала, поступающего на вход компаратора 7, не станет равным уровню опорного напряжения источника 6. В результате сигнал рассогласования становится равным нулю, а на выходе компаратора 7 появляется высокий уровень напряжения (фиг.2е), воздействие которого на управляющий вход преобразователя 5 частоты управления приводит к повышению частоты тактовых импульсов. Напряжение в это время на п-канале накопительного элемента 1,0.п (фиг.2р, левая часть, заштрихованкьй импульс) не повьш1ает514361

ся, а стабилизируется на уровне опорного. Стабилизированное напряжение данного канала Ю.п питает нагрузку 11.П, которой может быть центральная часть (центральньй процессор, программное постоянное запоминающее устройство и другие устройства, необходимые для организации выбора нужной подпрограммы) вычислительной Q системы, которая обеспечивает выбор команд ньшолняемьйс подпрограмм. Пока центральное устройство вы- числительной системы находится в ис- ходном состоянии на входных адресных 15 шинах 25 системь электропитания присутствует нулевой код команды. Нулевой код команды не изменяет исходного состояния регистра 17 адреса команд, из ШЗУ 18 считьтается нулевой код,, 20 которьй не изменяет исходного состояния регистра 19 управляемого кода. На выходах регистра 19 управляемого кода, кроме п-разряда, присутствует низкий уровень (логический О), во- 25 здействие которого на соответствующие входы кольцевого распределителя с переменным модулем запрещает в нем последователькьй перенос логической 1 в соответствующие разряды D-триг- ЗО геров. На разрядных выходах кольде- вого распределителя 20.1-20.п с па- ременным модулем присутствует низкий .уровень кроме п-разряда) , который .удерживает через соответствующие раз- .ряды блока элементов И.22.1-22.(п-1) в закрытом состоянии канал напряже- ния Э.п, который только один в данный момент открыт и напрялсение его стабилизируется.40

По окончании стабилизации интервала времени п-канала напряжения компаратор 7 вырабатывает высокий уровень напряжения, который поступает на второй вход блока 21.1-21.п формиро- 45 вания зеркальных импульсов и на первые входы элементов И 13 и 14 и разрешает проход соответствующей частоты тактовых импульсов (шины 28 и 29) сдвига и записи кода команд (фиг.2д, Q г), поступающих соответственно на вторые входы элементов И 13 и 14 от генератора 12 тактовых импульсов, Тактовые импульсы записи кода команд с выхода второго элемента И 14 по- gg ступают на стробирующий вход мультиплексора 15, на соответствующие импульсные входы которого поступает сигнал высокого уровня с п-разряд1ю116

го выхода кольцевого распределителя 20,1-20.п с переменным модулем, а на его адресные входы - код команды с выходных адресных шин 25 и при их совпадении в момент стробирования ; тактовым импульсом записи на выходе мультиплексора 15 появляется сигнал записи, поступающий на импульсный вход регистра 17 адреса команд, который производит запись кода команды присутствующий на входньсх адресных щинах 25, в регистр 17 адреса команд

Таким образом, по установленному адресу на регистре 17 адреса команд и в момент воздействия сигнала считывания, через элемент 16 задержки на считывающий вход ГШЗУ 18 с последнего производится считывание кода коммутации каналов напряжения в регистр 19 управляемого кода, код которого сохраняется до следующего изменения кода команды на входных адресных шинах 25.

Например, по заданному адресному коду (ГГ6).из 1ШЗУ 18 выбирается управляемый код 110, записывается и хранится в регистре 19 управляемого кода (фиг.2к,л,м), в результате которого открыты первый и второй каналы напряжения (фиг.2н,о) и закры пр едпо след ний (п-1)-ка нал (фиг.2 п). Разрешение открытия каналов напряжения и последовательность их стабилизации производятся соответственно при помощи блока элементов И 22.122о(п-1) и кольцевого распределителя 20.1-20.п с переменным модулем, которые учитывают.состояния управляемого кода регистра 19 управляемого кода. При управляемом коде 110 на вторых входах первого и второго элементов И 22.1 и 22.2 блока элементов И 22.1 22,п присутствует разрешающий (высокий) потенциал, на входах первого и второго разрядов кольцевого распределителя 20.1-20.П также присутствует разрешающий (высокий) потенциал, который разрешает последовательный перекос логической 1 в кольцевом распределителе из п- разряда в первый разряд D-триггера, выход последнего через соответствующий канал 21.1 блока 21.1-21.п фор- ми1 ования зеркальньгх импульсов и раз решенньй элемент И 22.1 блока элементов 22.1-22.п производит открыва- ние первого канала напряжения 9.1 блока управляемых вьшрямителей 9.1714

9.п. Напряжение, прошедшее через открытый управляемый выпрямитель первого канала напряжения 9.1, накапливается на накопительном элементе

10.1,которое через подготовленный коммутируемый элемент 23.1 поступает на вход компаратора 7, где происходи его сравнение с опорным напряжением начинается процесс стабилизации дан- ного канала напряжения. По окончании стабилизации первого канала напряжения компаратор 7 своим высоким уровнем разрешает первый элемент И 13, через который проходит тактовый им-

.пульс сдвига (шина 30), воздействие которого на С-входы D-триггеров кольцевого распределителя 20.1-20.п с переменным модулем переносит единичное состояние предвдущего (с дан11ом случае первого) разряда D-триггера, единичный выход последнего через : второй канал 21.2 блока 21,1-21. п. формирования зеркальнь1х импульсов - во второй разряд D-триггера и второй элемент 22.2 блока, элемент 22.1- . 22,п разрешает второй канал напряжения 9.2 блока 5Т1равляемых выпрями-, телей 9.1-9.п. Напряжение, накапливаемое на накопительном элементе

10.2,поступает через открытый (соответствующим разрядом кольцевого распределителя) второй коьмутирув мый элемент 23.2 блока коммутируемых элементов 23.1-23.п на вход компарато- ра 7, который сравнивает его с опорным напряжением. Начинается процесс стабилизации второго канала напряжения . Хотя первый канал 9.1 напряжения в этот момент тоже открыт, но стабилизация напряжения .его поддерживается за счет отстабилизирован- ного зеркального импульса, хранящегося в канале 21.1 блока 21.1-21.п формирования зеркальных импульсов. Процесс стабилизации каналов напряжения повторяется.

По окончании процесса стабилизации компаратор 7 (как и в предьщу- щем случае) разрешает первьй элемент И 13 для прохождения следующего тактового импульса сдвига, который, воздействуя на С-входы D-триггеров кольцевого распределителя 20.1-20.П с переменным -модулем, переносит еди- ничное состояние второго разряда D-триггера, но ни в третий разряд и ни в последующий (так как их разрядные входы и цепи переноса закрыты

11 . 8 согласно выбранного управляемого кода), а в п-разряд D-триггера кольцевого распределителя 20.1-20.п с переменным модулем. Таким образом, закончился цикл выбора каналов напряжения и подключения к ним соответствующих нагрузок с помощью блок элементов И 22.1-22.п и кольцевого распределителя 20.1-20.п., в которых постоянно разрешены п-й, первый и второй разряды элементов И 22.п, 22.2 блока элементов И 22П-22.п и периодически возбуждаются разряды п-го, первого и второго D-триггеров кольцевого распределителя 20.1-20.п для последовательной стабилизации каналов напряжения. В данном цикле п-й, первый и второй каналы напряжения подключены к соответствующим нагрузкам, остальные нагрузки обесточены. Цикличность повторяется до тех пор, пока на входе адресных щин 25 не. изменится код команды, который фиксируется мультиплексором 15 при воздействии высокого потенциала п-разряда D-триггера кольцевого распределителя 20.1-20.П и тактового импульса записи и вьфаботан- ный -сигнал записи мультиплексором 15 записывает новый код команды в регистр 17 адреса команд. В результте смены кода адреса из ППЗУ 18 счи тьшается новый управляемый код, например 011 (фиг.2к,л,м, правая часть эпюр), в регистр 18 управляемого кода, который изменяет модуль кольцевого распределителя 20.1-20.п и разрешает соответствующие разряды блока элементов И 22.1-22.п. В новом цикле производится подключение нагрузок соответственно к п-му, второму и третьему каналам напряжения Сфиг.2р,о,п, правая часть эпюр). В этом (во втором) цикле первый канал напряжения отключен и нагрузка со- отсетственно обесточена (фиг.2н, первая часть эпюры). Процесс последовательности подготовки (разрешения блока коммутируемых элементов 23.1- 23.п, подключения каналов напряжения к соответствумцим нагрузкам с помощью блока управляемых вьшрямите- лей 9.1-9.П и стабилизация напряжения каналов происходит так же, как и в первом цикле работы. Процесс в циклах повторяется. Смена циклов работы подключения каналов напряжения производится изменением крда команды, поступающего на входньш адресные шины 25 из центрального устройства вычислительной системы.

Технико-экономическая эффектив - ность предлагаемой многоканальной стабилизирующей системы электропитания по сравнению с известной состоит в резком снижении энергопотребления по каналам напряжения за счет полного или частичного отключения устройства (нагрузки) в статическом режиме работы устройства вычислительной системы с помощью кольцевого распределителя 20.1-20.п с переменньйч модулем, модуль которого определяет количество подключенных и отключенных каналов напряжения к соответствующим устройствам (нагрузкам) и определяется зшравлявмьям кодом, запрограммированным в ШЗУ 18, и блоком элементов И 22.1-22.п. Управляемый код считьшается из ППЗУ 18 в ре - гистр 19 управляемого кода по адресу регистра 17 адреса команд, адрес ко торого соответствует коду адреса команды, поступившему по входным адресным шинам 25 из центрального устройства вычислительной системы, Захват нового кода адреса и запись его в регистр 17 адреса команды производится мультиплексором 15 и элементом И 14. Реализация предлагаемой системы электропитания приводит к

10

15

ния, второй вход которого соединен с выходом источника опорного напряжения, выход компаратора соединен с управляющим входом преобразовател частоты управления блока стабилизац напряжения, с первым входом блока формирования зеркальных импульсов и с первым входом первого элемента И, генератор тактовых импульсов, пе вый выход которого соединен с входом преобразователя частоты управле ния и с вторым входом блока формиро вания зеркальных импульсов, второй

вьвсод генератора тактовых импульсов

I

подсоединен к второму входу первог

элемента И, отличающаяся тем, что, с целью эффективного использования по энергопотреблению вы ходных каналов за счет отключения на грузок, находящихся в нерабочих режимах, в нее введены второй элемент И, мультиплексор, элемент за- 25 держки, регистр адреса команд, про раммируемое постоянное запоминающе устройство, регистр управляемого к да, кольцевой распределитель с пер менным модулем и блок элементов И, ричем второй элемент И соединен первым входом с выходом компаратор второй вход второго элемента И - с третьим выходом генератора тактовы импульсов, а выход второго элемент

20

30

снижению энергопотребления по каналам 35 ° стробирующим входом мультиплексора, импульсные входы которог соединены с выходом старшего п-раз- ряда кольцевого распределителя с п ременным модулем, входные адресные шины подсоединены к соответствующим разрядным входам регистра адреса команд и адресным входом мультипле сора, выход последнего подсоединен к импульсному входу регистра адрес команд и через элемент задержки - к входу считывания программируемог постоянного запоминающего устройст выход регистра адреса команд соеди ны с соответствующими адресными вх дами программируемого постоянного запоминающего устройства, выход ко торого через регистр управляемого кода соединены с соответствующими разрядными входами кольцевого распределителя с переменным модулем и первыми входами блока элементов И который вторыми входами соединен с выходами блока формирования зеркаль ных импульсов, выходы блока элемен-напряжения соответствующей нагрузкой что ведет к упрощению схемы системь электропитания, уменьшению ее массо- габаритных параметров и снижению стоимости.

Формула изобретения

Многоканальная стабилизир тощая система электропитания, содержащая входной выпрямитель, соединеннъй выходом с входом преобразователя напряжения блока стабилизации напряжения, выход которого подсоединен к первичной обмотке силового трансформатора с вторичными обмотками по числу каналов, подключенными через блок управляемых выпрямителей к соответст- вуницим входам блока накопительных элементов, выходы которых подсоеди™ иены к выводам для подключения нагрузок и через блок коммутируклцих элементов - к одному из входов компаратора блока стабилизации напряже

5

ния, второй вход которого соединен с выходом источника опорного напряжения, выход компаратора соединен с управляющим входом преобразователя частоты управления блока стабилизации напряжения, с первым входом блока формирования зеркальных импульсов и с первым входом первого элемента И, генератор тактовых импульсов, первый выход которого соединен с входом преобразователя частоты управления и с вторым входом блока формирования зеркальных импульсов, второй

вьвсод генератора тактовых импульсов

I

подсоединен к второму входу первого

элемента И, отличающаяся тем, что, с целью эффективного использования по энергопотреблению выходных каналов за счет отключения нагрузок, находящихся в нерабочих режимах, в нее введены второй элемент И, мультиплексор, элемент за- 5 держки, регистр адреса команд, программируемое постоянное запоминающее устройство, регистр управляемого кода, кольцевой распределитель с переменным модулем и блок элементов И, ричем второй элемент И соединен первым входом с выходом компаратора, второй вход второго элемента И - с третьим выходом генератора тактовых, импульсов, а выход второго элемента

0

0

° стробирующим входом мульти

плексора, импульсные входы которого соединены с выходом старшего п-раз- ряда кольцевого распределителя с переменным модулем, входные адресные шины подсоединены к соответствующим разрядным входам регистра адреса команд и адресным входом мультиплексора, выход последнего подсоединен к импульсному входу регистра адреса команд и через элемент задержки - к входу считывания программируемого постоянного запоминающего устройства, выход регистра адреса команд соединены с соответствующими адресными входами программируемого постоянного запоминающего устройства, выход которого через регистр управляемого кода соединены с соответствующими разрядными входами кольцевого распределителя с переменным модулем и первыми входами блока элементов И, который вторыми входами соединен с выходами блока формирования зеркальных импульсов, выходы блока элемен111436111 . 12

тов И соединены с соответствующими ным модулем, выходы которого соедине- управляющими входами блока управляв- ны поразрядно с входами блока форми- мых вьтрямителей, выход первого эле- рования зеркальных импульсов и с втс- мента И соединен с импульсным входом рь1ми входами блока коммутирующих кольцевого распределителя с перемен- элементов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство контроля интегральных схем | 1987 |

|

SU1479899A1 |

| Устройство ввода-вывода | 2020 |

|

RU2753980C1 |

| МОДУЛЬ СИСТЕМЫ МИКРОПРОГРАММНОГО УПРАВЛЕНИЯ | 1999 |

|

RU2152071C1 |

| Устройство для контроля цифровых блоков | 1989 |

|

SU1762280A2 |

| Устройство для контроля параметров | 1986 |

|

SU1403074A1 |

| Устройство для формирования маршрута сообщения в однородной вычислительной системе | 1988 |

|

SU1508228A1 |

| Параллельный логический мультиконтроллер | 2016 |

|

RU2634199C1 |

| Устройство для накопления чисел с плавающей запятой | 1990 |

|

SU1829030A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1108449A1 |

| СИСТЕМА РАСПРЕДЕЛЕНИЯ РЕСУРСОВ | 2000 |

|

RU2189073C2 |

Изобретение относится к электротехнике и может быть использовано в системах электропитания устройств автоматики и вычислительной техники. Цель изобретения - эффективное использование по энергопотреблению выходных каналов за счет отключения нагрузок, находящихся в нерабочем режиме. Согласно кода адреса команды, Еьщаваемого центральным устройством вычислительной системы, автоматически производится подключение соответствующих нагрузок к каналам напряжения и отключения нагрузок, используемых в данный момент времени в статическом режиме работы (не участвующих в выполнении данной операции) . Это рейко сокращает энергопотребление от каналов напряжения вычислительной системой, и позволяет организовать более эффективную систему электропитания, уменьшить ее габариты, массу и стоимость. Цель достигается введением элемента И, мультиплексора, программируемого постоянного, запоминающего устройства (ППЗУ) и кольцевого распределителя с переменным модулем, соединенным разряднь - ми входами с соответствующими вьвсо- дами ППЗУ, адресные входы которых подсоединены к входным адресньН шинам и адресным входам мультрпшексо- ра, стробирующий вход которого сое- гЛ динен с выходом старшего п-разряда кольцевого распределителя с переменным модулем, а импульсные входы муль- g типлексора - к выходу элемента И, входы которого соединены с вь{ходами компаратора блока стабилизации напряжения и генератором тактовых шшуль- сов, вькод мультиплексора соединен |ч с импульсным входом регистра адреса v команд ППЗУ. 2 ил. Ц) s

| Многоканальный стабилизированный источник питания | 1977 |

|

SU736067A1 |

| Многоканальный стабилизированный источник питания | 1982 |

|

SU1030778A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1988-11-07—Публикация

1987-03-12—Подача