«

Изобретение относится к автоматике и вычислительной технике и может быть использовано в аппаратуре обработки образов, сжатия информации при передаче данных, для анализа и обработки звуковых и видеосигналов, для цифровой фильтрации и т.д.

Цель изобретения - упрощение устройства.

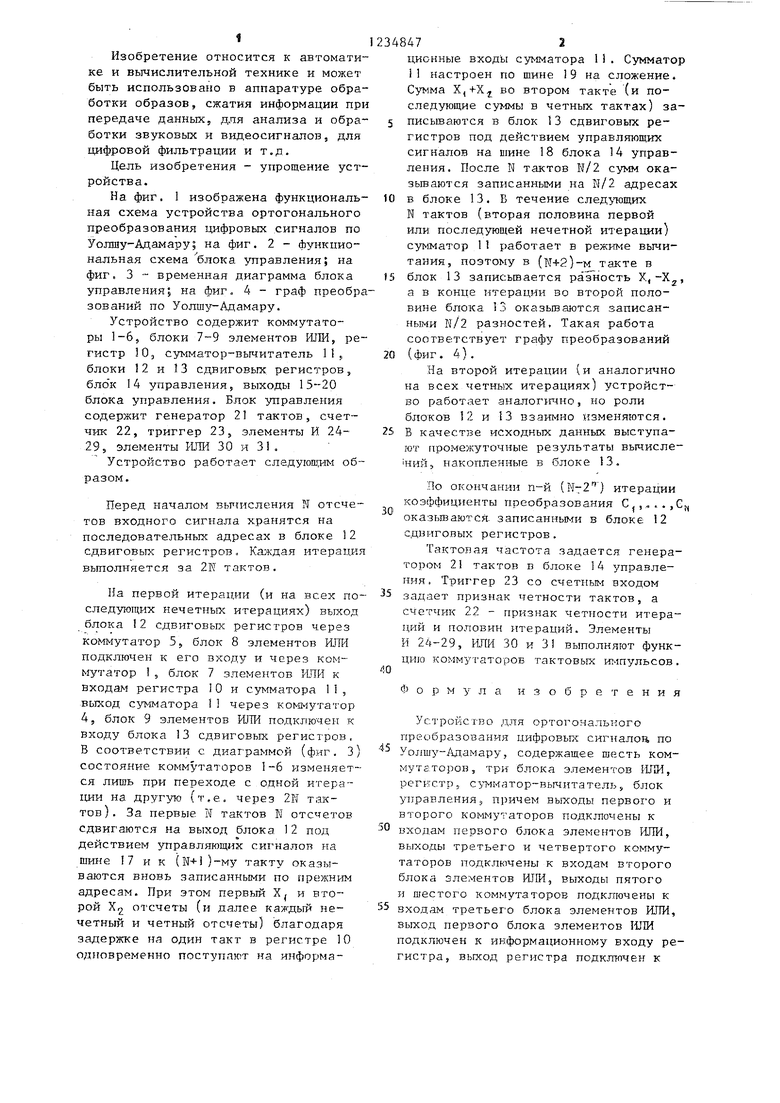

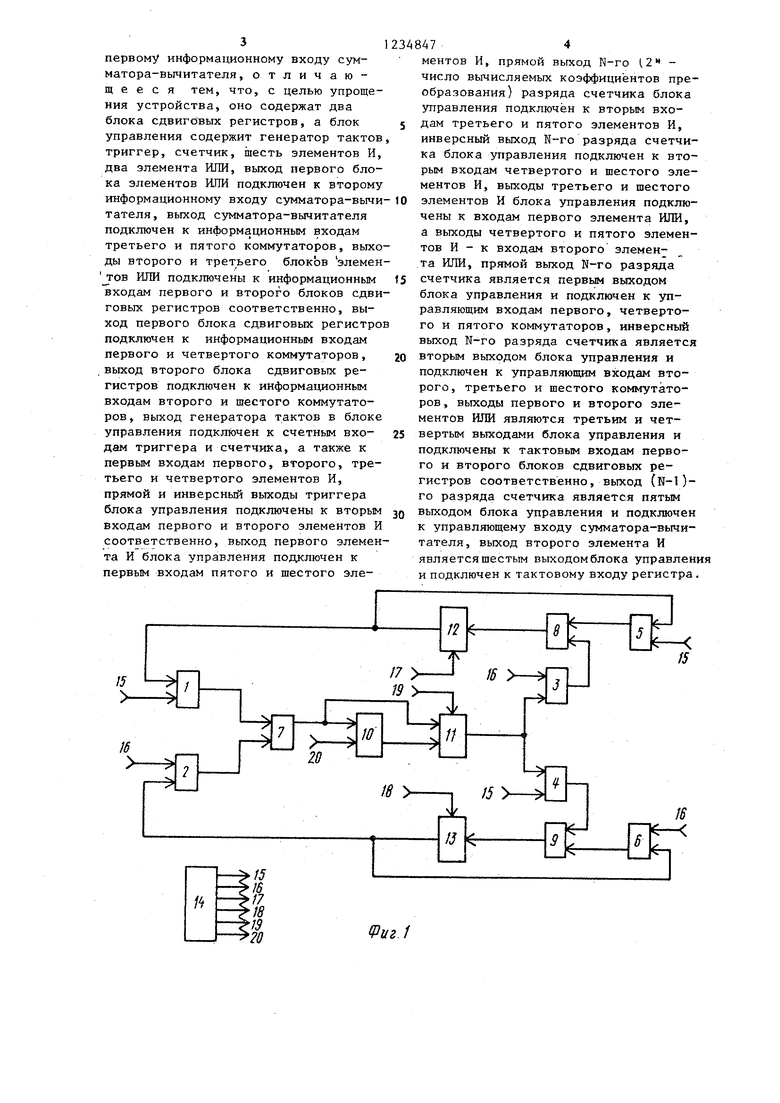

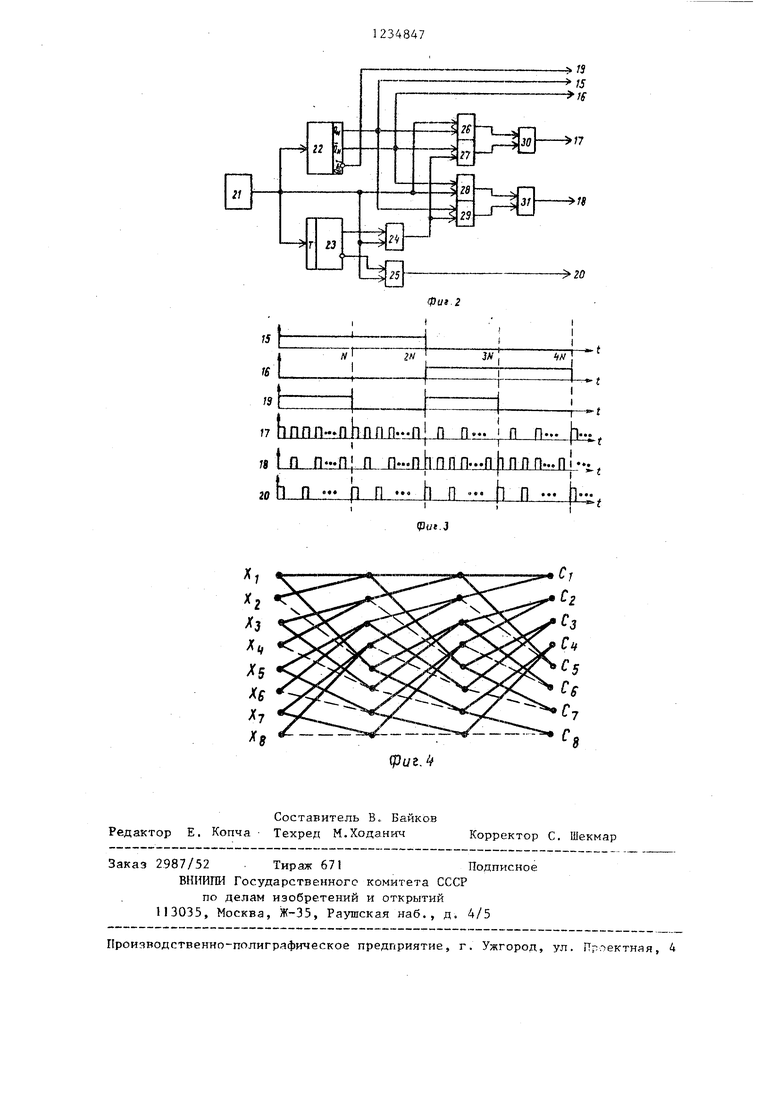

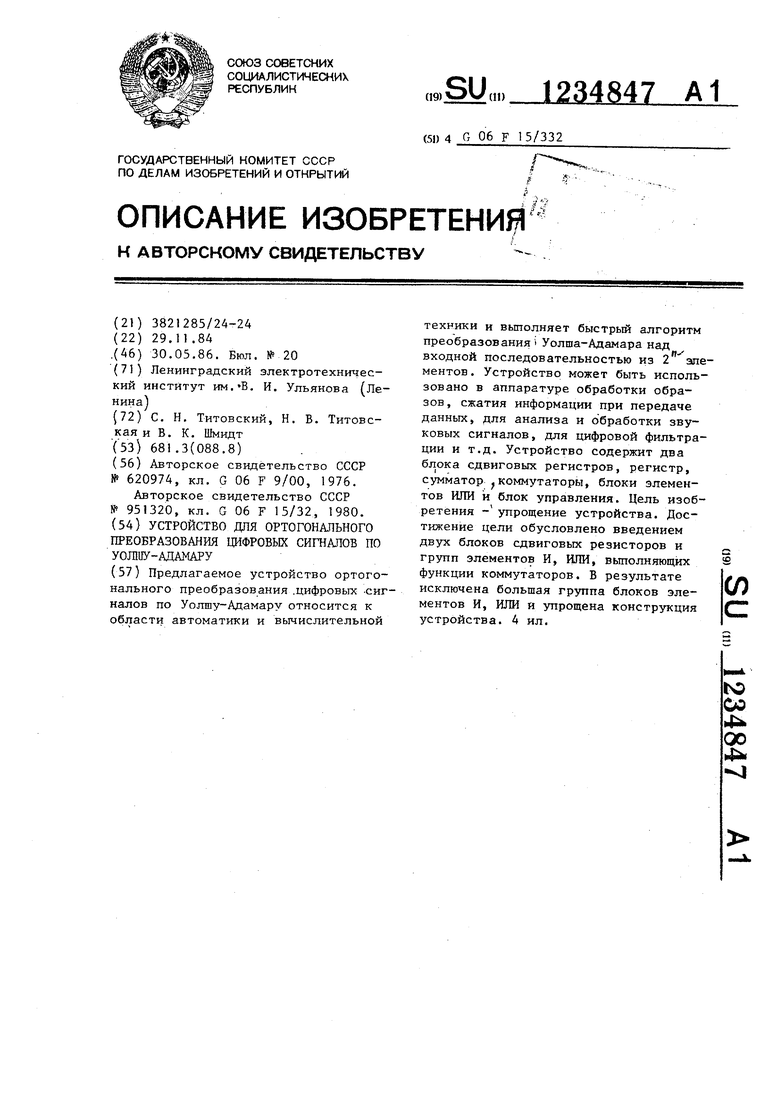

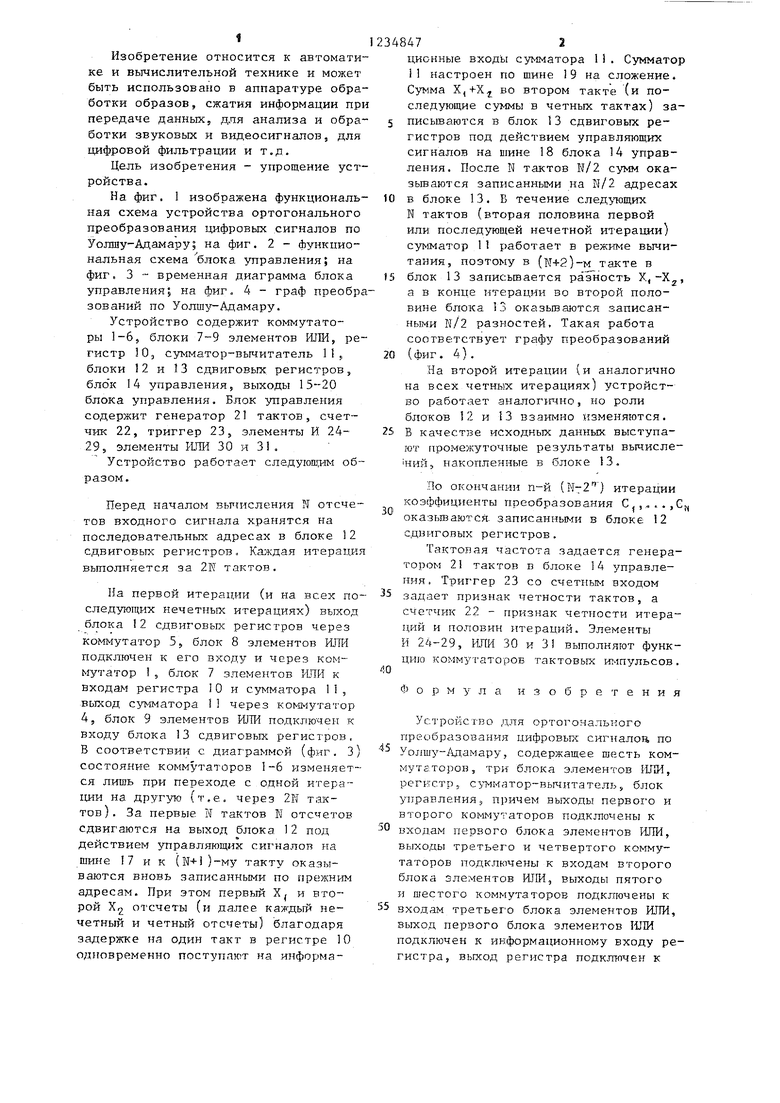

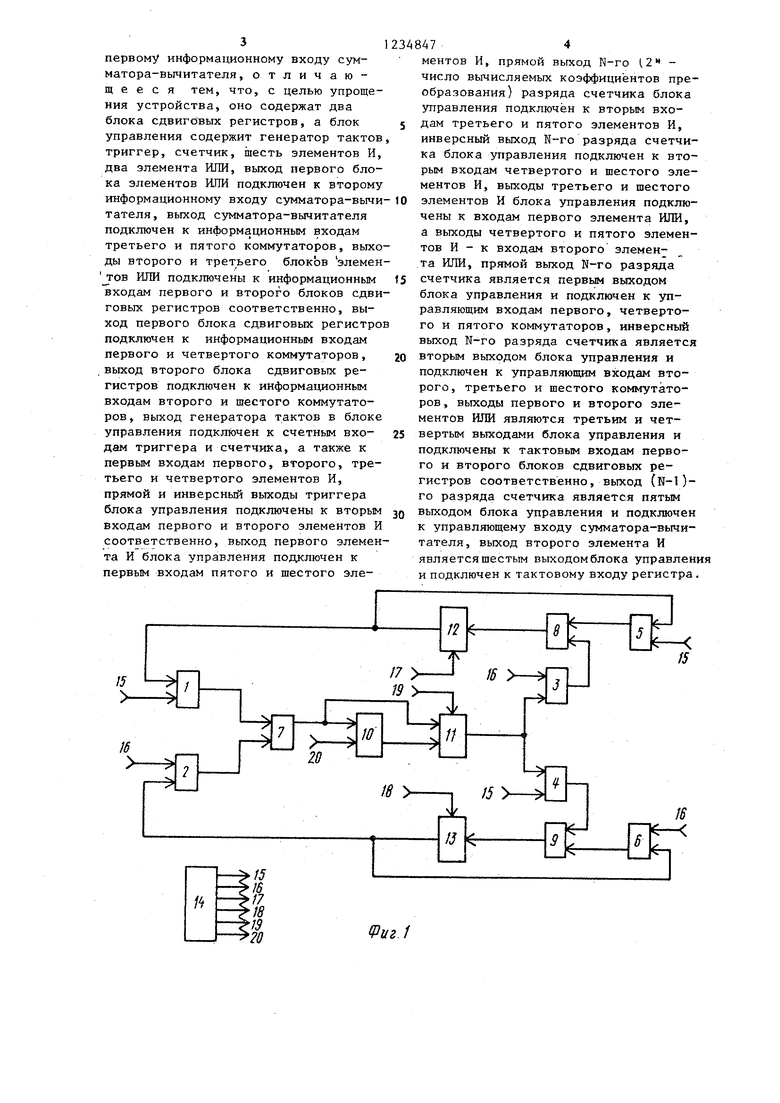

На фиг, 1 изображена функциональная схема устройства ортогонального преобразования цифровых сигналов по Уолшу-Адамару; на фиг. 2 - функциональная схема блока управления; на фиг. 3 - временная диаграмма блока управления; на фиг. 4 - граф преобразований по Уолшу-Адамару.

Устройство содержит коммутаторы 1-6,, блоки 7-9 элемер тов ШШ, регистр 10, сумматор-вьгчитатель 11, блоки 12 и 13 сдвиговых регистров, блок 14 управления 5 выходы 15-20 блока управления. Блок управления содержит генератор 21 тактов, счетчик 22, триггер 23, элементы И 24- 29, элементы РШИ 30 и 31.

Устройство работает следующим образом.

Перед началом вьписления N отсчетов входного сигнала хранятся на последовательных адресах в блоке 12 сдвиговых регистров. Каждая итерация выполняется за 2К тактов.

На первой итерации (и на всех последующих нечетнь Х итерациях) выход блока 2 сдвиговых регистров через коммутатор 5, блок 8 элементов ИЛИ подключен к его входу и через коммутатор 15 блок 7 элементов ЮТИ к входам регистра 10 и сумматора 11, выход сумматора 1 через ком:«)утатор 4, блок 9 элементов ИЛИ подключен к входу блока 13 сдвиговых регистров, В соответствии с диаграммой (фиг. З) состояние комм таторов 1-6 изменяется лишь при переходе с одной итерации на другую (т.е. через 2N тактов). За первые N тактов N отсчетов сдвигаются на выход блока 12 под действием управляющих сигналов на шине 7 и к ( )-му такту оказываются вновь записанными по прежним адресам. При этом первый Х и второй Х2 отсчеты (и далее каждый нечетный и четный отсчеты) благодаря задержке на один такт в регистре 10 одновременно поступают на информа348472

ционные входы сумматора 1i. Сумматор 11 настроен по шине 19 на сложение. Сумма X,+Xj во втором такте (и последующие суммы в четных тактах) за5 письшаются в блок 13 сдвиговых регистров под действием управляющих сигналов на шине 18 блока 14 управления. После N тактов Н/2 сумм ока- зьшаются записанными на N/2 адресах

10 в блоке 13. Б течение ,их N тактов (вторая половина первой или последующей нечетной итерации) сумматор I работает в режиме вычитания, поэтому в (N +2)-M такте в

5 блок 13 записьтается разность X,-Х, а в конце итерации во второй половине блока 13 оказьшаются записанными И/2 разностей. Такая работа соответствует графу преобразований

20 (фиг. 4).

На второй итерации (и аналогично на всех четных итерациях) устройство работает аналог1яно, но роли блоков 12 и 13 взаимно изменяются.

2S в качестве исходньк данных выступают промежуточные результаты вычисле- нийэ накопленные в блоке 13.

По окончании п-й (N-2) итерации коэффициенты преобразования С,,, .. ,Ср, оказьшаются. записанными в блоке 12 сдвиговых регистров.

Тактовая частота задается генератором 21 тактов в блоке 14 управления . Триггер 23 со счетпым входом 5 задает признак четности тактов, а счетчик 22 - признак четности итераций и половин итераций. Элементы И 24-29, ШИ 30 и 31 выполняют функцию коммутаторов тактовых Ш Шульсов.

40

Ф о р м у л а изобретения

Устройство для ортогонального преобразования цифровых сигналоа по

Уолшу-/1дамару, содержащее шесть коммутаторов, три блока элементов ИЛИ, регистр, с тчматор-вычитатель, блок управленияэ причем выходы первого и второго коммутаторов подключены к

входам первого блока элементов ИЛИ, выходы третьего и четвертого коммутаторов подключены к входам второго блока элементов ИЛИ, выходы пятого и шестого коммутаторов подключены к

входам третьего блока элементов ШТИ, выход первого блока злемектов 1ШИ одключен к информационному входу регистра, вькод регистра подключен к

первому информационному входу сум- матора-вычитателя, отличающееся тем, что, с целью упрощения устройства, оно содержат два блока сдвиговых регистров, а блок управления содержит генератор тактов, триггер, счетчик, шесть элементов И, два элемента ИЛИ, выход первого блока элементов И.Т1И подключен к второму информационному входу сумматора-вычи- тателя, выход сумматора-вычитателя подключен к информационным входам третьего и пятого коммутаторов, выходы второго и третьего блоков элемен- тов ИЛИ подключены к информационным входам первого и второго блоков сдвиговых регистров соответственно, выход первого блока сдвиговых регистров подключен к информационньм входам первого и четвертого коммутаторов, выход второго блока сдвиговых регистров подключен к информационным входам второго и шестого коммутаторов , выход генератора тактов в блоке управления подключен к счетным вхо- дам триггера и счетчика, а также к первым входам первого, второго, третьего и четвертого элементов И, прямой и инверсный выходы триггера блока управления подключены к вторым входам первого и второго элементов И соответственно, выход первого элемента И блока управления подключен к первым входам пятого и шестого элементов И, прямой выход N-ro I2 - число вычисляемых коэффициентов преобразования) разряда счетчика блока згправления подключён к вторым входам третьего и пятого элементов И, инверсный выход N-ro разряда счетчика блока управления подключен к вторым входам четвертого и шестого элементов И, выходы третьего и шестого элементов И блока управления подключены к входам первого элемента ШШ, а выходы четвертого и пятого элементов И - к входам второго элемента ИЛИ, прямой выход N-ro разряда счетчика является первьом выходом блока управления и подключен к управляющим входам первого, четвертого и пятого коммутаторов, инверсный выход N-ro разряда счетчика является вторым выходом блока управления и подключен к управляющим входам второго , третьего и шестого коммутаторов , выходы первого и второго элементов ИЛИ являются третьим и четвертым выходами блока управления и подключены к тактовьм входам первого и второго блоков сдвиговых регистров соответственно, выход (N-1)- го разряда счетчика является пятым выходом блока управления и подключен к управляющему входу сумматора-вычитателя, выход второго элемента И является шестым выходомблока управлен и подключен к тактовому входу регистра

22

1

t «I 4

r-i

4 I

7 hnnn- nhnnn -n| n n. ; n n- h-. III

Г8 In П n.nhniin...n|infTn ..n|- ;; w Ь П p fi h fi - |i П |i1 I

ч W

М

5

гй

I

JA

//

r-i

I

h-.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ортогонального преобразования цифровых сигналов по Уолшу-Адамару | 1988 |

|

SU1603398A1 |

| Устройство для ортогонального преобразования цифровых сигналов по Уолшу-Адамару | 1990 |

|

SU1815651A1 |

| Устройство для ортогонального преобразования цифровых сигналов по Уолшу-Адамару | 1990 |

|

SU1815650A1 |

| Устройство быстрого преобразования сигналов по Уолшу с упорядочением по Адамару | 1990 |

|

SU1784996A1 |

| Процессор быстрого преобразования уолша-адамара | 1989 |

|

SU1795471A1 |

| Устройство для быстрого преобразования Уолша-Адамара | 1987 |

|

SU1443002A1 |

| Устройство для быстрого ортогонального преобразования цифровых сигналов по Уолшу-Адамару | 1989 |

|

SU1615742A1 |

| Устройство для выполнения быстрого преобразования Уолша-Адамара | 1988 |

|

SU1605254A1 |

| Цифровой анализатор спектра Уолша речевых сигналов | 1987 |

|

SU1425710A1 |

| Устройство для ортогонального преобразования по Уолшу-Адамару | 1988 |

|

SU1571610A1 |

Предлагаемое устройство ортогонального преобразования .цифровых -сигналов по Уолшу-Адамару относится к области автоматики и вьтислительной техники и вьшолняет быстрый алгоритм преобразования Уолша-.Адамара над входной последовательностью из ментов. Устройство может быть использовано в аппаратуре обработки образов, сжатия информации при передаче данных, для анализа и обработки звуковых сигналов, для цифровой фильтрации и т.д. Устройство содержит два блока сдвиговых регистров, регистр, сумматор коммутаторы, блоки злемен- тов ИЛИ и блок управления. Цель изобретения - упрощение устройства. Достижение цели обусловлено введением двух блоков сдвиговых резисторов и групп элементов И, ИЛИ, вьтолняющих функции коммутаторов. В результате исключена большая группа блоков элементов И, ИЛИ и упрощена конструкция устройства. 4 ил. (Л ы 4 00 4; vi

Составитель В„ Байков Редактор Е. Копча Техред М.Ходанич

Заказ 2987/52 . Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

фае. 4

Корректор С. Шекмар

| Устройство ортогонального преобразования по уолшу | 1976 |

|

SU620974A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство ортогонального преобразования цифровых сигналов по Уолшу-Адамару | 1980 |

|

SU951320A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-05-30—Публикация

1984-11-29—Подача