Изобретение относится к автоматике и вычислительной технике и может быть использовано в аппаратуре обработки образов, сжатия информации при передаче данных, для анализа и обработки звуковых и видеосигналов, для цифровой фильтрации и т.д.

Известно устройство ортогонального преобразования по Уолшу, содержащее счетчик, регистры, сумматоры по модулю два, сумматоры-вычитатели и блоки свертки ij.

Наиболее близким техническим решением к данному изобретению является устройство ортогонального преобразования цифровых сигналов по УолшуАдамару, содержащее 2 сумматоров-вычитателей (п - порядок преобразования) . в известном устройстве, кроме того, содержится п-1 групп сумматоров-вычитателей по 2 сумматоров-вычитателей в каждой группе L2J.

Недостатком известных устройств является их сложность.

Цель изобретения - упрощение устройства.

Поставленная цель достигается тем, что устройство ортогонального преобразования цифровых сигналов по УолшуАдамару содержит регистров, 2

блоков элементов ИЛИ, блоков элементов И и блок формирования интервалов, причем i-ый информационный вход устройства (1+2) подключен к информационному входу (2i-l)-ro блока элементов И, выход i-ro сугиматрра-вычитателя подключен к информа- . ционному входу 2i-ro блока элементов И, управляющие -входы блоков элементов И с номерами (2i-l) и 21 подключены соответственно к прямом и инверсному выходам блока формирования временных интервалов, выходы (2i-l)го и 2i-ro блоков элементов И через i-й блок элементов ИЛИ подключены к входу i-ro регистра, выходы (2j-l)го и 2j-ro регистров (j ) подключены ко входам j-ro и ( )-го сумматоров-вычитателей, выходы регистров являются выходами устройства.

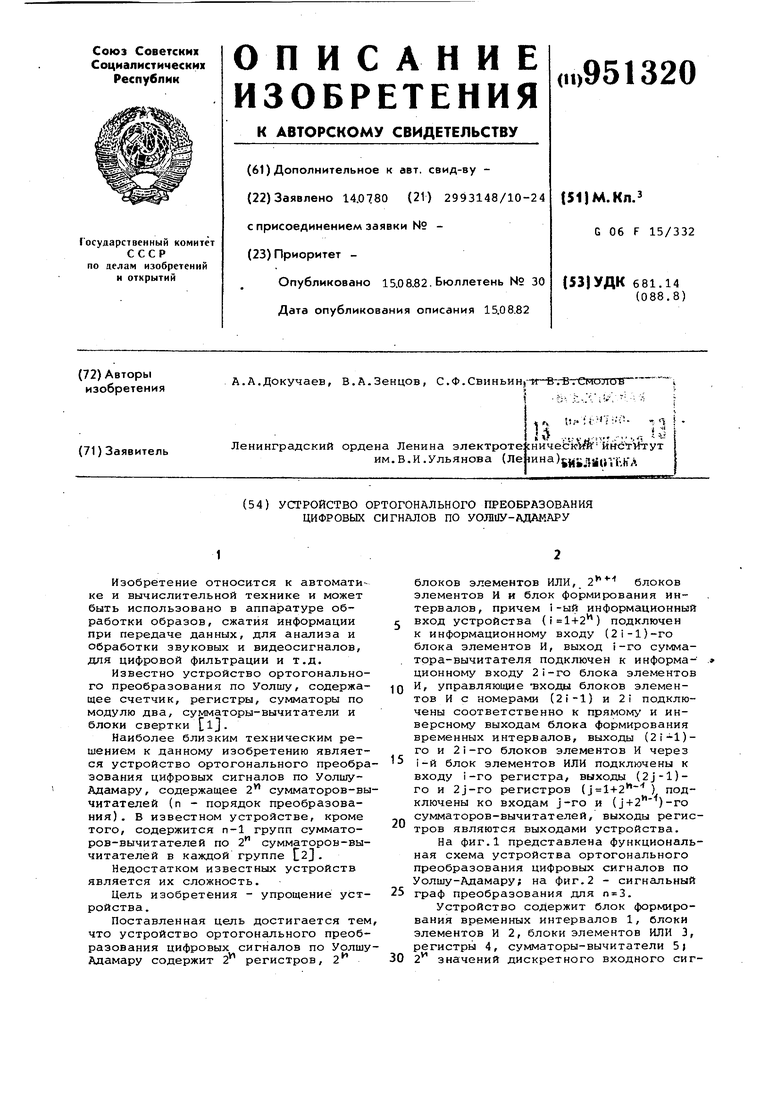

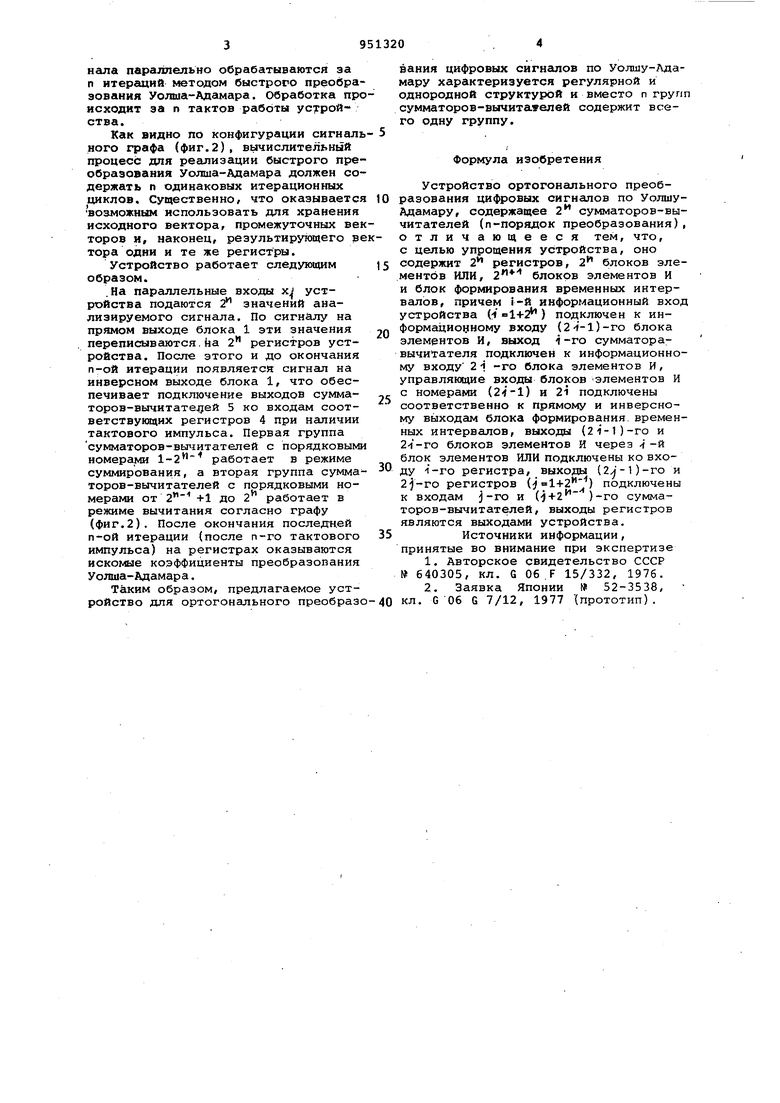

На фиг.1 представлена функциональная схема устройства ортогонального преобразования цифровых сигналов по Уолшу-Адамару; на фиг.2 - сигнальный граф преобразования для .

Устройство содержит блок формирования временных интервалов 1, блоки элементов И 2, блоки элементов ИЛИ 3, регистры 4, сумматоры-вычитатели 5 30 2 значений дискретного входного сигнала параллельно обрабатываются за п итерадий методом быстрого преобра зования Уолша-Адамара. Обработка пр исходит за п тактов работы устройства. Как видно по конфигурации сигналь кого графа (фиг.2), вычислительный процесс для реализации быстрого пре образования Уолша-Адамара должен со держать п одинаковых итерационных циклов. Существенно/ что оказываетс возможным использовать для хранения исходного вектора, промежуточных ве торов и, наконец, результирующего в тора одни и те же регистры. Устройство работает следующим образом. .На параллельные входы х устройства подаются 2 значений анализируемого сигнала. По сигналу на прямом выходе блока 1 эти значения переписываются.йа 2 регистров устройства. После этого и до окончания п-ой итерации появляется сигнал на инверсном выходе блока 1, что обеспечивает подключение выходов сумматоров-вычитате4 ей 5 ко входам соответствующих регистров 4 при наличии тактового импульса. Первая группа сумматоров-вычитателей с порядковыми номерами -2 работает в режиме суммирования, а вторая группа сумма торов-вычитателей с порядковыми номерами от +1 до 2 работает в режиме вычитания согласно графу (фиг.2). После окончания последней п-ой итерации (после п-го тактового импульса) на регистрах оказываются искомые коэффициенты преобразования Уолша-Адамара. Таким образом, предлагаемое устройство для ортогонального преобразо вания цифровых сигналов по Уолшу-Лдамару характеризуется регулярной и однородной структурой и вместо п групп сумматоров-вычитателей содержит всего одну группу. Формула изобретения Устройство ортогонального преобразования цифровых сигналов по УолшуАдамару, содержащее 2 сумматоров-вычитателей (п-порядок преобразования), отличающееся тем, что, с целью упрощения устройства, оно содержит 2 регистров, 2 блоков элементов ИЛИ, 2 блоков элементов И и блок формирования временных интервалов, причем i-й информационный вход устройства (i 1+ ) подключен к информациоуному входу (21-1)-го блока элементов И, выход i-го сумматоравычитателя подключен к информационному входу 21 -го блока элементов И, управляющие входы блоков элементов И с номерами () и 21 подключены соответственно к прямому и инверсному выходам блока формирования, временных интервалов, выходы (2i-1)-ro и 2-i-ro блоков элементов и через /J -и блок элементов ИЛИ подключены ко входу I-ro регистра, выходы (2.,-1 )-го и 2|-го регистров ( ) подключены к входам j-ro и (+2 )-го сумматоров-вычитателей, выходы регистров являются выходами устройства. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 640305, кл. G 06.F 15/332, 1976. 2.Заявка Японии 52-3538, кл. G 06 G 7/12, 1977 (прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ортогонального преобразования цифровых сигналов по Уолшу-Адамару | 1983 |

|

SU1107134A2 |

| Устройство для ортогонального преобразования цифровых сигналов по Уолшу-Адамару | 1987 |

|

SU1509930A1 |

| Устройство для вычисления коэффициентов преобразования по Уолшу-Адамару | 1983 |

|

SU1107133A1 |

| Устройство для выполнения быстрого преобразования Уолша | 1989 |

|

SU1693612A1 |

| Устройство для ортогонального преобразования цифровых сигналов по уолшу-адамару | 1984 |

|

SU1234847A1 |

| УСТРОЙСТВО БЫСТРОГО ПРЕОБРАЗОВАНИЯ УОЛША-АДАМАРА | 1991 |

|

RU2023299C1 |

| Устройство для выполнения быстрого преобразования Уолша | 1983 |

|

SU1141420A1 |

| Устройство для выполнения быстрого преобразования Уолша на скользящем интервале | 1990 |

|

SU1789990A1 |

| Устройство ортогонального преобразования по Уолшу | 1980 |

|

SU922721A2 |

| Устройство для ортогонального преобразования цифровых сигналов по Уолшу-Адамару | 1990 |

|

SU1815651A1 |

Авторы

Даты

1982-08-15—Публикация

1980-07-14—Подача