18 19

О5 ОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой анализатор спектра Уолша речевых сигналов | 1987 |

|

SU1425710A1 |

| Устройство для ортогонального преобразования цифровых сигналов по уолшу-адамару | 1984 |

|

SU1234847A1 |

| Устройство для быстрого преобразования Уолша-Адамара | 1987 |

|

SU1443002A1 |

| Процессор быстрого преобразования уолша-адамара | 1989 |

|

SU1795471A1 |

| Устройство для ортогонального преобразования цифровых сигналов по Уолшу-Адамару | 1990 |

|

SU1815650A1 |

| Устройство для быстрого ортогонального преобразования цифровых сигналов по Уолшу-Адамару | 1989 |

|

SU1615742A1 |

| Устройство для выполнения быстрого преобразования Уолша-Адамара | 1988 |

|

SU1605254A1 |

| Устройство для быстрого преобразования Уолша в реальном масштабе времени | 1988 |

|

SU1709341A1 |

| Устройство для ортогонального преобразования по Уолшу-Адамару | 1988 |

|

SU1571610A1 |

| Устройство для ортогонального преобразования цифровых сигналов по Уолшу-Адамару | 1990 |

|

SU1815651A1 |

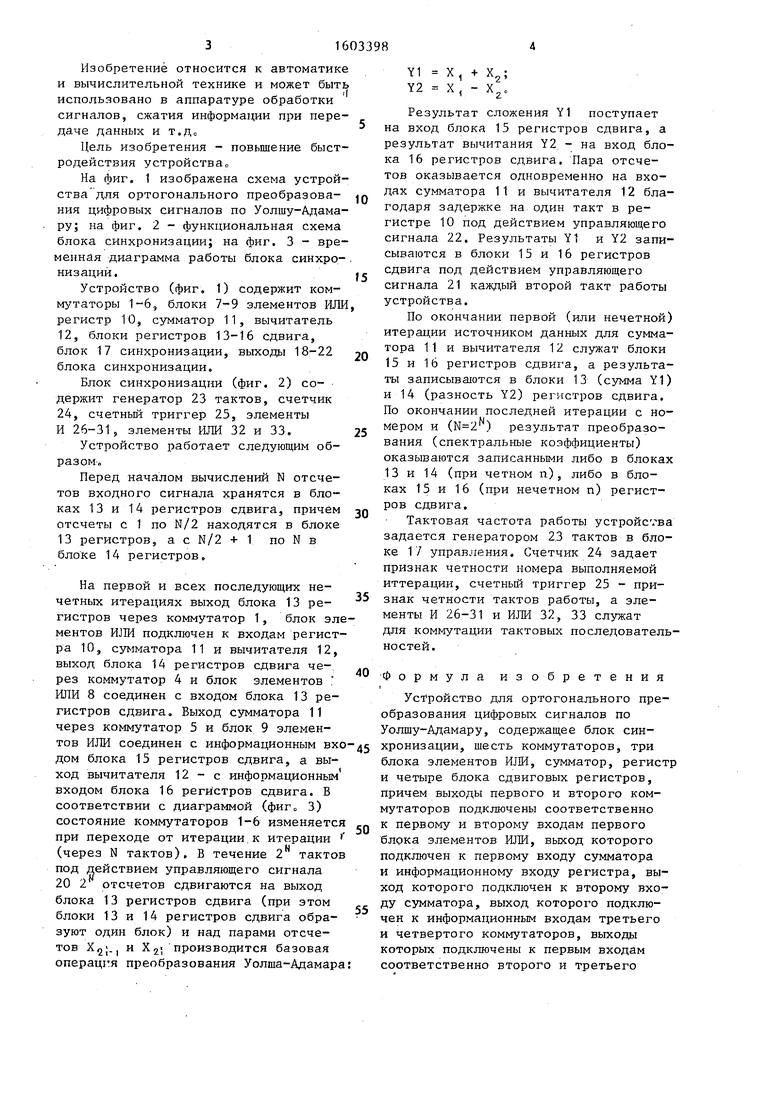

Изобретение относится к автоматике и вычислительной технике и может быть использовано в аппаратуре обработки сигналов, сжатия информации при передаче данных и т.д. Цель изобретения - увеличение быстродействия. Поставленная цель достигается за счет того, что в состав устройства входят коммутаторы 1-6, блоки элементов ИЛИ 7-9, регистр 10, сумматор 11, вычитатель 12, блоки сдвиговых регистров 13-16 и блок синхронизации 17. 3 ил.

Ф1/г.1

Изобретение относится к автоматике и вычислительной технике и может быть использовано в аппаратуре обработки сигналов, сжатия информации при передаче данных и т.До

Цель изобретения - повьшение быстродействия устройства

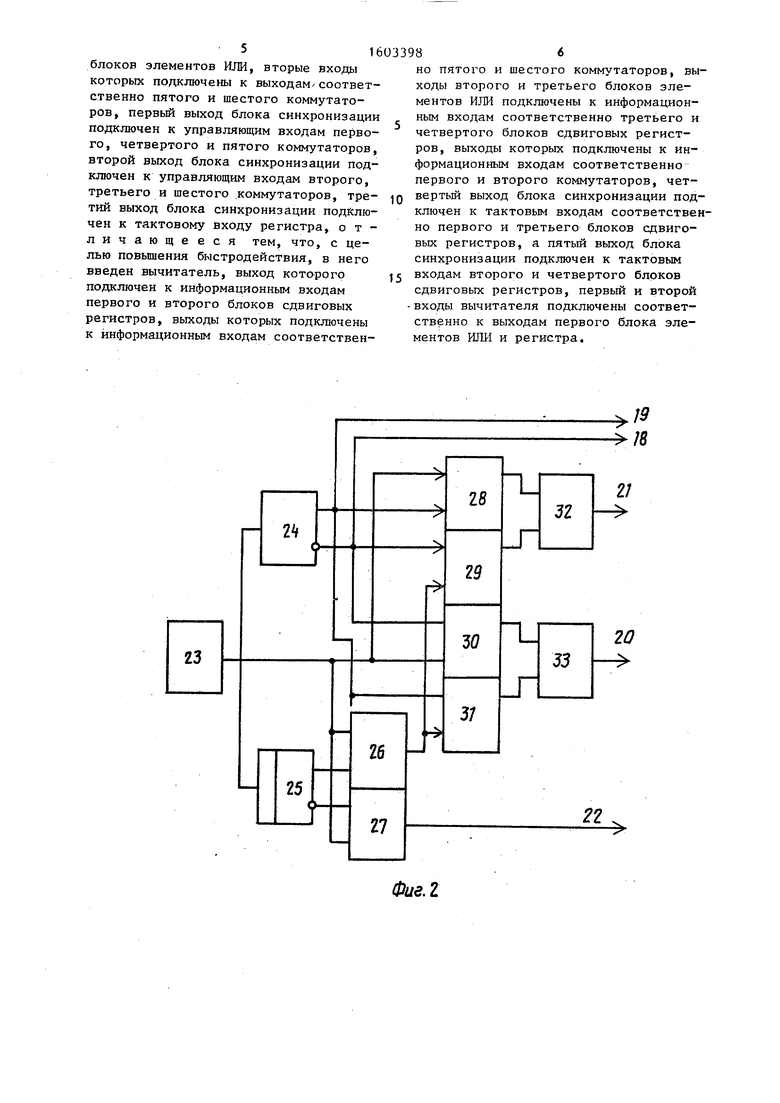

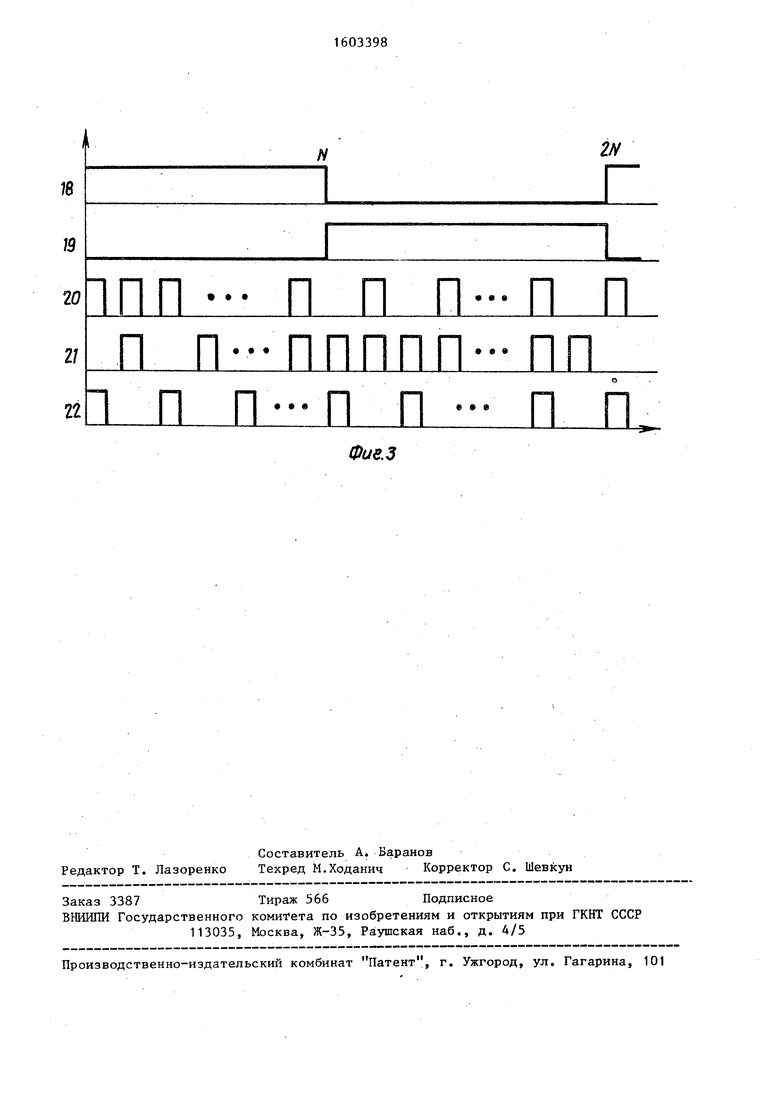

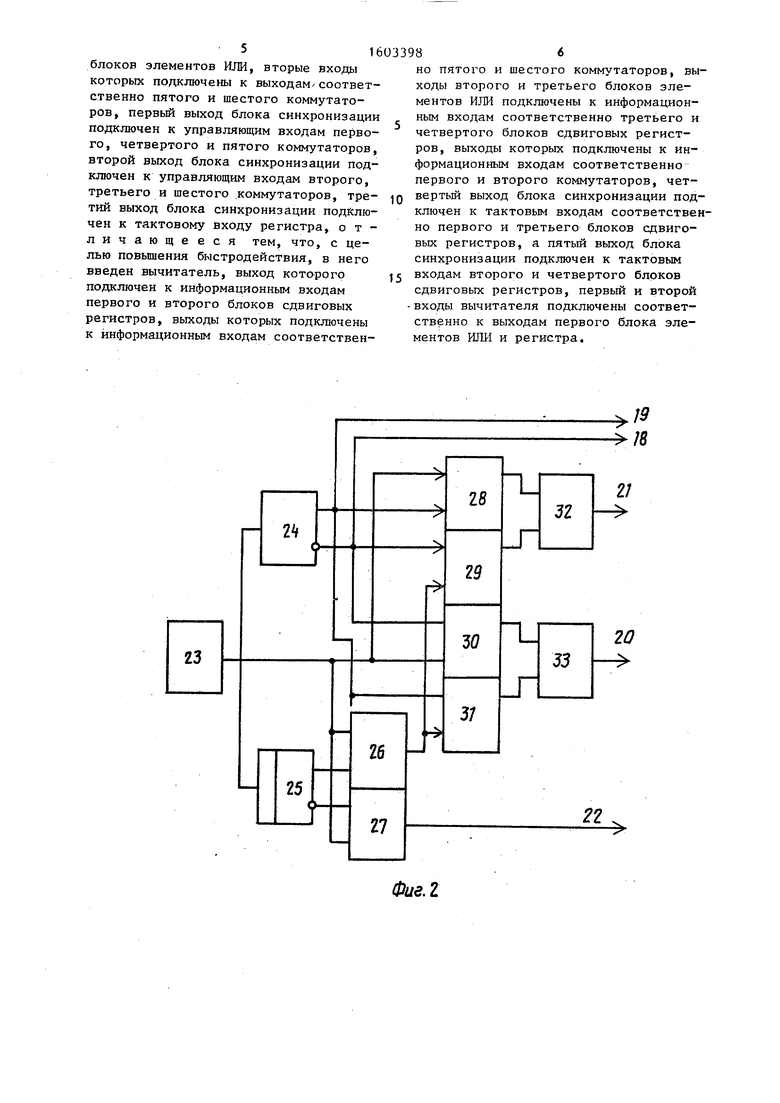

На фиг. 1 изображена схема устройства для ортогонального преобразования цифровых сигналов по Уолшу-Адама- ру; на фиг. 2 - функциональная схема блока синхронизации; на фиг. 3 - временная диаграмма работы блока синхро-. низаций.

Устройство (фиг. 1) содержит коммутаторы 1-6, блоки 7-9 элементов ИЛИ, регистр 10, сумматор 11, вычитатель 12, блоки регистров 13-16 сдвига, блок 17 синхронизации, выходы 18-22 блока синхронизации.

Блок синхронизации (фиг. 2) содержит генератор 23 тактов, счетчик 24, счетный триггер 25, элементы И 26-31, элементы ИЛИ 32 и 33.

Устройство работает следующим образом.

Перед началом вычислений N отсчетов входного сигнала хранятся в блоках 13 и 14 регистров сдвига, причем отсчеты с 1 по N/2 находятся в блоке 13 регистров, а с N/2 +1 по N в блоке 14 регистров.

На первой и всех последующих нечетных итерациях выход блока 13 регистров через коммутатор 1, блок элементов ИШ подключен к входам регистра 10, сумматора 11 и вычитателя 12, выход блока 14 регистров сдвига через коммутатор 4 и блок элементов ИЛИ 8 соединен с входом блока 13 регистров сдвига, Выход сумматора 11 через коммутатор 5 и блок 9 элемен10

15

20

25

30

35

40

Y1 X. + X,

Y2 X, X.

Результат сложения Y1 поступает на вход блока 15 регистров сдвига, а результат вычитания Y2 - на вход блока 16 регистров сдвига. Пара отсчетов оказывается одновременно на входах сумматора 11 и вычитателя 12 благодаря задержке на один такт в регистре 10 под действием управляющего сигнала 22. Результаты Y1 и Y2 записываются в блоки 15 и 16 регистров сдвига под действием управляющего сигнала 21 каждый второй такт работы устройства.

По окончании первой (или нечетной) итерации источником данных для сумматора 11 и вычитателя 12 служат блоки 15 и 16 регистров сдвига, а результаты записываются в блоки 13 (сумма Y1) и 14 (разность Y2) регистров сдвига. По окончании последней итерации с номером и () результат преобразования (спектральные коэффициенты) оказываются записанными либо в блоках 13 и 14 (при четном п), либо в блоках 15 и 16 (при нечетном п) регистров сдвига.

Тактовая частота работы устройства задается генератором 23 тактов в блоке 17 управления. Счетчик 24 задает признак четности номера выполняемой иттерации, счетньш триггер 25 - признак четности тактов работы, а элементы И 26-31 и ИЛИ 32, 33 служат для коммутации тактовых последовательностей.

Формула изобретения

Устройство для ортогонального преобразования цифровых сигналов по Уолшу-Адамару, содержащее блок синтов ИЛИ соединен с информационным хронизации, шесть коммутаторов, три

дом блока 15 регистров сдвига, а вы- блока элементов ИЛИ, сумматор, регистр

ход вычитателя 12 - с информационным

входом блока 16 регистров сдвига. В

соответствии с диаграммой (фиг о 3)

и четыре блока сдвиговых регистров, причем выходы первого и второго коммутаторов подключены соответственно к первому и второму входам первого блока элементов ИЛИ, выход которого подключен к первому входу сумматора и информационному входу регистра, выход которого подключен к второму входу сумматора, выход которого подключен к информационным входам третьего и четвертого коммутаторов, выходы которых подключены к первым входам соответственно второго и третьего

состояние коммутаторов 1-6 изменяется при переходе от итерации, к итерации (через N тактов). В течение 2 тактов под действием управляющего сигнала 20 2 отсчетов сдвигаются на выход блока 13 регистров сдвига (при этом блоки 13 и 14 регистров сдвига образуют один блок) и над парами отсчетов X,jj., и X2 , производится базовая операция преобразования Уолша-Адамара

Y1 X. + X,

Y2 X, X.

0

5

0

5

0

5

0

Результат сложения Y1 поступает на вход блока 15 регистров сдвига, а результат вычитания Y2 - на вход блока 16 регистров сдвига. Пара отсчетов оказывается одновременно на входах сумматора 11 и вычитателя 12 благодаря задержке на один такт в регистре 10 под действием управляющего сигнала 22. Результаты Y1 и Y2 записываются в блоки 15 и 16 регистров сдвига под действием управляющего сигнала 21 каждый второй такт работы устройства.

По окончании первой (или нечетной) итерации источником данных для сумматора 11 и вычитателя 12 служат блоки 15 и 16 регистров сдвига, а результаты записываются в блоки 13 (сумма Y1) и 14 (разность Y2) регистров сдвига. По окончании последней итерации с номером и () результат преобразования (спектральные коэффициенты) оказываются записанными либо в блоках 13 и 14 (при четном п), либо в блоках 15 и 16 (при нечетном п) регистров сдвига.

Тактовая частота работы устройства задается генератором 23 тактов в блоке 17 управления. Счетчик 24 задает признак четности номера выполняемой иттерации, счетньш триггер 25 - признак четности тактов работы, а элементы И 26-31 и ИЛИ 32, 33 служат для коммутации тактовых последовательностей.

Формула изобретения

0

5

и четыре блока сдвиговых регистров, причем выходы первого и второго коммутаторов подключены соответственно к первому и второму входам первого блока элементов ИЛИ, выход которого подключен к первому входу сумматора и информационному входу регистра, выход которого подключен к второму входу сумматора, выход которого подключен к информационным входам третьего и четвертого коммутаторов, выходы которых подключены к первым входам соответственно второго и третьего

5

блоков элементов ИЛИ, вторые входы которых подключены к выходам/соответственно пятого и шестого коммутаторов, первьй выход блока синхронизации подключен к управляющим входам первого, четвертого и пятого коммутаторов, второй выход блока синхронизации подключен к управляющим входам второго, третьего и шестого .коммутаторов, третий выход блока синхронизации подключен к тактовому входу регистра, отличающееся тем, что, с целью повышения быстродействия, в него введен вычитатель, выход которого подключен к информационным входам первого и второго блоков сдвиговых регистров, выходы которых подключены к информационным входам соответствен16

2

Z3

033986

но пятого и шестого коммутаторов, выходы второго и третьего блоков элементов ИЛИ подключены к информационным входам соответственно третьего и четвертого блоков сдвиговых регистров, выходы которых подключены к информационным входам соответственно первого и второго коммутаторов, четjQ вертьш выход блока синхронизации подключен к тактовым входам соответственно первого и третьего блоков сдвиговых регистров, а пятый выход блока синхронизации подключен к тактовым

5 входам второго и четвертого блоков

сдвиговых регистров, первый и второй - входы вычитателя подключены соответственно к выходам первого блока элементов ИЛИ и регистра.

19 1В

25

29

JZ

21

ЪО

20

55

27

22

Фие.2

Фие,3

| Устройство ортогонального преобразования по уолшу | 1976 |

|

SU620974A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для ортогонального преобразования цифровых сигналов по уолшу-адамару | 1984 |

|

SU1234847A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-10-30—Публикация

1988-12-19—Подача