Изобретение относится к цифровой вычислительной технике и может быть использовано в ЭВМ и цифровых системах с повьпненной достоверностью функ- илюнирования.

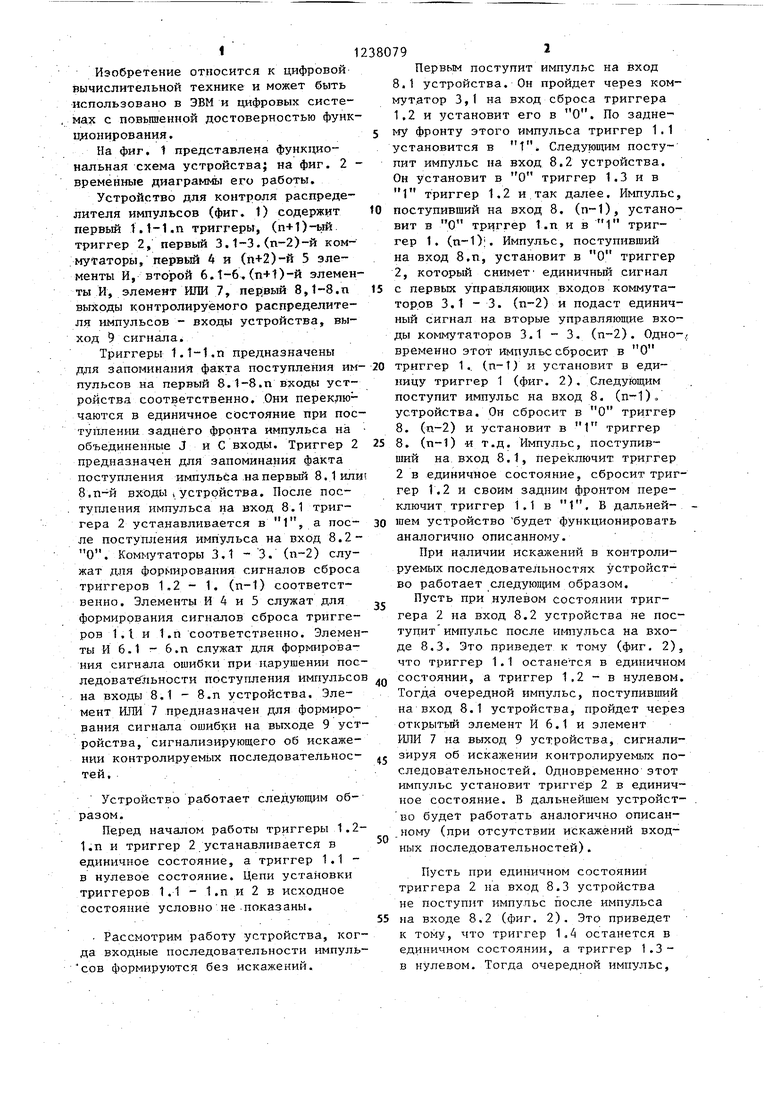

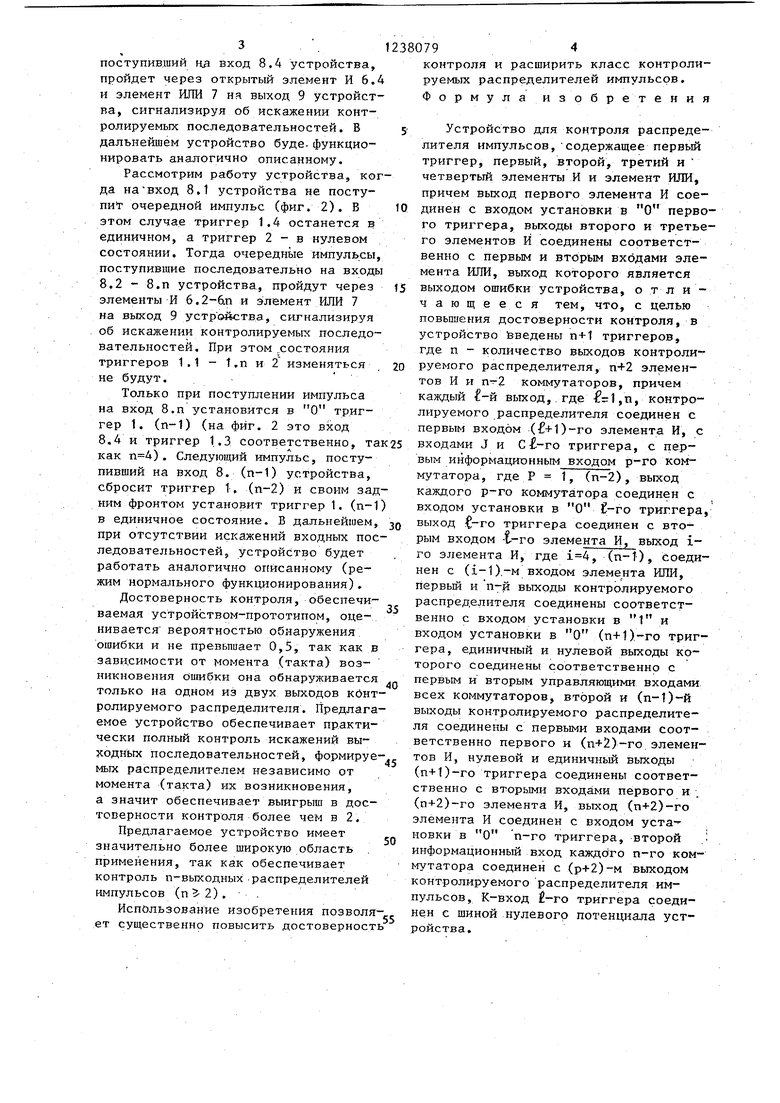

На фиг. 1 представлена функциональная схема устройства; на фиг. 2 - временные диаграм№Т его работы.

Устройство для контроля распределителя импульсов (фиг, 1) содержит первый 1.1-1.П триггеры, (п+1)-ый триггер 2, первый 3.1-3.(п-2)-й коммутаторы, первый 4 и ()-й 5 элементы И, второй 6.1-6, (п-И)-й элементы И, элемент ИЛИ 7, первый 8,1-8.п выходы контролируемого распределителя импульсов - входы устройства, выход 9 сигнала.

Триггеры 1.1-1.п предназначены

для запоминания факта поступления им- 20 триггер 1.. (п-1) и установит в еди- пульсов на первый 8.1-8.п входы уст- ницу триггер 1 (фиг. 2). Следующим

поступит импульс на вход 8. (п-1)о устройства. Он сбросит в О триггер

ройства соответственно. Они переключаются в единичное состояние при поступлении заднего фронта импульса на объединенные J и С входы. Триггер 2 предназначен для запоминания факта поступления импульса напервьш 8.1 или 8,п-й входы i устройства. После поступления импульса на вход 8.1 триггера 2 устанавливается в 1, а после поступления импульса на вход 8.2- 0. Коммутаторы 3.1 - 3. (п-2) служат для формирования сигналов сброса триггеров 1,2 - 1, (п-1) соответственно. Элементы И 4 и 5 служат для формирования сигналов сброса триггеров 1.1 и 1,п соответственно. Элементы И 6.1 - 6.П служат для формирова(п-2) и установит в 1 триггер

25

(п-1) « т.д. Импульс, поступивший на вход 8.1, переключит триггер 2 в единичное состояние, сбросит триггер 1.2 и своим задним фронтом переключит триггер 1.1 в 1, В дальней- 30 юем устройство будет функционировать аналогично описанному.

При наличии искажений в контролируемых последовательностях устройство работает следуюи(им образом.

Пусть при нулевом состоянии триггера 2 па вход 8.2 устройства не поступит импульс после ш-тульса на входе 8.3. Это приведет к тому (фиг. 2), что триггер 1.1 останется в единичном

35

Пусть при нулевом состоянии триггера 2 па вход 8.2 устройства не поступит импульс после ш-тульса на входе 8.3. Это приведет к тому (фиг. 2), что триггер 1.1 останется в единичном

ния сигнала ошибки при нарушении последоватё льности поступления импульсов Q состоянии, а триггер 1,2 - в нулевом.

на входы 8.1 - 8.П устройства. Эле- Тогда очередной импульс, поступивший

на вход 8.1 устройства, пройдет через открытый элемент И 6.1 и элемент ИЛИ 7 на выход 9 устройства, сигнали- ijj зируя об искажении контролируемых последовательностей. Одновременно этот импульс установит триггер 2 в единичное состояние. В дальнейшем устройст- во будет работать аналогично описанмент ИЛИ 7 предназначен для формирования сигнала ошибки на выходе 9 устройства, сигнализирующего об искажении контролируемых последовательностей.

Устройство работает следующим образом.

Перед началом работы триггеры 1.2- 1,п и триггер 2 устанавливается в единичное состояние, а триггер 1.1 - в нулевое состояние. Цепи установки триггеров 1.1 - 1 .п и 2 }з исходное состояние условно не показаны.

Рассмотрим работу устройства, когда входные последовательности импуль- сов формируются без искажений.

50

ному (при отсутствии искажений входных последовательностей).

Пусть при единичном состоянии триггера 2 на вход 8.3 устройства не поступит импульс после импульса 55 на входе 8.2 (фиг. 2). Это приведет к тому, что триггер 1,4 останется в единичном состоянии, а триггер 1.3- в нулевом. Тогда очередной импульс.

Первым поступит импульс на вход

8.1устройства. Он пройдет через коммутатор 3,1 на вход сброса триггера

1.2и установит его в О. По задне- му фронту этого импульса триггер 1,1

установится в 1. Следующим посту- пит импульс на вход 8.2 устройства. Он установит в О триггер 1.3 и в 1 триггер 1,2 и так далее. Импульс,

поступивший на вход 8, (п-1), установит в С триггер 1.П и в 1 триггер 1. (п-1):. Импульс, поступивший на вход 8.П, установит в О триггер 2, который снимет единичный сигнал

с первых управляюпщх входов коммутаторов 3.1 - 3. (п-2) и подаст единичный сигнал на вторые управляющие входы коммутаторов 3.1 - 3, (п-2). Одно-/ временно этот импульс сбросит в О

(п-2) и установит в 1 триггер

(п-1) « т.д. Импульс, поступивший на вход 8.1, переключит триггер 2 в единичное состояние, сбросит триггер 1.2 и своим задним фронтом переключит триггер 1.1 в 1, В дальней- юем устройство будет функционировать аналогично описанному.

При наличии искажений в контролируемых последовательностях устройство работает следуюи(им образом.

Пусть при нулевом состоянии триггера 2 па вход 8.2 устройства не поступит импульс после ш-тульса на входе 8.3. Это приведет к тому (фиг. 2), что триггер 1.1 останется в единичном

50

ному (при отсутствии искажений входных последовательностей).

Пусть при единичном состоянии триггера 2 на вход 8.3 устройства не поступит импульс после импульса на входе 8.2 (фиг. 2). Это приведет к тому, что триггер 1,4 останется в единичном состоянии, а триггер 1.3- в нулевом. Тогда очередной импульс.

поступивший нз вход 8,4 устройства, пройдет через открытый элемент И 6.4 и элемент ИЛИ 7 на выход 9 устройства, сигнализируя об искажении контролируемых последовательностей, В дальнейшем устройство буде- функционировать аналогично описанному.

Рассмотрим работу устройства, когда на ВХОД 8,1 устройства не поступит очередной импульс (фиг. 2). В этом случае триггер 1,4 останется в единичном, а триггер 2 - в нулевом состоянии. Тогда очередные импульсы, поступившие последовательно на входы 8,2 - 8,п устройства, пройдут через элементы И 6,2-6.п и элемент ИЛИ 7 на выход 9 устр ойства, сигнализируя об искажении контролируемых последовательностей. При этом .состояния триггеров 1.1 - t.n и 2 изменяться . не будут.

Только при поступлении импульса на вход 8.п установится в О триггер 1, (п-1) (на фиг, 2 это вход 8.4 и триггер 1,3 соответственно, так как ). Следующий импульс, поступивший на вход 8. (п-1) устройства, сбросит триггер 1, (п-2) и своим задним фронтом установит триггер 1, (п-1) в единичное состояние. В дальнейшем, при отсутствии искажений входных последовательностей, устройство будет работать аналогично описанному (режим нормшхьного функционирования).

Достоверность контроля, обеспечи

ваемая устройством-прототипом, оценивается вероятностью обнаружения ошибки и не превьпиает 0,5, так как р зависимости от момента (такта) возникновения оигибкн она обнарулсивается только на одном из двух выходов контролируемого распределителя. Предлагаемое устройство обеспечивает практически полный контроль искажений выходных последовательностей, формируемых распределителем независимо от момента (такта) их возникновения, а значит обеспечивает выигрыш в достоверности контроля более чем в 2.

Предлагаемое устройство имеет значительно более широкую область . применения, так как обеспечивает контроль п-выходных -распределителей шпульсов (п5- 2) , .

Использование изобретения позволяет существенно повысить достоверность

5

10 15 20

25 o

5

0

5

0

5

контроля и расширить класс контролируемых распределителей импульсов. Формула изобретения

Устройство для контроля распределителя импульсов,содержащее первый триггер, первый, второй, третий и четвертый элементы И и элемент ИЛИ, причем выход первого элемента И соединен с входом установки в О первого триггера, выходы второго и третьего элементов И соединены соответственно с первым и вторым входами элемента ИЛИ, выход которого является выходом ошибки устройства, о т л и - чающееся тем, что, с целью повьш1ения достоверности контроля, в устройство йведены п+1 триггеров, где и - количество выходов контроля- руемого распределителя, элементов И и п-2 коммутаторов, причем каждый f-й выход,. где ,п, контролируемого распределителя соединен с первым входОм (+1)-го элемента И, с входами J и Ct-ro триггера, с первым информационным входом р-го коммутатора, где Р 1, (п-2), выход каждого р-го коммутатора соединен с входом установки в О -го триггера, выход {-го триггера соединен с вторым входом -t-ro элемента И, выход i- го элемента И, где , (n-t-) соединен с (i-1),-M входом элеме нта ИЛИ, первый и п-й выходы контролируемого распределителя соединены соответственно с входом установки в 1 и входом установки в О (п+1)-го триггера, единичный и нулевой выходы которого соединены соответственно с первым и вторым управляющими входами всех коммутаторов, второй и (п-1)-и выходы контролируемого распределителя соединены с первыми входами соответственно первого и (п+2)-го.элементов И, нулевой и единичный выходы (п+1)-го триггера соединены соответственно с вторьми входами первого и . (п+2)-го элемента И, выход (п+2)-го элемента И соединен с входом уста- новки в О п-го триггера, второй . информационный вход каждОто п-го коммутатора соединен с (р+2)-м выходом контролируемого распределителя импульсов, К-вход -го триггера соединен с шиной нулевого потенциала устройства.

&1

«2

«3

i

г

tr

1.2 1.3 1Л A.t

4:i A3

4(

3

Редактор M. ТоЬтин

(pus.2

Составитель И. Сигалов

Техред Л.Сердюкова Корректор М. Шароши

Заказ 3293/50Тираж 671 Подписное

ВНИИЖ.Государственного комитета GCCP .

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. А/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля электропитания электронных вычислительных машин | 1984 |

|

SU1164714A1 |

| Устройство для решения задач на графах | 1990 |

|

SU1837312A1 |

| Устройство для сортировки чисел | 1990 |

|

SU1737441A1 |

| Устройство отождествления | 1991 |

|

SU1803910A1 |

| Счетное устройство | 1986 |

|

SU1368981A1 |

| Устройство для контроля распределения ресурсов в вычислительной системе | 1987 |

|

SU1476468A1 |

| Счетчик импульсов | 1985 |

|

SU1298906A1 |

| Устройство для контроля распределения ресурсов | 1985 |

|

SU1297061A1 |

| Счетное устройство | 1985 |

|

SU1256195A1 |

| Устройство для обмена информацией в мультипроцессорной вычислительной системе | 1988 |

|

SU1571594A1 |

Изобретение относится к области Цифровой вычислительной техники и может быть использовано в ЭВМ и цифровых системах с повьшенной достоверностью функционирования, В устройство, содержащее триггер, четыре элемента И и элемент ИЛИ, введены п+1 триггеров, где п - количество выходов контролируемого распределителя, п+2 элементов И и п-2 коммутаторов, что прив одит к повышению достоверности контроля. 2 ил. со оо QO

| Устройство для обнаружения ошибок в регистре сдвига | 1975 |

|

SU529488A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля импульсов | 1982 |

|

SU1045373A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-06-15—Публикация

1984-09-04—Подача