Изобретение относится к автоматике и вычислительной технике и может быть использовано при статистических испытаниях измерительгалх преобразователей, в измерительной технике, при статистическом моделировании и т.п. Цепь изобретения - повышение бы- cтpoдeйctвия и расширение функцио- налы-адх возможностей генератора за счет получения ступенчатого распре- деления. . - :

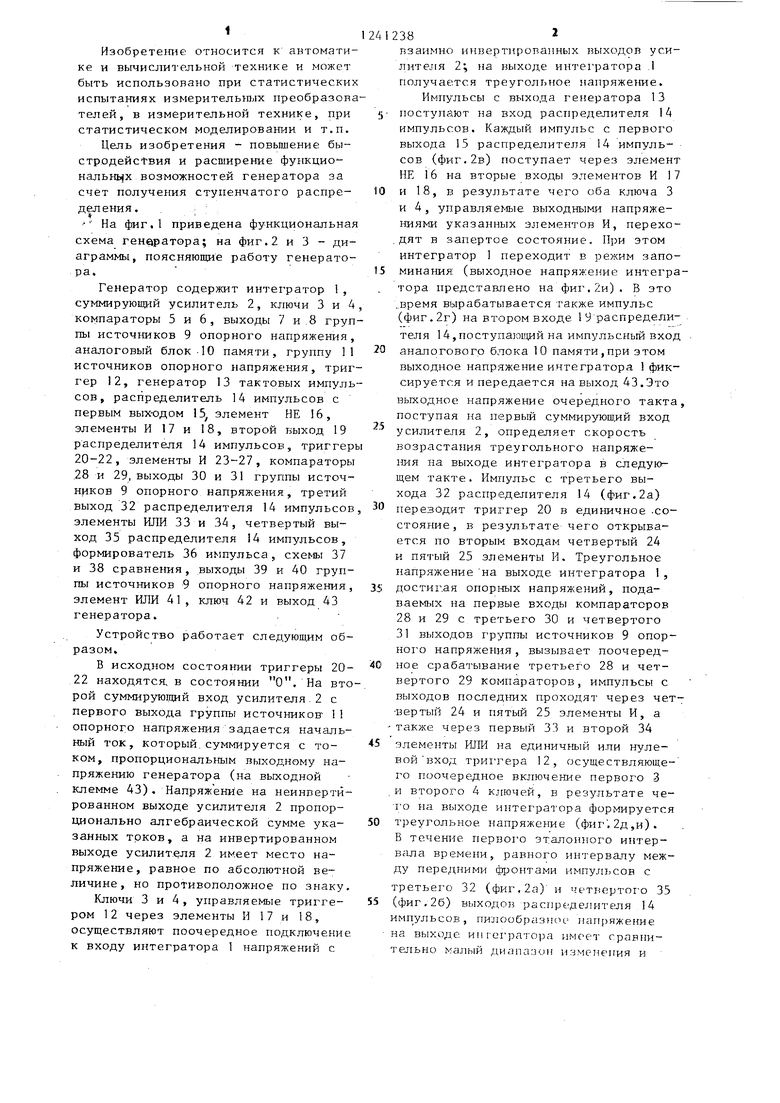

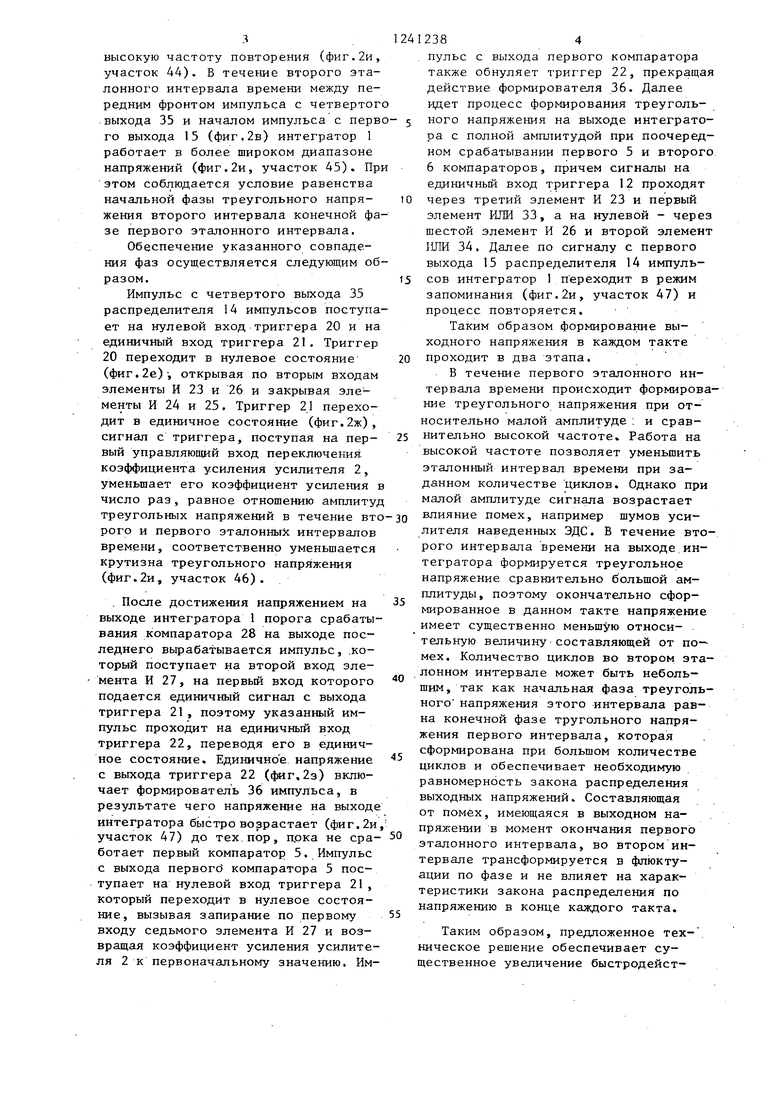

На фиг.1 приведена функциональная схема генератора; на фиг.2 и 3 - диаграммы, поясняющие работу генератора,

Генератор содержит интегратор 1, суммирующий усилитель 2, ключи 3 и 4 компараторы 5 и 6, выходы 7 и.8 группы источников 9 опорного напряжения, аналоговый блок -10 памяти, группу 11 источников опорного напряжения, триггер 12, генератор 13 тактовых импульсов, распределитель 14 импульсов с первым вых-одом 15. элемент НЕ 6,

элементы И 17 и 18, второй выход 19 распределителя 14 импульсов, триггер 20-22, элементы И 23-27, компараторы .28 и 29, выходы 30 и 31 группы источников 9 опорного напряжения, третий выход 32 распределителя 14 импульсов элементы ИЛИ 33 и 34, четвертый выход 35 распределителя 14 импульсов, формирователь 36 импульса, схемы 37 и 38 сравнения, выходы 39 и 40 группы источников 9 опорного напряжения, элемент ИЛИ 41, ключ 42 и выход 43 генератора.

Устройство работает следующим образом.

В исходном состоянии триггеры 20- 22 находятся, в состоянии О, На второй суммирующий вход усилителя.2 с первого выхода группы источников- 1 1 опорного напряжения задается начальный ток, который.суммируется с то- ком, пропорциональным выходному напряжению генератора (на выходной клемме 43). Напряжение на неинвертй- рованном выходе усилителя 2 пропорционально алгебраической сумме ука- занных трков, а на инвертированном выходе усилит.еля 2 имеет место напряжение, равное по абсолютной величине, но противоположное по знаку.

Ключи 3 и 4 , управляемые тригге- ром 12 через элементы И 17 и 18, осуществляют поочередное подключение к входу интегратора 1 напряжений с

5

5

5

2382

взаимно инвертированных выходов усилителя 2; на выходе интегратора .1 получается треугольное напряжение. Импульсы с выхода генератора 13 поступают на вход распределителя 14 импульсов. Каждый импульс с первого выхода 15 распределителя 14 импульсов (фиг,2в) поступает через элемент НЕ 16 на вторые входы элементов И 17 и 18, в результате чего оба ключа 3 и 4, управляем1)1е выходными напряжениями указанных элементов И, перехо- .дят в запертое состояние. При этом интегратор 1 переходит в режим запоминания (выходное напряжение интегратора предстанпено на фиг.2и). В это ..время вырабатывается также импульс (фиг.2г) на втором входе I У распределителя 14,поступа101и 1Й на импульсный вход аналоговог.о блока 10 памяти,при этом выходное напряжение и.нтегратора 1 фиксируется и передается на выход 43.Это выходное напряжение очередного такта, поступая на первый суммирующий вход усилителя 2, определяет скорость возрастания треугольного напряжения на выходе интегратора в следующем такте. Импульс с третьего выхода 32 распределителя 14 (фиг.2а) переводит триггер 20 в единичное -состояние , в результате чего открывается по вторым входам четвертый 24 и пятый 25 элементы И. Треугольное напряжение на выходе интегратора 1, достигая onopiHbix напряжений, пода- на первые входы компараторов 28 и 29 с третьего 30 и четвертого 31 выходов группы источников 9 опор- Hoi o на.пряжения, вызывает поочередное срабатывание третьего 28 и четвертого 29 компараторов, импульсы с выходов послед1та х проходят через чет- вертый 24 и пятый 25 элементы И, а - также через первый 33 и второй 34 элементы ИЛИ на единичный или нулевой вход т1)И1тера 12, осуществляющего поочередное включение первого 3 и второго 4 ключей, в результате чего на выходе интегратора формируется треугольное напряжение (фиг , 2д,и). В течение первого эталонного вала времени, равного интервалу между передними фронтами импульсов с третьего 32 (фиг.2а) и четвертого 35 (фиг,2б) выходов распределителя 14 имп ульсов, пилообразнсн напряжение на выходе ии rerpa i Opa имеет сравнительно малый диапазон изменечгия и

высокую частоту повторения (фиг.2и, участок 44). В течение второго эталонного интервала времени между передним фронтом импульса с четвертого выхода 35 и началом импульса с перво го выхода 15 (фиг.2в) интегратор 1 работает в более широком диапазоне напряжений (фиг.2и, участок 45). При этом соблюдается условие равенства начальной фазы треугольного напряжения второго интервала конечной фазе первого эталонного интервала.

Обеспечение указанного совпадения фаз осуществляется следующим образом.

Импульс с четвертого выхода 35 распределителя 14 импульсов поступает на нулевой вход триггера 20 и на единичный вход триггера 21. Триггер 20 переходит в нулевое состояние (фиг.2е)-, открывая по вторым входам элементы И 23 и 26 и закрывая элементы И 24 и 25. Триггер 21 переходит в единичное состояние (фиг.2ж), сигнал с триггера, поступая на первый управляющий вход переключения, коэффициента усиления усилителя 2, уменьшает его коэффициент усиления в число раз, равное отношению амплитуд треугольных напряжений в течение вто рого и первого эталонных интервалов времени, соответственно уменьшается крутизна треугольного напряжения (фиг.2и, участок 46).

. После достижения напряжением на выходе интегратора 1 порога срабатывания компаратора 28 на выходе последнего вырабатывается импульс, .который поступает на второй вход элемента И 27, на первый вход которого подается единичный сигнал с выхода триггера 21 , поэтому указанный импульс проходит на единичный вход триггера 22, переводя его в единичное состояние. Единичное напряжение с выхода триггера 22 (4яг.2з) включает формирователь 36 импульса, в результате чего напряжение на выходе

интегратора быстро возрастает (фиг.2и участок 47) до тех.пор, прка не сработает первый компаратор 5, Импульс с выхода nepBord компаратора 5 поступает на нулевой вход триггера 21 , который переходит в нулевое состояние, вызывая запирание по первому входу седьмого элемента И 27 и возвращая коэффициент усиления усилителя 2 к первоначальному значению, Им

10

15

20

25

30

35

40

45

0

55

12384

пульс с выхода первого компаратора также обнуляет триггер 22, прекращая действие формирователя 36. Далее идет процесс формирования треугольного напряжения на выходе интегратора с полной амплитудой при поочередном срабатывании первого 5 и второго 6 компараторов, причем сигналы на единичный вход триггера 12 проходят через третий элемент И 23 и первый элемент ИЛИ 33, а на нулевой - через шестой элемент И 26 и второй элемент 1ШИ 34, Далее по сигналу с первого выхода 15 распределителя 14 импульсов интегратор 1 переходит в режим запоминания (фиг,2и, участок 47) и процесс повторяется.

Таким образом формирование выходного напряжения в каждом такте проходит в два этапа,

В течение первого эталонного интервала времени происходит формирование треугольного напряжения при относительно малой амплитуде ; и сравнительно высокой частоте. Работа на высокой частоте позволяет уменьшить эталонный интервал времени при заданном количестве циклов. Однако при малой амплитуде сигнала возрастает влияние помех, например шумов усилителя наведенных ЭДС. В течение второго интервала времени на выходе.интегратора формируется треугольное напряжение сравнительно большой амплитуды, поэтому окончательно сформированное в данном такте напряжение имеет существенно меньшую относи- тельную величину составляющей от по мех. Количество циклов во втором эталонном инт ервале может быть небольшим, так как начальная фаза треугольного напряжения этого интервала равна конечной фазе тругольного напряжения первого интервала, которая сформирована при большом количестве циклов и обеспечивает необходимую равномерность закона распределения выходных напряжений. Составляющая от помех, имеющаяся в выходном напряжении в момент окончания первого эталонного интервала, во втором интервале трансформируется в флюктуации по фазе и не влияет на характеристики закона распределения по напряжению в конце каждого такта.

Таким образом, предложенное тех- ническое решение обеспечивает существенное увеличение быстродейст-

ВИЯ с сохранением точностных характеристик заданного закона распределения случайных выходных напряжений.

При формировании в течение перво- го эт-алонного интервала времени треугольного напряжения малой амплитуды введенные дополнительные элементы не влияют на работу устройства. В течение второго интервала времени, ког- да формируется треугольное напряжение большой амплитуды, при достижении напряжением на выходе интегратора 1 порогов срабатывания схем 37 и 38 сравнения, определяемых величиной напряжений на пятом 39 и шестом 40 выходах группы источников 9 опорного напряжения, сигналы поступают через элемент ИЛИ 41 на второй вход переключения коэффициента усиления усилителя 2 и на управляющий, вход третьего ключа 42. В результате изменяется коэффициент усиления усилителя и соответственно увеличивается входной ток смещения усилителя 2, чт приводит к увеличению крутизны треугольного напряжения в крайних диапазонах (меж,цу уровнем срабатывания сравнения 37 и компараторов 5 и между ypoвня ш срабатывания схем сравнения 38 и компараторов 6 - фиГъЗа). Если коэффициент передачи выходного напряжения и напряжения с мещения во .входную цепь интегратора на среднем участке в Е раз меньше чем на крайних участках диапазона выходных напряжений, то плотность, вероятностей на крайних участках в t раз меньше, чем на среднем участке (фиг.36). Таким образом, достигается получение ступенчатого закона распределения выходных напряжений.

Формула изобретения

Генератор случайного напряжения, содержащий генератор тактовых импульсов, выход которого соединен с входом распределителя импульсов, первый выход которого через элемент НЕ сое- /динен с первыми входами первого и второго элементов И, вторые входы которых подключены соответственно к единичному и нулевому выходам первого триггера, второй выход распределителя импульсов соединен с входом Запись аналогового блока памяти, выход которого является выходом генератора случайного напряжения и сое50 S 0 5 О 5 о

5

0

5

динен с первым сумьдарующим входом суммирующег о усилителя, второй сум- мируюЕшй вход которого подключен к первому выходу первого источника опорного напряжения, инверсный и прямой выходы сумми;рую1цего усилителя соединены с информационныъш входами соответственно первого и второго, ключей, управляющие входы которых подключены к выходс1М соответственно первого и второго элементов Hj выходы первого и второго ключей подключены к инфopмaциoннo ry входу интегратора, выход которого соединен с информационным входом аналогового блока памяти и с информационными входами первого и второго компараторов, входы задания уровня которых подключены соответственно к первому и второму выходам второго источника опорного напряжения , отличающийся тем, что, с целью расширения функциональных возможностей генератора путем получения ступенчатого распреде-. ления, он содеряшт три триггера, два компаратора, три элемента ИЛИ, фор- 1«1ирователь импульса, пять элементов И, две схемы сравнения и третий ключ, информационный вход которого подключен к второ гу выходу первого источ- .ника опорного напряжения, а выход третьего ключа соединен с третьим су1 1мир}лощим входом суммирующего усилителя , третий и четвертый выходы распределителя импульсов соединены соответственно с единичным и нулевым входами второго триггера, выход первого компаратора соединен с nep-i: БЫК входом третьего элемента И, ну- лейым входом третьего триггера и ну- .певым входом четвертого триггера, единичный выход которого через формирователь импульса соединен с входом Сброс интеграп-ора, выход которого соединен с первыми входами первой и второй схем срав.нения и информационными в одами третьего и четвертого компараторов, входы задания уровня которых подключены соответственно к третьему и четвертому выходам второго источника опорного напряжения, пятый и шестой вьгходы которого соединены соответственно с вторыми входами первой и второй схем сравнения., выходы которых соединены соответственно с первым и вторым входами первого элемента ИЛИ, выход которого соединен с управляющим входом

третьего ключа и входом задания первого коэффициента усиления суммирующего усилитехгя, вход задания второго коэффициента усиления которого подключен к единичному выходу третьего триггера, единичный вход которого подключен к четвертому выходу распределителя импульсов, выходы третьего и четвертого компараторов соединены соответственно с первыми входами четвертого и пятого элементов И, выходы которых соединены с первыми входами соответственно второго и третьего элементов ИЛИ, выходы которых соеди нены соответственно с единичным и ну левым входами первого триггера, выход второго компаратора соединен с

первым входом шестого элемента И, выход которого соединен с вторым входом третьего элемента ИЛИ, выход с третьего элемента И соединен с вторым входом второго элемента ИЛИ, выход третьего компаратора соединен с первым входом седьмого элемента И, второй вход которого подключен к

10 единичному выходу третьего триггера, а выход седьмого элемента И соединен с единичным входом четвертого триггера, единичный выход второго триггера соединен с вторыми входами

J5 четвертого и пятого элементов И, нулевой выход второго триггера соединен с вторыми входами третьего и шестого элементов И.

(flus.l

а О

Sg t О

t в

п

ев я а 9 в

I

(

-JL

, 15

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь напряжения в частоту | 1982 |

|

SU1045381A1 |

| Частотно-импульсное устройство преобразования сигнала с мостового датчика | 1986 |

|

SU1383474A1 |

| Аналого-цифровой преобразователь интегральных характеристик напряжений | 1984 |

|

SU1233283A1 |

| Цифровой измеритель активных сопротивлений | 1985 |

|

SU1308936A1 |

| Реле времени | 1988 |

|

SU1531196A1 |

| Преобразователь постоянного напряжения в частоту следования импульсов | 1984 |

|

SU1173559A1 |

| Преобразователь угла поворота вала в код | 1980 |

|

SU942089A1 |

| Цифровой измеритель температуры | 1990 |

|

SU1765719A1 |

| Аналого-цифровой преобразователь | 1974 |

|

SU1005305A1 |

| Емкостный преобразователь перемещения в код | 1989 |

|

SU1654970A1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано при статистических исследованиях. Целью изобретения является повышение быстродействия и расширение функцио- 5 нальных возможностей генератора за счет получения ступенчатого распределения . Генератор содержит две группы источников опорного напряжения, три ключа, суммирующий усилитель. генератор тактовых импульсов, распределитель импульсов, элемент НЕ, формирователь импульса,аналоговый блок памяти, три триггера, семь элементов И, три элемента ИЛИ, ин- тегратор,четыре компаратора, две схемы сравнения. Изобретение позволяет за счет небольшого дополнительного оборудования существенно повысить быстродействие формирования случайных напряжений при обеспечении высокой точности основных характеристик заданного закона распределения - диапазона формируемых напряжений, равномерной плотности вероятностей в заданном диапазоне, а также позволяет с большой точность реализовать ступенчатый закон распределения плотности вероятностей формируемых напряжений. Это позволит на более высоком метрологическом уровне проводить статистические испытания различных устройств автоматики, а следовательно , повысить качество выпускаемой продукции. 3 ил. с (О (Л с N3 ( N5 СО 00

Составитель А.Карас.ов Редактор Л.ПчелинскаяТехред О.ГортвайКорректор 0.Луговая

Заказ 3490/44Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 1130-35, Москва, Ж-35 , Раушская наб., д. 4/5

, -- - -

Производственно-полиграфическое предприятке.г.Ужгород,ул.Проектная,4

| ДАТЧИК СЛУЧАЙНЫХ УРОВНЕЙ НАПРЯЖЕНИЯ | 0 |

|

SU407348A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| ГЕНЕРАТОР СЛУЧАЙНЫХ НАПРЯЖЕНИЙ | 0 |

|

SU409348A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Патент США № 3205454, кл.331-78, опублик | |||

| Планшайба для точной расточки лекал и выработок | 1922 |

|

SU1976A1 |

Авторы

Даты

1986-06-30—Публикация

1984-06-26—Подача