код, регистр 25, введены ключи 4, 6, 7, 8, источники 2, 3 опорного напряжения, управляемый делитель 12 на

Изобретение относится к электроизмерительной технике и предназначено для измерения интегральных характеристик действующего, среднего и средневыпрямпенного значений напряжений произвольной формы.

Цель изобретения - распмрение области применения за счет обеспечения преобразования напряжений сложной формы.

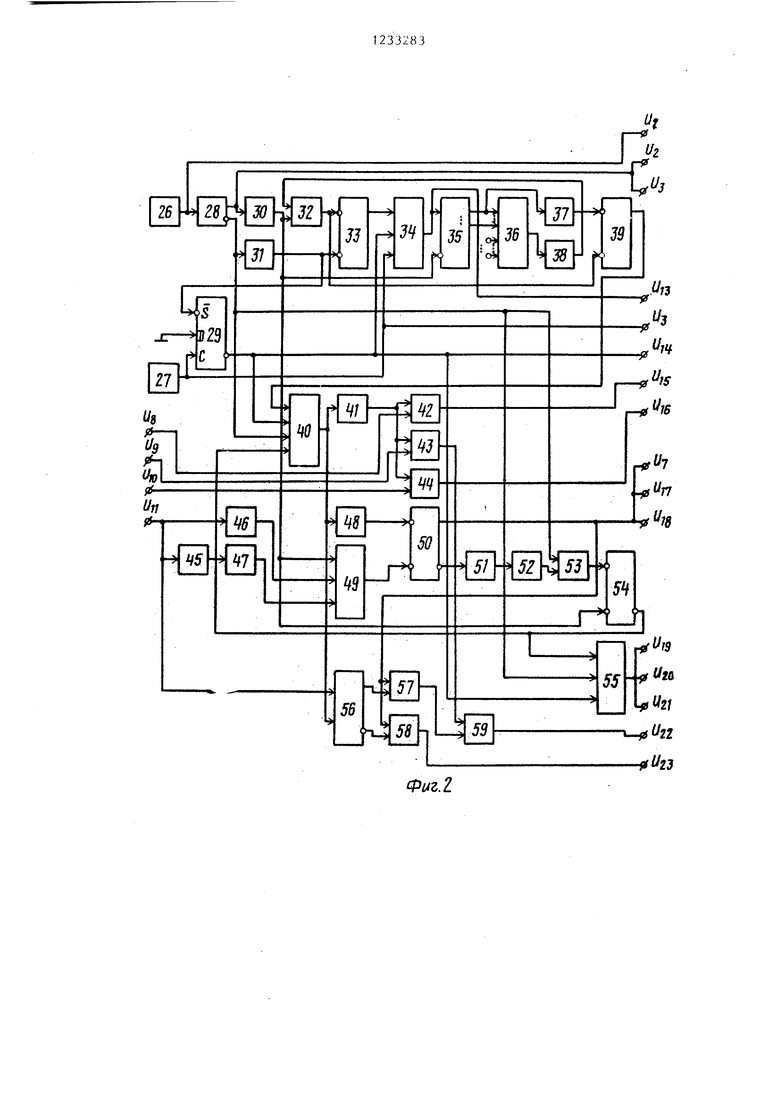

На фиг. 1 приведена функциональная схема устройства; на фиг, 2 - функциональная схема блока управления ; на фиг. 3 - функциональная схема микроэвм; на фиг. 4 - временные диаграммы работы устройства при преобразовании, например, действующего значения напряжения.

Устройство содержит (фиг., 1). источники 1-3 опорного напряжения, ключи 4-8, усилитель 9, блок 10 корекции нуля, функциональньм преобразователь 11, управляемый делитель 12 напряжения, инвертор 13, регистры 14 и 15, повторитель 16 напряжения, усилитель 17, интегратор 18, блок 19 разряда интегратора, компаратор 20, блок 21 управления, генератор 22 импульсов, преобразователь 23 время - код, микроэвм 24, регистр 25.

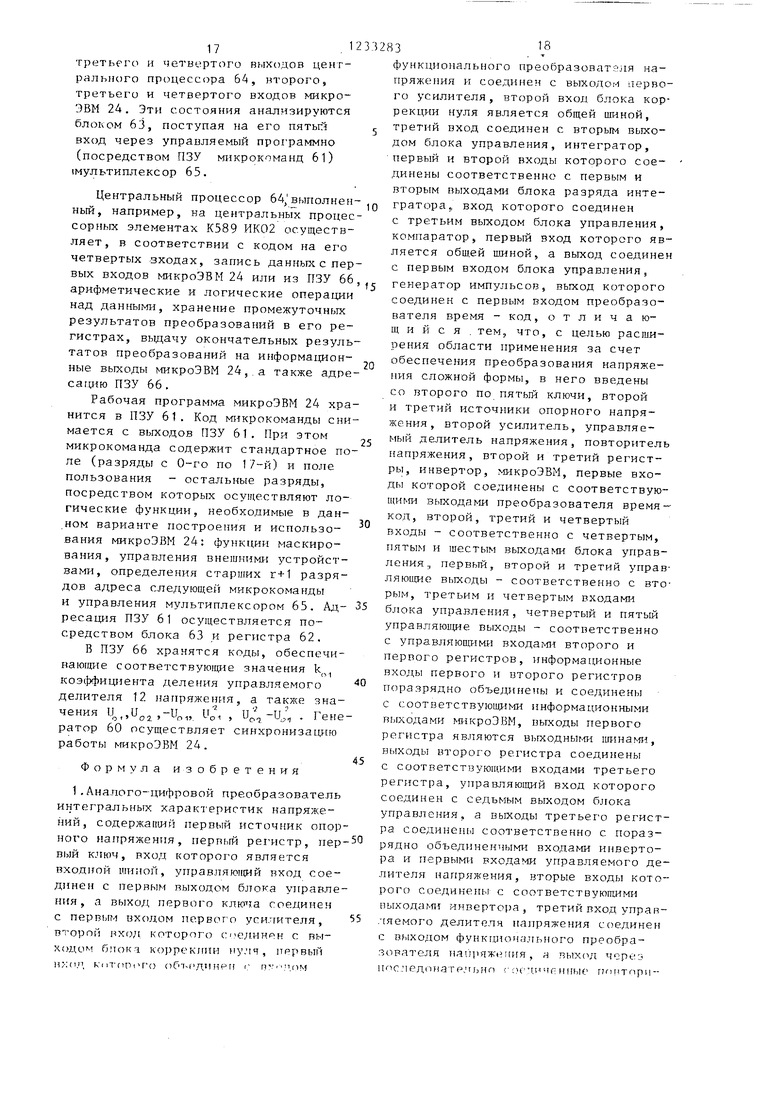

Блок управления (фиг. 2) содержит генераторы 26 и 27 импульсов, одно- вибратор 28, D-триггер 29, формирователи 30 и 31 коротких импульсов, элемент И 32, RS-триггер 33, элемент И 34, счетчик 35 импульсов, блок 36 сравнения, формирователи 37 и 38 коротких импульсов, RS-триггер 39, элемент И-НЕ 40, инвертор 41 элементы И 42 - 44, инвертор 45, формирователи 46 - 48 коротких импульсов, элемент И 49, RS-триггер 50, формирователь 51 коротких импульсов, инвертор 52, элемент И-НЕ 53, RS- триггер 54, элемент И-НЕ 55, D-триггер 56, элементы И 57,58, элемент Ш1И 59.

пряжении, повторитель 16 напряжений, усилитель 17, инвертор 13, регистры 14,15, микроэвм 24.2з.п.ф-лы,4ил.

Микроэвм содержит (фиг. 3) генератор 60 тактовых импульсов, постоян ное запо 1инающее устройство б1 , регистр 62, блок 63 микропрограммного управления, 5 центральный процессор 64, мультиплексор 65, постоянное запоминающее устройство 66. На временных диаграммах (фиг. 4) обозначено: U (t) - входное напряжение; U ,U ,U, - напряжения со 10 ответственно на выходах генератора 26, одновибратора 28, генератора 27 бло-. ка 21, которые и определяют соответственно длительность цикла преобразования, длительность времени началь15 ной установки и интервал времени Т между изменениями кода на управляющих входах управляемого делителя напряжения 12; U; - напряжение на выходе функ1дионального преобразователя 11 ,

.20 в качестве которого выступает анало- roBbriS квадратор; U - напряжение на выходе усилителя 17; U - напряжение на выходе интегратора 18 (который в данном примере является инвертирую25 щим); Uj - напряжение на третьем входе преобразователя 23.

Рассмотрим принцип работы устройства на примере преобразования действующего значения напряжения U(t)

ЗОВ цифровой код.

Общи:й цикл преобразования (интервал времени на фиг. 4) включает в себя три цикла, длительность которых определяется периодом импульс35 ного напряжения U. В течение первого цдкла (интервал времени ) происходит преобразование квадрата действующего значения преобразуемого напряжения U(t) в промежуточный ре40 зультат преобразования - двоичное число п,.

Преобразование осуществляется следующим образом. В течение времени начальной установки (интервал времени

jj ) первый вход входного усипителя 9 через ключ 6 подключен к нулевой пшне, а блок 10 н:а одится в ак

тивном состоянии. Интегратор 18нтечение времени начальной установки устанавливается в исходное начальное состояние посредством замыкания блока 19 в течение данного интервала времени. Одновременно в течение данного интервала времени преобразователь 23 устанавливается в нулевое состояние через его третий вход. Причем третий, второй и первый входы преобразователя 23 являются соответственно входами начальной установки, преобразуемого интервала времени и тактовой частоты.

По окончании времени начальной установки первый вход усилителя 9 остается подключенным посредством пятого ключа 6 к нулевой шине, блок 1 продолжает оставаться в активном состоянии, а блок 19 продолжает оставаться замкнутым.

С момента времени t первый вход усилителя 9 подключается посредством первого ключа 5 к преобразуемому напряжению и (t) , а блок 10 переходит в пассивное состояние, в котором он поддерживается до момента времени t. При этом на его выходе запоминается и хранится далее уровень корректирующего напряжения. Одновременно размы- кается блок 19 разряда интегратора, который поддерживается в разомкнутом состоянии до момента времени t.

Усилитель 17 (который при единичном или нулевом состоянии его управляющего входа работает соответственно в режиме инвертора или повторителя) с начала цикла преобразования и до момента времени t, поддерживается в режиме повторителя.

В течение интервала времени At(At t -t) происходит усреднение выходного напряжения функционального преобразователя 11 (в качестве которого выступает аналоговый квадратор), -прямо пропорционального значению U(t). Усреднение позволяет осуществить подавление переменной составляющей усредняемого напряжения, прямо пропорционального UJ(t) , при нулевом ослаблении его постоянной составляющей, которая прямо пропорциональна квадрату действующего значения преобразуемого напряжения U .

В устройстве усреднение осуществ- ляется известным методом весовой функ или посредством управляемого делителя 12 и интегратора 18. При этом в мо

е ,

12332834

мент времени 1 выходное напряжение- интегратора 18 l g,(t:) будет равно

J

,)Kjk;LK ct)(( t,

f I dt e(i-k ,At j, ut,(n-i)T,

где: k.

1 )

bv

коэффициент передачи усилителя 9;

k,J - соответственно коэффициент передачи и напряжение смещения функционального преобразователя 11; Lj(t) - весовая функция;

М - опорньш код на вторых входах блока сравнения 36; , 1 - соответственно коэффициент передачи и напряжение смещения повторителя 16; , Е - соответственно коэффициент передачи и напряжение смещения усилителя 17 при работе в режиме повторителя ;

k, t - соответственно коэффициент передачи и напряжение смещения интегратора 18; Т - период иьтульсов на выходе

генератора 27.

Весовая функция ) реализуется посредством управляемого делителя 12 напряжения известным методом ступенчатой аппроксима1дии по формуле

«

k

NK

35

oj (t)i: s(t)k.

(2)

где k - значение коэффициента деления управляемого делителя 12 в интервале времени

t.

- t

при этом длитель

ность интервала времени tj- t не зависит от значения i и равна периоду Т, значение t равно t

1

а t: -t

3

S(t) значение равно дt ,

единичная функция, которая определяется как ГО при ,,

S(t) 1 при t; .,

10 при (3)

Управляемьш делитель 12 напряжения является управляемым делителем напряжения известного типа R-2R. Его основу составляет декодирующая резис- тивная матрица типа R-2R разрядностью к+1, каждый разряд которой (при напряжении логической единицы на соответствующем управляющем входе) подключается соответственно к входному напряжению или к нулевой шине. При этом обеспечиваются значения коэфициента деления управляемого делителя 12 напряжения, лежапще в диапазоне от 1/2 до ( , которые мо гут изменяться с шагом дискретности .

Управляюиц1е коды, обеспечивающие соответствующие значения к (, 2,,..,т) коэффициента деления управляемого делителя 12, хранятся в соответствующем ПЗУ микроэвм 24 (например , в ПЗУ 66 при реализации микро- ЭВМ 24 по структурной , пред- ставленной на фиг. 3). Их поступление из соответствующего ПЗУ микро- ЭВМ 24 на первые и вторые входы управляемого делителя 12 напряжения осуществляется посредством инверто- ра 13, третьего и второго регистров 14 и 15 следующим образом. По окончании начальной установки (т.е. после момента времени t,, наступление которого распознается микроЭВМ 24 посредством анализа состояния ее второго входа) во второй регистр 15 по команде от микроЭВМ 24 заносится код соответствующий значению коэффициента деления управляемого делителя 12 напряжения, равному К, . Этот код в момент времени t, записывается в регистр 14, с выходов которого он поступает непосредственно на первые входы управляемого делителя 12 напряжения, и через инвертор 13 - на его вторые входы. После момента времени tj (наступление которого распознается микроЭВМ 24 посредством анализа состояния ее третьего входа) микро- ЭВМ 24 начинает запись во второй регистр 15 через промежутки времени, задаваемые программным путем и примерно равные Т кодов, соответствующих значениям коэффициентов деления управляемого делителя 12 напряжения , (где ,2 ,3 ,. . . ,т) . Эти коды записываются в регистр 14 через промежутки времени, точно равные Т, в связи с тем, что в течение интервала времени it на управляющий вход регистра 14 поступает импульсное напряжение Uj, Таким образом, изменения кода на входах управляемого делителя 12 напряжения происходят точно в соответствующие моменты времени t, (где ,2,.,.,т), что необходимо для обеспечения высокой точности ап- проксима1и1и. Введение регистра 14

.Q . п 25 ,..

5

0

5

0

5

обусловлено тем, что в отсутствие его длительность интервала времени между указанными изменениями кода (т.е. длительность интервала времени между занесениями кодов в регистр 15, задаваемая программно посредством микроЭВМ 24) не может быть обеспечена равной Т с высокой точностью.

Погрешность аппроксимации весовой фyнкпJ ИlJ(t) зависит от погрешности значений К , разрядности управляемого делителя 12 напряжения и от отно- гления T/ut| . Она может быть обеспечена достаточно малой при применении современной элементной базы.

Тогда после постановки в выражение (1) значения весовой функцииuJ(t), полученного в соответствии с (2) и (3), с учетом того, что ,, Б, 1 - напряжения постоянного тока, после соответствующих преобразований имеем

ив(зЬ-к,к;,к,. u;{i)di

.

i-n

K..H

jz:K,.L ,, E,(i-K.utJ, (Ц)

При этом подавление переменной составляющей усредняемого напряжения зависит от вида весовой функцииbJ(t) и длительности интервала времени усреднения, равного в данном случае ut,. Вид весовой функцииuj(t) и длительность интервала времени it,, в свою очередь, полностью определяются xpaняufl мcя в соответствующем ПЗУ микроэвм 24 массивом кодов, которые задают значения К коэффициента деления управляемого делителя 12 напряжения (размерностью массива и значениями кодов), а также кодом, определяюпц м длительность интервала времени лс , формируемого блоком 21 (например,, кодом на вторых входах блока 36 сравнения).

Тогда, исходя из того, что в процессе усреднения методом весовой функции переменная составляющая значения lJ,Mt), которую обозначим U (t) , подавляется при нулевом ослаблении постоянной составляющей, равной значению и,д , выражение (4) может быть

преобразовано следующим образом:

t .

(

и зЬ- кХпнХ. X ftu a

nCt)dt44,K,,,r

,(

fvi

l

к

d,

k n

к I - 1

.К,

f 4t

rri

К

к

-.,y.n,J.r,

:vKfnK K.,-(i-.t,),(s)

сГ - остаточная погрешность от

неполного подавления состав-to лякщей UMt), которая равна

cf.

VK

H4v

К,и„ (iUt

-- t .

1-1

ji может быть обеспечена достаточно малой при соответствующем выборе вида весовой фyнкп и uJ(t) и интервала времени d t| .

С момента времени первому ду усилителя 9 подключается посредством второго ключа 4 первое опорное напряжение U, на входах управляемого делителя 12 напряжения устанавливается код, обеспечиваюищй равенство его коэффициента деления фиксированному значению к , которое не меняется до момента времени t,. Одновременно усилитель 17 переводится в инверти bf,J f;Jdt-E.K,,,. (7) где KY , - соответственно коэффи- пиент передачи и напряжение смещения усилителя 17 при работе в режиме инвертораJ Е - напряжение смещения

нуля компаратора 20. Параллельно с процессом формирования интервала времени At импульсное напряжение U, определяющее данный интервал времени, поступает на третий вход преобразователя 23, в котором интервал времени ut линейно преобразуется в двоичное число п .

Подставив в выражение (7) значеРУЮ11ЩЙ режим работы. Выходное напря- 30 ние U(tj), полученное в соответствии

с выражением (5), с учетом того, что Ufli ,4 напряжения постоянного тока, а , , после соответствующих преобразований имеем

Р,.„

жение интегратора 18 U при этом с момента времени t начинает линейно возрастать, так как на третий вход интегратора 18 поступает напряжение, h ,--utj,-(к;

Х5

.jj)b.Ka, .

.

где f - частота выходных импульсов генератора 22.

Число п , получаемое на выходах . преобразователя 23, по окончании интервала времени /(,t заносится в COOT- S ветствующий регистр микроЭВМ 24. При этом окончание интервала времени дс распознается микроЭВМ 24 посредством анализа состояния ее четвертого входа.50

и п по тому же алгоритму, что и преВ течение интерзала времени t -t,образование в двоичное число п; квад(т.е. до начала следующего цикла пре-Р действующего значения напряжеобразования) первый вход усилителя М . описанное вьппе. Тогда,

через пятый ключ 6 подключен к нуле- 55с учетом того, что U, и U напря

вой шине, блок 10 находится в актив-жения постоянного тока, для п, и п

ном состоянии, -а блок 19 разряда ий-верны, по аналогии с , следующие

тегратора замкнут. Усилитель 17 с мо-равенства:

1233283

f 4t

времени д t

8

прямо пропорциональное значению - И Это продолжается в течение интервала от момента времени t.

тор 20 фиксирует равенство выходного напряжения интегратора 18 нулю. Тогда для выходного напряжения интегратора 18 в момент времени (t) верно следующее выражение- t,.

e(4).t,) K,,(K,K,K.;

15

,J f;Jdt-E.K,,,. (7) где KY , - соответственно коэффи- пиент передачи и напряжение смещения усилителя 17 при работе в режиме инвертораJ Е - напряжение смещения

нуля компаратора 20. Параллельно с процессом формирования интервала времени At импульсное напряжение U, определяющее данный интервал времени, поступает на третий вход преобразователя 23, в котором интервал времени ut линейно преобразуется в двоичное число п .

Подставив в выражение (7) значе-Гьк е

- 1 U (t

к :ьч

(8)

мента времени t переводится в режим повторителя .

В течение времени остальных двух циклов, входящих в общий цикл преобразования (интервалы времени соответственно t -t и t -t, ) осуществляетS Ю ЧО -13

ся преобразование квадратов действую- щих значений соответственно первого и второго опорных напряжений и Upi в промежуточные результаты преобразований - двоичные числа п

С инКкК : к:л.ЛкТ),,й1/с.(

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь интегральных характеристик напряжений | 1988 |

|

SU1615888A1 |

| Преобразователь код-напряжение | 1988 |

|

SU1508348A1 |

| Интегрирующий аналого-цифровой преобразователь | 1986 |

|

SU1345345A1 |

| Способ аналого-цифрового преобразования и устройство для его осуществления | 1986 |

|

SU1473083A1 |

| Интегрирующий аналого-цифровой преобразователь | 1986 |

|

SU1314458A1 |

| Интегрирующий аналого-цифровой преобразователь | 1982 |

|

SU1202056A1 |

| Помехоустойчивый преобразователь напряжения в интервал времени | 1985 |

|

SU1283972A1 |

| Устройство измерения частотных характеристик группового времени запаздывания четырехполюсников | 1988 |

|

SU1631511A1 |

| Устройство для управления регулируемым мостовым инвертором | 1988 |

|

SU1548830A1 |

| Аналого-цифровой преобразователь интегральных характеристик электрических величин | 1981 |

|

SU1035790A1 |

Изобретение относится к электроизмерительной технике и может быть использовано для измерения интегральных характеристик действующего, среднего и средневыпрямленного значений напряжений произвольной формы. Изобретение позволяет расширить область применения устройства. Это достигается тем, что в устройство, содержащее источник 1 опорного напряжения, ключ 5, усилитель 9, блок 10 коррекции нуля, функциональный преобразователь 11, интегратор 18, блок 19 разряда интегратора, компаратор 20, блок 21 управления, генератор 22 импульсов, преобразователь 23 вре:;я ю САд СО го 00 со

,-,5 .

ление окончательного результата преобразования - числа N , соответствую щего значению U,,. Это -вычисление

Л а

выполняется посредством микроЭВМ 24 по формуле

,,,...:

С11)

Время вьп1исления зависит от элементной базы, на которой построена микроэвм 24, и может быть обеспечено весьма малым по сравнению с длительностью интервала времени t - t . Значения и U при этом хранятся в соответствующем ПЗУ микро- ЭВМ 24 (например, в ПЗУ 66). Опорные напряжения Ug -U, ,U могут быть реализованы с высокой точностью известными методами.

Подставив в выражение (11) значения ,п и Hj , полученные в соответствии с вьфажениями (8), (9) и (10), после соответствующих преобразований имеем

и;,хЭ

K,K,,Z:K.K.C

(12) 45

где А,- остаточная погрешность конечного результата преобразования, обусловленная неполным подавлением переменной составляющей П(t) квадрата напряжения U(t). Приближенное значение д равно, в соответствии с известной формулой,

(K K .HKbKb,U,,,bK;,K,JJ)f К,

(

5

0

5

0

5

0

5

При этом, как следует из описанно го,значение Л может быть обеспечено достаточно малым при соответствующем выборе весовой функции ti-iCt) и интервала времени at .

По окончании процесса вычисления значение N заносится в первый регистр 25, затем снова осуществляются три описанных цикла преобразования.

Преобразование средневыпрямленного значения преобразуемого напряжения U.(t) происходит аналогично преобразованию его действующего значения. При этом в качестве функционального Преобразователя 11 выступает активный двухполупериодный вьшрямитель, напряжение на выходе которого прямо пропорционально значению модуля его входного напряжения. Постоянная состав- ляюш,ая модуля преобразуемого напряжения lU(t)l равна, по определению, средневыпрямпенному значению преобразуемого напряжения U. Переменную составляющую напряжения lUj(t)) обозначим (t:). В процессе усреднения напряжения lU,(t)l методом весовой функции его составляющая U (t) подавп

ляется при нулевом ослаблении постоянной составляющей, равной Uj. g Тогда, по аналогии с преобразованием действующего значения преобразуемого на- пряжения U(t), с учетом того, .что первое и второе опорные напряжения

и

01

и 1 - положительные напряже

ния постоянного тока, т.е. значения (Ug ) и (Uo,j) равны соответственно Up, и UQ , в данном случае промежуточные результаты преобразований п.,

.(

равны

,) ч ч,

d l)

II12)3283

где k ,К cci iTiu THTiuMiMo ко эф(1)иипент передачи и напряжение

смещения актиниого днух- полупериддиого пьтрямнтс- ля, выступающего в ка- 5 честве функционального преобразователя 11;

S -К к , к k,

о i, УК nfi I,

к , и, (tldt , 115J

преобразователя 11; значение. , как следует из опнсаи- остаточная погрешность от , обеспечено достаточ- нрпппногп попяялрния г.ос

неполного подаиления сое тавляющей U, (t) , равная 10

но малым

hj - fo

.,K,,u,T K;K jjif:K,K;j,,- .tj- К,„ к , J к ь КьТи7 Ь 1 п7 Г Р п

(.), pjf-)--V

(,ЧуЧс,РьЬ к н-р;к

Окончательный результат преобразователя при этом вычисляется посредством микроэвм 24 по формуле

N(U,,-U,,)U,,.

«св

к,к,,,к,к„

При преобразовании среднего значения преобразуемого напряжения Ц (t) в качестве функционального преобразователя 11 выступает простая перемычка . Преобразование выполняется аналогично преобразованию действующего и средневьшрямпенного значений преобразуемого напряжения U(t). При этом в течение интервалов времени ut , входящих в соответствующие циклы преобразования, осуществляется усреднение методом весовой функции напряжений, прямо пропорциональных

и..

соответственно значениям U(t) ,

и Ц,, .

Согласно определению, постоянная составляющая преобразуемого напряжения U,(t) равна его среднему значе- нию и , а его переменная составляющая, которую обозначим (t), подавляется в процессе усреднения методом весовой функции при нулевом ослаблении постоянной составляющей.

Преобразование среднего значения преобразуемого напряжения U(t) имее следующую особенность. Значение .

S -К к , к k,

о i, УК nfi I,

к , и, (tldt , 115J

значение ,

но малым

ue i

СП

д25

13)

30

35

е) йри 40 к

45

е- 50 ювоме55

я еет c.

в (ггличяе от 1); с 6 может быть как положительным, так и отрицательный.

В связи с этим выходное напряжение интегратора 18 в конце соответствующего нмтернала времени t (п течение которого происходит усреднение напряжения, прямо пропорционального значению ) может быть как отрицательным, так и положительным. Для обеспечения условий разряда интегратора 18 по окончании соответстиуюп1его интервала времени в устройстве к первому входу усилителя 9 в соответствующий момент времени подключается первое опорное напряжение U,, (при отрицательном выходном напряжении интегратора 18 по окончании соответствующего И1 тервала времени it, ) или второе опорное напряжение - U (в противоположном случае). При этом полярность выходного напряжения интегратора 18 по окончании интервала времени it оценивается блоком 21 посредством анализа состояния выхода компаратора 20 в соответствующий момент времени.

Тогда, по аналогии с преобразованием действующего и средневыпрямпен- ного значений преобразуемого напряжения и (t), с учетом того, что абсолютные значения первого и второго опорных напряжений U и U, равны, при преобразовании среднего значения напряжения U)i(t) промежуточные результаты преобразования nj , и п равны

Ъ -- f с

зования при этом вычисляется посредством микроэвм 24 по формуле

п. - гл

25

де напряжения на входе из нулевого в единичное состояние. Все используемые в блоке 21 RS-триггфы устанавливаются в единичное (нулевое) состояние импульсами инвертированной полярности соответственно на их входах S(R). Блок 36 имеет единичное состояние выхода при. равенстве кодов на обеих группах его входов, и нулевое - Блок 21 осуществляет синхрониза- ° противоположном случае.

Посредством первого D-триггера 29

(.-23;

1шю работы устройства и работает следуюцщм образом.

Первый и второй генераторы импульсов 26 и 27 осуществляют 2 енерацию импульсных напряжений соответственно Uj и и, . Период Т импульсного напряжения U должен быть обеспечен стабильным, что необходимо для обеспечения высокой точности аппроксимации весовой функ1Д1и (J (t) . Это может быть достигнуто, например, включением кварцевого резонатора во время- задающую цепь второго генератора 27 прямоугольных импульсов.

Одновибратор 28 генерирует, по перепаду напряжения на его входе из нулевого в единичное состояние, импульс длительностью прямой или инвертированной полярности соответст35

40

45

венно на прямом или инверсном выхо- 50 дах. Данный импульс определяет длительность начальной установки, а также поступает на второй вход микро- ЭВМ 24 и на третий вход преобразователя 2,3.

Все формирователи коротких импуль- соз, используемые в блоке 21, генерируют короткий пмпу.иьс гттшрртттрспани второго формирователя 31 осуществляется формирование на выходах первого D-триггера 29 импульса, длительность которого равна интервалу времени от конца начальной установки до прихода первого после ее окончания импульса, определяемого напряжением Uo. Данный импульс поступает на третий вход микроэвм 24. По его окончании посредством первого В-тригге- ра 29, второго 33 и третьего 39 триггеров, третьего элемента И 34, счетчика 35, блока 36, третьего 38 и четвертого 37 формирователей, первого элемента И-НЕ 40 и первого инвертора 41 осуществляются формирование импульса длительностью ut на выходе первого инвертора 41, а также Ьодача импульсного напряжения U с выхода третьего элемента 34 на управляющий вход регистра 14 в течение интервала времени dt, . При этом введением первого формирователя 30 и первого элемента И 32 осуп1ествляет- ся установка в нулевое состояние второго 33 и третьего 39 RS-триггеров в начале каждог о цикла п браэова(2.7)

5

0

5

0 5

и второго формирователя 31 осуществляется формирование на выходах первого D-триггера 29 импульса, длительность которого равна интервалу времени от конца начальной установки до прихода первого после ее окончания импульса, определяемого напряжением Uo. Данный импульс поступает на третий вход микроэвм 24. По его окончании посредством первого В-тригге- ра 29, второго 33 и третьего 39 триггеров, третьего элемента И 34, счетчика 35, блока 36, третьего 38 и четвертого 37 формирователей, первого элемента И-НЕ 40 и первого инвертора 41 осуществляются формирование импульса длительностью ut на выходе первого инвертора 41, а также Ьодача импульсного напряжения U с выхода третьего элемента 34 на управляющий вход регистра 14 в течение интервала времени dt, . При этом введением первого формирователя 30 и первого элемента И 32 осуп1ествляет- ся установка в нулевое состояние второго 33 и третьего 39 RS-триггеров в начале каждог о цикла п браэова15

ПИЯ. Тем самым устраняется влияние возможных ложных срабатываний RS- трип еров 33 н 39 по включении питания на дальнейшую работу устройства. Введение первого элемента Н-НЕ 40 устраняет одновременное подключение первого входа усилителя 9 к нулевой шине и к преобразуемому напряжению, что может иметь место при сбоях, могущих возникнуть, например, по вклю- чении питания.

На четвертом 42, пятом 43 и шестом 44 элементах И реализован распределитель импульсов. Первые входы элементов И 42 - 44, объединенные вмес- те, служат сигнальным входом данного распределителя импульсов, а вторые их входы - его управляющими входами. Таким образом, в зависимости от состояния первого, второго и тре- тьего управляющих выходов микроЭВМ 24 (которое может оставаться неизменным в течение всего текущего цикла преобразования) осуществляется подача в течение интервала времени л С , вхо дящего в текущий цикл преобразования импульса на управляющий вход ключей 5, 4 и 8, Тем самым в течение данного цикла преобразования осуществляется, по команде от микроЭВМ 24 преобразование напряжений U, (t) , U,., или DPI

По окончании интервала времени At посредством пятого формирователя 48 четвертьш RS-триггер 50 устанавли- Бается в единичное состояние. Одновременно посредством второго D-триг- гера 56, седьмого 57 и восьмого 58 логических элементов И и элемента 59 осуществляется подача напряжений логической единицы на управляющий вход второго 4 или третьего 7 ключа соответственно при единичном или нулевом состоянии выхода компаратора 20 по окончании интервала времени дй (т.е. соответственно при отрицательном или положительном выходном напряжении интегратора 18 по окончании интервала времени . Тем самым обеспечиваются условия разряда инте- rpteTopa 18 при преобразовании среднего значения. После фиксации компаратором 20 равенства нулю выходного напряжения интегратора 18 четвертый RS-триггер 50 сбрасывается выходным импульсом шестого 46 или седьмого 47 фop JИpoвaтeля коротких импульсов (в зависимости от того, было ли вы-.

ходиое напряжь: пне ин гегратс р; 18 по окончании интервала времени ut положительным или отрицательным . При этом на один из входов второго элемента И 49 (через который импульсы сброса поступают на вход R RS- тригтера 50) поступает выходной импульс первого формирователя 30. Это обеспечивает сброс RS-триггера 50 в начале каждого цикла преобразования, что устраняет влияние сбоев (например , по включении питания) на дальнейшую работу устройства.

Выходное напряжение RS-триггера 50, который, таким образом, находится в единичном состоя гаи от конца интервала времени ufc, до момента фик компаратором 20 равенства нулю выходного напряжения интегратора 18, поступает на управляющий вход усилителя 1 7 , на второй вход преобразователя 23 и на четвертый вход микроЭВМ 24 .

По сбросу RS-триггера 50 из единичного состояния в нулевое первый RS-триггер 54 устанавливается в единичное состояние посредством восьмого формирователя 51, третьего инвертора 52, а такие второго элемента И-НЕ 53, который введен для устранения возможнос ти одновременного прихода импульсов на входы S и R первого RS- триггера 54 (что может иметь место по включении питания). По окончании цикла преобразования RS-триггер 54 сбрасывается. При этом с помощью третьего элемента И-НЕ 55 осуществля ется формирование управляющих напряжений для ключа 6, блоков 10 и 19.

Посредством микроЭВМ 24 в данном устройстве выполняется формирование весовой функции jj(t) , вычисление окончательного результата преобразования а также управление подключением к первому входу усилителя 9 одного из тре напряжений (преобразуемого напряжения Ujj(t), первого UQ или второго и опорных напряжений) в течение соответствующего интервала времени ut, . Основу микроэвм 24 составляют блок 63, центральный процёС - сор 64 и ПЗУ микрокоманд 61. Блок 63 микропрограммного управления, например, реализованный на микросхеме К589 ИК01, выполняет функции управления последовательностью выбора микрокоманд из ПЗУ 61. При этом могут осуществляться условные переходы в зависимости от состояния объединенных

17

третьего и четвертого выходов центрального процессора 64, второго, третьего и четвертого входов микро- ЭВМ 24. Эти состояния анализируются блоком 63, поступая на его пятьй вход через управляемый программно (посредством ПЗУ микрокоманд 61) (мультиплексор 65.

Центральный процессор .шолнен-- ный, например, на центральных процессорных элементах К589 ИК02 осуществляет, в соответствии с кодом на его четвертых зходах, запись данных с первых входов микроэвм 24 или из ПЗУ 66 арифметические и логические операи;ии над данными, хранение промежуточных результатов преобразований в его регистрах, выдачу окончательных результатов преобразований на информационные выходы микроэвм 24,.а также адре- сагщю ПЗУ 66 .

Рабочая программа микроЭВМ 24 хранится в ПЗУ 61. Код микрокоманды снимается с выходов ПЗУ 61. При этом микрокоманда содержит стандартное поле (разряды с 0-го по 17-й) и поле пользования - остальные разряды, посредством которых осуществляют логические функции, необходимые в данном варианте построения и использования микроэвм 24: функции маскирования, управления внешним - устройствами, определения стариих г+1 разрядов адреса следующей микрокоманды и управления мультиплексором 65. Адресация ПЗУ 61 осуществляется посредством блока 63 и регистра 62.

В ПЗУ 66 хранятся коды, обеспечивающие соответствую1цие значения k коэ(})фицнента деления управляемого делителя 12 напряжения, а также значения и,, ,-и„„ Uo , иД-ЦД . Генератор 60 осуществляет синхронизащ1ю работы микроэвм 24.

12

Формула изобретения

Н/:(1Я, KI 1Т(1П1 Г() объСДИНРГ г- Г1У.ч.ПМ

--, -

20

233283{

функционального преобразователя на- ггряжения и соединен с выходом первого усилителя, второй вход блока коррекции нуля является общей щиной, , третий вход соединен с вторым выходом блока управления, интегратор, первый и второй входы которого соединены соответственно с первым и вторым выходами блока разряда инте- 1Q гратора, вход которого соединен

с третьим выходом блока управления, компаратор, первый вход которого является общей шиной, а выход соединен с первым входом блока управления, генератор импульсов, выход которого соединен с первым входом преобразователя время - код, отличающийся, тем, что, с целью расширения области применения за счет обеспечения преобразования напряжения сложной формы, в него введены со второго по пятый ключи, второй и третий источники опорного напряжения, второй усилит.ель, управляе- 22 мый делитель напряжения, повторитель напряжения, второй и третий регистры, инвертор, микроэвм, первые входы которой соединены с соответствующими выходами преобразователя время- код, второй, третий и четвертый входы - соответственно с четвертым, пятым и щестым выходами блока управления,, первый, второй и третий управляющие выходы - соответственно с вторым, третьим и четвертым входами блока управления, четвертый и пятый управляюидие выходы - соответственно с управляющими входами второго и первого Е)егистров, информационные входы первого и второго регистров поразрядно объединены и соединены с соответствующими информационными вьгходами iикpoЭBM, выходы первого регистра являются выходными iinsHaNfii, выходы второго регистра соединены с соответстнуюгцими входами третьего регистра, управляющий вход которого соединен с седьмым выходом блока управления, а выходы третьего регистра соединены соответственно с поразрядно объединенными входами инвертора и первыми входами управляемого делителя напряжения, вторые входы которого соединены с соответствующими иьгходами инвертора, третий вход упраи- 55 .- яемого делителя напряжения соединен с выходом фyнкциoч -Jльнoгo преобразователя наиряжвкня, н пых(1Д через ппследонатр. Пзнп г ое-гичг: ипыо nnnTnpii30

35

40

45

50

тель напряжения и второй усилитель соединен с третьим входом интегратора, выход которого соединен с 1зторым входом компаратора, первый вход первого усилителя соединен с объединен- ными выходами с второго по пятый ключей, входы которых соединены соответственно с выходами первого, второго и третьего источников опорного напряжения и общей шиной, а управляюн1ие входы с второго по пятый ключей и второго усилителя соединены соответственно с восьмого по дбенадцатый выходами блока управления, тринадцатый и четьфнадцатьп выходы которого сое- динены соответственно с вторым и третьим входами преобразователя время - код.

45

50

первого элемента И соединен с выходом третьего формирователя коротх их импульсов, а выход первого элемента И соединен с объединенными R-входами второго и третьего RS-триггеров, S-вход второго RS-триггера объединен с S-входом первого D-триггера И сое- Д1|нен с выходом второго формирователя коротких импульсов, прямой выход второго RS-триггера соединен с первым входом третьего элемента И, второй вход которого объединен со вторыми входами первого и третьего элементов И-НЕ, соединен с инверсным выходом первого D-триггера и является

ю 15 205 .

5

0

5

0

пятым выходом олока yiipaBJu-iiiiM, тро-- тий вход третьего элемента И оСп.е.ци йен с С-входом первого D-триггегч и соединен с выходом второго генератора импульсов, выход третьего элемента И соединен со счетным входом счетчика импульсов и является седьмым выходом блока управления, группа выходов счетчика импульсов соединена соответственно с первыми входами блока сравнения, вторые входы которого являются шинами установки опорного кода, первый выход группы выходов счетчика импульсов через четвертый формирователь коротких импульсов соединен с S-входом третьего RS-триггера, прямой выход которого соединен с третьим входом первого элемента И-НЕ, четвертый вход которого объединен с третьим входом третьего элемента И-НЕ и соединен с инверсным выходом первого RS-триггера, выход первого элемента И-НЕ соединен с объединенными входами первого инвертора, пятого формирователя коротких импульсов и С-входом второго D-триггера, выход первого инвертора соединен с объединенными первыми входами четвертого, пятого и шестого элементов И, вторые которых являются соответственно вторым, третьим и ч етвертым входами блока управления, выход четвертого элемента И является первым выходом блока управления, выход пятого элемента И соединен с первым входом элемента Ш1И, выход шестого элемента И является десятым выходом блока управления, второй вход элемента ИЛИ соединен с выходом седьмого элемента И, а выход элемента ИЛИ является восьмым выходом блока управления, первый вход седьмого элемента И объединен с первым входом восьмого элемента И, соединен с прямым выходом четвертого RS-триггера и является шестым, двенадцатым и тринадцатым выходами блока управления, второй вход седьмого элемента И соединен с прямым выходом второго D-триггера, инверсный выход которого соединен с вторым входом восьмого элемента И, D-вход второго D-триггера объединен с входом второго инвертора и шестого формирователя коротких импульсов и является первым входом блока управления, выход восьмого элемента И является девятым выходом блока управления, выход второго инвертора через седьмой формирователь коротких импульсов соединен с втophl t входом второго элемента И, третий вход которого соединен с выходом шестого формирователя коротких импульсов, а выход второго элемента Н соединен с R-BXO- дом четвертого КЗ-триггерл, S-вход которого соединен с выходом пятого формирователя коротких имлульсов, инверсный выход четвертого RS-триг- гера через последовательно соединен- ные восьмой формирователь коротких импульсов и третий инвертор соединен с вторым входом второго элемента И-НЕ, выход которого соединен с S-BXO- дом первого RS-триггера, выход блока сравнения соединен с входом третьего фор№1рователя коротких импульсов, D-вход первого D-триггера является общей тиной, а выход третьего элемента - соответственно вторым, третьим и одиннадцатым выходами блока управления.

t/2

и.

.

tJ3 ищ

% 16

u

Uj7

(/M

UK

W2/

Фиг.г

Фиг.

Ив Ug U,g U24 Uzs

J ifrU

Uze (J(26-tn}

fs Я Ss

iJ( U(2g42n })

tj tst iltj t t f;;t;2fjj tя tjy

.

Составитель А.Титов Редактор А.Сабо Техред О.Сопко Корректор С.Черни

---- - -- - --- . .« .,.««B.M.«.V,V.

Заказ 2782/57 Тираж 816Подписное

ВНРПШИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

| Справочник по нелинейным схемам | |||

| /Под ред | |||

| Д.Шейнгольда | |||

| М.: Мир, 1977, с | |||

| Способ обработки медных солей нафтеновых кислот | 1923 |

|

SU30A1 |

| Способ измерения действующего значения переменного напряжения | 1983 |

|

SU1140054A2 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1986-05-23—Публикация

1984-11-27—Подача