Изобретение относится к вычислительной технике и может быть использовано при построении специализированных ЭВМ для цифровой обработки сигналов.

Целью изобретения является повышение производительности.

Сравнительный анзгиз прототипа и заявляемого устройстиз показывает, что заявляемое устройство за счет новой организации вычислительного процесса, обеспечиваемой дополнительными линейками процессорных элементов с предложенной конфигурацией связей, имеет производительность о L раза выше, чем прототип,

Неизвестно использование такой совокупности отличительных признаков в других

источниках, следовательно, заявляемое техническое решение соответствует критерию существенные отличия.

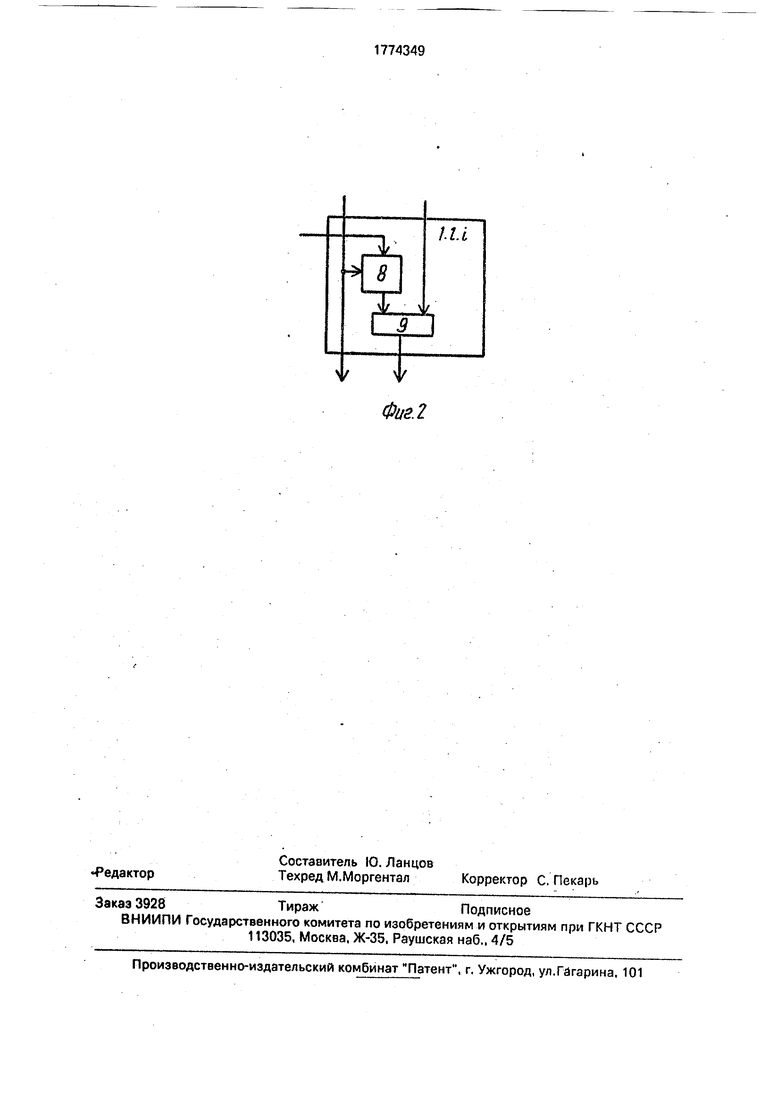

На фиг. 1 изображена структурная схема предлагаемого устройства; на фиг. 2 - структура процессорного элемента. В табл. 1, 2, 3, 4 приведены первые десять тактов работы устройства.

Устройство содержит L групп по К про- цессорных элементов 1.N.t(,K. ,L, где К - количество коэффициентов импульсной характеристики), группу регистров 2.N.t, 2.N.I.J (. .... L, , 2); группу регистров S.N.t, выходы 4.1-4.L, блок 5 ввода, вход 6, группу регистров 7.1-7.L. Процессорный элемент 1.N.I (фиг. 2) состоит из умножителя 8 и сумматора 9. Блок 5 ввода содержит

VI

VI

4 CJ -N О

группу последовательно соединенных регистров 10.1...10.L, генератор 11 тактовых импульсов, счетчик 12 и дешифратор 13.

Рассмотрим работу устройства для случая , . Правило формирования выходных отсчетов у(п) имеет вид y(n)a(1)x(n)-t-a(2)x(n-1)-K..+a(t)x(n-t-1)+... ... + a(K)x(n-k+1).

где К - число весовых коэффициентов фильтра;

a(i) - весовые коэффициенты;

Х0). У(°) отсчеты на входе и выходе устройства соответственно (j-n+1,2,3,...).

Для случая полный выходной отсчет имеет вид y(n)a(1)x(n)+a(2)x(n-1)+a(3)x(n-2)+a(4)x(n-2).

8 начале работы устройства на его вход поступает L нулевых отсчетов.

В первые К микротактов в цепочку регистров 10.1...10.Кблока 5 сопряжения последовательно записываются К входных отсчетов. В начале такта информация с выхода блока сопряжения зафиксирована в соответствующих регистрах 7.1...7.К первой группы, причем х(1) записан в регистр 7.1. х(2) - в регистр 7.3 и х(3) - в регистр 7.2. К началу второго такта в этих регистрах зафиксированы соответственно входные отсчеты х(4), х(6), х(5), в третьем такте - соответственно х(7), х(9), х(8) и т.п.

К началу работы устройства на третьи информационные входы процессорных элементов 1.1.t, 1.2.t I.L.t поступает коэффициент a(t) импульсной характеристики ().

К концу первого такта с первого выхода процессорного элемента 1.1.1 на вход регистра 2.1.1 поступает входной отсчет х(1), а с второго выхода на вход регистра 3.1.1 поступает у(1)а(1)х(1). К концу второго такта с первого выхода процессорного элемента 1.1.1 на вход регистра 2.1.1 поступает входной отсчет х(4), а с второго выхода на вход регистра 3.1.1 поступает результат у (4Н(1)х(4).

К концу первого такта с первого выхода процессорного элемента 1.2.1 на вход регистра 2.2.1.1 поступает входной отсчет х{3), а с второго выхода процессорного элемента 1.2.1 на вход регистра 3.2.1 поступает результат у (3)а(1)х(3). К концу второго такта с первого выхода процессорного элемента 1.2.1 на вход регистра 2.2.1.1 поступает входной отсчет х(б), а с его выхода на вход регистра 2.2.1.2 поступает входной отсчет х(3). С второго выхода процессорного элемента 1.2.1 на вход регистра 3.2.1 поступает результат у (6)а(1)х(6).

В конце первого такта с первого выхода процессорного элемента 1.3.1 на вход регистра 2.3.1 поступает входной отсчет х(2), а с второго выхода процессорного элемента 1.3.1 на вход регистра 3.3.1 поступает результат вычисления у (2)э(1)х(2). К концу

второго такта с первого выхода процессорного элемента 1.3.1 на вход регистра 2.3.1 поступает входной отсчет х(5), а с второго выхода процессорного элемента 1.3.1 на вход регистра 3.3.1 поступает результат

0 у (5)а(1)х(5).

К концу второго такта с первого выхода процессорного элемента 1.1.2 на вход регистра 2.1.2 поступает ноль, а с второго выхода процессорного элемента 1.1.2 на вход

5 регистра 3.1.2 поступает у(1). К концу третьего такта с первого выхода процессорного элемента 1.1.2 на вход регистра 2.1.2 поступает входной отсчет х(3), а с второго выхода процессорного элемента 1.1.2 на

0 вход регистра 3.1.2 поступает результат у(4)у (4)+а(2МЗ).

К концу второго такта с первого выхода процессорного элемента 1.2.2 на вход регистра 2.2.2 поступает нуль входной отсчет х(1), а с

5 второго выхода процессорного элемента 1.2.2 на вход регистра 3.2.2 поступает результат вычисления у(2Н ((2)х(1)а(1)х(2)+а(2)х(1). К концу третьего такта с первого выхода процессорного элемента 1.2,2 на вход регистра

0 2.2.2 поступает входной отсчет х(4), а с второго выхода процессорного элемента 1.2.2 на вход регистра 3.2.2 поступает результат у(5)у (5)а(2)х(4).

К концу второго такта с первого выхода

5 процессорного элемента 1.3.2 на вход регистра 2.3.2.1 поступает нуль входной отсчет х(2), а с второго выхода процессорного элемента 1.3.2 на вход регистра 3.3.2 поступает результат вычисления у(3)у (3)+а(2)х(2). К

0 концу третьего такта с выхода процессорного элемента 1.3.2 на вход регистра 2.3.2.1 поступает входной отсчет х(5), а с его выхода на вход регистра 2.3.2.2 поступает входной отсчет х(5). С второго выхода процессорного

5 элемента 1.3.2 на вход регистра 3.3.2 поступает результат у(6)у(6)+а(2)х(5).

К концу третьего такта с первого выхода процессорного элемента 1.1.3 на вход регистра 2.1.3 поступает ноль, а с второго выхо0 да процессорного элемента 1.1.3 на вход регистра 3.1.3 поступает у(2). К концу четвертого такта с первого выхода процессорного элемента 1.1.3 на вход регистра 2.1.3 поступает входной отсчет х(3), а с второго

5 выхода процессорного элемента 1.1.3 на вход регистра 3.1.3 поступает результат У (4)у(4)+а(3)х(3).

К концу третьего такта с первого выхода процессорного элемента 1.2.3 на вход регистра 2.2.3 поступает ноль, а с второго выхода процессорного элемента 1.23 на вход регистра 3.2.3 поступает результат вычисления у(3). К концу четвертого такта с первого выхода процессорного элемента 1 2.3 на вход регистра 2.2.3 поступает входной от- счет х(2). а с второго выхода процессорного элемента 1.2.3 на вход регистра 3.2.3 поступает результат у (4)у(4)+а(3)х(2).

К концу третьего такта с первою выхода процессорного элемента 1.3.3 на вход реги- стра 2.3.3.1 поступает входной отсчет х(1), а с второго выхода процессорного элемента 1.3.3 на пход регистра 3.3.3 поступает результат вычисления у(3)у(3)+а(3)х1. К концу четвертого такта с первого выхода процессорного элемента 1.3.3 на вход регистра 2.3.3.1 поступает входной отсчет х(4), а с его выхода на вход решстра 2.3.3.2 по- ступа ет входной отсчет х(1). С второго выхода процессорного элемента 1.3.3 на вход регистра 3.3.3 поступает результат y-(6H Wa(3)x(4).

К концу четвертого гакта на выходах 4.1, 4.2, 4.3 устройства зафиксированы соответственно выходные отсчеты у(2) у(1).у(3).

К концу пятого тзктя на выходах 4.1,4 2, 4.3 устройства зафиксированы соответственно выходные отсчеты у(5), у(4), у(6).

Вычисление последующих отсчетов производится аналогично. Первые десять тактов работы устройства приведены в табл, 1, 2, 3,4.

Формула изобретен и я

1. Цифровой нерекурсивный фильтр, содержащий первую группу из К процессор- ных элементов (где К - количество коэффициентов импульсной характеристики), первую группу регистров, блок ввода, причем процессорный элемент состоит из умножителя и сумматора, причем первый информационный вход процессорного элемента является первым его выходом и подключен к первому входу умножителя, второй информационный вход процессорного элемента подключен к второму входу умножителя, выход которого подключен к первому иходу сумматора, второй вход которого является третьим информационным входом процессорного элемента, выход сумматора является вторым выходом про- цессорного элемента, выход сумматора является вторым выходом процессорного элемента, отличающийся тем, что, с целью повышения производительности в него введено (L-1) групп из К процессорных элементов и две группы регистров, причем

1-й ( . L) информационный выход блока ввода соединен с информационным входом 1-го регистра первой группы, выход которого соединен с первым информационным входом первого процессорного элемента 1-й группы, первый выход 1-го процессорного элемента (...K) N-й группы соединен либо через один регистр второй группы, если mod Ы 1 при (г-1) t rL.r- ном. или modL при (r-1)L k rL, г - четном, либо через два последовательно соединенных регистра второй группы, если mod L-i-1 npn(r-1)L t rL, i - нечетном, или mod L при (r-1)L , r-четном, с первым информационным входом (КН)-го процессорного элемента h-й группы (где при . если t - четное или , если (t+L) - четное; при () - четном; при (t+N) - нечетном), второй выход t-ro процессорного элемента j-й группы соединен через регистр третьей группы со вторым информационным входом (t+1)-ro процессорного элемента S-й группы (i де при , если т - нечетное или , если (t+L) - нечетное; при (t+j) - нечетное; при (t-t-j)-четном, выход К-го процессорного элемента 1-й группы является i-м выходом устройства, вход блока сопряжения является входом устройства, выход тактовых сигналов блока ввода подключен соответственно к тактовым входам регистров, вторые информационные входы t-x процессорных элементов (...K) каждой группы объединены и являются входами загрузки коэффициентов цифрового нерекурсивного фильтра.

2. Устройство по п. 1, отличающее- с я тем, что блок сопряжения содержит группу последовательно соединенных регистров, генератор тактовых импульсов, счетчик и дешифратор, причем информационный вход первого регистра группы является входом блока ввода, а выход i-ro регистра группы (... P-1, P L/2+1, если P(L+1)/2, если L 2r+1; r- целое положительное число) является соответственно 21-м выходом блока ввода, выход j-ro регистра группы (...L) является (2(L-j)+1)-M информационным выходом бло.а ввода, выход генератора тактовых импульсов подключен к тактовому входу счетчика, выход которого соединен со входом дешифратора, выход которого является тактовым выходом блока ввода, тактовые входы группы регистров объединены и подключены к выходу генератора тактовых импульсов.

+а(2)х(1)

3 ) у(4)у (4) х(4) у(5)у(5) х(5) +а(2)х(3)+а(2) х(4)

у(7)у (7) +а(2)х(6)

х(7)

)у (10) х(10) +а(2)х(9)

у(13)у (13) х(13) (2)х(12)

у(16)у (16) Х(16) +а(2)х(15)

у(19)у (19) х(19) +а(2)х(18)

у(8)у(3) х(0) +а(2)х(7)

у(11)у (11) х(11) +a(2)ix(10)

у«(14)у(14) х(14) +а(2)х(13)

у(17)у(17) х(17) +а(2)х(16)

у(20)у(20) х(20) +а(2)«.х(19)

+а(2)жх(2) у(6)у (6) ((5)

у(9)уЧ9) +а(2)х(8)

у(12)У (12) +а(2)х(11)

у(15)у (15) +а(2)х(14)

у(18)у (18) +а(2)х(17)

y(21)y (2t) ,а(2)х(20)

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ПЕРЕМНОЖЕНИЯ МАТРИЦ | 1990 |

|

RU2006937C1 |

| Устройство для умножения матриц | 1991 |

|

SU1835548A1 |

| Устройство для операций над матрицами | 1988 |

|

SU1575205A1 |

| Коррелятор | 1985 |

|

SU1381539A1 |

| Устройство для операций над матрицами | 1990 |

|

SU1802363A1 |

| СПОСОБ ПЕРЕДАЧИ ИНФОРМАЦИИ НА ОСНОВЕ ХАОТИЧЕСКИ ФОРМИРУЕМЫХ АНСАМБЛЕЙ ДИСКРЕТНЫХ МНОГОУРОВНЕВЫХ ОРТОГОНАЛЬНЫХ СИГНАЛОВ | 2010 |

|

RU2428795C1 |

| Устройство для LL @ -разложения симметричных матриц | 1987 |

|

SU1520542A1 |

| ТЕСТЕР УРОВНЯ ИННОВАЦИОННОГО ИНТЕЛЛЕКТА ЛИЧНОСТИ | 2013 |

|

RU2522992C1 |

| Устройство для LU-разложения матриц | 1986 |

|

SU1401478A1 |

| Генератор функций Попенко-Турко | 1990 |

|

SU1753464A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении специализированных ЭВМ для цифровой обработки сигналов. Целью изобретения является повышение производительности за счет увеличения частоты поступления входных отсчетов. Для этого цифровой нерекурсивный фильтр содержит L групп из К процессорных элементов (К - количество коэффициентов импульсной характеристики), блок ввода и три группы регистров. Предлагаемый фильтр за счет новой организации вычислительного процесса, обеспечиваемой дополнительными линейками процессорных элементов с предложенной конфигурацией связей, имеет производительность в L раз выше, чем прототип. 1 з.п. ф-лы, 4 табл., 2 ил. у Ё

ТаблицаЗ

ф4

(Риг.1

Таблица

W.2

i t.J

Фае. 2

| Плакс Т | |||

| Систолические структуры одномерной свертки | |||

| Тезисы доклада, 1-я Всесоюзная конференция Однородные вычислительные среды и систолические структуры, т | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Счетный сектор | 1919 |

|

SU107A1 |

| Многооборотный переменный резистор | 1983 |

|

SU1314392A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-11-07—Публикация

1990-12-05—Подача