равляются при помощи генератора тактовых импульсов и счетчика 2.

Недостатком известного устройства является то, что его реализация требует больших аппаратурных затрат.

Целью изобретения является снижение аппаратурных затрат.

Поставленная цель достигается тем, что в устройство для вычисления БПФ, содержащее генератор тактовых импульсов, счетчик, умножитель, первый блок постоянной памяти, блоки входной и выходной буферной памяти, введены второй, третий и четвертый блоки постоянной памяти, первая группа из (А-1)/2 вычислительных модулей первого типа, каждый из которых состоит из двух сумматоров, двух буферных регистров, проходного регистра, регистра результата и триггера, первый вычислительный модуль второго типа, который состоит из сумматора и буферного регистра, вторая группа из (В-1)/2 вычислительных модулей третьего типа, каждый из которых состоит из группы проходных регистров, содержащей А регистров, трех (за исключением 1-го вычислительного модуля, который содержит две группы) групп буферных регистров, каждая из которых содержит по А регистров, двух коммутаторов, триггера, двух сумматоров, первый вычислительный модуль четвертого типа, который состоит из триггера, сумматора, коммутатора и группы буферных регистров, содержащей А регистров, вторая группа (В-1)/2 вычислительных модулей третьего типа, полностью аналогичная первой, второй вычислительный модуль четвертого типа, аналогичный первому, вторая группа (А-1)/2 вычислительных модулей первого типа, полностью аналогичная первой, второй вычислительный модуль второго типа, аналогичный первому, выход генератора тактовых импульсов соединен с шиной синхронизации и со счетным входом счетчика, выход которого соединен с адресными входами первого-четвертого блоков постоянной памяти, входного и выходного блоков буферной памяти, 2(А+В) двухразрядных выходов второго блока постоянной памяти соединены соответственно с управляющими входами всех сумматоров, имеющихся в вычислительном устройстве, В+1 выходов третьего блока постоянной памяти соединены соответственно с синхровхода- ми триггеров в первой и второй группах вычислительных модулей третьего типа и в первом и втором вычислительных модулях четвертого типа, в первой и второй группах вычислительных мод/лей первого типа вход и выход проходного регистра соединены с входами первого и второго буферных регистров соответственно, выходы которых соединены с входами сумматора, выход которого соединен с первым входом сумматора результата, выход которого соединен с

входом регистра результата, вход триггера соединен с синхровходами буферных регистров, синхровходы триггера, проходного регистра, регистра результата соединены с шиной синхронизации, выход проходного

0 регистра i-ro(l 1, (А-1)/2-1) вычислительного модуля соединен с входом проходного регистра (i-M)-ro вычислительного модуля, вход триггера 1-го (I 1, (А-1)/2-1) вычислительного модуля соединен с выхо5 дом триггера (i+1)-ro вычислительного модуля, второй вход сумматора результата 1-го (i 1, (А-1)/2-1) вычислительного модуля соединен с выходом регистра результата (1+1)-го вычислительного модуля, выход

0 проходного регистра (А-1)/2-го вычислительного модуля соединен с входом регистра первого (второго) модуля второго типа, выход которого соединен с первым входом сумматора этого вычислительного модуля,

5 выход которого соединен с вторым входом сумматора результата (А-1)/2-го вычислительного модуля, синхровход регистра первого и второго вычислительных модулей второго типа соединен с шиной синхрониза0 ции, второй вход сумматора первого и второго вычислительных модулей второго типа соединен с нулевой шиной, вход проходного регистра первого вычислительного модуля является информационным входом

5 группы вычислительных модулей первого типа, выход регистра результата первого вычислительного модуля является информационным выходом всей группы вычислительных модулей, в первой группе

0 вычислительных модулей первого типа информационный вход соединен с выходом входного блока буферной памяти, вход которого является информационным входом всего устройства, информационный выход

5 соединен с информационным входом первой группы вычислительных модулей третьего типа, вход триггера (А-1)/2-го вычислительного модуля соединен с первым выходом первого блока постоянной памяти,

0 во второй группе вычислительных модулей первого типа информационный вход соединен с информационным выходом второй группы вычислительных модулей третьего типа, вход триггера (А-1)/2-го вычислитель5 ного модуля соединен с четвертым выходом первого блока постоянной памяти, информационный выход соединен с входом выходного блока буферной памяти, выход которого является информационным выходом всего устройства, в первой и второй

группах вычислительных модулей третьего типа вход первого регистра проходных регистров первого вычислительного модуля является информационным входом всей группы вычислительных модулей, выход сумматора результата первого вычислительного модуля является информационным выходом всей группы вычислительных модулей, во всех группах регистров выход i-ro ( ,А-1) регистра соединен с входом (+1)-го регистра, вход и выход группы проходных регистров соединен соответственно с первыми входами первого и второго коммутаторов, вторые входы которых соединены с выходами первой и второй групп буферных регистров соответственно, входы которых соединены с выходами первого и второго коммутаторбв соответственно, выходы которых соединены с входами сумматора, выход которого соединен с первым входом сумматора результата, выход которого (за исключением первого вычислительного модуля) соединен с входом третьей группы буферных регистров, синх- ровходы которых, а также синхровходы всех остальных регистров соединены с шиной синхронизации, управляющие входы коммутаторов соединены с входом триггера, выход группы проходных регистров 1-го (i 1,(В-1)/2-1) вычислительного модуля соединен с входом группы проходных регистров (1+1)-го вычислительного модуля, второй вход сумматора результата i-го (i 1,(В-1)/2-1) вычислительного модуля соединен с выходом третьей группы буферных регистров (i-M)-ro вычислительного модуля, вход триггера 1-го (i 1,(B-1)/2-1) вычислительного модуля соединен с выходом триггера (+1}-го вычислительного модуля в первом и втором вычислительных модулях четвертого типа выход i-ro (i 1 ,А-1) регистра группы буферных регистров соединен с входом (i+1)-ro регистра, вход группы буферных регистров соединен с выходом коммутатора, второй вход которого соединен с выходом группы буферных регистров, выход которой соединен с первым входом сумматора, второй вход которого соединен с нулевой шиной, управляющий вход коммутатора соединен с входом триггера, выход которого соединен с входом триггера (В-1)/2-го вычислительного модуля, первый вход коммутатора соединен с выходом группы проходных регистров(В-1)/2-го вычислительного модуля, вь.ход сумматора соединен с вторым входом сумматора результата (В-1)/2-го вычислительного модуля, в первой группе вычислительных модулей третьего типа информационный выход соединен с первым входом умножителя, вход триггера первого вычислительного модуля четвертого типа соединен с третьим выходом первого блока постоянной памяти, во второй группе вычислительных модулей третьего типа информационный вход соединен с выходом умножителя, вход триггера второго вычислительного модуля четвертого типа соединен с четвертым выходом первого блока постоянной памяти, второй вход умножителя соединен с выходом четвертого блока постоянной памяти, все четыре типа вычислительных модулей работают с комплексными операндами.

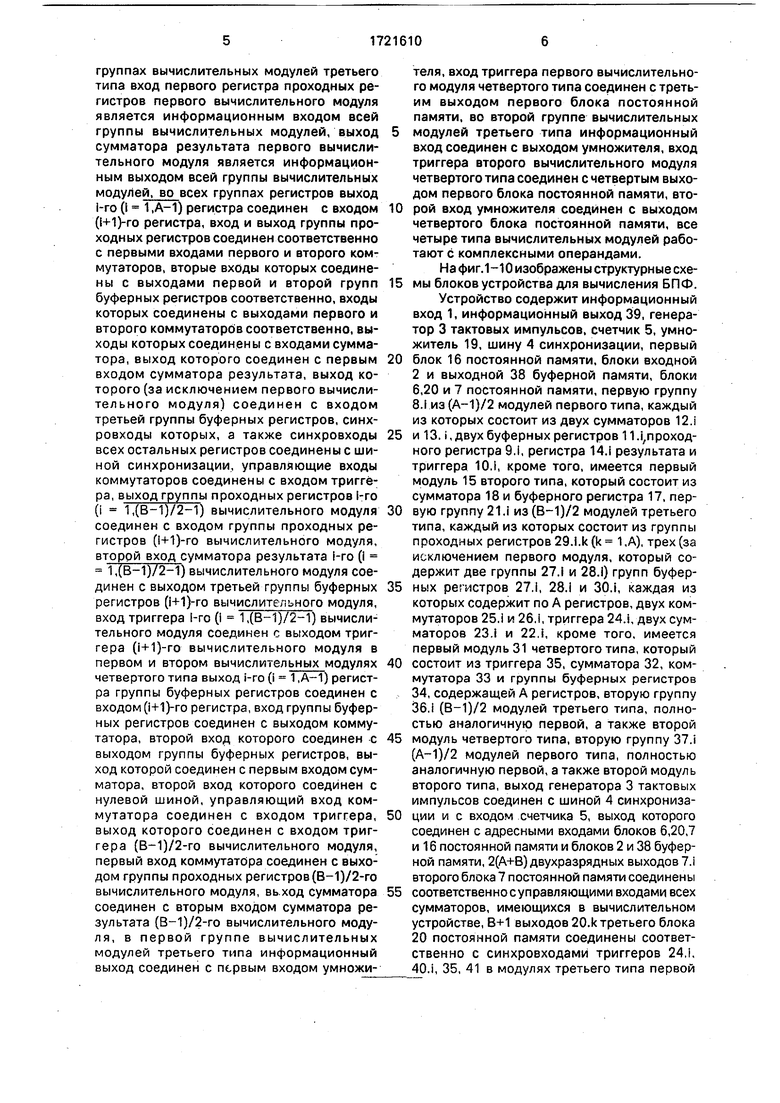

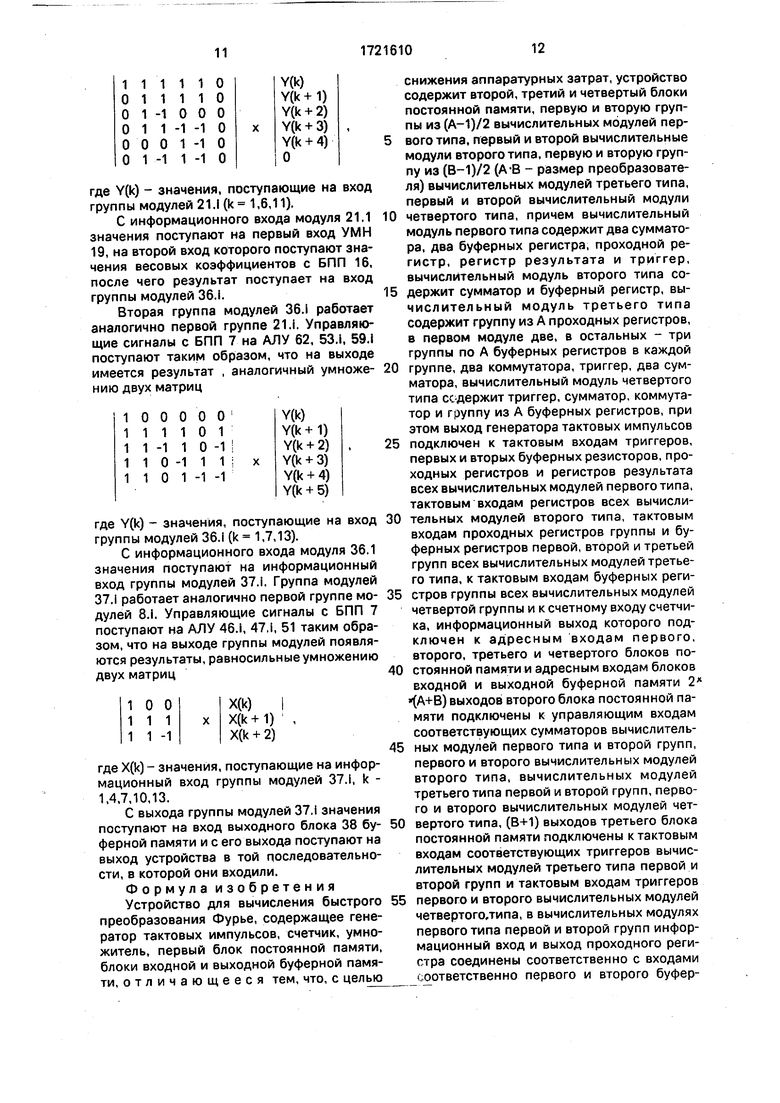

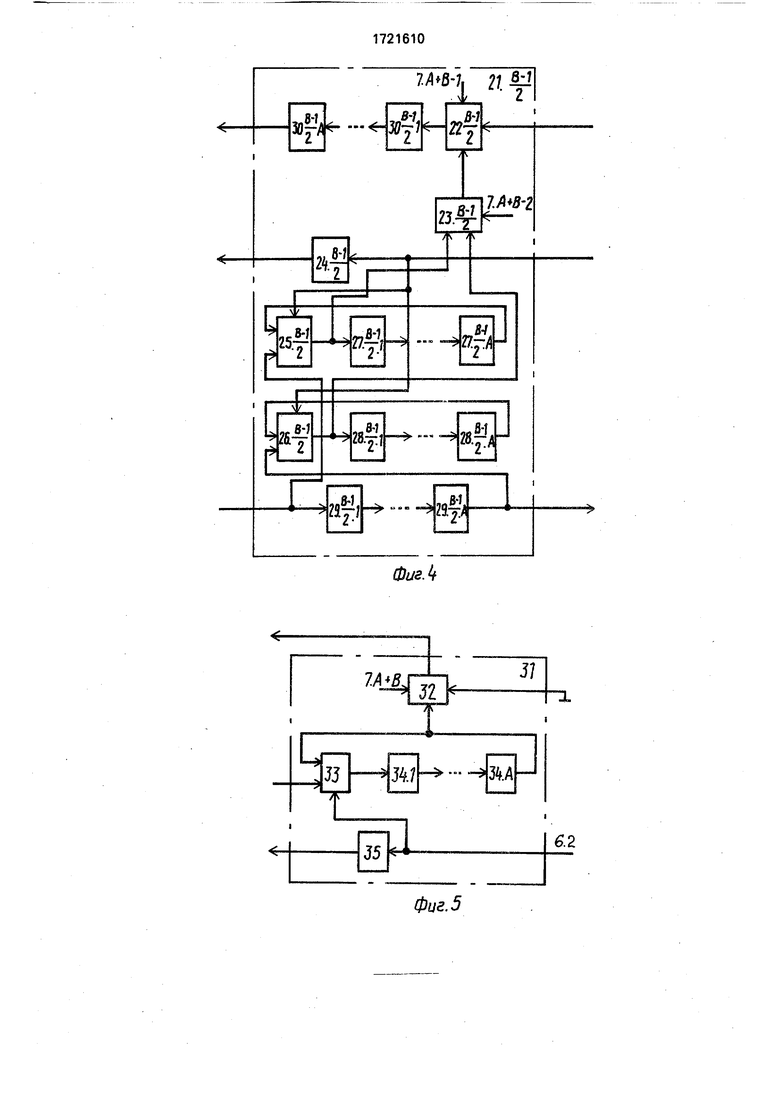

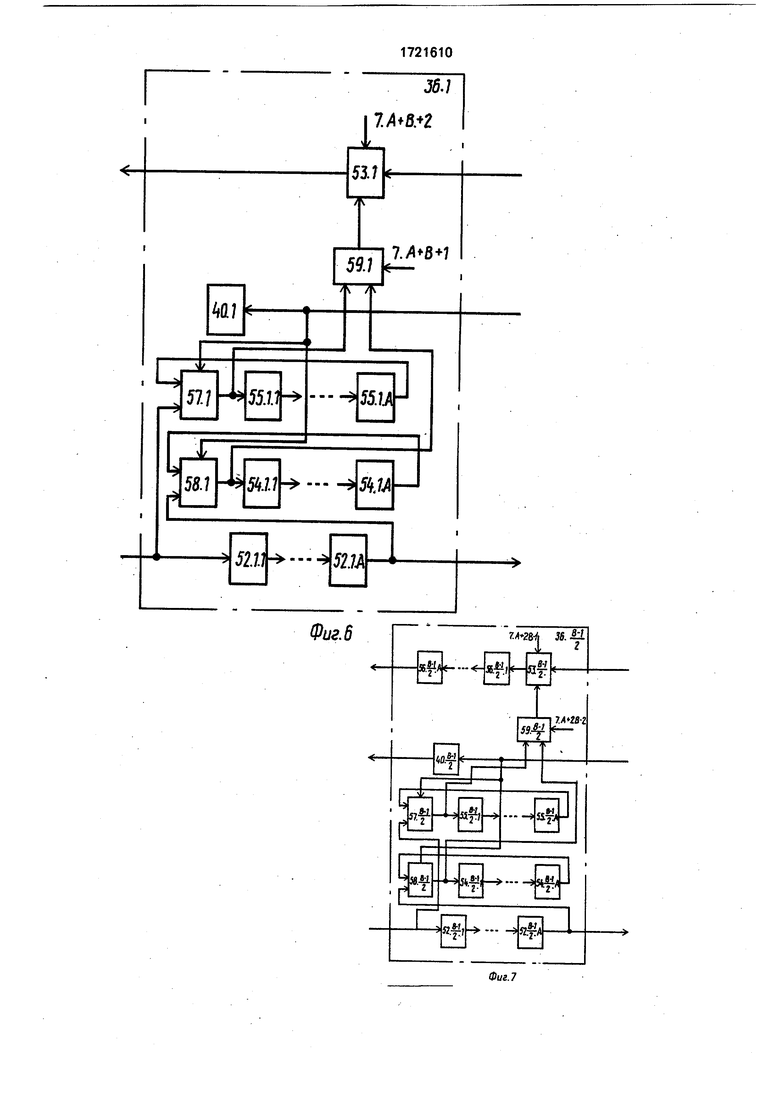

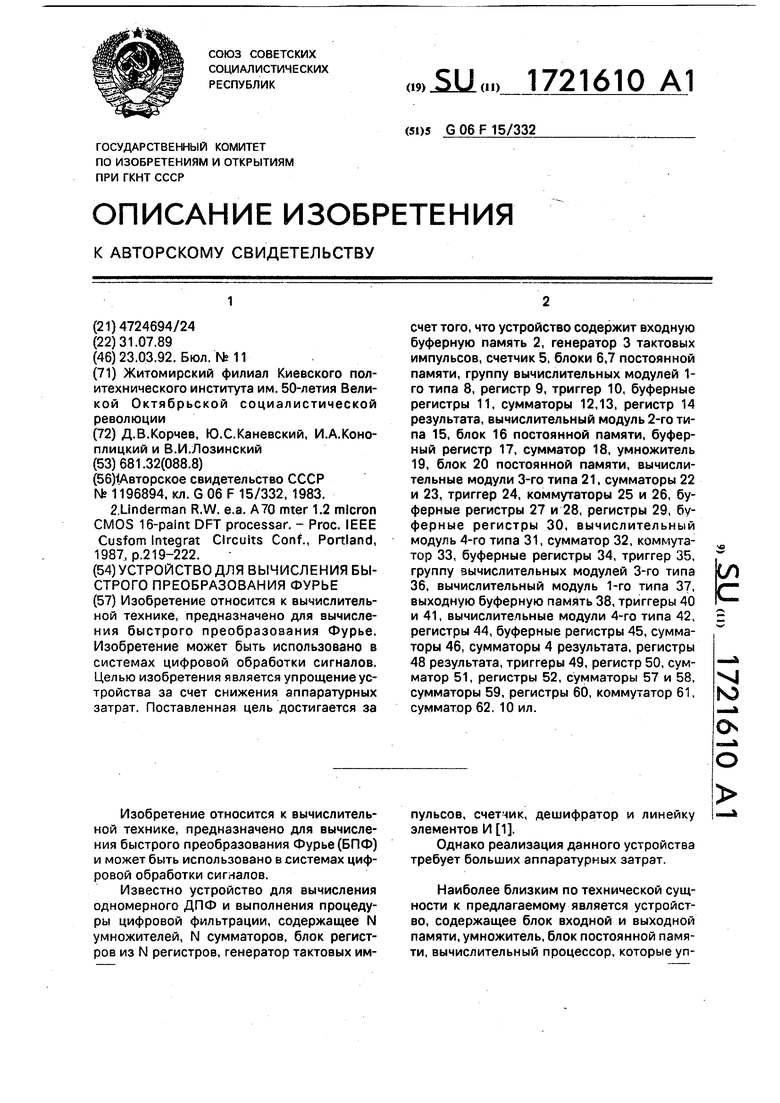

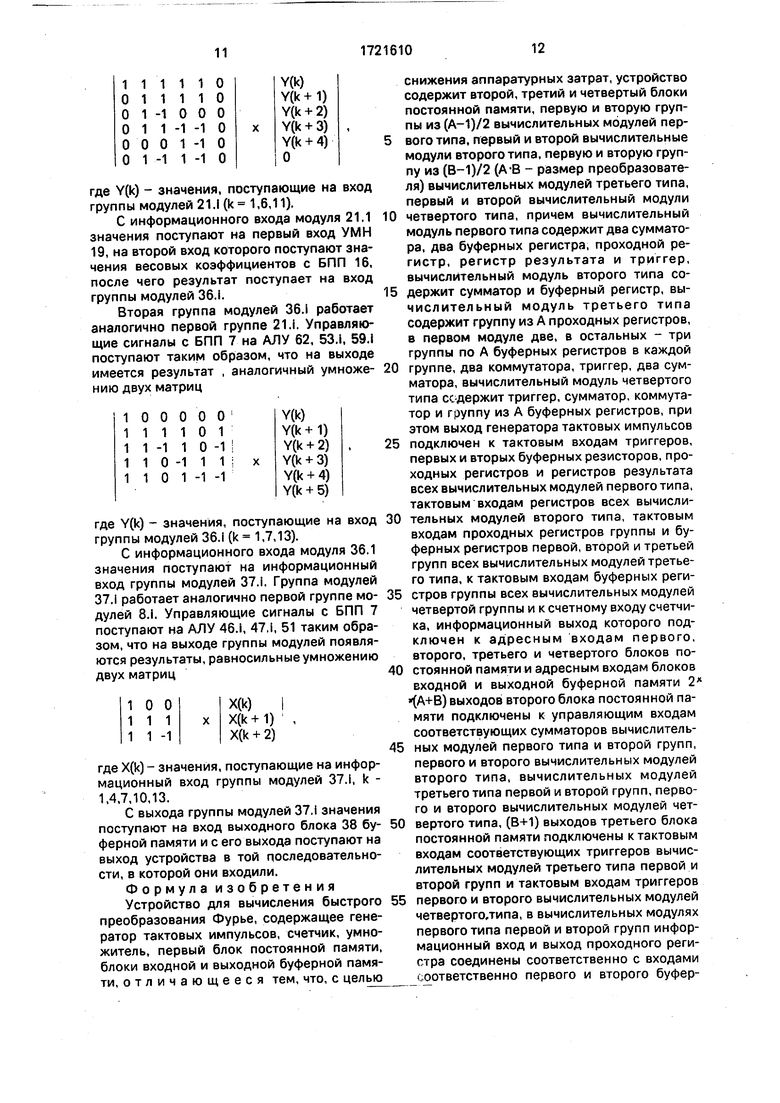

На фиг.1-10 изображены структурные схемы блоков устройства для вычисления БПФ.

Устройство содержит информационный вход 1, информационный выход 39, генератор 3 тактовых импульсов, счетчик 5, умножитель 19, шину 4 синхронизации, первый блок 16 постоянной памяти, блоки входной 2 и выходной 38 буферной памяти, блоки 6,20 и 7 постоянной памяти, первую группу 8.I из (А-1)/2 модулей первого типа, каждый из которых состоит из двух сумматоров 12Л и 13. i, двух буферных регистров 11.проходного регистра 9.I, регистра 14.1 результата и триггера 10.1, кроме того, имеется первый модуль 15 второго типа, который состоит из сумматора 18 и буферного регистра 17, первую группу 21.1 из (В-1)/2 модулей третьего типа, каждый из которых состоит из группы проходных регистров 29.i.k(k 1,A), трех (за исключением первого модуля, который содержит две группы 27. и 28.1) групп буферных регистров 27.i, 28.1 и 30.i, каждая из которых содержит по А регистров, двух коммутаторов 25. и 26., триггера 24.i, двух сумматоров 23. и 22,, кроме того, имеется первый модуль 31 четвертого типа, который состоит из триггера 35, сумматора 32, коммутатора 33 и группы буферных регистров 34, содержащей А регистров, вторую группу 36.i (B-1)/2 модулей третьего типа, полностью аналогичную первой, а также второй модуль четвертого типа, вторую группу 37.1 (А-1)/2 модулей первого типа, полностью аналогичную первой, а также второй модуль второго типа, выход генератора 3 тактовых импульсов соединен с шиной 4 синхронизации и с входом счетчика 5, выход которого соединен с адресными входами блоков 6,20,7 и 16 постоянной памяти и блоков 2 и 38 буферной памяти, 2(А+В) двухразрядных выходов 7. второго блока 7 постоянной памяти соединены соответственносуправляющими входами всех сумматоров, имеющихся в вычислительном устройстве, В+1 выходов 20.k третьего блока 20 постоянной памяти соединены соответственно с синхровходами триггеров 24.i, 40., 35, 41 в модулях третьего типа первой

21.1 и второй 36.1 групп, включая и модули четвертого типа 31 и 42, в первой и второй группах 8.I (37.1) модулей первого типа вход и выход проходного регистра 9.1 (44.1) соединены с входами первого 11.1.1 (45.1.1) и второго 11.1.2 (45.1.2) буферных регистров соответственно, выходы которых соединены с входами сумматора 12.1 (46.1), выход которого соединен с первым входом сумматора 13.1 (47.1) результата, выход которого соединен с входом регистра 14.1 (48.1) результата, вход триггера 10.1 (49.1) соединен с синхровходами буферных регистров 11.1 (45.1), синхровходы триггера 10.1 (49.1), проходного регистра 9.i(44.i), регистра 14.1(48.1) результата соединены с шиной 4 синхронизации, выход проходного регистра 9.I (44 .1) 8,1-го (37.1-го)( 1,(А-1)/2-1) модуля соединен с входом проходного регистра 9.1+1 (44.1+1) (8.1+1)-го (37.1+1-го) модуля, вход триггера 10.1 (49.1) 8.1-го (37.1-го) (1 1,(А- 1)/2-1) модуля соединен с выходом триггера 10.1+1 (49.1+1) (8.1+1)-го (37.i+1-ro) модуля, второй вход сумматора 13.1 (47.1) результата 8.i-ro (37.i-ro) (1 1, (А-1)/2-1) модуля соеди- нен с выходом регистра 14.1+1 (48.1+1) результата (8.1+1)-го (37.1+1-го) модуля, выход проходного регистра 9.1 (44.1) 8.(А-1)/2-го (37.(А-1)/2-го) модуля соединен с входом регистра 17 (50) модуля 15 (43), выход которого соединен с первым входом сумматора 18 (51) этого модуля, выход которого соединен с вторым входом сумматора 13.1 (47.1) результата 8.(А-1)/2-го (37.(А-1)/2-го) модуля, синхровход регистра 17 (50) модуля второго типа соединен с шиной 4 синхронизации, второй вход сумматора 18 (51) модуля 15(43) соединен с нулевой шиной, вход проходного регистра 9.1 (44.1) 8.1-го (37.1-го) модуля является информационным входом всей группы модулей, выход регистра 14.1 (48.1) результата 8.1-го (37.1-го) модуля является информационным выходом всей группы модулей, в первой группе модулей 8.1 информационный вход соединен с выходом входного блока 2 буферной памяти, вход которого является информационным входом 1 всего устройства, информационный выход соединен с информационным входом первой группы 21.1 модулей, вход триггера 10.1 8.(А-1)/2-го модуля соединен с первым выходом 6.1 первого блока 6 постоянной памяти, во второй группе модулей 37.1 информационный вход соединен с информационным выходом второй группы модулей 36.1, вход триггера 49.i 37,(A-1)/2-ro модуля соединен с четвертым выходом 6.4 первого блока 6 постоянной памяти, информационный выход соединен с входом выходного блока 38 буферной памяти, выход которонго

является информационным выходом 39 всего устройства, в первой 21.1 и во второй 36.1 группах модулей вход первого регистра группы проходных регистров 29.1 (52.1) 21.1- го (36.1-го) модуля является информационным входом всей группы модулей, выход сумматора результата 22.i (53.i) 21.1 -го (36.1- го) модуля является информационным выходом всей группы модулей, во всех группах регистров 29.i.k (52.i.k), 28.l.k (54.i.k), 27.i.k (55.i.k), 30.i.k (56.l.k) выход k-ro (k 1,A-1) регистра соединен с входом (k+1)-ro регистра, вход и выход группы проходных регистров 29.i (52.1) соединены соответственно с первыми входами первого 25.i (57.i) и второго 26.1 (58.1) коммутаторов, вторые входы которых соединены с выходами первой 27.i (55.i) и второй 28.i (54.i) групп буферных регистров соответственно, входы которых соединены с выходами первого 25.i (57.i) и второго 26.1 (58.1) коммутаторов соответственно, выходы которых соединены с входами сумматора 23.i (59.i), выход которого соединен с первым входом сумматора 22. (53.1) результата, выход которого (за исключением 21.1-го (36.1-го) модуля) соединен с входом третьей группы буферных регистров 30.i (56.i), синхровходы которых, а также синхровходы всех остальных регистров соединены с шиной 4 синхронизации, управляющие входы коммутаторов 25.i (57.i) и 26.i (58.1) соединены с входом триггера 24.i (40.i), выход группы проходных регистров 29.1 (52.1) 21.1-го (36.i-ro)(i 1,(В-1)/2-1) модуля соединен с входом группы проходных регистров 29.1+1 (52.1+1)(21.1+1)-го(36.1+1-го) модуля, второй вход сумматора 22.1 (53.1) результата 21.1-го (36.1-го) (1 1,(В-1)/2-1) модуля соединен с выходом группы буферных регистров 30.1+1 (56.1+1). (21.1+1)-го (36.1+1-го) модуля, вход триггера 24,i (40.i) 21 .i-ro (36.1-ro) (i 1 ,(B-1)/2-1) модуля соединен с выходом триггера 24,1+1 (40.1+1) (21.1+1)-го(36.1+1-го) модуля, в модуле 31 (42) выход 34.1-го (60.1-го) (1 1.А-1) регистра группы буферных регистров соединен с входом (34.1+1)-го (60,1+1-го) регистра, вход группы буферных регистров 34.i (60,i) соединено с выходом коммутатора 33 (61), второй вход которого соединен с выходом группы буферных регистров 34.i (60.i), выход которой соединен с первым входом сумматора 32 (62), второй вход которого соединен с нулевой шиной, управляющий вход коммутатора соединен с входом триггера 35 (41), выход которого соединен с входом триггера 24. (40.I) 21.(В-1)/2-го (36,(В-1)/2-го) модуля, первый вход коммутатора 33 (61) соединен с выходом группы проходных регистров 29.1 (52.1) 21.(В-1)/2-го (36.(В-1)/2-го) модуля, выход сумматора 32 (62) соединен с вторым входом сумматора результата 22.1 (53.1) 21.(В-1)/2-го (36.(В-1)/2-го) модуля, в группе модулей 21.1 информационный выход соединен с первым входом умножителя 19, вход триггера 35 модуля 31 - с третьим выходом 6.3 первого блока 6 постоянной памяти, в группе модулей 36.1 информационный вход соединен с выходом умножителя 19, вход триггера 41 модуля 42 соединен с чет- вертым выходом 6.4 первого блока 6 постоянной памяти, второй вход умножителя 19 соединен с выходом четвертого блока 16 постоянной памяти, все группы модулей работают с комплексными операндами.

Рассмотрим работу устройства потакт- но. Устройство вычисляет БПФ по алгоритму Винограда с периодом в N отсчетов, где N А х В, где А и В - простые числа. Для определенности полагают, что А 3; В 5. С генератора 3 тактовых импульсов идут синхросигналы типа меандр. Применяются следующие сокращения: РГ - регистр; ТР - триггер; MX - мультиплексор; СТ - счетчик; БПП - блок постоянной памяти; ББП - блок буферной памяти; ВХ - вход; В ЫХ- выход; АЛУ - сумматор; УМН - умножитель; ШС - шина синхронизации.

Рассмотрим работу первой группы модулей 8.I. Допустим, что триггеры 10.1 (49.1), проходные регистры 9.i (44.1), регистры 17 и 50, регистры 14.1 (48.1) результата срабатывают по переднему фронту синхросигнала (положительный перепад), а буферные регистры 11.1 (45.) - по заднему фронту синхро- сигнала (отрицательный перепад).

В течение первых 15 тактов входные отсчеты поступают на ВХ 1 и записываются в ББП 2, после чего следует три холостых такта. В 19-м такте на выходе ББП 2 появляется первый отсчет (но уже в нужной последовательности). Этот такт считают первым, поскольку он первый для работы первой группы модулей первого типа.

1-й такт-ББП 2 Х(0);

2-й такт - ББП 2 Х(5); РГ 9.1 Х(0);

3-й такт - ББП 2 Х(10); РГ 9.1 - Х(5); РГ

17 Х(0); РГ11.1.1 Х(10); РГ 11.1.2 Х(5); АЛУ 18 Х(0); АЛУ 12.1 Х(5) + Х(10); АЛУ 13.1 Х(0) + Х(5) + Х(10); БПП 6(6.1) 1.

В 4-м такте на выходе первой группы появляется операнд Y(1) Х(0) + Х(5) + Х(10). Дальше работа первой группы продолжает- ся по описанному алгоритму. Управляющие сигналы с БПП 7 поступают на АЛУ 12.i, 13,1,

18таким образом, что на выходе первой группы появляются результаты, равносильные умножению двух матриц

1 1 1Х(к)

011 х Х(к + 5)

01-1Х(к+10)

где Х(к) - входные отсчеты сигнала;

k 0,3,6,9,12,

а суммирование в скобках происходит по модулю 15.

Работу первой группы модулей 21.1 рассмотрим начиная с 5-го такта.

5-й такт-РГ 14.1 Y(1).

Далее в течение 9 тактов происходит передача по проходным регистрам 29.1. В 12-м такте на выходе БПП 6(6.2) 1, на выходах БПП 20 1, в результате чего ТР 35 1, а операнды через MX 33 проходят в цепочку регистров 34.1.

14-й такт-БПП 6(6.2) БПП 20 Г; ТР 24.2 РГ 34.3 Y(1); РГ 34.2 Y(2); РГ 34.1 Y(3); РГ 29.2.3 Y(4); РГ 29.2.2 Y(5); РГ 29.2.1 Y(6); РГ 29.1.3 Y(7); РГ 29.1.2 Y(8); РГ29.1.1 - Y(9); MX25.2 Y(7); MX 26.2 - Y(4); АЛУ 32 Y(1); АЛУ 23.2 Y(4) + Y(7); АЛ.У 22.2 Y(1) +Y(4)+Y(7);/ РГ 14.1 Y(10).

15-й такт - БПП 20 ТР 24.2 Г; РГ 34.3 Y(2); РГ 34.2 Y(3); РГ 34.1 - Y(1); РГ 29,2.3 Y(5); РГ 29.2.2 Y(6); РГ 29.1.3 Y(8); РГ 29.1.2 Y(9); РГ 14.1 Y(11); РГ 29.1.1 Y(10); MX 25.2 Y(8); MX 26.2 Y(5); АЛУ 32 Y(2); АЛУ 23.2 Y(5) + Y(8); АЛУ 22.2 Y(2) + Y(5) + Y(8); РГ 27.2.1 Y(7); РГ 28.2.1 Y(4); РГ 30.2.1 Y(1) + Y(4) + Y(7).

16-й такт - БПП 20 ТР 24.2 Г; РГ 34.3 - Y(3); РГ 34.2 - Y(1); РГ 34.1 Y(2); РГ 29.2.3 Y(6); РГ 29.1.3 Y(9); РГ 29.1.2 Y(10); РГ14.1 Y(12); РГ29.1.1 Y(11); MX 25.2 Y(9); MX 26.2 Y(6); АЛУ 32 Y(3); АЛУ 23.2 Y(6) + Y(9); АЛ У 22.2 Y(3) + Y(6) + Y(9); РГ 27.2,1 Y(8); РГ 28.2.1 Y(5); РГ 30.2.1 Y(2)+ Y(5) + Y(8); РГ30.2.2 Y(1) + Y(4) + Y(7); РГ 27.2.2 Y(7); РГ 28.2.2 Y(4).

17-й такт - БПП 20 Г; ТР 24.1 Г; РГ 34.3 Y(1); РГ 34.2 Y(2); РГ 34.1 Y(3); РГ29.1.3 У(10); РГ29.1.2 У(11); РГ14.1 Y(13); РГ29.1.1 Y(12); MX 25.1 Y(13); MX 26.1 Y(10); АЛУ 32 0; АЛ У 23.2 Y(4) + Y(7); АЛУ 22.2 Y(4) + Y(7); РГ 27.2.1 Y(9); РГ

28.2.1 Y(6); РГ 30.2.1 Y(3) + Y(6) + Y(9); РГ

30.2.2 Y(2) + Y(5) + Y(8); РГ 27.2.2 Y(8); РГ

28.2.2 V(5); РГ 30.2.3 Y(1) + Y(4) + Y(7); РГ

27.2.3 Y(4); РГ 28.2.3 - Y(7); MX 25.2 Y(7); MX 26.2 Y(4); АЛУ 23.1 Y(10) + Y(13); АЛУ 22.1 Y(1) + Y(4) + Y(7) + Y(10) + Y(13).

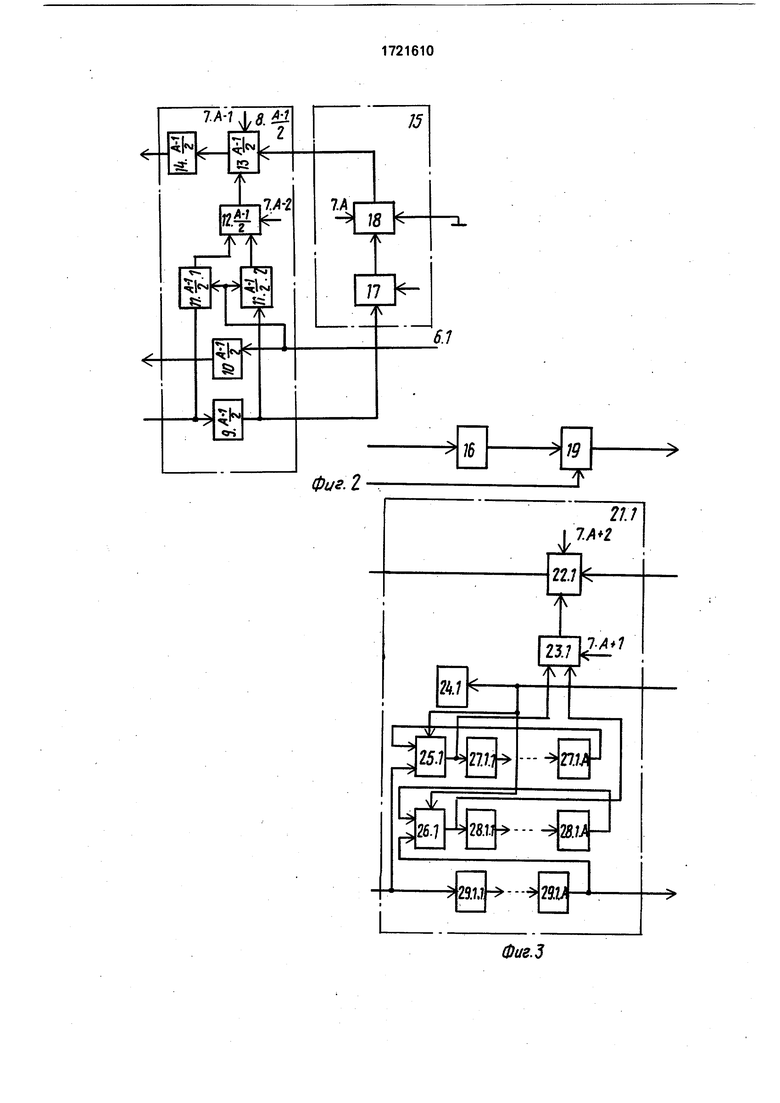

Далее работа группы модулей 21.1 продолжается по описанному алгоритму. Управляющие сигналы с БПП 7 на АЛУ 32, 23.1, 22.1 поступают таким образом, что на выходе имеется результат, равносильный умножению матриц

11110 11110 1-1000 1 1-1-10 0 0 1-1 О 1-11-10

Y(k) Y(k + 1) Y(k + 2) Y(k + 3) Y(k + 4) 0

где Y(k) - значения, поступающие на вход группы модулей 21.i(k 1,6,11).

С информационного входа модуля 21.1 значения поступают на первый вход УМН 19, на второй вход которого поступают значения весовых коэффициентов с БПП 16, после чего результат поступает на вход группы модулей 36,i.

Вторая группа модулей 36.1 работает аналогично первой группе 21.1. Управляющие сигналы с БПП 7 на АЛУ 62, 53.1, 59.1 поступают таким образом, что на выходе имеется результат , аналогичный умножению двух матриц

0 0 0 0 0 11101 1-1 1 0 -1 10-111; 1 0 1 -1 -Г

Y(k) Y(k + 1) Y(k + 2) Y(k + 3) Y(k + 4) Y(k + 5)

где Y(k) - значения, поступающие на вход группы модулей 36.I (k 1,7,13).

С информационного входа модуля 36.1 значения поступают на информационный вход группы модулей 37.i. Группа модулей 37.I работает аналогично первой группе модулей 8.I. Управляющие сигналы с БПП 7 поступают на АЛУ 46.i, 47.i, 51 таким образом, что на выходе группы модулей появляются результаты, равносильные умножению двух матриц

О О 1 1 1 -1

X(k) X(k + 1) X(k + 2)

где X(k) - значения, поступающие на информационный вход группы модулей 37.1, k - 1,4,7,10,13.

С выхода группы модулей 37.1 значения поступают на вход выходного блока 38 буферной памяти и с его выхода поступают на выход устройства в той последовательности, в которой они входили.

Формула изобретения Устройство для вычисления быстрого преобразования Фурье, содержащее генератор тактовых импульсов, счетчик, умножитель, первый блок постоянной памяти, блоки входной и выходной буферной памяти, отличающееся тем, что, с целью

снижения аппаратурных затрат, устройство содержит второй, третий и четвертый блоки постоянной памяти, первую и вторую группы из (А-1)/2 вычислительных модулей первого типа, первый и второй вычислительные модули второго типа, первую и вторую группу из (В-1)/2 (А-В - размер преобразователя) вычислительных модулей третьего типа, первый и второй вычислительный модули

0 четвертого типа, причем вычислительный модуль первого типа содержит два сумматора, два буферных регистра, проходной регистр, регистр результата и триггер, вычислительный модуль второго типа со5 держит сумматор и буферный регистр, вычислительный модуль третьего типа содержит группу из А проходных регистров, в первом модуле две, в остальных - три группы по А буферных регистров в каждой

0 группе, два коммутатора, триггер, два сумматора, вычислительный модуль четвертого типа содержит триггер, сумматор, коммутатор и группу из А буферных регистров, при этом выход генератора тактовых импульсов

5 подключен к тактовым входам триггеров, первых и вторых буферных резисторов, проходных регистров и регистров результата всех вычислительных модулей первого типа, тактовым входам регистров всех вычисли0 тельных модулей второго типа, тактовым входам проходных регистров группы и буферных регистров первой, второй и третьей групп всех вычислительных модулей третьего типа, к тактовым входам буферных реги5 строе группы всех вычислительных модулей четвертой группы и к счетному входу счетчика, информационный выход которого подключен к адресным входам первого, второго, третьего и четвертого блоков по0 стоянкой памяти и адресным входам блоков входной и выходной буферной памяти 2х (А+В) выходов второго блока постоянной памяти подключены к управляющим входам соответствующих сумматоров вычислитель5 ных модулей первого типа и второй групп, первого и второго вычислительных модулей второго типа, вычислительных модулей третьего типа первой и второй групп, первого и второго вычислительных модулей чет0 вертого типа, (В+1) выходов третьего блока постоянной памяти подключены к тактовым входам соответствующих триггеров вычислительных модулей третьего типа первой и второй групп и тактовым входам триггеров

5 первого и второго вычислительных модулей четвертогодипа, в вычислительных модулях первого типа первой и второй групп информационный вход и выход проходного регистра соединены соответственно с входами соответственно первого и второго буферных регистров, выходы которых подключены соответственно к первому и второму входам первого сумматора, выход которого подключен к первому входу второго сумматора, выход которого подключен к информа- ционному входу регистра результата, в первой и второй группах выход проходного регистра i-ro(i 1, (А-1)72-1) вычислительного модуля первого типа подключен к информационному входу проходного регистра (i+1)-ro вычислительного модуля первого типа, информационный вход 1-го триггера 1-го вычислительного модуля первого типа подключен к выходу триггера (i+1)-ro вычислительного модуля первого типа, выход регистра результата которого подключен к второму входу второго сумматора 1-го вычислительного модуля первого типа, выход проходного регистра (А-1)/2-го вычислительного модуля первого типа соединен с информационным входом регистра вычислительного модуля второго типа, выход которого подключен к первому входу сумматора данного вычислительного модуля, выход которого подключен к второму входу второго сумматора (А-1)/2-го вычислительного модуля первого типа, второй вход сумматора вычислительного модуля второго типа подключен к входу логического нуля устройства, информационный вход проходного регистра первого вычислительного модуля первого типа первой группы подключен к выходу блока входной буферной памяти, информационный вход которого является информационным входом устройства, информационный выход регистра результата первого вычислительного модуля первого типа первой группы подключен к информационному входу первого проходного регистра группы первого вычис- лительного.модуля третьего типа первой группы, информационный вход триггера (А- -1)/2-го вычислительного модуля первого типа первой группы подключен к первому выходу первого блока постоянной памяти, выход регистра второго сумматора первого вычислительного модуля третьего типа второй группы подключен к информационному входу проходного регистра вычислительного модуля первого типа второй группы, ин- формационный вход триггера (А-1)/2-го вычислительного модуля первого типа которой подключен к второму выходу первого блока постоянной памяти, а выход регистра результата первого вычислительного моду- ля первого типа второй группы подключен к информационному входу блока выходной буферной памяти, выход которого является информационным выходом устройства, во всех группах регистров вычислительных модулей третьего типа выход i-ro (i 1.A-1) регистра группы подключен к информационному входу (1+1)-го регистра группы, информационный вход первого проходного регистра группы объединен с первым информационным входом первого коммутатора, а выход А-го проходного регистра группы подключен к первому информационному входу второго коммутатора, вторые информационные входы первого и второго коммутаторов подключены к выходам А-х буферных регистров соответственно первой и второй групп, информационные входы первых регистров которых подключены к выходам соответственно первого и второго коммутаторов, кроме того, выходы первого и второго коммутаторов подключены соответственно к первому и второму входам первого сумматора, выход которого подключен к первому выходу второго сумматора, выход которого подключен к информационному входу первого буферного регистра третьей группы, а управляющие входы первого и второго коммутаторов подключены к выходу триггера, выход А-го проходного регистра группы 1-го (I 1,(В-1)/2-1) вычислительного модуля третьего типа подключен к информационному входу первого проходного регистра группы (1+1)-го вычислительного модуля третьего типа, второй вход второго сумматора -го вычислительного модуля третьего типа подключен к выходу А-го буферного регистра третьей группы (i+1)-ro вычислительного модули третьего типа, выход триггера которого подключен к информационному входу триггера i-ro вычислительного модуля третьего типа, выход i-ro (I 1,А-1) буферного регистра группы вычислительного четвертого типа подключен к информационному входу (i+T)-ro буферного регистра группы этого же модуля, а информационный вход первого буферного регистра группы подключен к выходу коммутатора, первый информационный вход которого подключен к выходу А-го буферного регистра группы и соединен с первым входом первого сумматора, второй вход которого подключен к входу логического нуля устройства, выходы триггеров первого и второго вычислительных модулей четвертого типа подключены к управляющим входам коммутаторов этих же модулей и к информационным входам триггеров (В-1)/2-го вычислительного модуля третьего типа соответственно первой и второй групп, а вторые информационные входы коммутаторов и выходы сумматоров первого и второго вычислительных модулей четвертого типа подключены соответственно к выходам А-проходных регистров групп и вторым входам вторых сумматоров (В-1)/2-х вычислительных модулей соответственно первой и второй группы, выход второго сумматора первого вычислительного модуля третьего типа первой группы подключен к первому входу умножителя, а информационный вход триггера первого вычислительного модуля четвертого типа подключен к третьему выходу первого блока постоянной памяти, информационный вход

первого проходного регистра группы первого вычислительного модуля третьего типа второй группы подключен к выходу умножителя, второй вход которого подключен к выходу четвертого блока постоянной памяти, информационный вход триггера второго вычислительного модуля четвертого типа подключен к четвертому выходу первого блока постоянной памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления быстрого преобразования Фурье | 1988 |

|

SU1644158A1 |

| Устройство для вычисления быстрого преобразования Фурье | 1988 |

|

SU1571611A1 |

| Устройство для контроля многоразрядных блоков оперативной памяти | 1987 |

|

SU1495854A1 |

| МОДУЛЬ МАТРИЧНОЙ КОММУНИКАЦИОННОЙ СЕТИ | 2000 |

|

RU2168755C1 |

| Устройство цифровой фильтрации | 1987 |

|

SU1446627A1 |

| Устройство для вычисления дискретного преобразования Фурье | 1989 |

|

SU1781684A1 |

| Кодек на основе кода Рида - Маллера первого порядка | 1990 |

|

SU1777243A1 |

| Цифровой фильтр | 1987 |

|

SU1501088A1 |

| Мультипроцессорная система | 1990 |

|

SU1732351A1 |

| Многоканальное устройство для обмена управляющей информацией в вычислительной системе | 1988 |

|

SU1566362A1 |

Фиг. 1

-

.

I TH

/%

W-L

+fzf

OL9L3AI

г :

Фиг.

.

31

Фиг. 5

511

ТОп

:ш ./

Г

- -

яи

h --52.7.А

Фиг. 6

1

1721610

57

Й1А

ям

38

Ш

Фиг.8.

39

±и+гб+г 37.1

,-

Ш

-

Фиг.9

Фиг. Ю

Авторы

Даты

1992-03-23—Публикация

1989-07-31—Подача