11

Нзобретение относится к.импульсно технике и может бьггь использовано для формирования задержанных импульсов.

Цель изобретения - расширение области применения за счет исключения зависимости величины задержки от скважности входных импульсов и увеличения крутизны фронта выходного импульса .

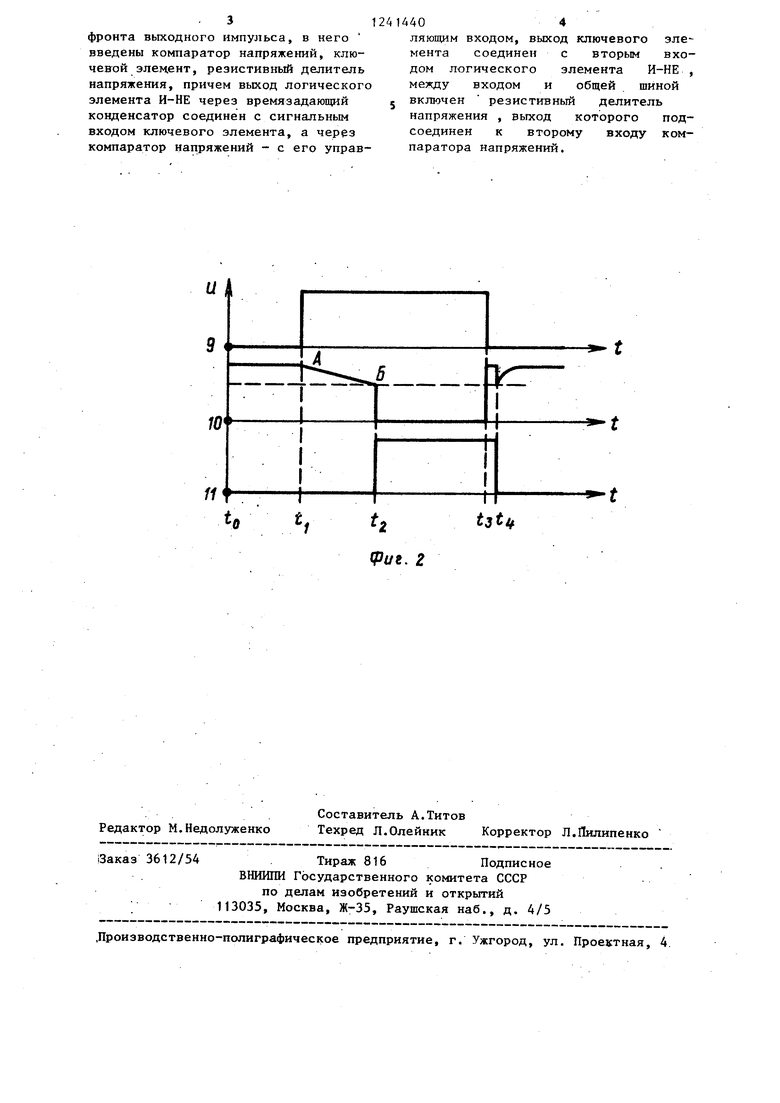

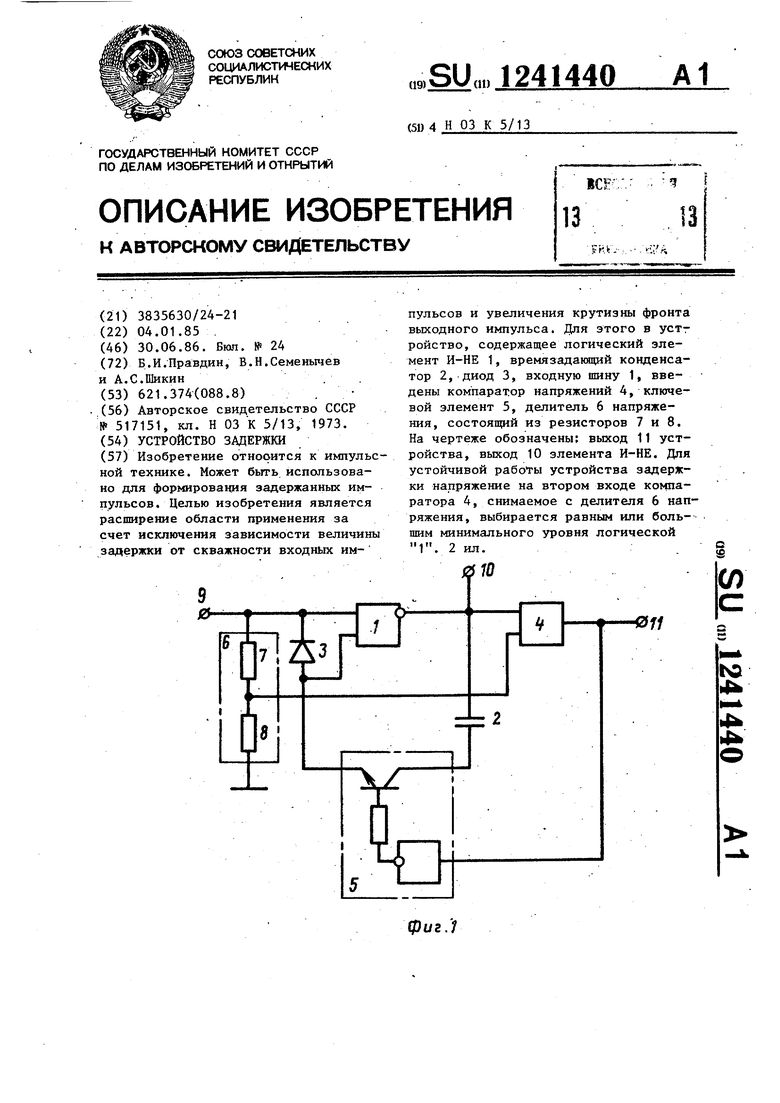

На фиг. 1 приведена схема предлагаемого устройства задержки ,на фиг.2 диаграммы напряжений в соответствующих точках устройства, пояснякнцие его работу.

Устройство задержки содержит логический элемент И-НЕ 1, ;времязадаю- щий конденсатор 2, диод 3, компаратор 4, ключевой элемент 5, делитель ,6 напряжения, состоящий из резисторов 7 и 8. Первый вход логического элемента И-НЕ 1 подключен к входной шине 9 и к катоду диода 3, анод которого соединен с вторым входом- логического элемента И-НЕ 1 и с выходом ключевого элемента 5,выход 10 логического элемента И-НЕ 1. через время- задающий конденсатор 2 соединен с сигнальным входом, а через компаратор 4 с управляющим входом ключевого элемента 5, делитель 6 напряжения .включен между входной и общей шиной, причем средняя точка делителя 6 подключена к второму входу компаратора 4, выход 11 которого является выходом устройства.

Устройство задержки работает следующим образом.

В исходном состоянии на входной шине 9 присутствует уровень логического р (фиг. 2, интервал времени с t( При этом на выходе 10 логического элемента И-НБ Т устанавливается уровень логической 1, на выходе 11 компаратора 4 - уровень логического О, при этом ключевой элемент 5 находится в открытом состоянии, а конденсатор 2 заряжен до уровня логической 1.

При поступлении на входную шину уровня логической 1 (фиг. 2, момент времени t,), диод 3 запирается, конденсатор 2. йачинает заряжаться через входную и выходную цепь логического элемента И-НЕ 1, который при охвачен глубокой отрицательной обратной связью через конденсатор 2 и открытый ключевой элемент 5. Вслед стане глубокой обратной связи напря14402

жение на выходе 10 логического элемента И-НЕ 1 уменьшается по линейному закону (фиг. 2, участок А-Б).

Когда напряжение на выходе 10 ло, гического элемента И-НЕ 1 уменьшится до напряжения на втором входе компаратора 4, определяемого уровнем входного сигнала и коэффициентом деления разистивного делителя 6, на

fg выходе 11 компаратора 4 устанавливается уровень логической 1 (фиг.2, момент времени tj), которым закрывается ключевой элемент 5. Отрицательная обратная связь логического

элемента И-НЕ 1 при этом разрывается и на его выходе скачком устанавливается уровень логического О.

При поступл:ении на входную шину уровня логического О (фиг. 2, мо2().мент времени tj , на выходе 10 логического элемента И-НЕ 1 устанавливается уровень логической 1 на выходе компаратора 4 с задержкой, обусловленной его быстродействием

25 устанавливается уровень логического О (фиг. 2, момент времени t), ключевой элемент 5 замыкается и на первом входе компаратора 4 устанавливается напряжение, до которого

JQ разрйдился кон1: енсатор 2, начинающий заряжаться до уровня логическрй 1 При этом напряжение на втором входе компаратора 4, снимаемое с делителя 6 напряжения, близко к О, т.е. всегда меньше, чем напряжение на конденсаторе 2 и на первом входе компаратора 4, что обеспечивает устойчивую работу компаратора 4 в процессе заряда-конденсатора 2.

рЦля устойчивой работы устройства задержки напряжение на втором входе компаратора 4, снимаемое с делителя 6 напряжения, выбирается равным или большим минимального уровня логической 1.

35

40

45

Формула изобретения

Устройство задержки, содержащее логический элемент И-НЕ, времязадаю- щий конденсатор и диод, подсоединенный катодом к входной шине и к первому входу логического элемента .И-НЕ, а анодом - к второму его входу, отличающееся тем, что, с целью расширения области применения за счет исключения зависимости величины задержки от скважности входт ных импульсов и увеличения крутизны

фронта выходного импульса, в него введены компаратор напряжений, ключевой элем,ент, резистивный делитель напряжения, причем выход логического элемента И-НЕ через времязадающий конденсатор соединен с сигнальным входом ключевого элемента, а через компаратор напряжений - с его управРедактор М.Недолуженко

Составитель А.Титов

Техред Л.Олейник Корректор Л.Яилипенко

3612/54

Тираж 816Подписное

ВНИШШ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

.Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4.

ляющим входом, выход ключевого эле мента соединен с вторым входом логического элемента И-НЕ , между входом и общей шиной включен реэистивный делитель напряжения , выход которого подсоединен к второму входу компаратора напряжений.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многофазный мультивибратор | 1984 |

|

SU1231580A1 |

| Одновибратор | 1978 |

|

SU790123A1 |

| Устройство задержки | 1978 |

|

SU790214A1 |

| Формирователь импульсов | 1985 |

|

SU1325674A1 |

| Устройство задержки импульсов | 1979 |

|

SU856000A1 |

| Многофазный формирователь импульсов | 1977 |

|

SU684729A1 |

| Мультивибратор | 1978 |

|

SU738106A1 |

| Ключевой стабилизатор напряжения с повышением выходного напряжения | 1989 |

|

SU1654802A1 |

| Формирователь импульсов | 1985 |

|

SU1330738A1 |

| Устройство для управления электромагнитным механизмом | 1983 |

|

SU1150676A1 |

Изобретение относится к импульсной технике. Может быть использовано для формирования задержанных импульсов . Целью изобретения является расширение области применения за счет исключения зависимости величины задержки от скважности входных импульсов и увеличения крутизны фронта выходного импульса. Для этого в устг ройство, содержащее логический элемент И-НЕ 1, времязадающий конденсатор 2, диод 3, входную шину 1, введены компаратор напряжений 4, ключевой элемент 5, делитель 6 напряжения, состоящий из резисторов 7 и 8. На чертеже обозначены; выход 11 устройства, выход 10 элемента И-НЕ. Для устойчивой работы устройства задержки напряжение на втором входе ратора 4, снимаемое с делителя 6 напряжения, выбирается равным или большим минимального уровня логической 1. 2 ил. 010 (Л ND 4 (рог. 7

| Элемент задержки | 1973 |

|

SU517151A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-06-30—Публикация

1985-01-04—Подача