(54) ЭЛЕМЕНТ ЗАДЕРЖКИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Элемент задержки потенциальных сигналов | 1978 |

|

SU731568A2 |

| Генератор импульсов | 1987 |

|

SU1448387A1 |

| Одновибратор | 1980 |

|

SU892665A1 |

| Генератор импульсов | 1987 |

|

SU1628190A1 |

| Одновибратор | 1975 |

|

SU712930A1 |

| Генератор импульсных сигналов | 1978 |

|

SU780165A1 |

| Ждущий мультивибратор | 1978 |

|

SU782134A1 |

| Делитель частоты | 1983 |

|

SU1152087A2 |

| ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ | 1972 |

|

SU425334A1 |

| Одновибратор | 1978 |

|

SU733088A1 |

1

Изобретение относится к импульсной технике и может быть использовано Б схемах формирователей импульсов, в частности, для формирования задержанных импульсных сигналов.

Известен элемент задержки потенциальных сигналов, содержащий элемент И-НЕ транзисторно-транзисторной логики, к одному иа входов которого подключена времязадающая диодно конденсаторная последовательная цепь.

Цель изобретения - увеличение быстродествия устройства и повышение стабильности временной задержки.

Поставленная цель достигается тем, что в устройстве вход логического расширения элемента И-НЕ подключен к точке соединения диода и конденсатора времязадаюшей цепи.

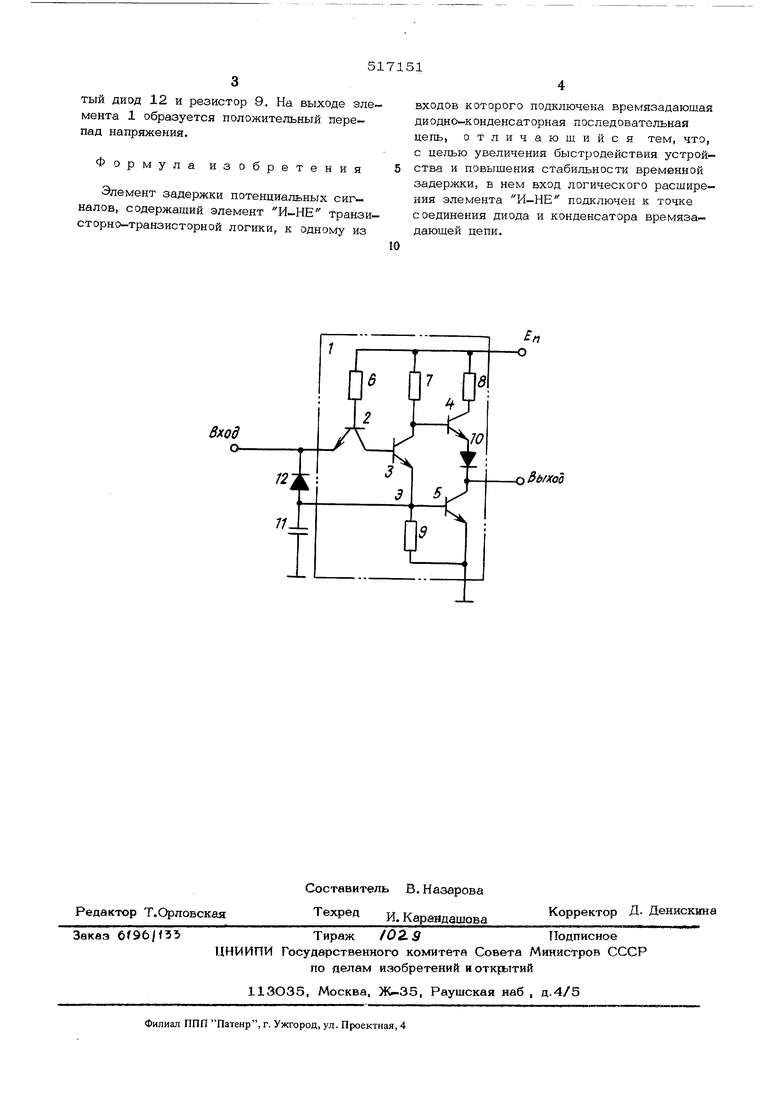

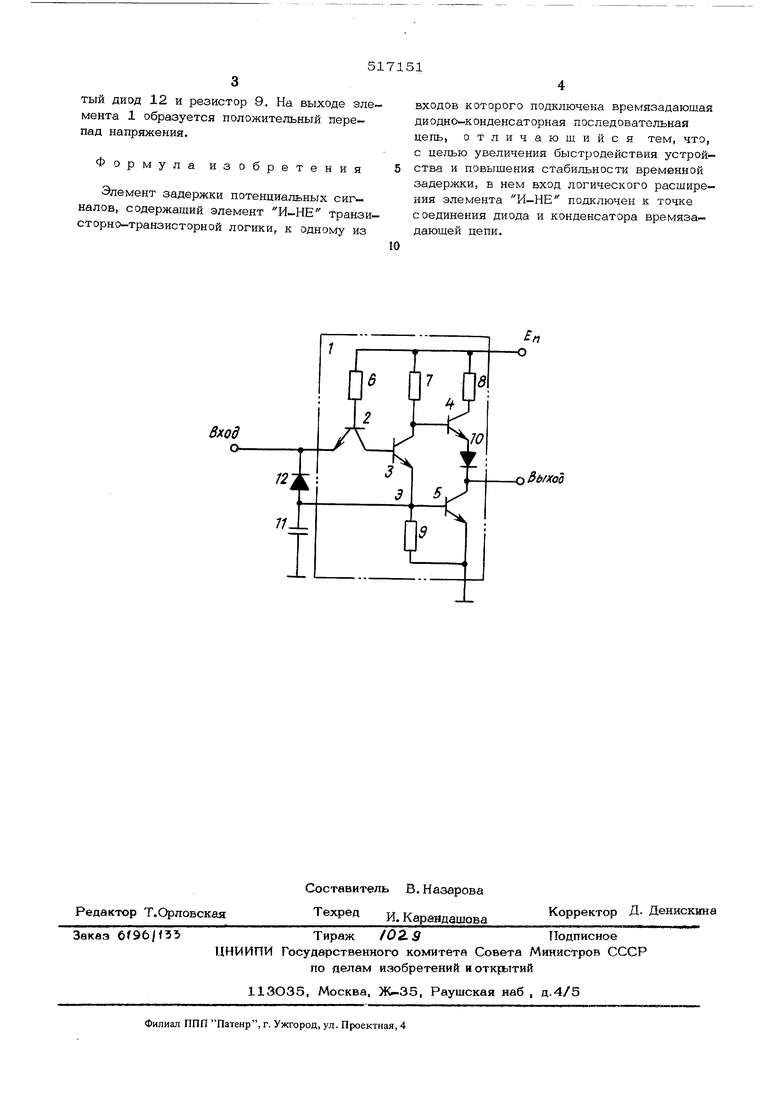

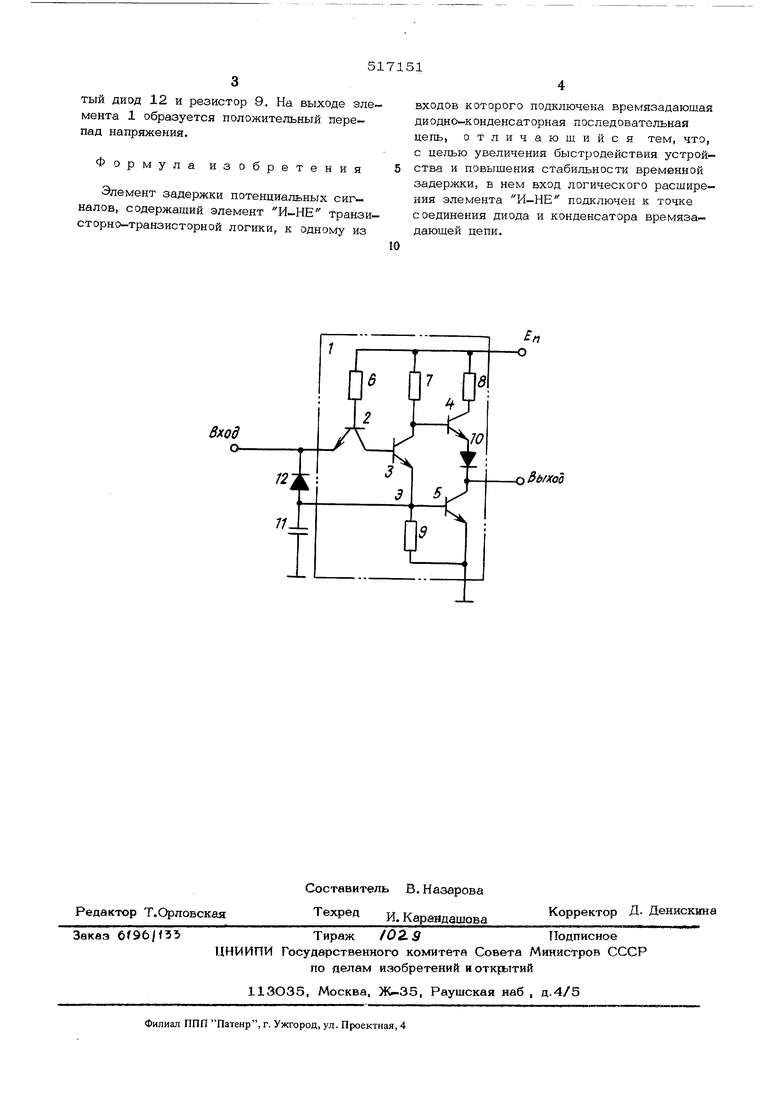

На чертеже приведена схема предложенн го элемента задержки потенциальных сигналов.

Элемент задержки состоит из элемента И-НЕ транзисторно-транзисторной логики 1, содержащего транзисторы 2-5, резисторы 6-9 и диод 10 и имеющего эмиттерный ввод логического расширения (Э), времязадающего конденсатора 11 и диода 12.

Элемент работает следующим образом.

В исходном состоянии вход логического элемента И-НЕ 1 имеет низкий потенциал, а выход - высокий потенциал. При поступлении положительного перепада напряжения на вход логического элемента 1 открывается транзистор 2, который затем открывает транзистор 3. Начинается заряд конденсатора 11 через резистор 7 и открытый транзистор 3. При этом на выходе логического элемента 1 создается высокий потенциал, так как тра 1зистор 4 остается открытым, а транзистор 5 - закрытым. После зарядки конденсатора 11 до потенциала отпирания транзистора 5 последний открывается, а транзистор 4 закрывается. На выходе элемента 1 формируется отрицательный перепад напряжения.

При поступлении отрицательного перепада напряжения на вход элемента 1 происходит разряд конденсатора 11 через открытый диод 12 и резистор 9. На выходе злемента 1 образуется положительный перепад напряжения.

Формула изобретения

Элемент задержки потенциальных сигналов, содержащий элемент И-НЕ транзисторно-транзисторной логики, к одному из

Вход

входов которого подключена времязадающая диодно-конденсаторная последовательная цепь, отличающийся тем, что, с целью увеличения быстродействия устройства и повышения стабильности временной задержки, в нем вход логического расщирения элемента И-НЕ подключен к точке соединения диода и конденсатора времяза- дающей цепи.

о bfxoo

Авторы

Даты

1976-06-05—Публикация

1973-01-04—Подача