ГТИ 3 через элемент И 2 на вход ГКС 4. ГКС 4 вьфабатывает псевдослучайные т-элементные последователности Г и О, которые поступают на другие входы сумматора 6 и ФП ,

8сумматоре 6 осуществляется сложение по модулю два п повторов сигнала и информац. символа,. Этот сигнал передается передатчиком 5. Из линии связи принимается приемником

9каждый из п повторов m -последовательности, составляющих информад. символ, Принятьй повтор поступает на первый вход перемножителя 12, а на Второй вход подаются канальные сигналы из ГКС 16, строго синхрониИзобретение относится к электросвязи и может быть использовано в асинхронных адресных системах связи с кодовым разделением каналов.

Цель изобретения - повьшение помехоустойчивости при периодических

взаимных помехах. I

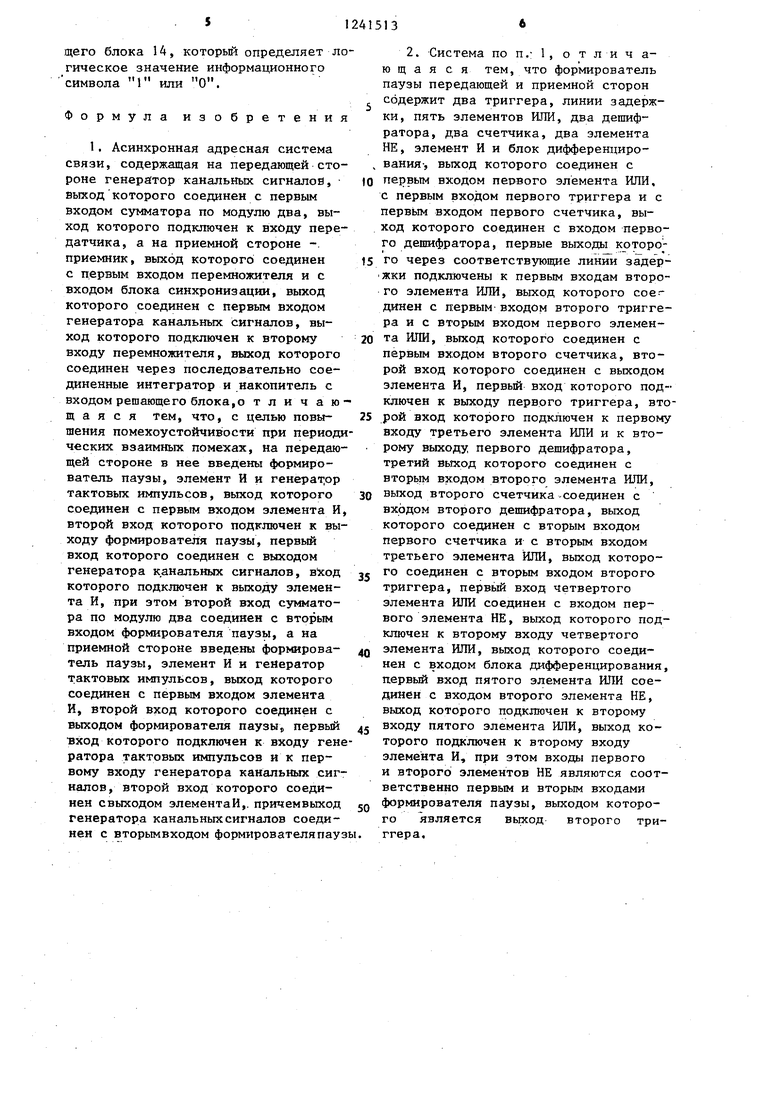

На фиг. 1 изображена структурная

электрическая схема предложенной системы связи; на фиг. 2 - структурная электрическая схема, формирователя паузы.

Асинхронная адресная система связи содержит на передающей стороне формирователь 1 паузь (ФП), элемент И 2, генератор 3 тактовых импульсов (ГТИ), генератор 4 канальных сигналов (ГКС), передатчик 5, сумматор 6 по модулю два, на приемной стороне - ФП 7, элемент И В, приемник 9, блок 10 синхроназидии, интегратор 1 ,, перемножитель 12, накопитель 13, решающий блок 14, ГТИ 15, ГКС 16.

Формирователь паузы содержит первый и второй элементы НЕ 17 и 1В первый и второй триггеры 19 и 20, линии 21 задержки первый, второй, третий, четвертьй и пятый элементы ИЛИ 22-26, первьш и второй дешифраторы 27 и 28, первый и второй счетчики 29 и 30, элемент И 31, блок 32 дифференцирования.

Система работает следующим образом.

13

зргрованные по фазе и циклам с помощью блока си1гх;ронизадии 10. По его командам ФП 7 управляет работой ГКС 16 с помоапэю элемента И 8 и ГТИ 15„ Пере1-даожит(5ль 12 и интегратор 1 осуществляют коррелядионную об работку каждого повтора информац. символа. Затем сигнал накапливается в накопителе 13 и подается на вход решаюп1его блока 14, который определяет логическое значение информац. символа 1 или О, Цель достигается введением ФП 1 и 7, элементов И 2 и 8 и ГТИ 3 и 15. Дан пример выполнения ФП 1 и 7. 1 з.п. ф-лы, 2 ил.

Информационные символы в виде логическихностью

и О каждый ДгЕительTj, nTi, +

r.i

Ui t

где t( - задержка сигнала i-x линий

21 задержки в ФЦ 1, . поступают в сумматор 6 по модулю два и ФП 1, на другой вход которого подаются из генератора 4 канальных сигнапов канальные сигналы, пред- ставляюшие собой т-элементные псевдослучайные последовательности 1 и О, причем длительность каждого элемента То Tn/m.

Очередные информационные 1 или о, проходя в ФП 1 через элементы

НЕ 17, FUM 25 поступают в виде 1 на вход блока 32 дифференцирования, Где преобразуются в сигнал длительностью Ц , который подается одновременно на установочньй вход первого счетчика 29, через элемент ИЛИ 22 на установочный вход счетчика 30 и на единичнъм вход триггера 19. При этом счетчик 29 (вычитающий, емкостью п) устанавливается в состояние п,соответствующее числу повторов информационного символа, счетчик 30 (суммир тощий, емкостью т) - в нулевое состояние, а триггер 19 - в единичное состояние, причем единичный потенцисш с его выхода разрешает

3

прдхождение сигналов через элемент И 31 .

Код состояния счетчика 29 поступает На первьй дешифратор 27, где, дешифрируясь, снимается на одном из п+1 выходов, п-1 из которых подключены к линиям 21 задержки сигнала, п-й выход - к элементу ИЛИ 23, а - к элементу ИЛИ 24. п-1 лини 21 задержек построены таким образом что вместе они обеспечивают задержку повторов друг относительно друга на псевдослучайную длительность, кратную длительности канального элемента, т.е.

il Г i

jtn

О,

где 15,(,-длительность задержки i-ro

повтора;

(f -псевдослучайное число из некоторого отрезка ряда на - турал ьных чисел.

При этом необходимо обеспечить, чтобы шахе (t jl ) Т. При определении длительности задержки сигнала в линиях 21 задержки должны быть также учтены задержки сигнала в соответствующих элементах формирователя 1 паузы.

Сигнал, задержанньш на величину t через элемент ИЛИ 23 поступает на единичный вход триггера 20, ко- торьш переходит в единичное состояние. В этом случае на вход элемента И 2 подается потенциал, разрешающий прохождение тактовых импульсов длительностью i-o с ГТИ 3 на вход ГКС 4.

ГКС 4 вырабатывает псевдослзгчай- ные т-элементные последовательности 1 , которые поступают в сум матор 6 по модулю два и на второй вход формирователя 1 паузы,. т-пос- ледовательности 1 и О в ФП 1 поступают через элементы НЕ 18, ИЛИ 26 в виде 1 через открытый элемент И 31 на счетный вход второго счетчика 30. Счетчик 30 подсчитывае ровно m элементов последовательности. Второй дешифратор 28 настроен на код числа т. Поэтому при достижении счетчиком 30 состояния с выхода дешифратора 28 снимается сигнал, которьй одновременно установит в нулевое состояние через элемент ИЛИ 24 триггер 20, а также, поступая на счетный вход первого счетчика 29, уменьшит его содержимое на единицу.

415134

Нз левое состояние триггера 20 запрещает прохождение через элемент И 2 тактовых импульсов, что приводит . к остановке генератора 4 канальных 5 сигналов.

После фop иpoвaния последнего п-го повтора информационного символа первый счетчик 29 установится в нулевое состояние. При этом с нуле- 10 во-го выхода дешифратора 27 снимается сигнал, который установит триггер 19 в нулевое состояние и через элемент ИЛИ 24 триггер 20, тем самым заканчивается работа формирователя 15 I паузы и отключается генератор 4 канальных сигналов до поступления следующего информационного символа. В сумматоре 6 по модулю два осуществляется сложение по модулю два 20 п повторов сигнала и информационного символа. При этом, если на вход сумматора 6 по модулю два поступит информационная 1, то на его выходе образуется п сдвинутых относительно 25 друг друга на псевдослзгчайное время, определяеме в формирователе 1, m последовательностей, формируемых генератором 4 канальных сигналов, а если - информационный О, то на 30 вьосоде сумматора 6 по модулю два об- разутотся инвертированные п m последовательности со сдвигом., п га последовательностей, образующих 1 повторов информационного символа, с выхода сумматора 6 по модулю два поступает в передатчик 5. На приемной стороне приемник 9 принимает из линии связи каждый из п повторов m последовательности, составляющие информационный символ. Принятьй повтор .поступает на вход умножителя 12.

На второй вход умножителя подаются канальные сигналы из ГКС 16, строго синхронизиро.ванные по фазе и цик- 5 лам с помощью блока 10 синхронизации. Работой ГКС 16 управляет формирователь 7 паузы по командам от блока 10 синхронизации.

Умножитель 12 и интегратор 11 осу- 0-ществляют корреляционную обработку каждого повтора информационного символа. После обработки сигнал с выхода интегратора 11 поступает на вход Накопителя 13, где пакапливает- 5 ся значение сигнала повторов информационного символа. По окончании накопления повторов с выхода накопителя 13 сигнал подается на вход решаю5

0

щего блока 14, которьй определяет логическое значение информационного символа 1 или О.

Формула изобретения

1. Асинхронная адресная система связи, содержащая на передающей стороне генератор канальных сигналов, выход которого соединен с первым входом сумматора по модулю два, выход которого подключен к входу передатчика, а на приемной стороне - приемник, выход которого соединен с первым входом перемножителя и с входом блока синхронизации, выход которого соединен с первым входом генератора канальных сигналов, выход которого подключен к второму входу перемножителя, выход которого соединен через последовательно соединенные интегратор и накопитель с входом решающего блок а, о т л и ч а ю- щ а я с я тем, что, с целью повы- шения помехоустойчивости при периодических взаимных помехах, на передающей стороне в нее введены формирователь паузы, элемент И и reHepatiop тактовых импульсов, выход которого соединен с первым входом элемента И, второй вход которого подключен к выходу формирователя паузы, первый вход которого соединен с выходом генератора канальных сигналов, в ход которого подключен к выходу элемента И, при этом второй вход сумматора по модулю два соединен с вторым входом формирователя паузы, а на приемной стороне введены формирова- тель паузы, элемент И и генератор тактовых импульсов, выход которого соединен с первым входом элемента И, второй вход которого соединен с выходом формирователя паузы, первый ВХОД которого подключен к входу генератора тактовых импульсов и к первому входу генератора канальных сигналов, второй вход которого соединен свыходом элементам,, причемвыход генератора канальныхсигналов соединен с вторымвходом формирователя пау

2. Система по п.; 1 , о т л и ч а- ю щ а я с я тем, что формирователь паузы передающей и приемной сторон содержит два триггера, линии задержки, пять элементов ИЛИ, два дешифратора, два счетчика, два элемента НЕ, элемент И и блок дифференцирования-, выход которого соединен с первым входом первого элемента ИЛИ. с первым входом первого триггера и с первьм входом первого счетчика, выход которого соединен с входом первого дешифратора, первые выходы которого через соответствующие линии задер Жки подключены к первым входам второго элемента ИЛИ, выход которого сое- динен с первым входом второго триггера и с вторым входом первого элемента ИЛИ, выход которого соединен с первым входом второго счетчика, второй вход которого соединен с выходом элемента И, первый вход которого подключен к выходу первого триггера, втрой вход которого подключен к первом входу третьего элемента ИЛИ и к второму выходу первого дешифратора, третий выход которого соединен с BTopbiM входом второго элемента ИЛИ, выход второго счетчика -соединен с входом второго дешифратора, выход которого соединен с вторым входом первого счетчика и с вторым входом третьего элемента ИЛИ, выход которого соединен с вторым входом второго триггера, первьй вход четвертого элемента ИЛИ соединен с входом первого элемента НЕ, выход которого подключен к второму входу четвертого элемента ИЛИ, выход которого соединен с входом блока дифференцирования первый вход пятого элемента ИЛИ соединен с входом второго элемента НЕ, выход которого подключен к второму входу пятого элемента Ш1И, вьпсод которого подключен к второму входу элемента И, при этом входы первого и второго элементов НЕ являются соответственно первым и вторым входами формирователя паузы, выходом которого является вьгход второго триггера.

Редактор М. Недолуженко ,

Заказ 3616/58Тираж 624Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. .тная, 4

фиг. 2

Составитель 0. Геллер

Техред О.Гортвай Корректор В. Бутяга

| название | год | авторы | номер документа |

|---|---|---|---|

| СТАРТСТОПНАЯ СИСТЕМА СВЯЗИ | 2003 |

|

RU2252489C2 |

| СТАРТСТОПНАЯ СИСТЕМА СВЯЗИ | 2005 |

|

RU2284668C1 |

| Устройство для декодирования сверточного кода | 1984 |

|

SU1213491A1 |

| СТАРТСТОПНАЯ СИСТЕМА СВЯЗИ | 2002 |

|

RU2229200C2 |

| СТАРТСТОПНАЯ СИСТЕМА СВЯЗИ | 2002 |

|

RU2218669C1 |

| СИСТЕМА ДЛЯ ПЕРЕДАЧИ И ПРИЕМА ИНФОРМАЦИИ КОДОМ ПЕРЕМЕННОЙ ДЛИНЫ | 1996 |

|

RU2123765C1 |

| Вероятностное устройство для решения уравнения Лапласа | 1983 |

|

SU1091172A1 |

| Цифровой интегратор | 1990 |

|

SU1709309A1 |

| РАДИОСТАНЦИЯ | 2010 |

|

RU2484583C2 |

| СИСТЕМА СВЯЗИ | 2003 |

|

RU2249914C2 |

Изобретение относится к электросвязи. Повышается помехоустойчивость при периодических взаимных помехах. Устройство содержит на передающей стороне формирователь паузы (ФП) 1, элемент И 2, генератор тактовых импульсов (ГТИ) 3, генератор канальных сигналов (ГКС) 4, передатчик 5 и сумматор 6 по модулю два, а на приемной стороне ФП 7, элемент И 8, приемник 9, блок синхронизации 10, интегратор 1, перемножитель 12, накопитель 13, решающий блок 14, ГТИ 15 и ГКС 16. Информац. символы поступают на первые входы сумматора 6 и ФП 1, который вырабатывает сигнал, разрешающий или запрещающий прохождение тактовых импульсво с (Л с

| Дядюнов Н.Г | |||

| и др | |||

| Ортогональные и квазиортогональные сигналы | |||

| М.: Связь, 1977, с | |||

| Схема обмотки ротора для пуска в ход индукционного двигателя без помощи реостата, с применением принципа противосоединения обмоток при трогании двигателя с места | 1922 |

|

SU122A1 |

Авторы

Даты

1986-06-30—Публикация

1984-05-18—Подача