Изобретение относится к электро- связи и может быть использовано, например, в системах передачи цифровой видеоинформации.

Цель изобретения - повышение быстродействия и надежности установления состояния циклового синхронизма устройства.

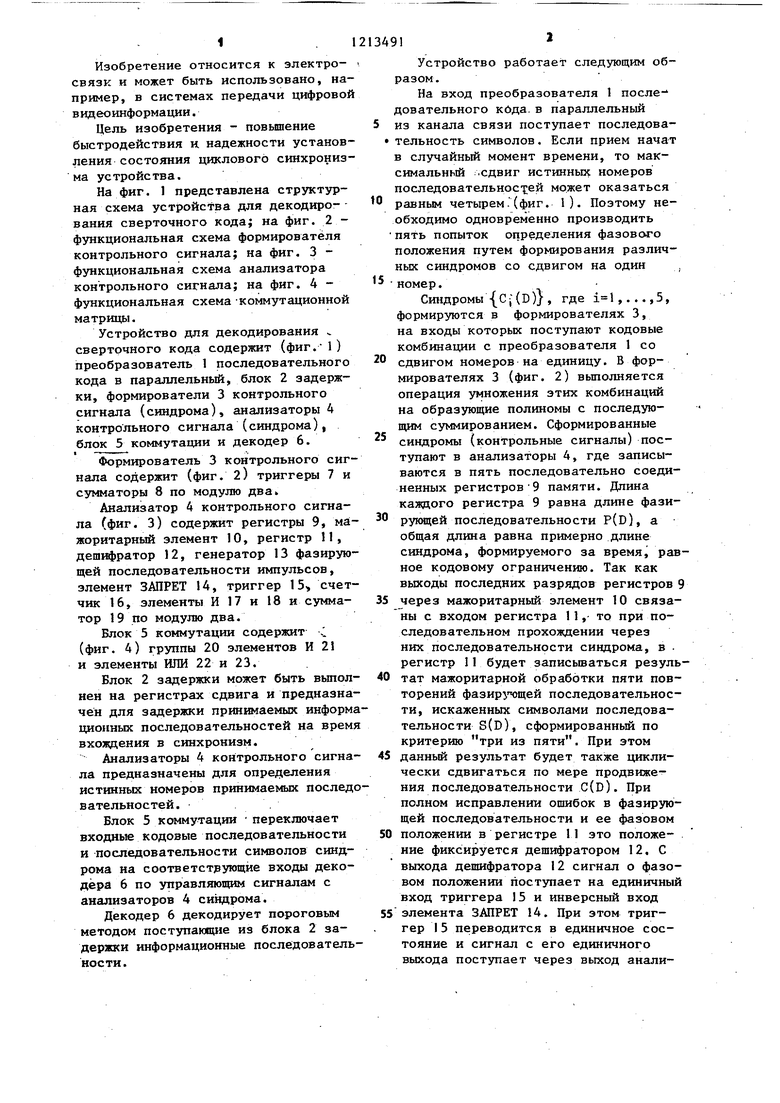

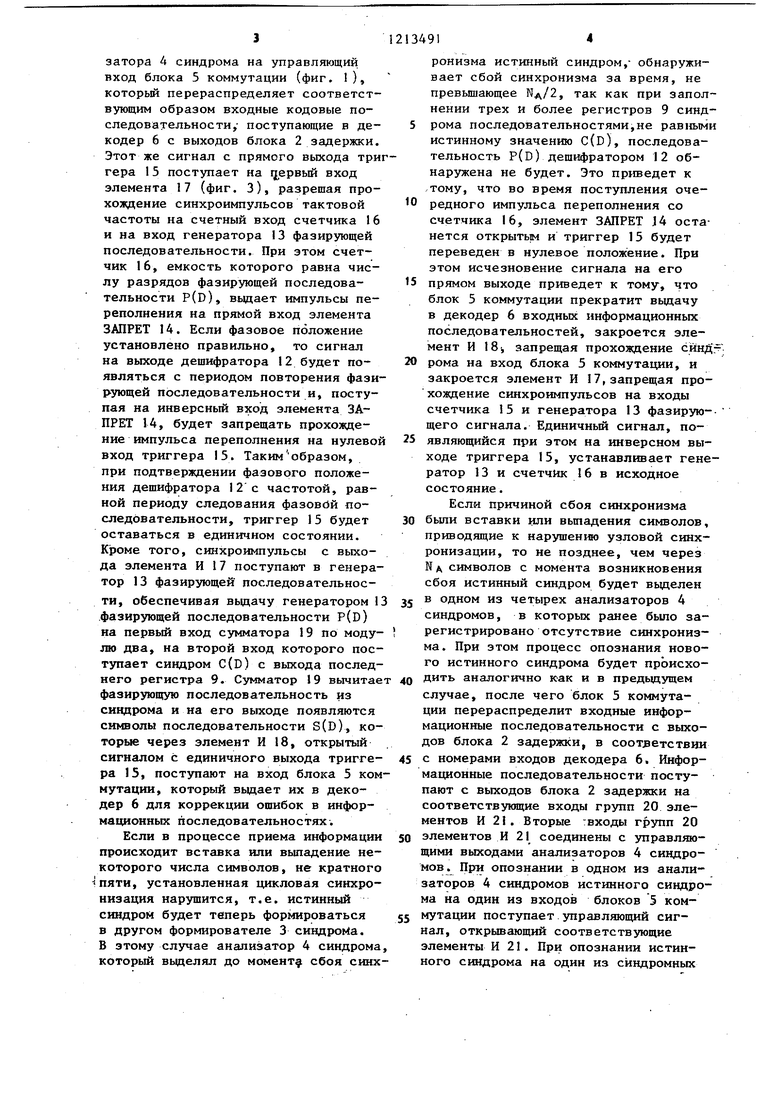

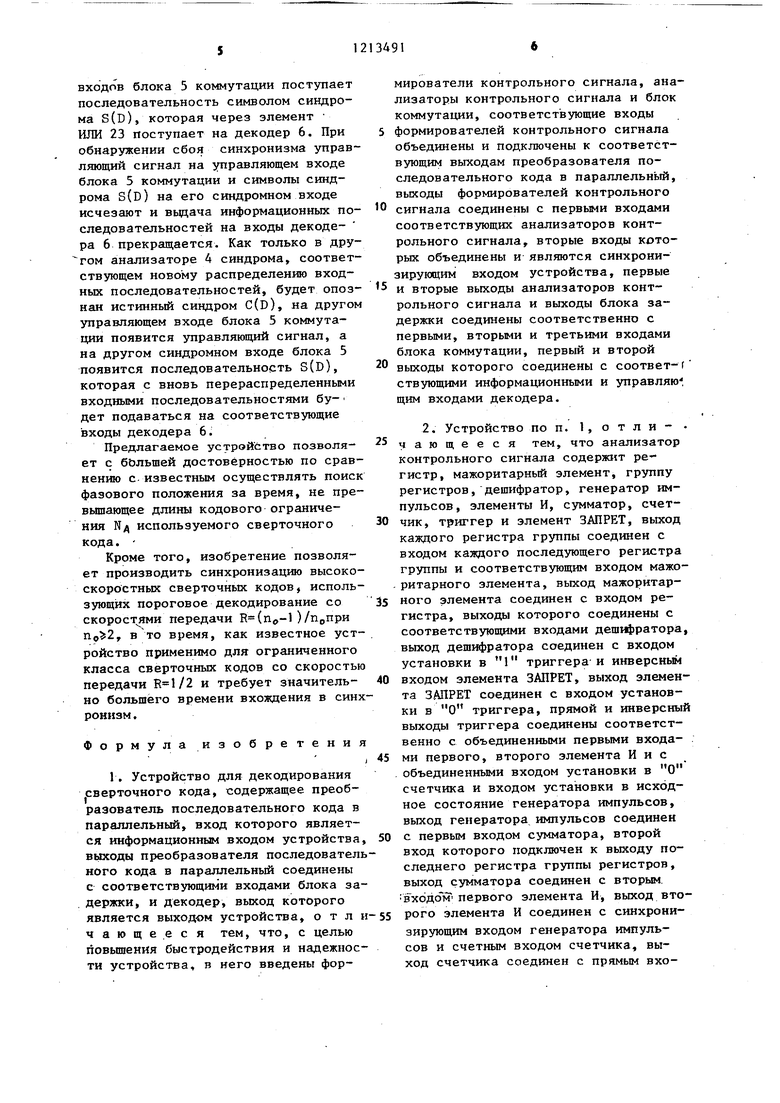

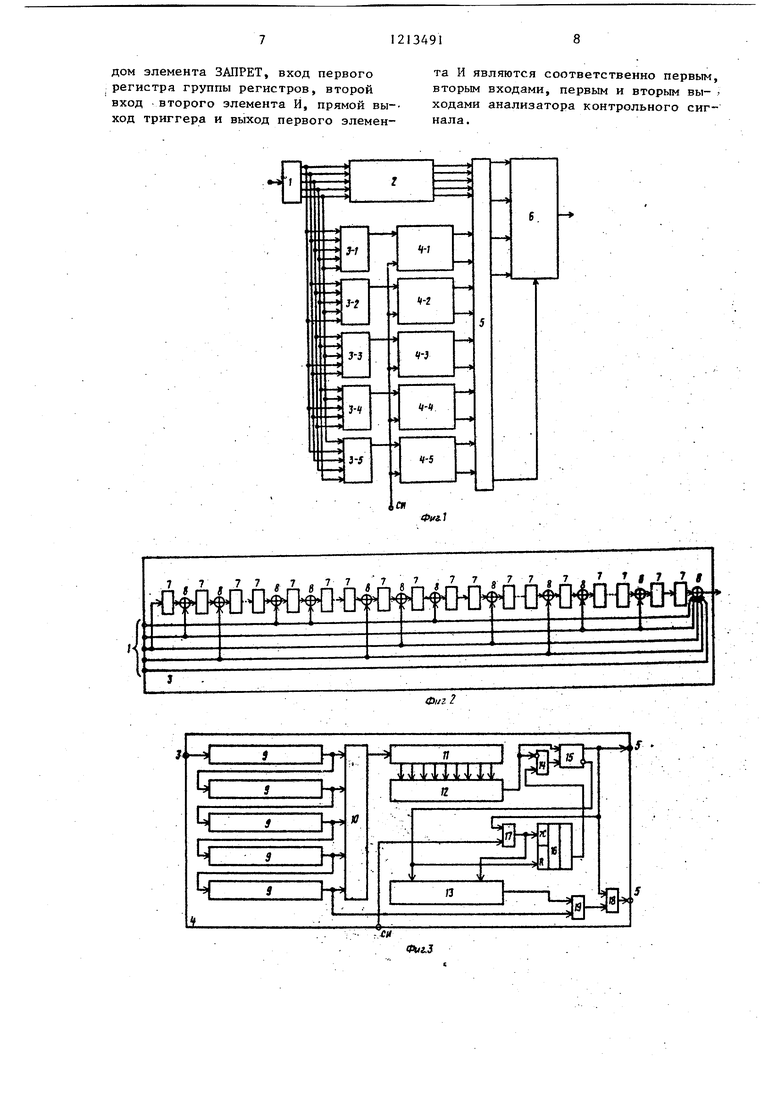

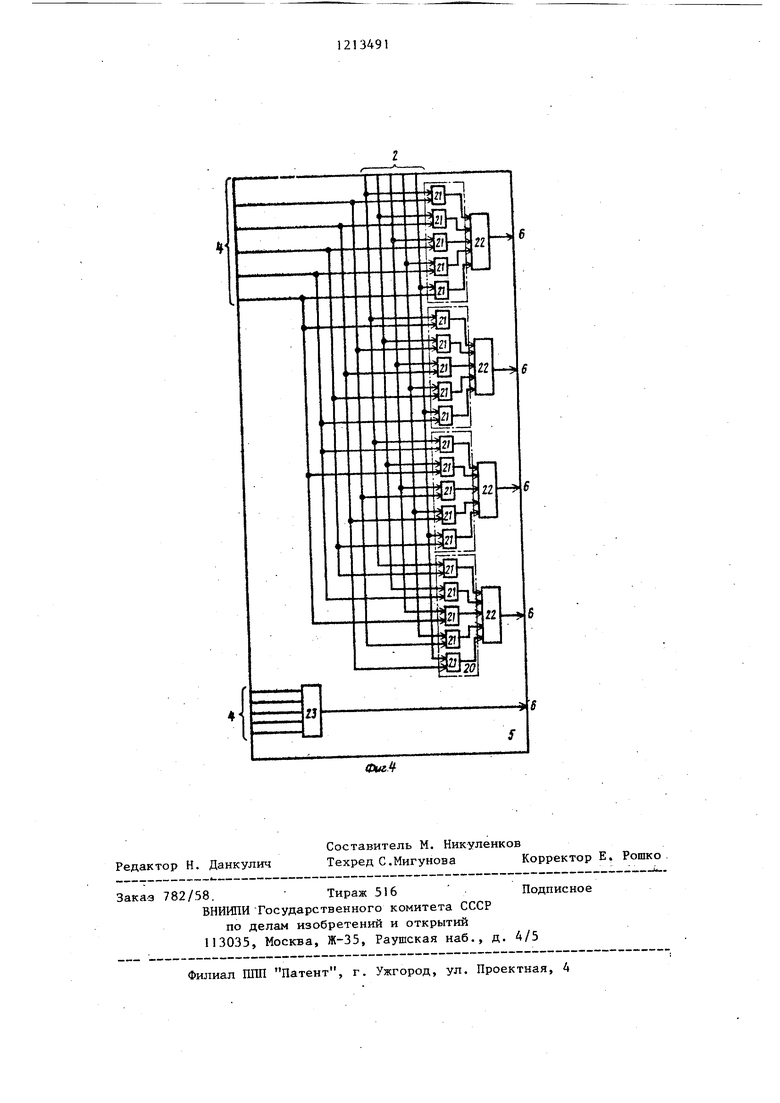

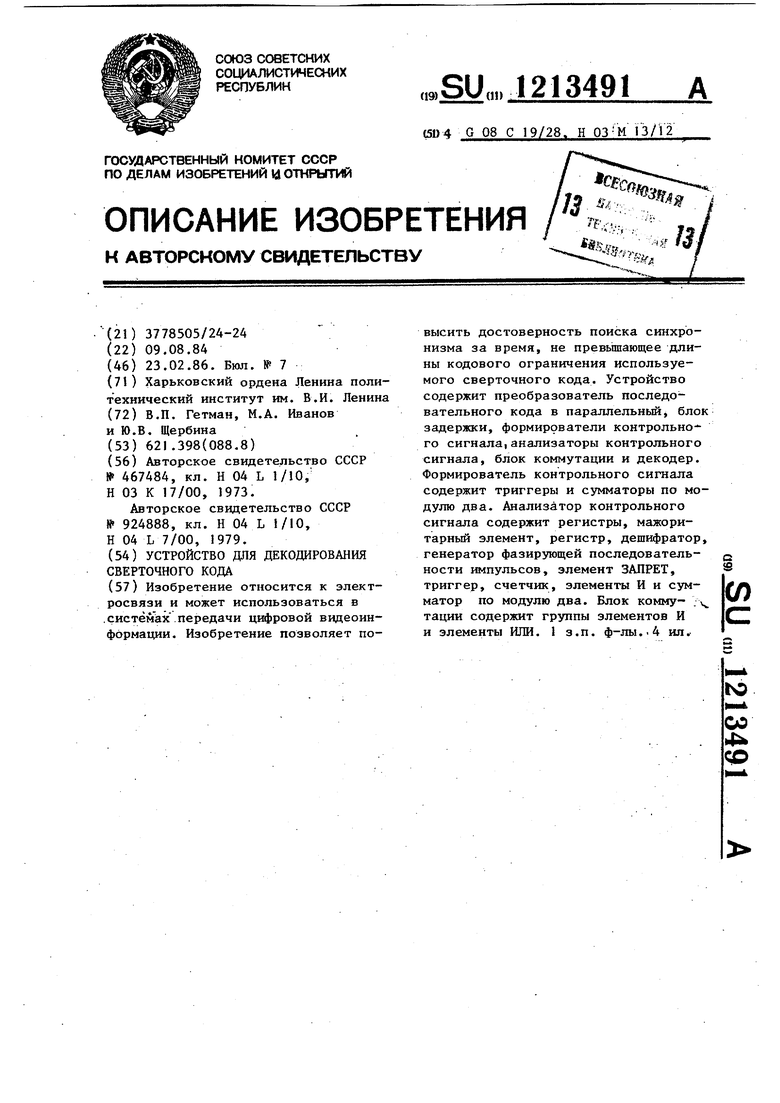

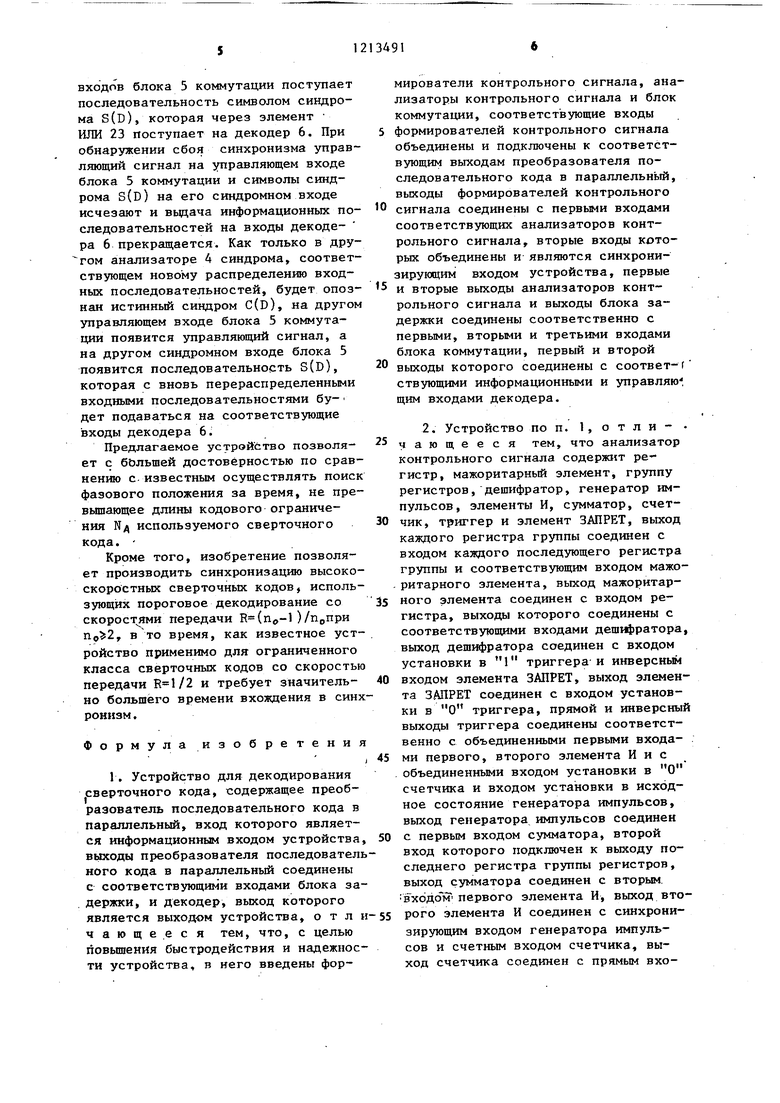

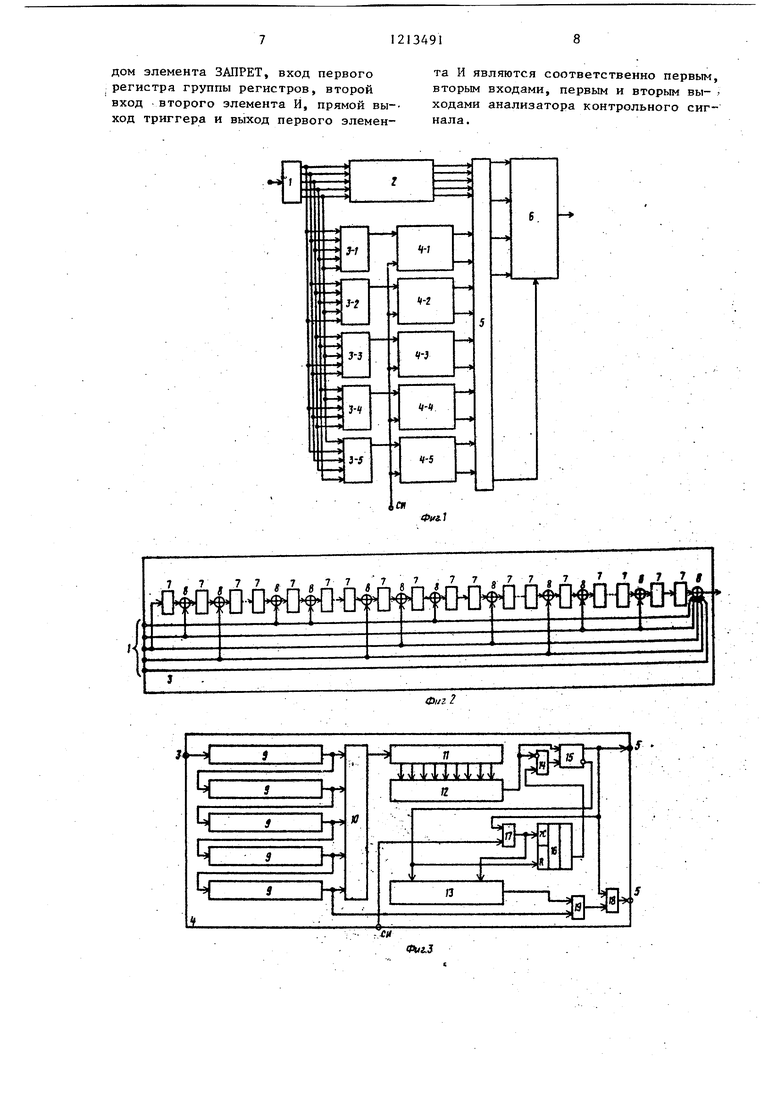

На фиг. 1 представлена структурная схема устройства для декодиро- - вания сверточного кода; на фиг. 2 - функциональная схема формирователя контрольного сигнала; на фиг. 3 - функциональная схема анализатора контрольного сигнала; на фиг. 4 - функциональная схема-коммутационной

матрицьь

Устройство для декодирования сверточного кода содержит (фиг. 1) преобразователь 1 последовательного кода в параллельный, блок 2 задержки, формирователи 3 контрольного сигнала (синдрома), анализаторы 4 контрольного сигнала (синдрома), блок 5 коммутации и декодер 6.

Формирователь 3 контрольного сигнала содержит (фиг. 2) триггеры 7 и сумматоры 8 по модулю два.

Анализатор 4 контрольного сигнала (фиг. 3) содержит регистры 9, мажоритарный элемент 10, регистр 11, дешифратор 12, генератор 13 фазирующей последовательности импульсов, элемент ЗАПРЕТ 14, триггер 15 счетчик 16, элементы И 17 и 18 и сумматор 19 по модулю два.

Блок 5 коммутации содержит ,1 (фиг. 4) группы 20 элементов И 21 и элементы ИЛИ 22 и 23.

Блок 2 задержки может быть вьшол- нен на регистрах сдвига и предназначен для задержки принимаемых информационных последовательностей на время вхождения в синхронизм.

Анализаторы 4 контрольного сигнала предназначены для определения истинных номеров принимаемых последовательностей.

Блок 5 коммутации переключает входные кодовые последовательности и последовательности символов синдрома на соответствующие входы декодера 6 по управляющим сигналам с анализаторов 4 синдрома.

Декодер 6 декодирует пороговым методом поступающие из блока 2 задержки информационные последовательности.

Устройство работает следующим образом.

На вход преобразователя 1 после довательного кбда. в параллельный

из канала связи поступает последова- тельность символов. Если прием начат в случайный момент времени, то мак- симальньй .сдвиг истинных номеров последовательностей может оказаться

равным четырем.(фиг. 1). Поэтому необходимо одновременно производить пять попыток определения фазового положения путем формирования различных синдромов со сдвигом на один ,

номер.

Синдромы {с- (D)}, где ,...,5, формируются в формирователях 3, на входы которых поступают кодовые комбинации с преобразователя 1 со

сдвигом номеров на единицу. В формирователях 3 (фиг. 2) выполняется операция умножения этих комбинаций на образующие полиномы с последующим суммированием. Сформированные синдромы (контрольные сигналы) поступают в анализаторы 4, где записываются в пять последовательно соединенных регистров 9 памяти. Длина каждого регистра 9 равна длине фазирующей последовательности P(D), а общая длина равна примерно длине синдрома, формируемого за время, равное кодовому ограничению. Так как выходы последних разрядов регистров 9

через мажоритарный элемент 10 связаны с входом регистра 11, то при последовательном прохождении через них последовательности синдрома, в регистр 11 будет записьшаться результат мажоритарной обработки пяти повторений фазир ощей последовательности, искаженных символами последовательности S(D), сформированный по критерию три из пяти. При этом

данный результат будет также циклически сдвигаться по мере продвижения последовательности C(D). При полном исправлении ошибок в фазирующей последовательности и ее фазовом

положении в регистре 11 это положение фиксируется дешифратором 12. С выхода дешифратора 12 сигнал о фазовом положении поступает на единичный вход триггера 15 и инверсный вход

элемента ЗАПРЕТ 14. При этом триггер 15 переводится в единичное состояние и сигнал с его едршичного выхода поступает через выход анализатора 4 синдрома на управляющий вход блока 5 коммутации (фиг. 1), который перераспределяет соответствующим образом входные кодовые последовательности,- поступающие в де- 5 кодер 6 с выходов блока 2 задержки. Этот же сигнал с прямого выхода триггера 15 поступает на Г| ервый вход элемента 17 (фиг. 3), разрешая прохождение синхроимпульсов тактовой частоты на счетный вход счетчика 16 и на вход генератора 13 фазирующей последовательности. При этом счетчик 16, емкость которого равна числу разрядов фазирующей последова- 15 тельности P(D), вьадает импульсы переполнения на прямой вход элемента ЗАПРЕТ 14. Если фазовое положение установлено правильно, то сигнал на выходе дешифратора 12 будет по- 20 являться с периодом повторения фази- рзпощей последовательности и, поступая на инверсный вход элемента ЗАПРЕТ 14, будет запрещать прохождение импульса переполнения на нулевой 25 вход триггера 15. Таким образом, при подтверждении фазового положения дешифратора 12 с частотой, равной периоду следования фазовЬй последовательности, триггер 15 будет 30 оставаться в единичном состоянии. Кроме того, синхроимпульсы с выхоа элемента И 17 поступают в генератор 13 фазирующей последовательности, обеспечивая выдачу генератором 13 35 фазирующей последовательности Р(в) на первый вход сумматора 19 по моду- лю два, на второй вход которого поступает синдром C(D) с выхода последнего регистра 9. Сумматор 19 вычитает 40 фазирующую последовательность из синдрома и на его выходе появляются символы последовательности S(D), которые через элемент И 18, открытый сигналом с единичного выхода тригге- 45 ра 15, поступают на вход блока 5 коммутации, который выдает их в декодер 6 для коррекции ошибок в информационных последовательностях.

Если в процессе приема информации 50 происходит вставка или выпадение некоторого числа символов, не кратного ПЯТИ, установленная цикловая синхронизация нарушится, т.е. истинный синдром будет теперь формироваться 55 в другом формирователе 3 синдрома. В этому случае анализатор 4 синдрома, который вьщелял до моменту сбоя синхронизма истинный синдром,- обнаруживает сбой синхронизма за время, не превышающее Нд/2, так как при заполнении трех и более регистров 9 синдрома последовательностями,не равным истинному значению С(ю), последовательность P(D) дешифратором 12 обнаружена не будет. Это прршедет к /тому, что во время поступления очередного импульса переполнения со счетчика 16, элемент ЗАПРЕТ J4 останется открытьм и триггер 15 будет переведен в нулевое положение. При этом исчезновение сигнала на его прямом выходе приведет к тому, что блок 5 коммутации прекратит выдачу в декодер 6 входных информационных последовательностей, закроется элемент И 18i, запрещая прохождение сйнД рома на вход блока 5 коммутации, и закроется элемент И 17, запрещая прохождение синхроимпульсов на входы счетчика 15 и генератора 13 фазирующего сигнала. Единичный сигнал, появляющийся при этом на инверсном выходе триггера 15, устанавливает генератор 13 и счетчик 16 в исходное состояние.

Если причиной сбоя синхронизма были вставки нли выпадения символов, приводящие к нарушен11ю узловой синхронизации, то не позднее, чем через N А символов с момента возникновения сбоя истинный синдром будет выделен в одном из четырех анализаторов 4 синдромов, в которых ранее было зарегистрировано отсутствие синхронизма. При этом процесс опознания нового истинного синдрома будет происходить аналогично как и в предьщущем случае, после чего блок 5 коммутации перераспределит входные информационные последовательности с выходов блока 2 задержки, в соответствии с номерами входов декодера 6. Информационные последовательности поступают с выходов блока 2 задержки на соответствующие входы групп 20. элементов И 21. Вторые твходы групп 20 элементов И 21 соединены с управляющими выходами анализаторов 4 синдромов . Прт опознании в одном из анализаторов 4 синдромов истинного синдрома на один из входов блоков 5 коммутации поступает управляющий сигнал, открывающий соответствующие элементы И 21. При опознании истинного синдрома на один из сйндромных

входов блока 5 коммутации поступает последовательность символом синдрома S(D), которая через элемент ИЛИ 23 поступает на декодер 6. При обнаружении сбоя синхронизма управляющий сигнал на управляющем входе блока 5 коммутации и символы синдрома S(D) на его синдромном входе исчезают и выдача информационных последовательностей на входы декодера 6 прекращается. Как только в дру- гом анализаторе А синдрома, соответствующем новому распределению входных последовательностей, будет опознан истинный синдром C(D), на другом управляющем входе блока 5 коммутации появится управляющий сигнал, а на другом синдромном входе блока 5 появится последовательность S(D), которая с вновь перераспределенными входными последовательностями бу- дет подаваться на соответствующие входы декодера 6.

Предлагаемое устройство позволяет с бЬльшей достоверностью по сравнению с известным осуществлять поиск фазового положения за время, не превышающее длины кодового ограничения N; используемого сверточного кода. Кроме того, изобретение позволяет производить синхронизацию высокоскоростных сверточных кодов, использующих пороговое декодирование со скоростями передачи Н(по-1)/ПоПри , в то время, как известное устройство применимо для ограниченного класса сверточных кодов со скоростью передачи и требует значительно большего времени вхождения в синхронизм .

Формула изобретения

1. Устройство для декодирования сверточного кода, содержащее преобразователь последовательного кода в параллельный, вход которого является информационным входом устройства, выходы преобразователя последовательного кода в параллельный соединены с соответствующими входами блока задержки, и декодер, выход которого является выходом устройства, отличающееся тем, что, с целью повышения быстродействия и надежности устройства, в него введены формирователи контрольного сигнала, анализаторы контрольного сигнала и блок коммутации, соответствующие входы

формирователей контрольного сигнала объединены и подключены к соответствующим выходам преобразователя последовательного кода в параллельнь1й, выходы формирователей контрольного

сигнала соединены с первыми входами соответствующих анализаторов контрольного сигнала, вторые входы которых объединены и являются синхронизирующим входом устройства, первые

И вторые выходы анализаторов контрольного сигнала и выходы блока задержки соединены соответственно с первыми, вторыми и третьими входами блока коммутации, первый и второй выходы которого соединены с соответ-f ствующими информационными и управляю , щим входами декодера.

2. Устройство по п. 1, о т л и -

чающееся тем, что анализатор контрольного сигнала содержит регистр, мажоритарный элемент, группу регистров, дешифратор, генератор импульсов, элементы И, сумматор, счетчик, триггер и элемент ЗАПРЕТ, выход каждого регистра группы соединен с входом каждого последующего регистра группы и соответствующим входом мажо- ритарного элемента, выход мажоритарного элемента соединен с входом регистра, выходы которого соединены с соответствующими входами деши4)ратора, выход дешифратора соединен с входом установки в 1 триггера и инверсным

входом элемента ЗАПРЕТ, выход элемента ЗАПРЕТ соединен с входом установки в О триггера, прямой и инверсный выходы триггера соединены соответственно с объединенными первыми входами первого, второго элемента И и с объединенными входом установки в О счетчика и входом установки в исходное состояние генератора импульсов, выход генератора импульсов соединен

с первым входом сумматора, второй вход которого подключен к выходу последнего регистра группы регистров, выход сумматора соединен с вторым. в ходсГм первого элемента И, выход второго элемента И соединен с синхронизирующим входом генератора импульсов и счетным входом счетчика, выход счетчика соединен с прямым вхо712134918

дом элемента ЗАПРЕТ, вход первогота И являются соответственно первым регистра группы регистров, второйвторым входами, первым и вторым вы- . вход второго элемента И, прямой вы-.ходами анализатора контрольного сиг- ход триггера и выход первого элемен-нала.

| название | год | авторы | номер документа |

|---|---|---|---|

| Кодек несистематического сверточного кода | 1990 |

|

SU1714812A1 |

| Пороговый декодер сверточного кода | 1989 |

|

SU1667264A1 |

| Пороговый декодер сверточного кода | 1982 |

|

SU1078654A1 |

| Декодер сверточного кода (его варианты) | 1985 |

|

SU1320875A1 |

| Декодер сверточного кода | 1985 |

|

SU1320904A1 |

| Устройство для приема сигналов с частотно-фазовой модуляцией | 1988 |

|

SU1555902A2 |

| Устройство для устранения неопределенности дискретнофазовой модуляции | 1983 |

|

SU1095428A1 |

| Кодек несистематического сверточного кода | 1988 |

|

SU1580567A1 |

| ПОРОГОВЫЙ ДЕКОДЕР СВЕРТОЧНОГО КОДА | 1991 |

|

RU2023349C1 |

| Устройство для адаптивного мажоритарного декодирования фазирующих сигналов | 1984 |

|

SU1213492A1 |

Изобретение относится к электросвязи и может использоваться в .системах передачи цифровой видеоинформации. Изобретение позволяет повысить достоверность поиска синхронизма за время, не превьппающее длины кодового ограничения используемого сверточного кода. Устройство содержит преобразователь последовательного кода в параллельный, блок задержки, формирователи контрольно го сигнала анализаторы контрольного сигнала, блок коммутации и декодер. Формирователь контрольного сигнала содержит триггеры и сумматоры по модулю два. Анализатор контрольного сигнала содержит регистры, мажоритарный элемент, регистр, дешифратор, генератор фазирующей последовательности импульсов, элемент ЗАПРЕТ, триггер, счетчик, элементы И и сумматор по модулю два. Блок комму- .х тации содержит группы элементов И и элементы ИЛИ. 1 з.п. ф-лы. 4 ил. а (Л tvD СО

Ч

Редактор Н. Данкулич

Составитель М. Никуленков

Техред С.Мигунова Корректор Е. Рошко

Заказ 782/58. Тираж 516 Подписное ВНИИПИ Тосударственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. А/5

Филиал ШШ Патент, г. Ужгород, ул. Проектная, 4

| Устройство узловой синхронизации сверточного декодера | 1973 |

|

SU467484A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Устройство для узловой синхронизации сверточного декодера | 1979 |

|

SU924888A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1986-02-23—Публикация

1984-08-09—Подача