Изобретение относится к сштомати ке и вычислительной технике и предназначено для использования в качесве универсального логического эле- мента при синтезе нерегулярных струтур диск ретных устройств.

Це.пь изобретения - упрощение модули.

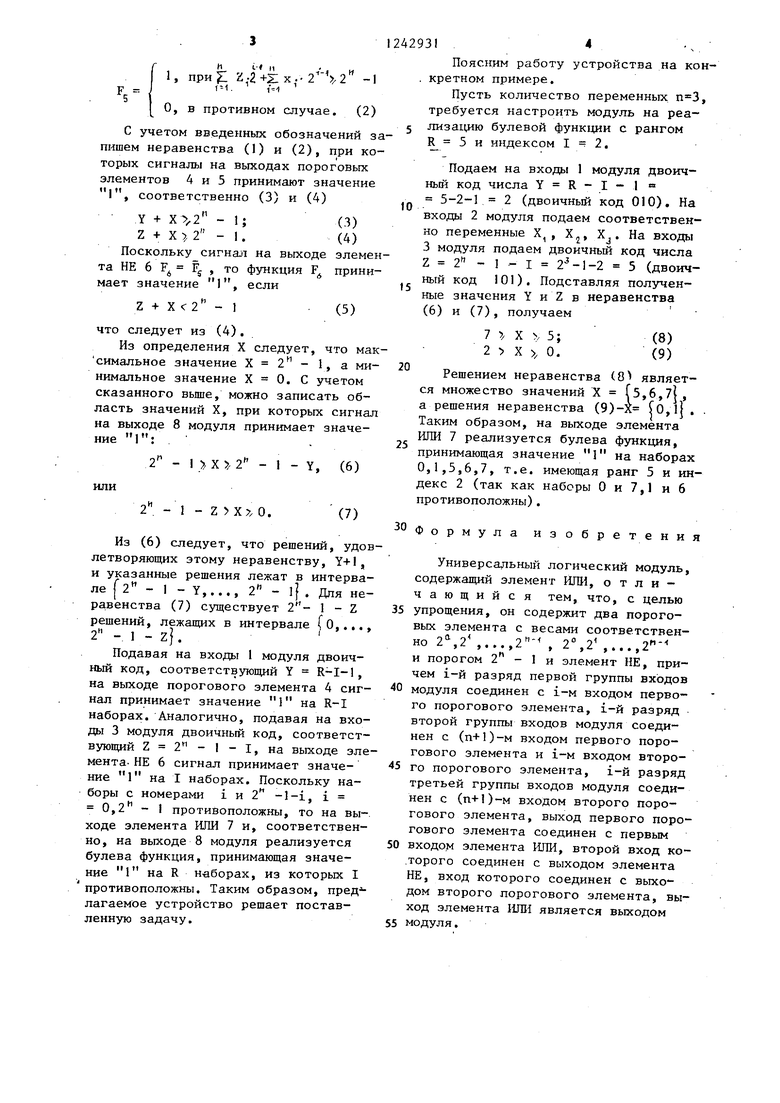

На чертеже приведена схема универсального логического модуля.

Модуль имеет входы 1-3, пороговы элементы 4 и 5, элемент НЕ 6, элемент ИЛИ 7 и выход 8,

Пороговые элементы 4 и 5 являются стандартными элементами вычислительной техники и могут быть выполнены по любой известной схеме.

Нумерация входов пороговых элеметов ведется последовательно сверху вниз, т.е. вес п ервого (сверху на чертеже) входа порогового элемента 2°, второго - 2 и т.д.,...,, п-го 2 , (п+1)-го 2°, (п+2)-го 2 и т.д.,..., 2п-го 2 . Возле аждого входа порогового элемента указан ег вес.

Входы 1-3 модуля имеют по п разрядов, причем значение i-ro разряда имеющего вес 2 , поступает по со- ответствующему входу на ,вход nojppro вого элемента с весом ,(,n), т.е. с тем же весом.

Рассмотрим работу универсального логического модуля.

При описании работы использованы следующие обозначения: v.; - вес i-ro входа порогового элемента, Т - порог, - значение сигнала на 1-м разряде входов 1 модуля,

у., 1, i 1, п;

и .

дьсятичный эквива1 -1

лент двоичного числа, поступающего на входы 1 модуля; х| - значение сигнала на i-M разряде входов 2 модуля

x.,lj , i 1,п;

х. 2 - десятичный эквива1 1

лент двоичного числа, поступающего на входы 2 модуля; Zy - значение сигнала на i-м разряде входов 3 мо- ДУЛЯ,

Z- 0,, i 1,п;

-- десятичный эквивалент

(1

двоичного числа, поступающего на входы 3 модуля„

Рд - значение сигнала на выходе порогового элемента 4, F - значение сигнала на выходе порогового элемента 5, F, - значение сигнала

ь

на вьпсоде элемента НЕ 6, F - значение сигнала на выходе элемента ИПИ 7„ равное значению сигнала на выходе 8 модуля.

Предлагаемы универсальный логический модуль предназначен для реализации К„ типов булевых функций. Типовые булевые функции относительно группы Kjj преобразований однозначно определяются двумя параметрами: рангом и индексом. Рангом булевой функции называется количество конституент единицы в ее совершенной дизъюнктивной нормальной форме (СДНФ). Индексом называется число пар противоположных конституент единицы в ее СДНФ. Две булевых функции относятся к одному типу, если их ранги и :нндексы совпадают.

Для реализации типа булевой функ1щи с рангом R и индексом I на входы 1 модуля подается двоичный п-раз- рядный код числа R - I - 1, на входы 2 модуля подаются переменные х, , x.,,..,,,Xj (на i-й разряд входов 2

модуля подается переменная , i 1,1)9 а. входа 3 модуля подается двоичный п-разрядный код числа - j

Z - 1 - 1.

Докажем, что при этом на выхо де 8 модуля регшизуется типовая бу- левая функция с рангом R и индексом I,

В общем случае сигнал на выходе m входового порогового элемента с ве- CaNOi входов у , v ,.,., v и порогом

Т определяется следующим образом:

F

1, если2: v-ХрД

о, в противном случае.

Йля пороговых элементов 4 и 5 с учетом весов их входов можно записать .

f 1,при2: Z.-2 Vix,-2 h -1 1 1 1 i-.1

о, в противном случае; (1)

I.- М

1-1 n И

1, при 2.2+2:х.-2 Л2 -1

1-1. I-о, в противном случае. (2)

С учетом введенных обозначений запишем неравенства (1) и (2), при которых сигналы на выходах пороговых элементов 4 и 5 принимают значение 1, соответственно (3) и (4)

Y + - 1;(3) Z + X ), 2 - I.(4) Поскольку сигнал на выходеэлемента НЕ 6 F FJ , то функция Р принимает значение I, если

Z + X с 2 - 1

(5)

что следует из (4).

Из определения X следует, что мак- симальное значение X 2 - 1, а минимальное значение X 0. С учетом сказанного вьше, можно записать область значений X, при которых сигнал на выходе 8 модуля принимает значение 1 :.

2 - 1 Х5. 2 - 1 - Y, (6)

или

2 - 1 - Z Хг 0.

(7)

Из (6) следует, что решений, удовлетворяющих этому неравенству, Y+1, и указанные решения лежат в интервале 2 - 1 - Y,..., 2 - l| . Для неравенства (7) существует 1 - Z решений, лежащих в интервале (о,.,., 2 -. I - ZJ .

Подавая на входы 1 модуля двоичный код, соответствующий Y R-I-1, на выходе порогового элемента 4 сигнал принимает значение 1 на R-I наборах. Аналогично, подавая на входы 3 модуля двоичный код, соответствующий Z 2 - I - I, на выходе элемента- НЕ 6 сигнал принимает значение 1 на I наборах. Поскольку наборы с номерами i и 2 -1-i, i 0,2 - I противоположны, то на выходе элемента ИЛИ 7 и, соответственно, на выходе 8 модуля реализуется булева функция, принимающая значение 1 на R наборах, из которых I противоположны. Таким образом, лагаемое устройство решает поставленную задачу.

10

t5

4293 Поясним работу устройства на кон- . кретном примере.

Пусть количество переменных , требуется настроить модуль на реа- 5 лизаьщю булевой функции с рангом R 5 и индексом I - 2.

Подаем на входы 1 модуля двоич- ньп код числа Y R - I - 1 5-2-1 2 (двоичный код 010). На входы 2 модуля подаем соответственно переменные Х, Х, Xj. На входы 3 модуля подаем двоичный код числа Z 2 - 1 - I 5 (двоичный код 101), Подставляя полученные значения Y и Z в неравенства (6) и (7), получаем

7 / X , 5;(8)

2 X , 0. (9)

Решением неравенства (8 является множество значений X (5,6,7(, а решения неравенства (9)-Х fO,l| . . Таким образом, на выходе элемента ИЛИ 7 реализуется булева функция, принимающая значение 1 на наборах 0,1,5,6,7, т.е. имеющая ранг 5 и индекс 2 (так как наборы О и 7,1 и 6 противоположны).

° Формула изобретения

Универсальный логический модуль, содержащий элемент ИЛИ, отличающийся тем, что, с целью 35 упрощения, он содержит два пороговых элемента с весами соответственoft о ат- 9° 9 - НО i. ,/ ,...,/ , / , ,...,

И порогом 2 - 1 и элемент НЕ, причем i-й разряд первой группы входов

40 модуля соединен с i-м входом первого порогового элемента, i-й разряд второй группы входов модуля соединен с (п+1)-м входом первого порогового элемента и i-м входом второ45 го порогового элемента, i-й разряд третьей группы входов модуля соединен с (п+1)-м входом второго порогового элемента, выход первого порогового элемента соединен с первым

50 входом элемента ИЛИ, второй вход которого соединен с выходом элемента НЕ, вход которого соединен с выходом второго порогового элемента, выход элемента ИЛИ является выходом

55 модуля.

Редактор Е.Папп

Составитель О.Березикова Техред Н.Вонкало

Заказ 3705/47 Тиралс 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий М3035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие,, г.Ужгород, ул.Проектная, 4

Корректор А.Зимокосов

| название | год | авторы | номер документа |

|---|---|---|---|

| Универсальный логический модуль | 1985 |

|

SU1290289A1 |

| Универсальный логический модуль | 1986 |

|

SU1345187A1 |

| Универсальный логический модуль | 1978 |

|

SU813410A1 |

| Логический модуль | 1984 |

|

SU1242929A1 |

| Устройство для вычисления булевых дифференциалов | 1988 |

|

SU1689942A1 |

| Преобразователь формы представления логических функций | 1987 |

|

SU1474671A1 |

| МНОГОФУНКЦИОНАЛЬНОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2015 |

|

RU2610247C1 |

| Логический элемент | 1985 |

|

SU1343550A1 |

| Модуль для логических преобразований булевых функций | 1989 |

|

SU1667050A1 |

| САМОПРОВЕРЯЕМЫЙ СПЕЦИАЛИЗИРОВАННЫЙ ВЫЧИСЛИТЕЛЬ СИСТЕМ БУЛЕВЫХ ФУНКЦИЙ | 2012 |

|

RU2485575C1 |

Изобретение относится к автоматике и вычислительной технике и предназначено для использования в качестве универсального логического элемента при синтезе нерег лярных структур дискретных устройств. Цель изобретения - упрощение устройства. Устройство содержит три группы входов модуля, два пороговых элемента, элемент НЕ, элемент ШШ и выход модуля. Оно предназначено для реализации К „-типов булевых функций, причем типовые булевые функции относительно группы К преобразований однозначно определяются рангом и индексом.I ил. (Л с: ю 4ib ГС CD СО

| МНОГОФУНКЦИОНАЛЬНЫЙ ЛОГИЧЕСКИЙ МОДУЛЬ | 1972 |

|

SU430376A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Универсальный логический модуль | 1978 |

|

SU813410A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-07-07—Публикация

1984-12-19—Подача