Изобретение относится к автоматике и вычислительной технике и предназначено для использования в качестве универсального логического элемента при синтезе нерегулярных структур дискретных устройств.

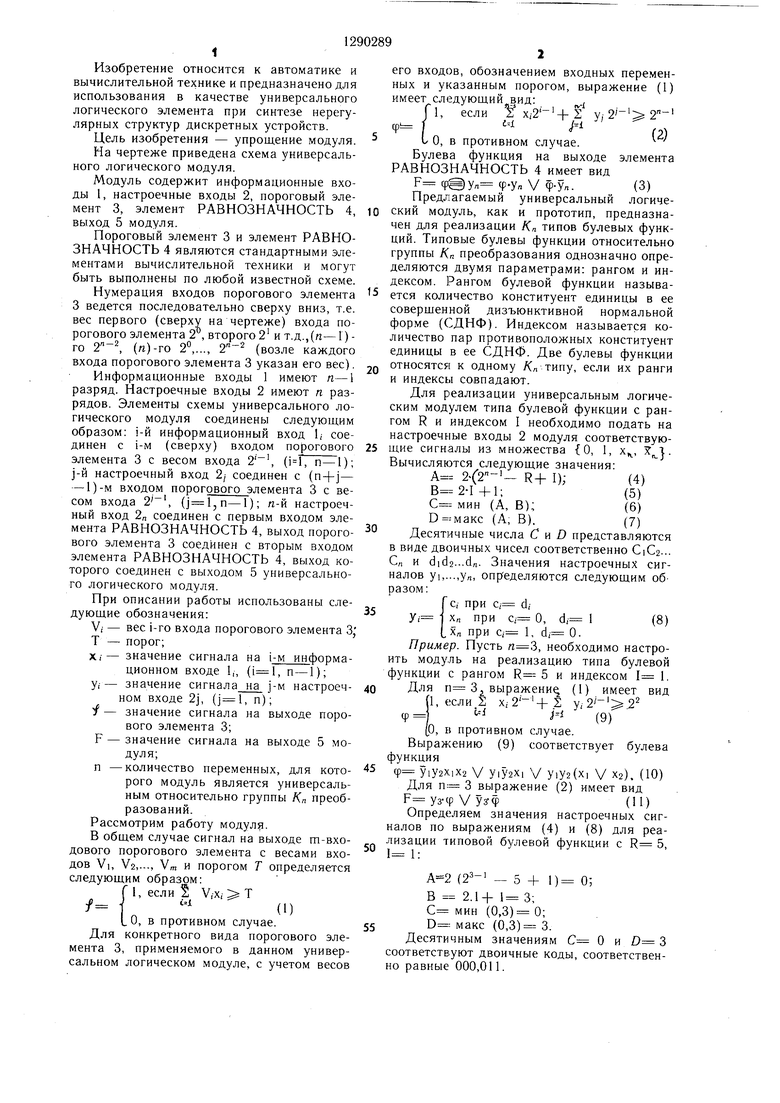

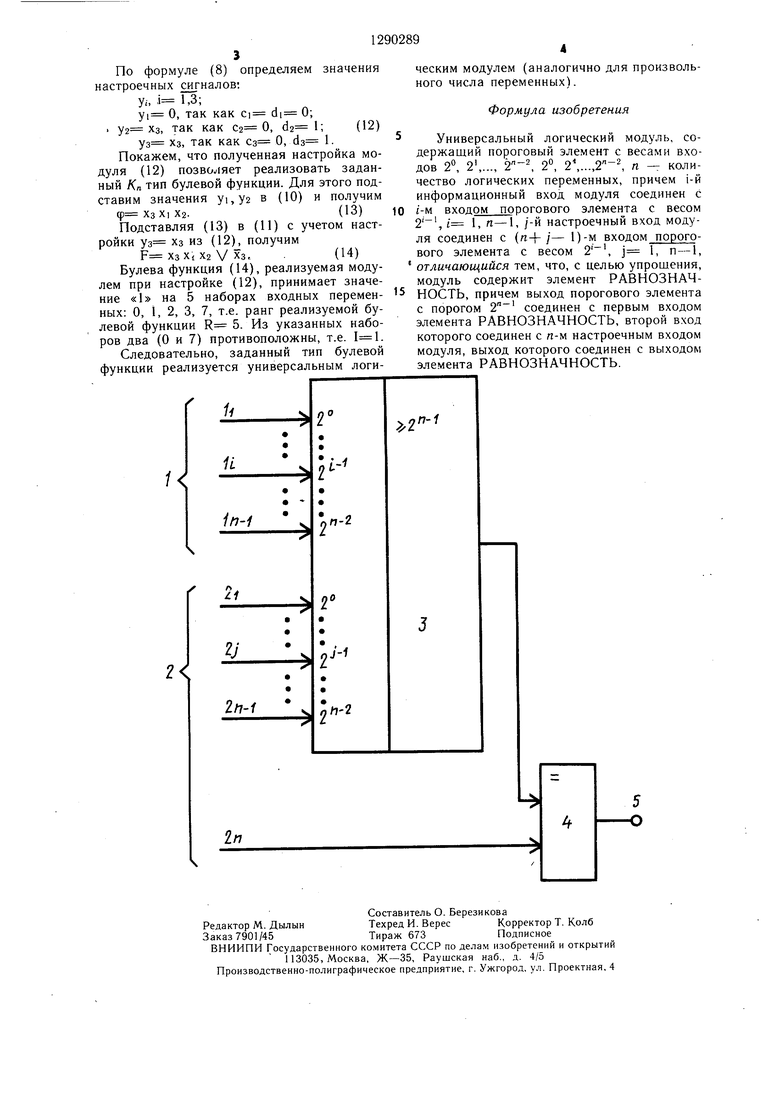

Цель изобретения - упрощение модуля. На чертеже приведена схема универсального логического модуля.

Модуль содержит информационные входы 1, настроечные входы 2, пороговый элемент 3, элемент РАВНОЗНАЧНОСТЬ 4, выход 5 модуля.

Пороговый элемент 3 и элемент РАВНОЗНАЧНОСТЬ 4 являются стандартными элементами вычислительной техники и могут быть выполнены по любой известной схеме.

Нумерация входов порогового элемента 3 ведется последовательно сверху вниз, т.е. вес первого (сверху на чертеже) входа порогового элемента 2 , второго 2 и т.д.,(п-Г) - го , (л)-го 2°,..., 2 (возле каждого входа порогового элемента 3 указан его вес). Информационные входы 1 имеют п-1 разряд. Настроечные входы 2 имеют п разрядов. Элементы схемы универсального логического модуля соединены следующим образом: i-й информационный вход 1, соединен с i-M (сверху) входом порогового элемента 3 с весом входа , (, п-1); j-й настроечный вход 2/ соединен с (n+j- - 1)-м входом порогового элемента 3 с весом входа , (1,п-1); п-й настроечный вход 2„ соединен с первым входом элемента РАВНОЗНАЧНОСТЬ 4, выход порого- вого элемента 3 соединен с вторым входом элемента РАВНОЗНАЧНОСТЬ 4, выход которого соединен с выходом 5 универсального логического модуля.

При описании работы использованы следующие обозначения:

Vj - вес i-ro входа порогового элемента 3

Т - порог;

X;- значение сигнала на i-м информационном входе 1„ (, п-1); У;- значение сигнала на |-м настроеч-

ном входе 2j, (, п); i - значение сигнала на выходе порового элемента 3;

F - значение сигнала на выходе 5 модуля;

п -количество переменных, для которого модуль является универсальным относительно группы /(„ преобразований.

Рассмотрим работу модуля. В общем случае сигнал на выходе ш-вхо- дового порогового элемента с весами входов Vi, Уг,.-., Vm и порогом Т определяется следующим образом:

Г I, если S V,x,T / (1)

1 О, в противном случае.

Для конкретного вида порогового элемента 3, применяемого в данном универсальном логическом модуле, с учетом весов

0

5 0

0

5

его входов, обозначением входных переменных и указанным порогом, выражение (1) имеет следующий вид:

5

5

0

Г 1, если Xi2 - 4- 2 у/ 2- 2

|Л-1

i-i -i

I/ о, в противном случае.

(2)

Булева функция на выходе элемента РАВНОЗНАЧНОСТЬ 4 имеет вид

F Ф®УЯ Ф-У« V Ф-УЯ.(3)

Предлагаемый универсальный логический модуль, как и прототип, предназначен для реализации К.п типов булевых функций. Типовые булевы функции относительно группы Кп преобразования однозначно определяются двумя параметрами: рангом и индексом. Рангом булевой функции называется количество конституент единицы в ее соверщенной дизъюнктивной нормальной форме (СДНФ). Индексом называется количество пар противоположных конституент единицы в ее СДНФ. Две булевы функции относятся к одному /(я типу, если их ранги и индексы совпадают.

Для реализации универсальным логическим модулем типа булевой функции с рангом R и индексом I необходимо подать на настроечные входы 2 модуля соответствующие сигналы из множества {О, 1, х, } Вычисляются следующие значения:

А- 2.( R+ I);(4)

В 2-1+1;(5)

С мин (А, В);(6)

(А, В).(7)

Десятичные числа Си) представляются в виде двоичных чисел соответственно CiC2... С,1 и did2...dn. Значения настроечных сигналов у1,...,уп, опр еделяются следующим образом:

(с, при с, d,- х„ при с, О, d, 1(8)

х„ при с,- 1, d/ 0. Пример. Пусть , необходимо настроить модуль на реализацию типа булевой функции с рангом R 5 и индексом 1 1. Для Г1 Зд выражение (1) имеет вид

(1, если S х; 2- -f Z у, 2 (9)

О, Hi противном случае. Выражению (9) соответствует булева функция

ф У1У2Х1Х2 V У1У2Х1 V У1У2(Х| V Х2). (Ю)

Для п: 3 выражение (2) имеет вид

Р уз фУугф(И)

Определяем значения настроечных сигналов по выражениям (4) и (8) для реа- .пизации типовой булевой функции с R 5, 1:

( - 5 + 1) 0;

В 2.1+ 1 3;

С мин (0,3) 0;

D макс (0,3) 3.

Десятичным значениям С О и D 3 соответствуют двоичные коды, соответственно равные 000,011.

По формуле (8) определяем значения настроечных сигналов: У;, i 1,3;

У О, так как ci di 0; У2 хз, так как С2 О, d2 1; (12)

УЗ Хз, так как сз О, d3 1. Покажем, что полученная настройка модуля (12) позволяет реализовать заданный /(„ тип булевой функции. Для этого подставим значения yi,y2 в (10) и получим

ф ХзХ1Х2.(13)

Подставляя (13) в (11) с учетом настройки УЗ Хз из (12), получим

F xaXt Х2 V Хз. .(14)

Булева функция (14), реализуемая модулем при настройке (12), принимает значе10

ческим модулем (аналогично для произвольного числа переменных).

Формула изобретения

Универсальный логический модуль, содержащий пороговый элемент с весами входов 2, 2,..., , 2°, 2..., п - количество логических переменных, причем i-й информационный вход модуля соединен с J-M входом порогового элемента с весом , 1 1, п-1, /-Й настроечный вход модуля соединен с j- 1)-м входом порого- вого элемента с весом , j 1, п--1, отличающийся тем, что, с целью упрощения.

модуль содержит элемент РАВНОЗНАЧние «1 на 5 наборах входных перемен- 5 НОСТЬ, причем выход порогового элемента

ных: О, 1, 2, 3, 7, т.е. ранг реализуемой бу-с порогом соединен с первым входом

левой функции R 5. Из указанных набо-элемента РАВНОЗНАЧНОСТЬ, второй вход

ров два (О и 7) противоположны, т.е. .которого соединен с п-м настроечным входом

Следовательно, заданный тип булевоймодуля, выход которого соединен с выходом

функции реализуется универсальным логи-элемента РАВНОЗНАЧНОСТЬ.

ческим модулем (аналогично для произвольного числа переменных).

Формула изобретения

Универсальный логический модуль, содержащий пороговый элемент с весами входов 2, 2,..., , 2°, 2..., п - количество логических переменных, причем i-й информационный вход модуля соединен с J-M входом порогового элемента с весом , 1 1, п-1, /-Й настроечный вход модуля соединен с j- 1)-м входом порого- вого элемента с весом , j 1, п--1, отличающийся тем, что, с целью упрощения.

модуль содержит элемент РАВНОЗНАЧ

| название | год | авторы | номер документа |

|---|---|---|---|

| Универсальный логический модуль | 1986 |

|

SU1345187A1 |

| Универсальный логический модуль | 1984 |

|

SU1242931A1 |

| Логический модуль | 1984 |

|

SU1242929A1 |

| Универсальный логический модуль | 1978 |

|

SU813410A1 |

| Универсальный логический модуль | 1986 |

|

SU1335974A1 |

| Модуль логического устройства | 1988 |

|

SU1684790A1 |

| Тестопригодное логическое устройство | 1986 |

|

SU1451695A1 |

| МНОГОФУНКЦИОНАЛЬНОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2015 |

|

RU2610247C1 |

| Универсальный логический модуль | 1986 |

|

SU1319019A1 |

| Универсальный логический модуль | 1984 |

|

SU1234825A1 |

Изобретение относится к автоматике и вычислительной технике и предназначено для использования в качестве универсального логического элемента при синтезе нерегулярных структур дискретных устройств. Цель изобретения - упрощение модуля. Устройство содержит информационные входы, настроечные входы, пороговый элемент, элемент РАВНОЗНАЧНОСТЬ, выход модуля. Универсальный логический модуль реализует при соответствующей настройке типовые булевы функции относительно группы К„ преобразований. Настройка модуля состоит в подаче на настроечные входы модуля соответствующих сигналов из множества (О, 1, Х„, ХДпри этом на выходе модуля формируется булева функция с заданным рангом и индексом. 1 ил. U-jcX к ю 00

| Универсальный логический модуль | 1978 |

|

SU813410A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Универсальный логический модуль | 1984 |

|

SU1242931A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-02-15—Публикация

1985-05-08—Подача