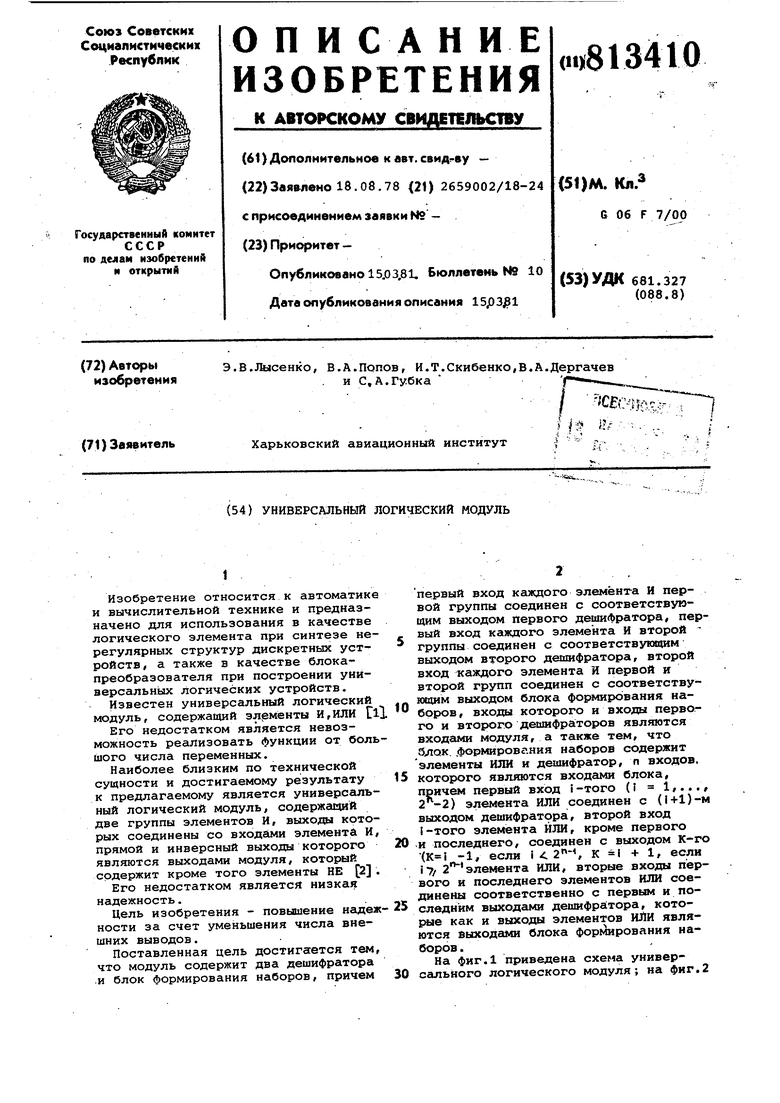

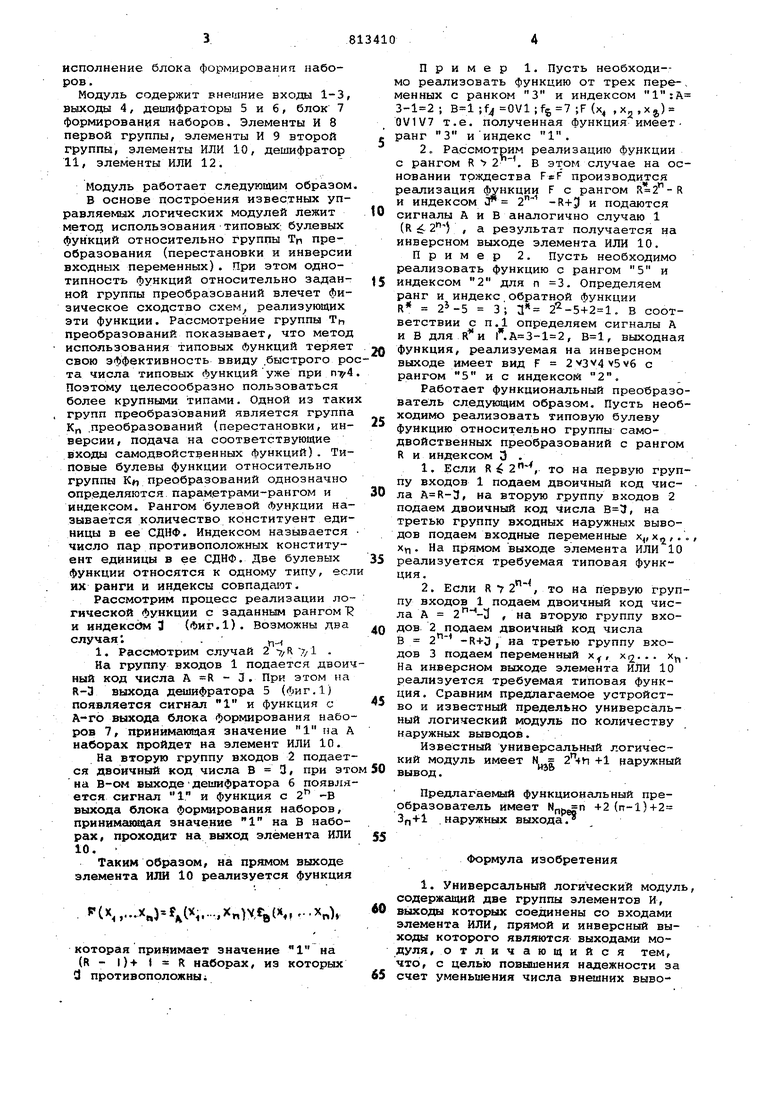

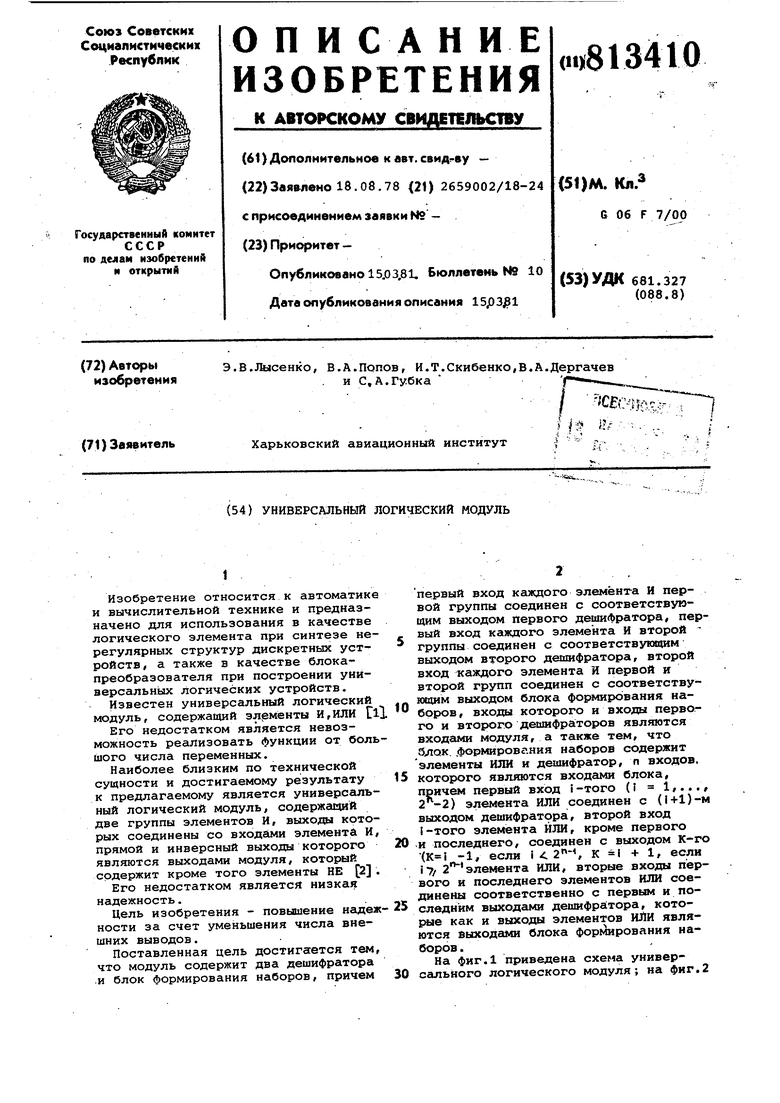

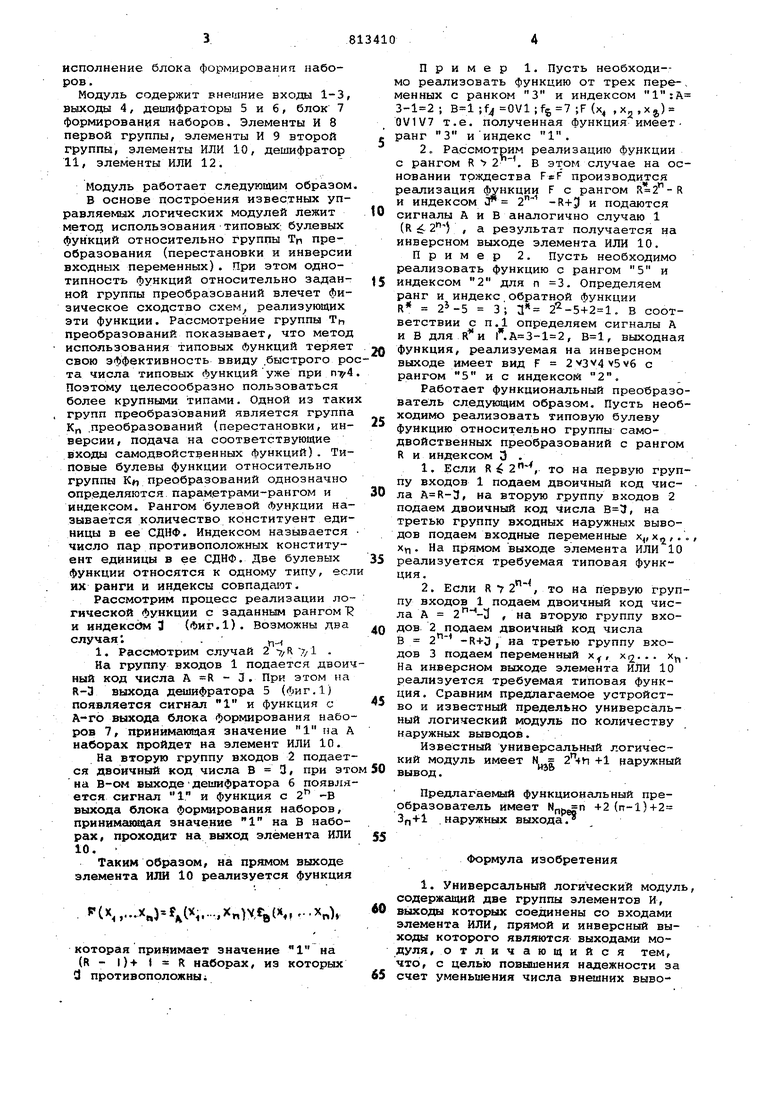

Изобретение относится к автоматике и вычислительной технике и предназначено для использования в качестве логического элемента при синтезе нерегулярных структур дискретных устройств, а также в качестве блокапреобразователя при построении универсальных логических устройств. Известен универсальный логический модуль, содержащий элементы И,ИЛИ 11 Его недостатком яв.Ьяется невозможность реализовать функции от боль шого числа переменных. Наиболее близким по технической сущности и достигаемому результату к предлагаемому является универсальный логический модуль, содержащий две группы элементов И, выходы которых соединены со входе1ми элемента И прямой и инверсный выходы которого являются выходами модуля, который содержит кроме того элементы НЕ 2 Его недостатком является низкая надежность.. Цель изобретения - повышение надеж ности за счет уменьшения числа внешних выводов. Поставленная цель достигается тем что модуль содержит два дешифратора .и блок формирования наборов, причем первый вход каждого элемента И первой группы соединен с соответствующим выходом первого дешифратора, первый вход каждого элемента И второй группы соединен с соответствующим выходом второго дешифратора, второй вход каждого элемента И первой и второй групп соединен с соответствующим выходом блока формирования наборов , входы которого и входы первого и второго дешифра торов являются входами модуля, а также тем, что блок, .формирования наборов содержит элементы ИЗШ и дешифратор, п входов, которого являются входс№в1 блока, причем первый вход i-того (1 1,... 2-2) элемента ИЛИ соединен с (1+1)-м выходом дешифратора, второй вход 1-того элемента ИЛИ, кроме первого -и последнего, соединен с выходом К-го ( -1, если i 2- К i + 1, если 17/ 2 элемента ИЛИ, вторые входы первого и последнего элементов ИЛИ соединены соответственно с первым и последним выход 1ми дешифратора, которые как и выхода элементов иЛИ являются выходами блока формирования наборов. На фиг.1 приведена схема универсального логического модуля; на фиг.2 исполнение блока формирования наборов. Модуль содержит внешние входы 1-3, выходы 4, дешифраторы 5 и 6, блок 7 формирования наборов. Элементы И 8 первой группы, элементы И 9 второй группы, элементы ИЛИ 10, дешифратор 11, элементы ИЛИ 12. Модуль работает следующим образом В основе построения известных управляемых логических модулей лежит метод использования ТИПОВЫХ; булевых функций относительно группы Тп преобразования (перестановки и инверсии входных переменных). При этом однотипность функций относительно заданной группы преобразований влечет физическое сходство схем реализующих эти функции. Рассмотрение группы Тп преобразований показывает, что метод использования типовых функций теряет свою эф4 ективность ввиду .быстрого ро та числа типовых функций уже при Поэтому целесообразно пользоваться более крупными типами, Одной из таки групп преобразований является группа KO .преобразований (перестановки, инверсии, подача на соответствующие входы самодвойственных функций). Типовые булевы функции относительно группы Kji преобразований однозначно опр.еделяются паранетрами-рангом и индексом. Рангом булевой функции называется количество конституент единицы в ее СДНФ. Индексом называется число пар противоположных конституент единицы в ее СДНФ. Две булевых функции относятся к одному типу, есл их ранги и индексы совпадают. Рассмотрим процесс реализации логической функции с заданным рангом 1 и индексбм 3 (Фиг.1). Возможны два случая; . . 1. Рассмотрим случай 2 7/R7/1 . На группу входов 1 подается двоич ный код числа А R - 3. При этом на R-3 выхода дешифратора 5 (Фиг.1) появляется сигнал 1 и функция с А-го выхода блока формирования набо ров 7, принимающая значение 1 на А наборах пройдет на элемент ИЛИ 10. На вторую группу входов 2 подает ся двоичный код числа В 3, при эт на В-ом выходедешифратора 6 появля ется сигнал 1 и функция с выхода блока формирования наборов, принимающая значение 1 на В наборах, проходит на выход элемента ИЛИ 10. Таким образом, на прямом выходе элемента ИЛИ 10 реализуется функция (,...,--,n)4fa() . которая принимает значение 1 на (R - 1)+ J R наборах, из которых d противоположныi Пример 1. Пусть необходи-мо реализовать функцию от трех пере-, менных с ранкой 3 и индексом B l;f4 OVl;f 7 ;F(x ,X2,Xg,) OV1V7 т.е. полученная функция имеетранг 3 ииндекс 1. 2. Рассмотрим реализацию функции с рангом R 2 . В этом случае на основании тождества FsF производится реализация функции F с рангом и индексом 0 -R+3 и подаются сигналы А и В аналогично случаю 1 (R , а результат получается на инверсном выходе элемента ИЛИ 10. Пример 2. Пусть необходимо реализовать функцию с рангом 5 и индексом 2 для л 3. Определяем ранг и индекс обратной функции R 3; 3 . В соответствии с п.1 определяем сигналы А и В для |., , выходная функция, реализуемая на инверсном выходе имеет вид F 2v3V4v5v6 с рангом 5 и с индексом 2. Работает функциональный преобразователь следующим образом. Пусть необходимо реализовать типовую булеву функцию относительно группы самодвойственных преобразований с рангом R и индексом 3 . 1.Если Я 4 , то на первую группу входов 1 подаем двоичный код числа , на вторую группу входов 2 подаем двоичный код числа , на третью группу входных наружных выводов подаем входные переменные х,,х,,.., Xfl. На прямом выходе элемента ИЛИ 10 реализуется требуемая типовая функция. 2.Если R 7 , то на первую группу входов 1 подаем двоичный код числа А 2 -З , на вторую группу входов 2 подаем двоичный код числа -R+Э , на третью группу входов 3 подаем переменный На инверсном выходе элемента ИЛИ 10 реализуется требуемая типовая функция. Сравним предлагаемое устройство и известный предельно универсальный логический модуль по количеству наружных выводов. Известный универсальный логический модуль имеет N +1 наружный вывод. Предлагаемый функциональный преобразователь имеет И„, +2(п-1)+2 наружных выхода. Формула изобретения 1. Универсальный логический модуль, содержащий две группы элементов И, выходы которых соединены со входами элемента ИЛИ, прямой и инверсный выходы которого являются выходами модуля, отличающийся тем, что, с целью повышения надежности за счет уменьшения числа внешних выводрв, он содержит два дешифратора и блок формирования наборов, причем первый вход каждого элемента И перво группы соединен с соответствукяцим выходом первого дешифратораf первый вход каждого элемейта И второй группы соединен с сооТветстбующим выходом второго дешифратораf второй вход каждого элемента И первой и второй групп соединен с соответствуюиим выходом блока формирования наборов,входы которого и входы первого и второго дешифраторов являются входгшог модуля .

2. Модуль по п.1, отличающийся тем, что блок формирования наборов содержит элементы ИЛИ и дешифратор, п входов которого являт ются входами блока, причем первый вход I-того (i 1,...2 -2) элемента ИЛИ соединен с (И-1)-м выходом дешифратора второй вход 1-того v элемента ИЛИ кррме первого и последнего соединен с выходомк-того Кс I -1, если i / , к I +1, если элемента ИЛИ, вторые выходы первого и. последнего элементов ИЛИ соединены соответственно с первым и последним выходгши д оифратора, которые как и выходы элементов ИЛИ, яв.ляются выходами блока формирования наборов..

Источники имформадии, принятые во внимание при экспертизе

1.Авторское свидетельство СССР 15 43(3376, кл.С 06 F 7/00,15.12.1972.

2.Якубайтис Э.Я. Логические и микромодули. Рига, Знание 1975, сЛ95-197 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Универсальный логический модуль | 1986 |

|

SU1345187A1 |

| Логическое устройство | 1976 |

|

SU657432A1 |

| Логический модуль | 1984 |

|

SU1242929A1 |

| Универсальный логический модуль | 1985 |

|

SU1290289A1 |

| Универсальный логический модуль | 1984 |

|

SU1242931A1 |

| Устройство для вычисления булевых дифференциалов | 1988 |

|

SU1689942A1 |

| Устройство для реализации логических функций | 1981 |

|

SU1001080A1 |

| Программируемое логическое устройство | 1991 |

|

SU1777133A1 |

| Устройство для распознавания на линейность булевых функций | 1990 |

|

SU1756879A1 |

| Устройство для определения свойств полноты логических функций | 1984 |

|

SU1170446A1 |

8

/

t t

.«. I

W

4

/

9

/К

V-

ФЫ2./

Авторы

Даты

1981-03-15—Публикация

1978-08-18—Подача