Изобретение относится к автоматике и вычислительной технике и предназначено для использования в качестве логического элемента при синтезе нерегулярных структур дискретных устройств.

Цель изобретения - повышение быстродействия модуля.

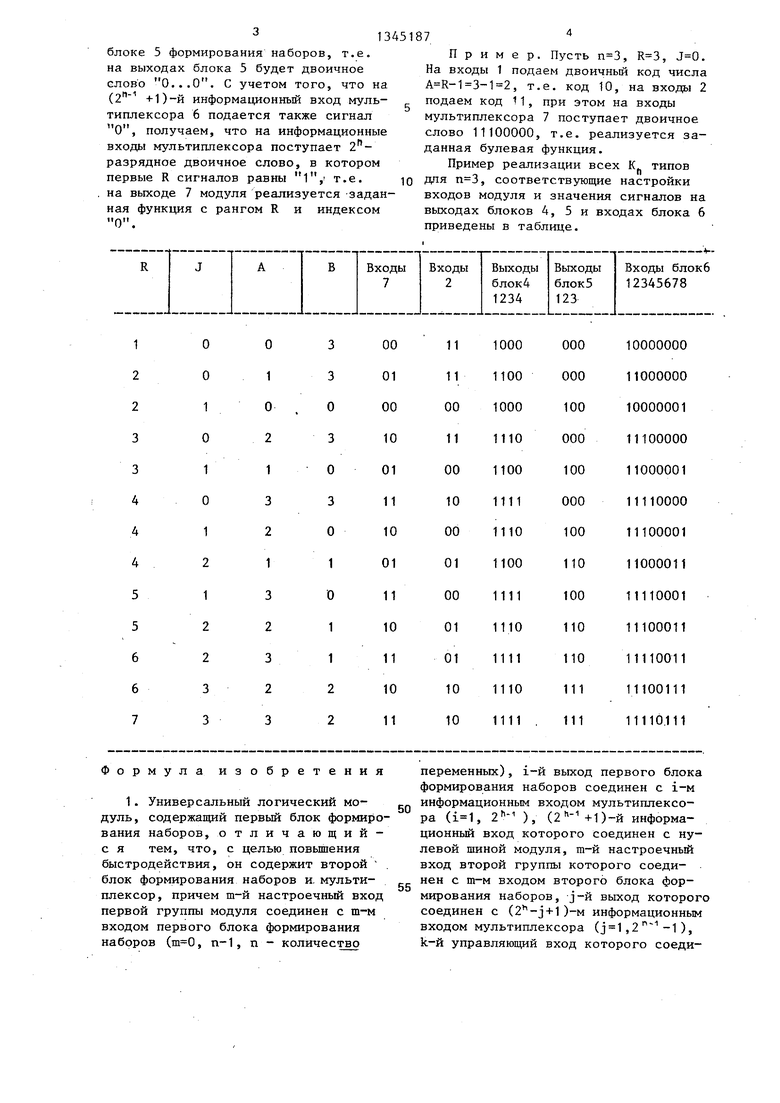

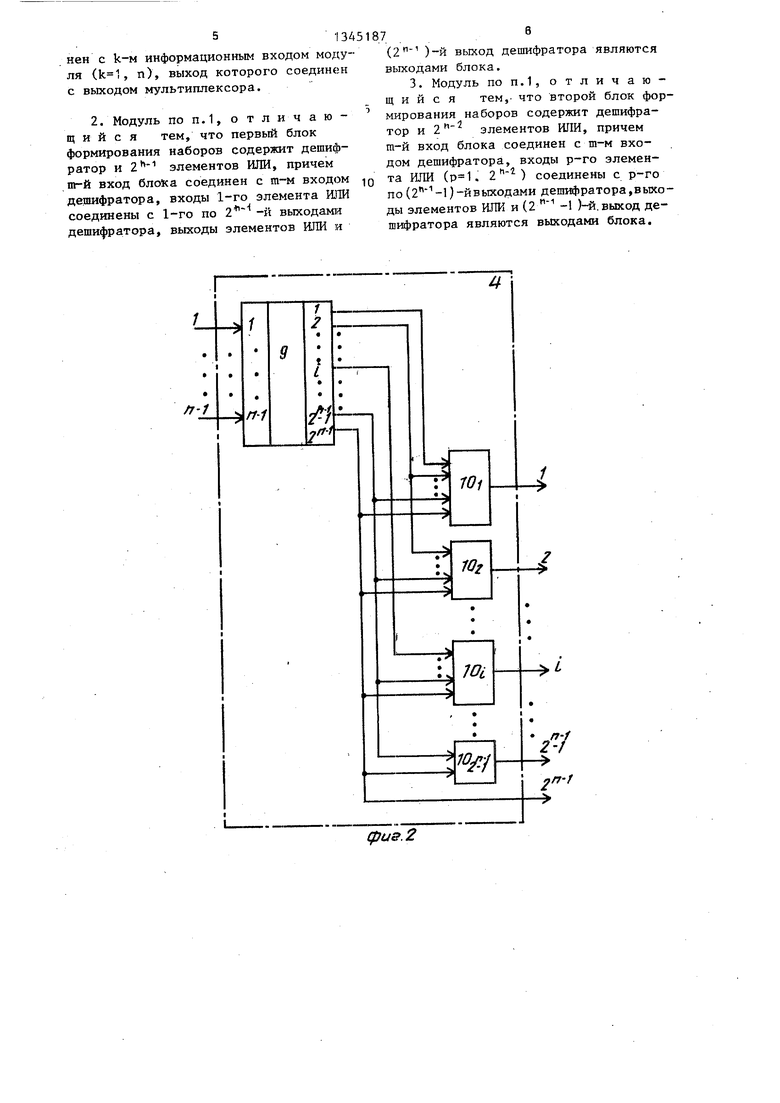

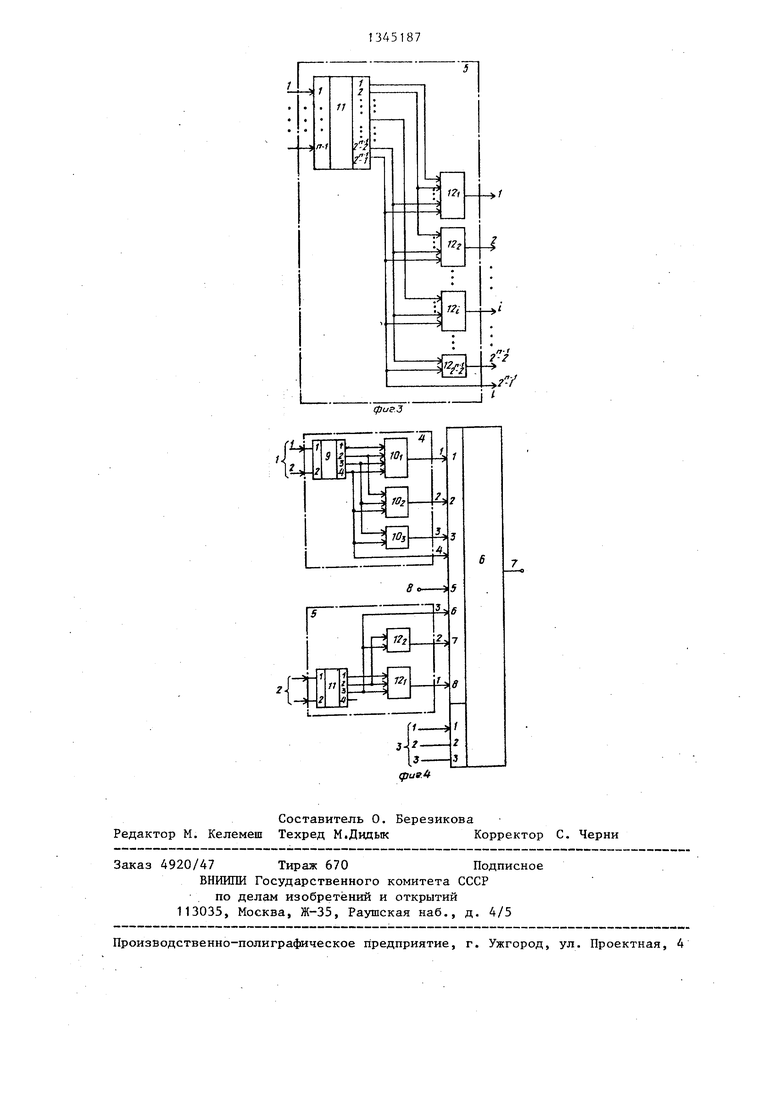

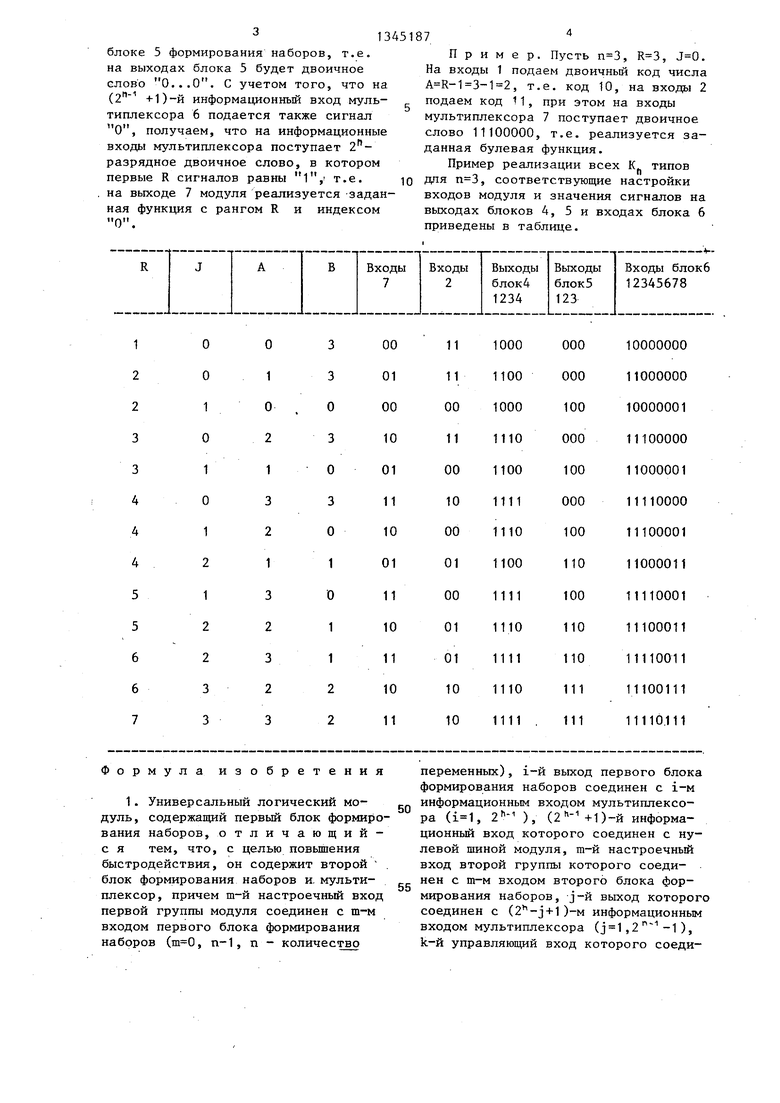

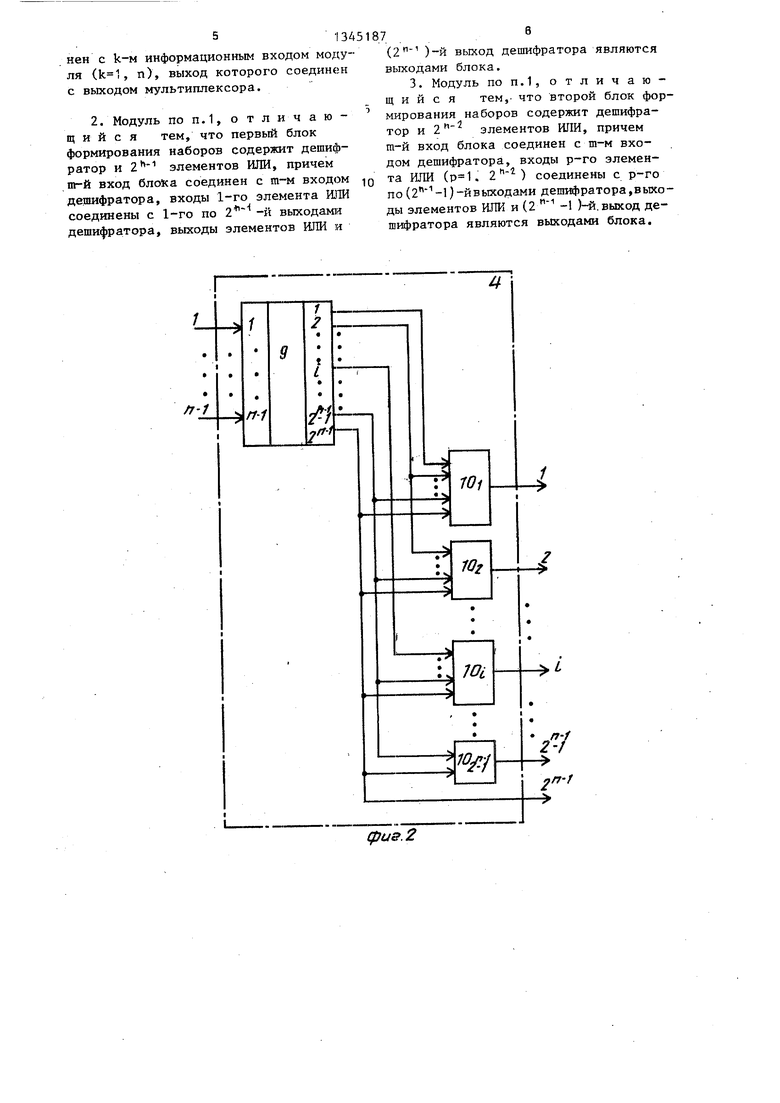

На фиг. t приведена схема универсального логического модуля; на фиг. 2 - схема первого блока формирования наборов; на фиг. 3 - то же, второго блока формирования наборов; на фиг. 4 - пример реализации модуля для конкретного значения числа переменных модуля ().

Модуль (фиг. 1) содержит группы 1, 2, 3 входов модуля, блоки. 4, 5 формирования наборов, мультиплексор 6, выход модуля 7, нулевую шину 8.

Первый блок 4 формирования наборов (фиг. 2) содержит дешифратор 9, элементы ИЛИ.

Второй блок 5 формирования наборов (фиг. 3) содержит дешифратор 11, элементы 1 2 -1 2 п-1

Модуль работает следующим образом

Предложенный модуль реализует все

К. типы булевых функций для п переп

менных. Типовые булевые функции относительно группы К (самодвойственных) преобразований однозначно оп- ределяются двумя параметрами: рангом и индексом. Рангом булевой функции называется количество конституент единицы в ее совершенной дизъюнктивной нормальной форме (СДНФ). Индексом называется число пар противоположных конституент единищл в ее СДНФ. Две булевых функции относятся к одному К типу, если их ранги и индексы совпадают.

Рассмотрим процесс реализации булевой функции с заданным рангом R и индексом J. При этом возможны два случая реализации. . I. Пусть .

На группу 1 входов подается двоичный код числа A R-J-1.

При этом на выходах с номерами 1-(А+1) блока 4 формирования наборов появляется сигнал 1.

На группу входов 2 подается двоичный код числа , при этом на вы- ходах с номерами 1-(В+1) блока 5 формирования наборов появляется сигнал 1 (на i-e входы блоков 4, 5 формирования наборов подаются значения

5

0

g

1-х разрядов соответствующих двоичных чисел, поступающих соответственно на входы 1, 2 модуля).

На группу 3 входов подаются значения входных переменных модуля (на i-й вход модуля - значение переменной X,-). На выходе 7 модуля реализуется булевая функция

F(x,, ..., х)4 . ,

1Г1

где с/- - значение булевой функции на наборе входных переменных - ( соответствует набору 00...О, g - набору 00.,.01, - набору 0...010 и т.д.). На выходах с номерами блока 4 формирования наборов формируется множество значений с/,- о( - на выходах с номерами 1-2 - 1 блока 5 формирования наборов формируются соответственно значения о.п-о/оп-т ,,. В результате подачи на входы 1 и 2 модуля двоичных кодов, соответствую- 5 щих А и В, формируются сигналы о/,- ( и o/ jh.t,- c(jn , равные 1 (остальные равны О). Поскольку наборы . и лп-1 являются противоположными, то реализуемая на выходе 7 мо- 0 дуля функция принимает значение 1 на (A+1)+(B+1)R-1-1+1+J-1+1 R наборах, из которых J противоположны, т.е. предложенное устройство решает поставленную задачу.

Пример . Пусть , , (фиг. 4). Определяем значения A,B:A R-J-1 4-1-1- 2 (двоичный код 10), (двоичный код 00). На входы 1 подаем двоичный код 10 (старшие разряды кода - на входы блока 4, имеющие больишй вес). На входы 2 подаем двоичньй код 00. При этом на выходах 1-4 блока 4 формируется двоичное слово 1110, а на выхо- g дах 1-3 блока 5 формируется слово 100. На информационные входы 1-8 мультиплексора 6 поступает двоичное слово 11100001, соответств ующее настройке на реализацию логической функции с рангом 4 и индексом 1.

II. Пусть . На входы 1 подается двоичный код числа , при этом на выходах с номерами 1-(А+1) блока 4 (и на соответствующих информационных входах мультиплексора 6) появляется сигнал 1. На входы 2 подается код 1...1, при этом сигнал 1 появится на 2 -м выходе дешифратора 11, который не используется в

5

0

0

31345187

блоке 5 формирования наборов, т.е.

на выходах блока 5 будет двоичное слово 0...0. С учетом того, что на ( +1)-й информационный вход мультиплексора 6 подается также сигнал О, получаем, что на информационные входы мультиплексора поступает разрядное двоичное слово, в котором первые R сигналов равны 1, т.е.

Пример. Пусть , , . На входы 1 подаем двоичный код числа , т.е. код 10, на входы 2 подаем код 11, при этом на входы мультиплексора 7 поступает двоичное слово 11100000, т.е. реализуется заданная булевая функция.

Пример реализации всех К типов

10Дпя , соответствующие настройки

на выходе 7 модуля реализуется задан-входов модуля и значения сигналов на

ная функция с рангом R и индексомвыходах блоков 4, 5 и входах блока 6

О.приведены в таблице.

Формула изобретения

1. Универсальный логический модуль, содержащий первый блок формирования наборов, отличающий- с я тем, что, с целью повышения быстродействия, он содержит второй . блок формирования наборов и, мультиплексор, причем т-й настроечный вход первой группы модуля соединен с т-м входом первого блока формирования наборов (, п-1, п - количество

Пример. Пусть , , . На входы 1 подаем двоичный код числа , т.е. код 10, на входы 2 подаем код 11, при этом на входы мультиплексора 7 поступает двоичное слово 11100000, т.е. реализуется заданная булевая функция.

Пример реализации всех К типов

0Дпя , соответствующие настройки

переменных), i-й выход первого блока формирования наборов соединен с i-м информационным входом мультиплексора (, ), (2 - +1)-й информационный вход которого соединен с нулевой шиной модуля, т-й настроечный вход второй группы которого соединен с т-м входом второго блока формирования наборов, j-й выход которого соединен с ( + l )-м информационным входом мультиплексора (j 1, ), k-й управляющий вход которого соеди-

нен с k-M информационным входом модуля (, п), выход которого соединен с выходом мультиплексора.

2. Модуль поп.1,отличаю- щ и и с я тем, что первый блок формирования наборов содержит дешифратор и элементов РШИ, причем т-й вход блока соединен с т-м входом дешифратора, входы 1-го элемента ИЛИ соединены с 1-го по -и выходам) дешифра.тора, выходы элементов ИЛИ и

( )-й вькод дешифратора являются выходами блока.

3. Модуль ПОП.1, отличающийся тем,- что второй блок формирования наборов содержит дешифратор и 2 элементов ИЛИ, причем т-й вход блока соединен с ш-м входом дешифратора, входы р-го элемента ИЛИ (. ) соединены с р-го по()-йвыходами дешифратора,выходы элементов ИЛИ и (2 -1 )-й.выход дешифратора являются выходами блока.

фи&.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Универсальный логический модуль | 1978 |

|

SU813410A1 |

| Универсальный логический модуль | 1985 |

|

SU1290289A1 |

| Универсальный логический модуль | 1984 |

|

SU1242931A1 |

| Устройство для программного управления технологическими процессами | 1989 |

|

SU1633377A1 |

| МНОГОФУНКЦИОНАЛЬНОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2015 |

|

RU2610247C1 |

| Логический модуль | 1984 |

|

SU1242929A1 |

| Устройство для вычисления булевой разности | 1983 |

|

SU1187159A1 |

| Устройство для вычисления булевых производных | 1985 |

|

SU1277089A1 |

| Преобразователь формы представления логических функций | 1987 |

|

SU1474671A1 |

| Устройство для вычисления булевых дифференциалов | 1988 |

|

SU1689942A1 |

Изобретение относится к автоматике и вычислительной технике и предназначено для использования в качестве логического элемента при синтезе нерегулярных структур дискретных устройств. Цель изобретения - повышение быстродействия модуля. Устройство содержит три группы входов 1-3, два блока формирования наборов 4, 5, мультиплексор 6, выход модуля 7, нулевую шину 8. Модуль реализует К ти пы булевых функций с помощью настроек . Настройка модуля состоит в подаче на Соответствующие входы модуля сигналов О или 1. 2 з.п. ф-лы, 1 табл. 4 ил. /7-/ (Л СлЭ 4 сд 00

| ВИБРАТОР ДЛЯ УПЛОТНЕНИЯ БЕТОННЫХ СМЕСЕЙ | 0 |

|

SU400376A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Универсальный логический модуль | 1978 |

|

SU813410A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-10-15—Публикация

1986-06-02—Подача