1

41зобретение относится к вычислительной технике и технической кибернетике и может быть использовано в системах цифровой обработки сигналов (в частности, изображений), а также в системах кодирования, принцип действия которых базируется на теории конечных колец.

Целью изобретения является повышение быстродействия работы устройства.

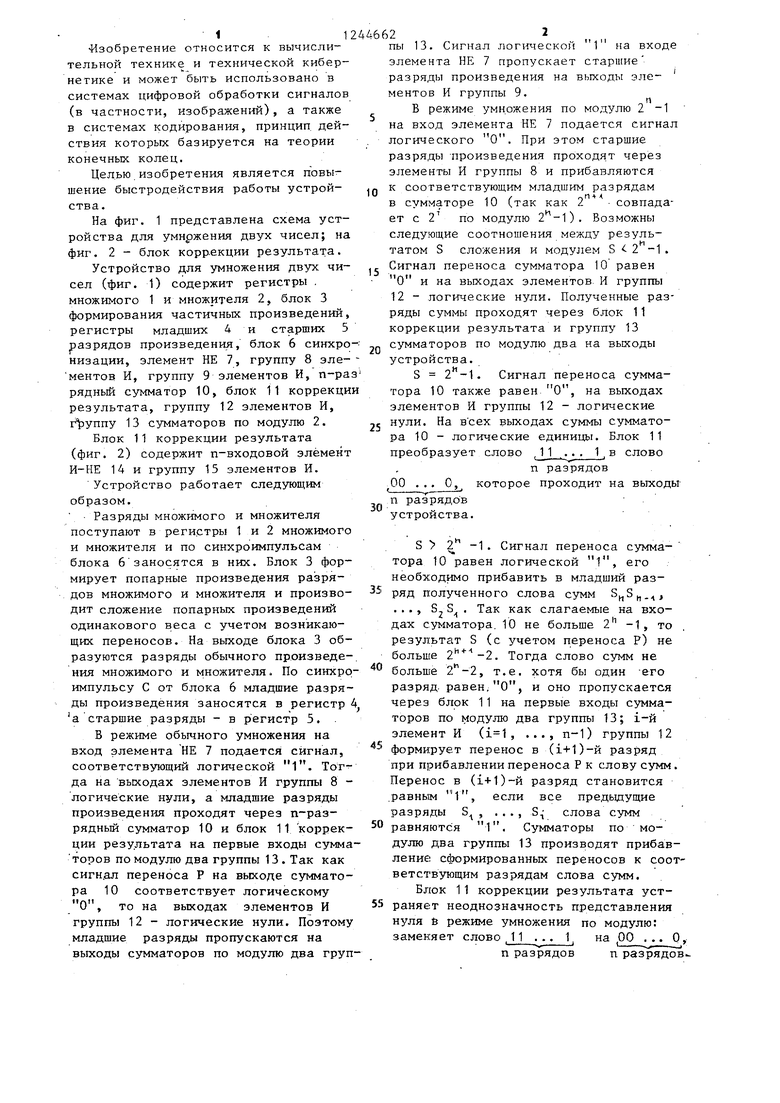

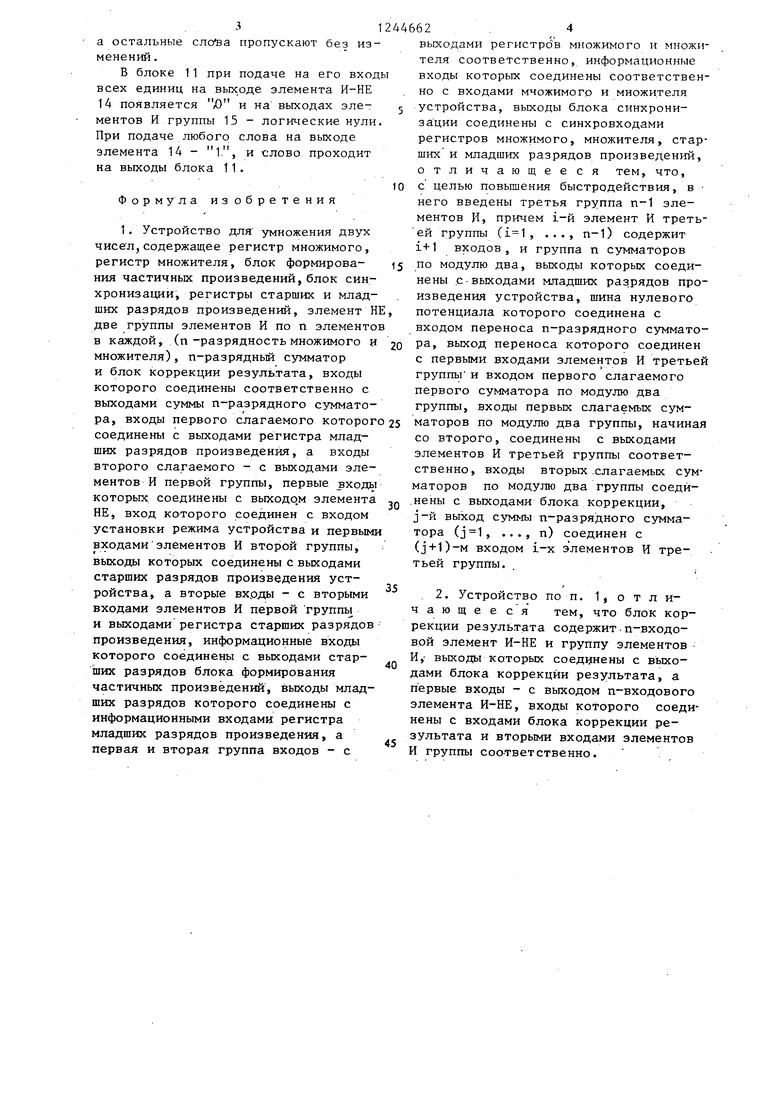

На фиг. 1 представлена схема устройства для умиржения двух чисел; на фиг. 2 - блок коррекции результата.

Устройство для умножения двух чисел (фиг. 1) содержит регистры . множимого 1 и множителя 2, блок 3 формирования частичных произведений, регистры младших 4 и старших 5 разрядов произведения, блок 6 синхронизации, элемент НЕ 7, группу 8 эле ментов И, группу 9 элементов И, п-ра рядньй сумматор 10, блок 11 коррекци результата, группу 12 элементов И, группу 13 сумматоров по модулю 2.

Блок 11 коррекции результата (фиг. 2) содержит п-входовой элемент И-НЕ 14 и группу 15 элементов И.

Устройство работает следующим образом.

Разряды множимого и множителя поступают в регистры 1 и 2 множимого и множителя и по синхроимпульсам блока 6 заносятся в них. Блок 3 формирует попарные произведения разрядов множимого и множителя и производит сложение попарных произведений одинакового веса с учетом возникающих переносов. На выходе блока 3 образуются разряды обычного произведения множимого и множителя. По синхроимпульсу С от блока 6 младшие разряды произведения заносятся в регистр а старшие разряды - в р егистр 5. .

В режиме обычного умножения на вход элемента НЕ 7 подается сигнал, соответствующий логической 1. Тогда на выходах элементов И группы 8 - логические нули, а младшие разряды произведения проходят через рядный сумматор 10 и блок 11 коррекции результата на первые входы сумма торов по модулю два группы 13 . Так как сигн.ал переноса Р на выходе сумматора 10 соответствует логическому О, то на выходах элементов И группы 12 - логические нули. Поэтому младшие разряды пропускаются на выходы сумматоров по модулю два груп

44662 пы

10

15

20

25

30

13. Сигнал логической 1 на входе элемента НЕ 7 пропускает старшие разряды произведения на выходы элементов И группы 9.

В режиме умножения по модулю 2 -1 на вход элемента НЕ 7 подается сигнал логического О. При этом старшие разряды Произведения проходят через элементы И группы 8 и прибавляются к соответствующим младшим разрядам в сумматоре 10 (так как 2 совпадает с 2 по модулю ). Возможны следующие соотношения между результатом S сложения и модулем S 2 -1 . Сигнал переноса сумматора 10 равен О и на выходах элементов. И группы 12 - логические нули. Полученные разряды суммы проходят через блок 11 коррекции результата и группу 13 сумматоров по модулю два на выходы устройства.

S 2 -1. Сигнал переноса сумматора 10 также равен О, на выходах элементов И группы 12 - логические нули. На в сех выходах суммы сумматора 10 - логические единиць. Блок 11 преобразует слово , J 1 .. . 1 в слово

п разрядов

00 . .. О , которое проходит на выходы п разрядо в устройства.

S / 2 -1 . Сигнал переноса сумматора 10 равен логической 1, его необходимо прибавить в младший разряд полученного слова сумм ., ..., S S . Так как слагаемые на входах сумматора. 10 не больше 2 -1, то результат S (с учетом переноса Р) не больше . Тогда слово сумм не больше , т.е. хотя бы один -его разряд, равен,О, и оно пропускается через блок 11 на первые входы сумматоров по модулю два группы 13; i-й элемент И (, ..., п-1) группы 12

формирует перенос в (14-1)-й разряд при прибавлении переноса Р к слову сумм. еренос в (1+1)-й разряд становится равным 1 , если все предьщущие азряды S , ..., S слова сумм

равняются 1. Сумматоры по модулю два группы 13 производят прибавление с гармированных переносов к соответствующим разрядам слова сумм.

Блок 11 коррекции результата устраняет неоднозначность представления нуля 6 режиме умножения по модулю:

заменяет слово 11

1,

на 00

О

п разрядов

п разрядов.

а остальные пропускают без изменений.

В блоке 11 при подаче на его входы всех единиц на выходе элемента И-НЕ 14 появляется Л и на выходах эле- ментов И группы 15 - логические нули. При подаче любого слова на выходе элемента 14 - 1, и слово проходит на выходы блока 11 .

Формула изобретения

1. Устройство для умножения двух чисе л, содержащее регистр множимого, регистр множителя, блок формнрова- НИН частичных произведений, блок синхронизации, регистры старших и младших разрядов произведений, элемент НЕ две группы элементов И по п элементов в каждой, (п-разрядность множимого и множителя), п-разрядный сумматор и блок коррекции результата, входы которого соединены соответственно с выходами суммы п-разрядного сумматора, входы первого слагаемого которого соединены с выходами регистра младших разрядов произведения, а входы второго слагаемого - с выходами элементов И первой группы, первые Jxoды

которых соединены с выходо.м элемента НЕ, вход которого соединен с входом установки режима устройства и первыми входами элементов И второй группы, выходы которых соединены с выходами старших разрядов произведения устройства, а вторые вх.о.ды - с вторыми входами элементов И первой группы и выходами регистра старших разрядов произведения, информационные входы которого соединены с выходами старших разрядов блока формирования частичных произведений, выходы младших разрядов которого соединены с информационньми входами регистра младших разрядов произведения, а первая и вторая группа входов - с

j

0

5 0 5

0

0

выходами регистров множимого и множителя соответственно,, информационные Бходь которых соединены соответственно с входами множимого и множителя устройства, выходы блока синхронизации соединены с синхровходами регистров множимого, множителя, старших и младших разрядов произведений, отличающееся тем, что, с целью повышения быстродействия, в него введены третья группа п-1 элементов И, причем i-й элемент И треть- ей группы (, ..., п-1) содержит i+1 входов, и группа п сумматоров по модулю два, выходы которых соединены с-выходами младших раз.рядов произведения устройства, шина нулевого потенциала которого соединена с входом переноса п-разрядного сумматора, выход переноса которого соединен с первыми входами элементов И третьей группы и входом первого слагаемого первого сумматора по модулю два группы, входы первых слагаемых сумматоров по модулю два группы, начиная со второго, соединены с выходами элементов И третьей группы соответственно, входы вторых .слагаемых сумматоров по модулю два группы соедй- .нены с выходами блока коррекции, j-й выход суммы п-разрядного сумматора (, ..., п) соединен с (j-i-l)-M входом i-x элементов И третьей группы.

. 2. Устройство по п. 1, о т л и- чающееся тем, что блок коррекции результата содержит.п-входо- в.ой элемент И-НЕ и группу элементов И, выходы которых соединены с выходами блока коррекции результата, а первые входы - с выходом п-входового элемента И-НЕ, входы которого соединены с входами блока коррекции результата и вторыми входами элементов И группы соответственно.

Редактор Л. Повхан

f.2

Составитель E. Захарченко

Техред .М.Ходанич Корректор О, Луговая

Заказ 3919/52

Тираж 671

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, , Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Подписное

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения двух чисел | 1984 |

|

SU1179322A1 |

| Матричное множительное устройство | 1984 |

|

SU1170450A1 |

| Матричное устройство для умножения чисел (его варианты) | 1983 |

|

SU1160398A1 |

| Устройство для умножения двух чисел | 1989 |

|

SU1667059A2 |

| Матричное устройство для умножения чисел по модулю 2 @ -1 | 1985 |

|

SU1254471A1 |

| Устройство для умножения | 1982 |

|

SU1038937A1 |

| Устройство для умножения | 1986 |

|

SU1399729A1 |

| Устройство для умножения | 1981 |

|

SU1032453A1 |

| Устройство для умножения | 1985 |

|

SU1322265A1 |

| Устройство для умножения | 1984 |

|

SU1226447A1 |

Изобретение относится к области вычислительной техники и технической ;кибернетики, преимущественно к устройствам для цифровой обработки сигналов. Цель изобретения - повьппение быстродействия работы устройства. Поставленнай цель достигается тем, что в устройство введены группа элементов И и группа сумматоров по модулю два, причем выход переноса п-раз- рядного сумматора соединен с (1+1)-м входом i-ro (, ..., n-.l) элемента И и вторым входом первого сумматора по модулю два, j-й вход i-го (, ..., п-1, , ..., i) элемента И соединен с j-м выходом суммы п-раз- рядного сумматора, выходы элементов И соединены с первыми входами соответствующих сумматоров по модулю два, начиная со второго, вторые входы -. которых соединены с соответствующими выходами блока коррекции, а их выходы являются выходами устройства. 1 з.п. ф-лы, 2 ип. с $ (П tC 4 4 Од Од ISD

| Рабинер Л., Гоунд Б | |||

| Теория и применение цифровой обработки сигналов | |||

| М.: Мир, 1978 | |||

| Устройство для умножения двух чисел | 1984 |

|

SU1179322A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-07-15—Публикация

1984-11-20—Подача