Изобретение относится к вычислительной технике и технической кибернетике и может быть использовано в устройствах для цифровой обработки сигналов (в частности, для цифровой обработки изображений), а также в системах кодирования, принцип действия которых базируется на теории полей Галуа.

Цель изобретения - расширение функциональных возможностей устройства за счет обеспечения дополнительно умножения п -разрядных двоичных чисел по модулю , которой отличен от степени двойки.

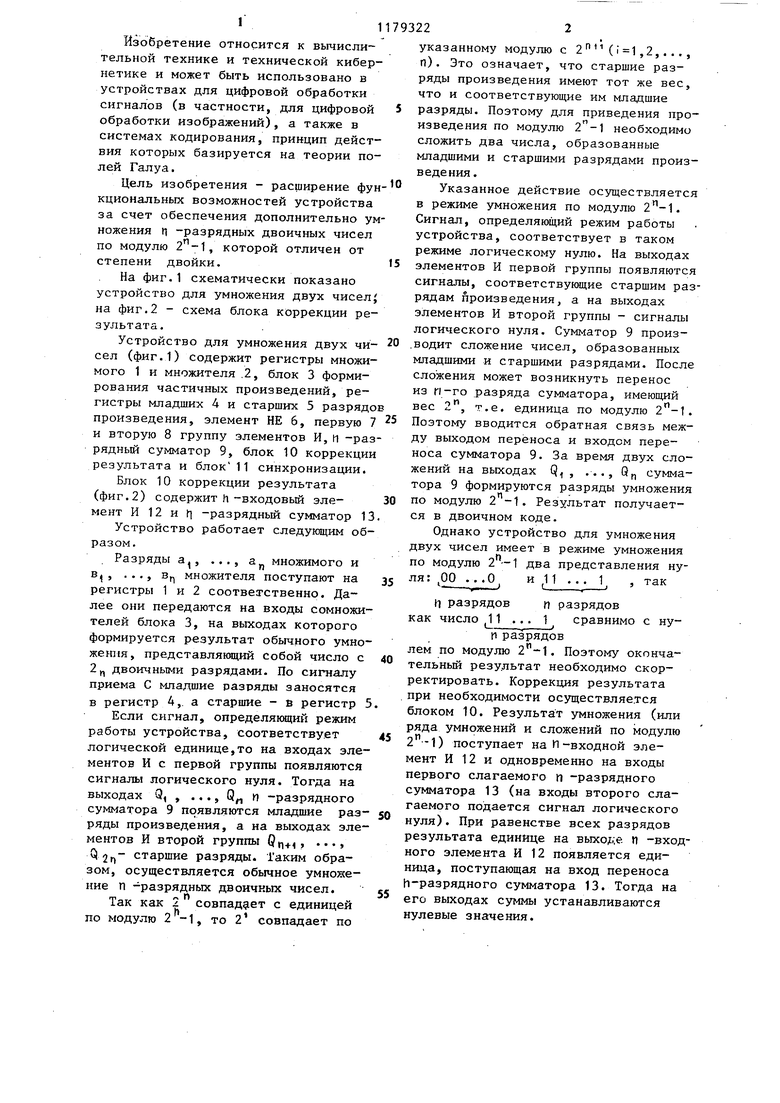

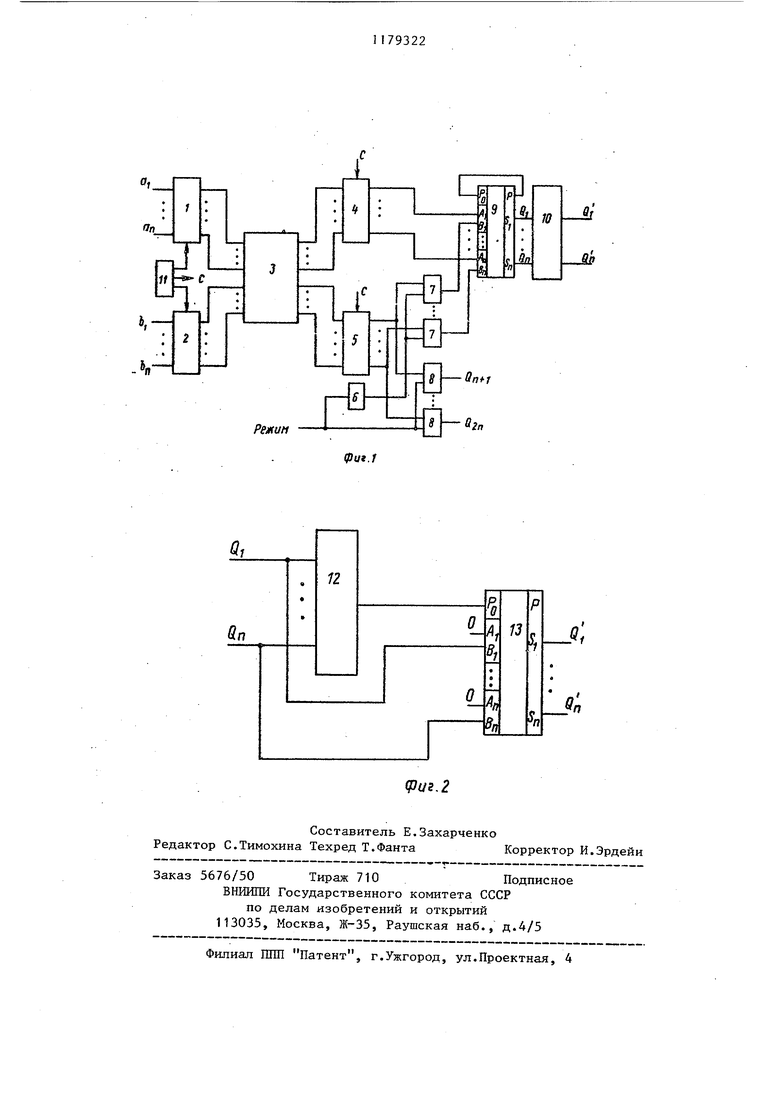

На фиг,1 схематически показано устройство для умножения двух чисел} на фиг.2 - схема блока коррекции результата.

Устройство для умножения двух чисел (фиг.1) содержит регистры множимого 1 и множителя .2, блок 3 формирования частичных произведений, регистры младших 4 и старших 5 разрядо произведения, элемент НЕ 6, первую 7 и вторую 8 группу элементов И,и -разрядный сумматор 9, блок 10 коррекции результата и блок11 синхронизации.

Блок 10 коррекции результата (фиг.2) содержитh-входовый элемент И 12 и 1 -разрядный сумматор 13

Устройство работает следующим образом.

Разряды а, ..., а, множимого и в , .., Вр| множителя поступают на регистры 1 и 2 соответственно. Далее они передаются на входы сомножителей блока 3, на выходах которого формируется результат обычного умножения, представляющий собой число с 2 двоичными разрядами. По сигналу приема С младшие разряды заносятся в регистр i, а старшие - в регистр 5

Если сигнал, определяющий режим работы устройства, соответствует логической единице,то на входах элементов И с первой группы появляются сигналы логического нуля. Тогда на выходах Э , . , Q -разрядного сумматора 9 появляются младшие разряды произведения, а иа выходах элементов И второй группы Qti+ , ..., С) 2п старшие разряды. Таким образом, осуществляется обычное умножение п -разрядных двоичных чисел.

Так как 2 совпадает с единицей по модулю 2 -1, то 2 совпадает по

указанному модулю с ,2,..., л). Это означает, что старшие разряды произведения имеют тот же вес, что и соответствующие им младшие разряды. Поэтому для приведения произведения по модулю 2 -1 необходимо сложить два числа, образованные младшими и старшими разрядами произведения.

Указанное действие осуществляется в режиме умножения по модулю . Сигнал, определяющий режим работы устройства, соответствует в таком режиме логическому нулю. На выходах элементов И первой группы появляются сигналы, соответствующие старшим разрядам произведения, а на выходах элементов И второй группы - сигналы логического нуля. Сумматор 9 произ.водит сложение чисел, образованных младшими и старшими разрядами. После сложения может возникнуть перенос из Г1-ГО разряда сумматора, имеющий вес 2, т.е. единица по модулю . Поэтому вводится обратная связь между выходом переноса и входом переноса сумматора 9. За время двух сложений на выходах Q, , ..., Q сумматора 9 формируются разряды умножения по модулю 2 -1. Результат получается в двоичном коде.

Однако устройство для умножения двух чисел имеет в режиме умножения по модулю 2 -1 два представления нуля: 00 . . .0 и (, J так

Л разрядов

(1 разрядов

как число 11 ...1 сравнимо с ну11 разрядов

лем по модулю . Поэтому окончательный результат необходимо скорректировать. Коррекция результата при необходимости осуществляется блоком 10. Результат умножения (или ряда умножений и сложений по модулю ) поступает на И-входной элемент И 12 и одновременно на входы первого слагаемого ц -разрядного сумматора 13 (на входы второго слагаемого подается сигнал логического нуля). При равенстве всех разрядов результата единице на выходе п -вхоного элемента И 12 появляется единица, поступающая на вход переноса h-разрядного сумматора 13. Тогда на его выходах суммы устанавливаются нулевые значения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения двух чисел | 1984 |

|

SU1244662A1 |

| Матричное устройство для умножения чисел (его варианты) | 1983 |

|

SU1160398A1 |

| Матричное множительное устройство | 1984 |

|

SU1170450A1 |

| Устройство для умножения | 1985 |

|

SU1322265A1 |

| Матричное устройство для умножения чисел по модулю 2 @ -1 | 1985 |

|

SU1254471A1 |

| Устройство для умножения | 1981 |

|

SU1032453A1 |

| Устройство для умножения двух чисел | 1989 |

|

SU1667059A2 |

| Устройство для умножения чисел | 1991 |

|

SU1797112A1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ | 1991 |

|

RU2021633C1 |

| Устройство для умножения | 1989 |

|

SU1667061A1 |

УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ДВУХ ЧИСЕЛ, содержащее регистр множимого, регистр множителя, блок формирования частичных произведений, блок синхронизации, регистры старших и младших разрядов произведений, информационные входы которых соединены соответственно с выходами старших и младших разрядов блока формирования частичных произведений, первая и вторая группы входов которого соединены соответственно с выходами регистров множимого и множителя, информационные входы которых соединены соответственно со входами множимого и множителя устройства, выходы блока синхронизации соединены с синхровходами регистров множимого, множителя, старших разрядов произведения и младших разрядов произведения соответственно, отличающееся тем, что, с целью расширения функциональных возможностей за счет обеспечения умножения двоичных целых чисел по модулю 2 -1, в него введены элемент НЕ, две группы элементов И по h элементов И в каждой, И -разрядньм сумматор и блок коррекции результата, содержащий ц -входовый элемент И и П-разрядный сумматор, причем выходы регистра младших разрядов произведения соединены со входами первого слагаемого П-разрядного сумматора, входы второго слагаемого которого соединены с вьгходами элементов И первой группы, первые входы которых соединены с выходом элемента НЕ, с s вход которого соединен со входом установки режима работы устройства и с первыми входами элементов И второй группы, вторые входы которых соединены с выходами регистра старших разрядов произведения и вторыми входами соответствующих элементов И первой группы, а выходы - с выходами старших разрядов произведения устройства, выходы младших разрядов произведения которого соединены с выходами И -разрядного сумматора бло- . ьэ ка коррекции результата, входы первого слагаемого которого соединены с ши1чд ной нулевого потенциала, а входы второго слагаемого - со входами п -входового элемента И блока коррекции результата и выходами суммы п-разрядного сумматора, выход переноса .которого соединен со входом переноса этого же г1 -разрядного сумматора, выход tl-входового элемента И блока коррекции результата соединен со входом переноса п-разрядного сумматора блока коррекции результата.

| Патент США № 4037093, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Шеститрубный элемент пароперегревателя в жаровых трубках | 1918 |

|

SU1977A1 |

| Устройство для умножения произвольных элементов полей Галуа GF(р @ ) | 1979 |

|

SU900281A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Макаревич О.Б., Спиридонов Б.Г | |||

| Цифровые процессоры обработки сигналов на основе БИС | |||

| - Зарубежная электронная техника, 1983, № 1, с | |||

| Устройство для охлаждения водою паров жидкостей, кипящих выше воды, в применении к разделению смесей жидкостей при перегонке с дефлегматором | 1915 |

|

SU59A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1985-09-15—Публикация

1984-03-28—Подача