Изобретение относится к области вычислительной техники и может быть использовано в вычислительных машинах и устройствах последовательно-параллельного действия, работающих в позиционной и избыточной системах счисления, а также в специализированных .устройствах цифровой обработки сигналов в реальном масштабе времени.

Цель изобретения - повышение быстродействия устройства.

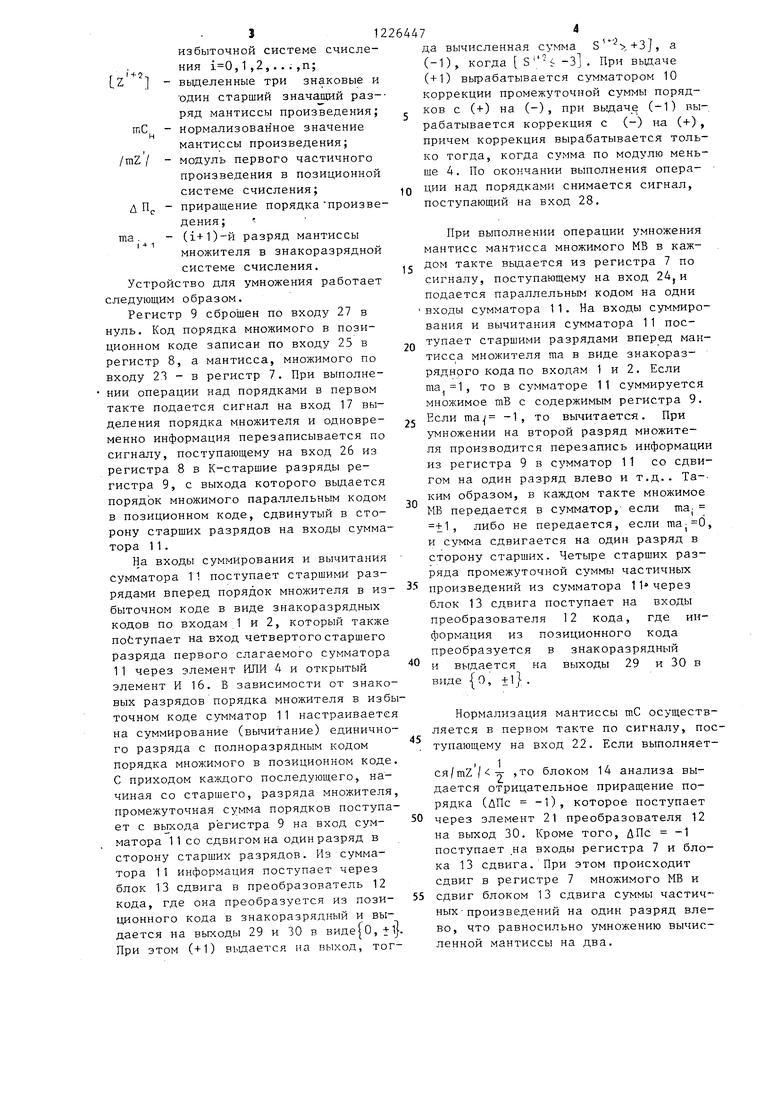

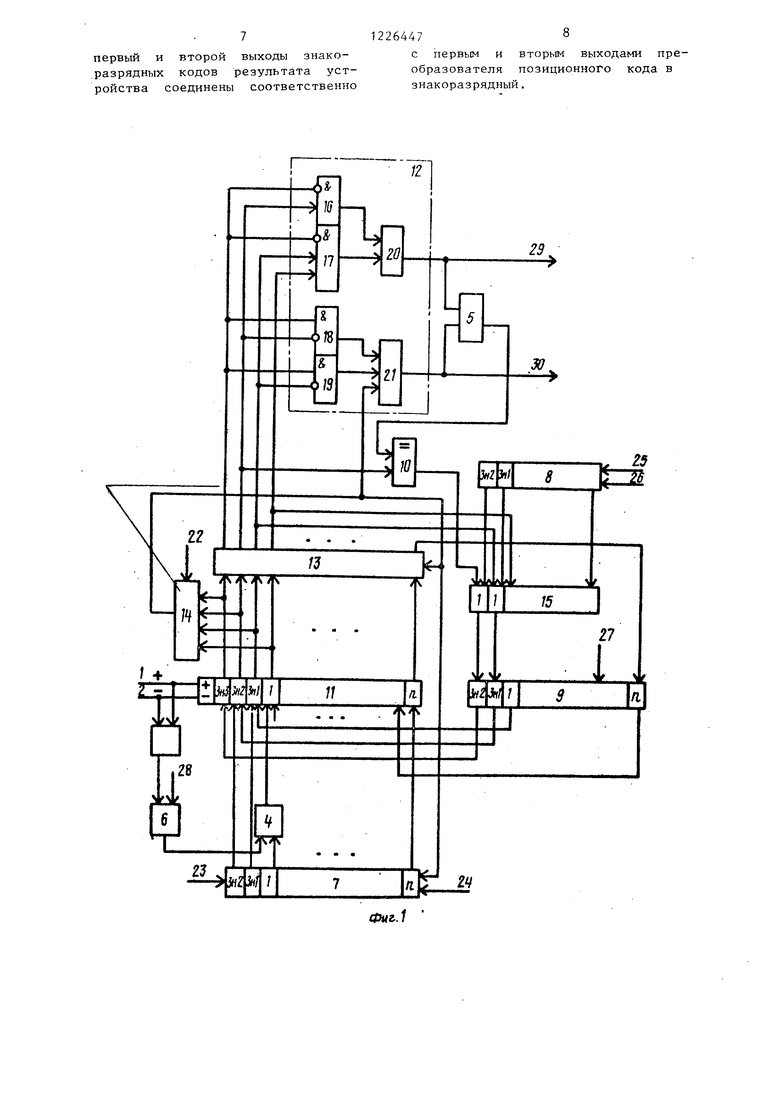

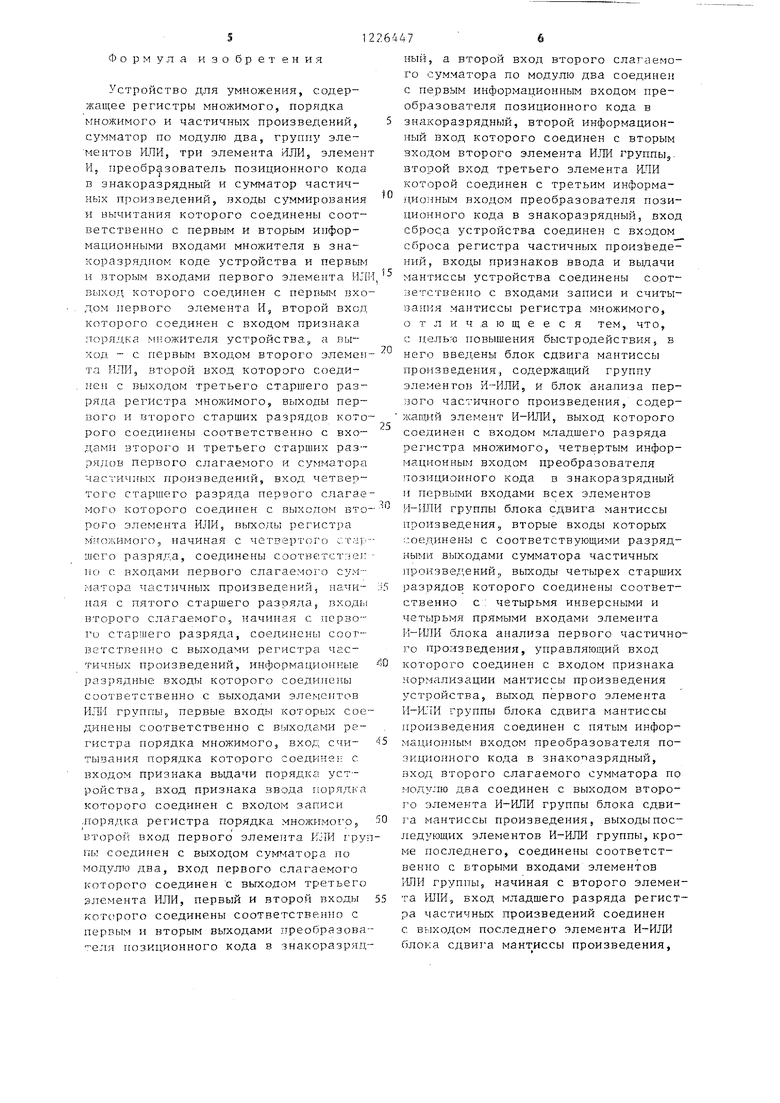

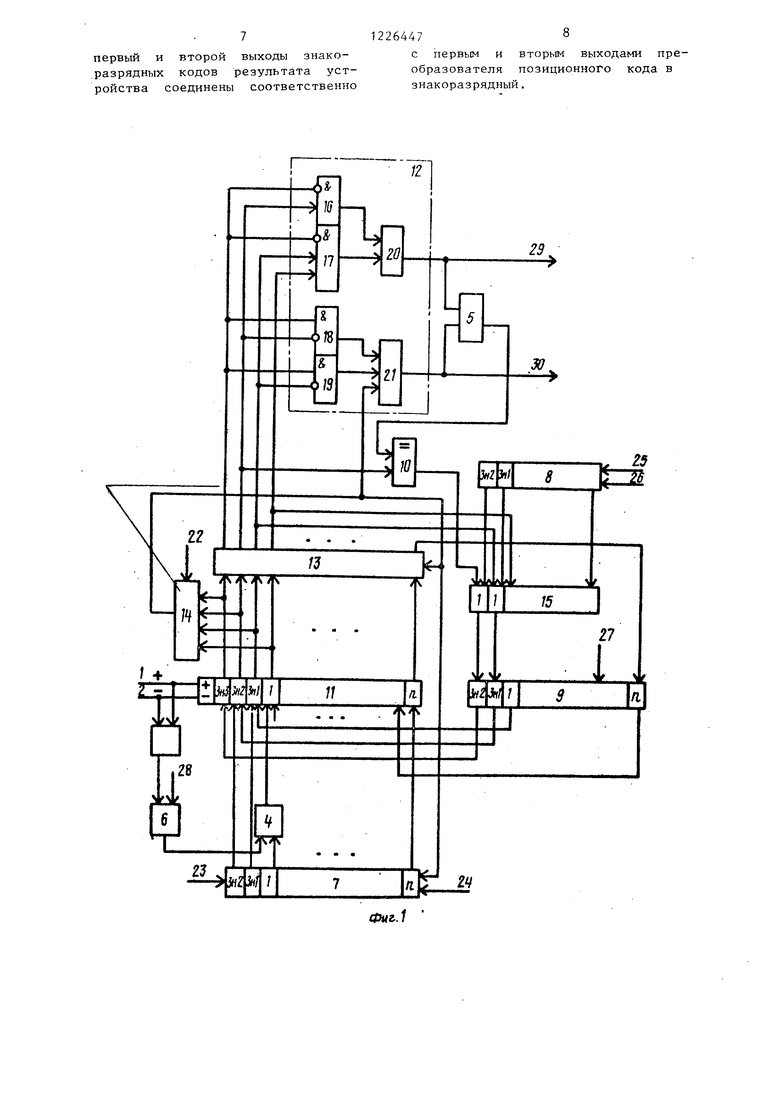

На фиг. 1 представлена структурная схема устройства для умножения; на фиг. 2 - функциональные схемы блоков сдвига мантиссы произведения и анализа первого частичного произведения

-Устройство для умножения (фиг.1) содержит информационные входы 1 и 2 множителя в знакоразрядном коде устройства, три элемента ИЛИ 3-5, элемент И 6, регистры множимого 7;, порядка множимого 8, частичных произведений 9, сумматоры по модулю два 10 и частичных произведений 11,преобразователь 12 позиционного кода в зна- коразрядный, блоки сдвига мантиссы произведения 13 и анализа первого частичного произведения 14, группу элементов ИЛИ 15, четыре элемента И 16-19 преобразователя 12, два элемента ИЛИ 20 и 21 преобразователя 12 вход 22 признака нормализации мантиссы произведения устройства, входы признаков ввода 23 и вьщачи 24 мантиссы устройства, входы признаков ввода 25 и вьщачи 26 порядка устройства, вход 27 сброса устройства, вход 28 признака вьзделёния порядка множителя, выходы 29 и 30 знакораз- рядных кодов результата устройства.

Блок 13 сдвига мантиссы произведения (фиг. 2) содержит группу элементов И-ИЛИ 31

Блок 14 анализа первого частичного произведения-(фиг. 2) содержит элемент И-ИПИ 32.

Алгоритм вьтолнения операции умножения, начиная со старших разрядов нйд мантиссами MB (множимое, представленное в обычной двоичной системе счисления) и та (множитель в знакоразрядной системе счисления), имеет вид

па

пв

., где та, .МБ

ПС.fie, . . Па ч

тС(2 МВ)х(2 та)2

хМБ X та.

Действие над порядками

+ Па; s ПВ + Па; (S . , )+Па(1+2);

{ ЗИЗ, 3112, ЗИ1, 1р} ,

1, если S . 3 г / -Т П -1, если J

2( 1 ..,

О-В остальных случаях.

«5

Действие над мантиссами

та; mZ МВ X та; mZ 2(mZ -4mC,.,))+MBx та , ;

, ЗН2, ЗН1, 1pj

1 ,. если Z .3 m.-{-1, если

О-в остальных случаях;

Г I lc, если 2 6/mz / 1 ; mc |2mc, если /mZ / 2 ;

лп /mZ / 1; 1-1, если /mZ / 2- ,

где П - i-й разряд порядка произве- с 1

дения в двоично-избыточном

коде;

raCj - i-й разряд мантиссы произведений ,1,2,..., п; Пс - порядок произведения в по- зиционном коде;

та - мантисса операнда (а) в двоично-избыточном коде; та- - i-й разряд мантиссы операнда (а);

MB - мантисса операнда (В) в позиционном коде, нормализованная;

,. I -1

1 - промежуточная сумма порядков в позиционном коде; - выделенные четыре старших разряда промежуточной суммы порядков);

mZ - (i + 1)-е значение мантиссы частичного произведения в обычной двоичной системе

счисления; тс - i-й разряд мантиссы произведения в знакоразрядной

S122644

избыточной системе счисления ,1,2,...,n;

1+2,

Z, I - выделенные три знаковые и ОДИН старший значащий раз-- ряд мантиссы произведения; тС - нормализован ное значение

мантиссы произведения; /mZ / - модуль первого частичного произведения в позиционной системе счисления; Q д П;, - приращение порядка произведения;та. - (1+1)-й разряд мантиссы

множителя в знакоразрядной

системе счисления.

Устройство для умножения работает следующим образом.

Регистр 9 сброшен по входу 27 в нуль. Код порядка множимого в позиционном коде записан по входу 25 в регистр 8, а мантисса, множимого по входу 23 - в регистр 7. При выполнении операции над порядками в первом такте подается сигнал на вход 17 выделения порядка множителя и одновре- менно информация перезаписывается по сигналу, поступающему на вход 26 из регистра 8 в К-старшие разряды регистра 9, с выхода которого выдается порядок множимого параллельным кодом в позиционном коде, сдвинутый в сторону старших разрядов на входы сумматора 11.

На входы суммирования и вычитания сумматора 11 поступает старшими разрядами вперед порядок множителя в из быточном коде в виде знакоразрядных кодов по входам 1 и 2, который также notTynaeT на вход четвертого старшего разряда первого слагаемого сумматора 11 через элемент ИЛИ 4 и открытый элемент И 16. В зависимости от знаковых разрядов порядка множителя в избточном коде сумматор 11 настраиваетс на суммирование (вычитание) единичного разряда с полноразрядным кодом порядка множимого в позиционном коде С приходом каждого последующего, начиная со старшего, разряда множителя промежуточная сумма порядков поступает с выхода регистра 9 на вход сум- матера 11 со Сдвигом на один разряд в сторону старших разрядов. Из сумматора 11 информация поступает через блок 13 сдвига в преобразователь 12 кода, где она преобразуется из пози- ционного кода в знакоразрядный и выдается на Бькоды 29 и 30 в ,+1 При этом (+1) выдается на выход, тог

Q

5

0

о 5

5

5

да вычисленная сумма S ,+3, а (-1), когда S t -З . При выдаче (+1) вьфабатывается сумматором 10 коррекции промежуточной суммы порядков с (+) на (-), при выдаче (-1) вырабатывается коррекция с (-) на (+), причем коррекция вырабатывается только тогда, когда сумма по модулю меньше 4. По окончании выполнения операции над порядками снимается сигнал, поступающий на вход 28.

При выполнении операции умножения мантисс мантисса множимого MB в каждом такте вьщается из регистра 7 по сигналу, поступающему на вход 24j и подается параллельным кодом на одни входы сумматора 11. На входы суммирования и вычитания сумматора 11 поступает старшими разрядами вперед мантисса множителя та в виде знакораз- ряднрго кода по входам 1 и 2. Если , то в сумматоре 11 суммируется множимое шВ с содержимым регистра 9. Если та -1, то вычитается. При умножении на второй разряд множителя производится перезапись информации из регистра 9 в сумматор 11 со сдвигом на один разряд влево и т.д.. Та-- КИМ образом, в каждом такте множимое МБ передается в сумматор, если та +1, либо не передается, если , и сумма сдвигается на один разряд в сторону старших. Четыре старших разряда промежуточной суммы частичных произведений из сумматора 11° через блок 13 сдвига поступает на входы преобразователя 12 кода, где информация из позиционного кода преобразуется в знакоразрядный и выдается на выходы 29 и 30 в виде jo, .

Нормализация мантиссы тС осуществляется в первом такте по сигналу, поступающему на вход 22. Если выполняется/mZ /- у то блоком 14 анализа выдается отрицательное приращение порядка (ДПс -1), которое поступает через элемент 21 преобразователя 12 на выход 30. Кроме того, ДПс -1 поступает на входы регистра 7 и блока 13 сдвига. При этом происходит сдвиг в регистре 7 множимого MB и сдвиг блоком 13 сдвига суммы частичных произведений на один разряд влево, что равносильно умножению вычисленной мантиссы на два.

Формула изобретения

Устройство для умножения, содержащее регистры множимого, порядка множимого и частичных произведений, сумматор по модулю два, группу эле- ментов ИЛИ, три элемента ИЛИ, элеме}2Т И. преобразователь позиционного кода D знакоразрядный и сумматор частичных произведений, входы суммирования и вычитания которого соединены соответственно с первым и вторьм информационными входами множителя в зна коразрядном коде устройства и первым и вторым входами первого элемента 1-L4H выхо.д которого соединен с первым входом первого элемента И, второй вход которого соединен с входом признака порядка множителя устройства, а выход - с первым входом второго элемен- та ИЛИ, второй вход которого соединен с вЕлходом третьего старшего разряда регистра множимого, выходы первого и второго старших разрядов кото- рого соединены соответственно с вхо- дами второго и третьего старшр х разрядов первого слагаемого и сумматора частичных произведений, вход четвертого старшего разряда первого слагаемого которого соединен с выхотгом вто- рого элемента ИЛИ, выходы регистра множимого, начиная с teTBepToi o ста ; шего разряда, соединены соответстгзеп по с входами первого слагаемого сумматора частичных произведений, начи- ная с пятого старшего разряда, входы второго слагаемого, начипая с перво го старшего разряда, соедипены соответственно с выходами регистра частичных произведений, информационные разрядные входы которого соединены соответственно с выходами элементов ИЛ1-1 группы, первые входы которых соединены соответственно с выходами регистра порядка множимого, вход счи- тывания порядка которого соедине ; с входом признака выдачи порядка устройства, вход признака ввода порядка которого соединен с входом записи .порядка регистра порядка множимот о, второй вход первого элемента КЛИ груп г;ь соединен с выходом сумматора по модулю два, вход первого слагаемого которого соединен с выходом третьего 0j:eMeHTa ИЛИ, первый и второй входы которого соединены соответственно с первым и вторым выходами преобразова- позиционного кода в знакоразрядo

ный, а второй вход второго слагаемого сумматора по модулю два соединен с первым информационным входом преобразователя позиционного кода в знакоразрядный, второй информационный вход которого соединен с вторым входом второго элемента ИЛИ группы, второй вход третьего элемента ИЛИ которой соединен с третьим информационным входом преобразователя позиционного кода в знакоразрядный, вход сброса устройства соединен с входом сброса регистра частичных произведений, входы признаков ввода и вьщачи мантиссы устройства соединены сорт- зетствен1Ш с входами записи и считы- oaHi iH мантиссы регистра множимого, отличающееся тем, что, с целью повышения быстродействия, в него введены блок сдвига мантиссы произведения, содержащий группу эле.1енгов И-ИЛИ, и блок анализа первого частичного произведения, содер- жащ1-1й элемент И-ИЛИ, выход которого соединен с входом младшего разряда регистра множимого, четвертым информационным входом преобразователя пози1; ионргого кода в знакоразрядный I первыми входами всех элементов И-ИЛИ группы блока сдвига мантиссы произведения, вторые входы которых соед.инены с соответствуюш,ими разрядными выходами сумматора частичных произвег ений, выходь четырех старших разрядов которого соединены соответственно с : четырьмя инверсными и четырьмя прямыми входами элемента И-ИЛИ блока анализа первого частичного произведения, управляющий вход которого соединен с входом признака нормализации мантиссы произведения устройства, выход первого элемента И-ИЛИ группы блока сдвига мантиссы произведения соединен с пятым информационным входом преобразователя позиционного кода в знакопазрядный, вход второго слагаемого сумматора по модулю два соединен с выходом второго элемента И-ИЛИ группы блока сдвига мантиссы произведения, выходы последующих элементов И-ИЛИ группы,кроме последнего, соединены соответственно с вторыми входами элементов 1-1ЛИ группы, начиная с второго элемента ИЛИ, вход младшего разряда регистра частичных произведений соединен с выходом последнего элемента И-ИЛИ блока сдвига мантиссы произведения,

71226447°

первый и второй выходы знаке- с первым и вторым выходами пре- разрядных кодов результата устройства соединены соответственно

образователя позиционного кода в знакоразрядный.

Ю

-о

/8

& 15

с первым и вторым выходами пре

образователя позиционного кода в знакоразрядный.

20

23

С

ю

Ф

25

/5

ff

11

15

27

3

с

В

Е

2V

Фиг..1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1979 |

|

SU868751A1 |

| УСТРОЙСТВО УМНОЖЕНИЯ | 1998 |

|

RU2148270C1 |

| Устройство для умножения чисел с плавающей запятой | 1985 |

|

SU1280624A1 |

| Устройство для умножения | 1989 |

|

SU1612295A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Специализированный процессор | 1983 |

|

SU1144117A1 |

| Устройство для умножения и деления с плавающей точкой | 1985 |

|

SU1278837A1 |

| Преобразователь двоичных чисел в двоично-десятичные числа | 1980 |

|

SU941990A1 |

| Преобразователь двоично-десятичногоКОдА B дВОичНый КОд | 1979 |

|

SU809151A1 |

Изобретение относится к области вычислительной техники и может быть использовано в вычислительных маши- йах и устройствах последовательно- параллельного дейст вия работающих в позиционной и избыточной системах счисления, а также в специализированных устройствах цифровой обработки сигналов в реальном масштабе времени. Целью изобретения является повьшение быстродействия. Устройство для умножения содержит комбинационный сумматор, элемент И, три элемента ИЛИ, регистры порядка и мантиссы мйожимого и частичных произведений, с умматор по модулю два, блок элементов ШШ, преобразователь кодов, состоящий из четырех элементов И и двух элементов ИЛИ, а также входы и выходы знакораз- рядных кодов схемы сдвига мантиссы произведения и схемы анализа модуля первого частичного произведения, состоящие из элементов И-ИЛИ, что позволило сократить дополнительную задержку на нормализацию мантисЪы результата. 2 ил. (Л с ю IvD Oi 4 4

| Авторское свидетельство СССР | |||

| Устройство для умножения чисел | 1981 |

|

SU999045A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для умножения | 1979 |

|

SU868751A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-04-23—Публикация

1984-09-29—Подача