Изобретение относится к электротехнике и может использоваться в системах управления технологическими процессами.

Целью изобретения является повышение надежности работы устройства.

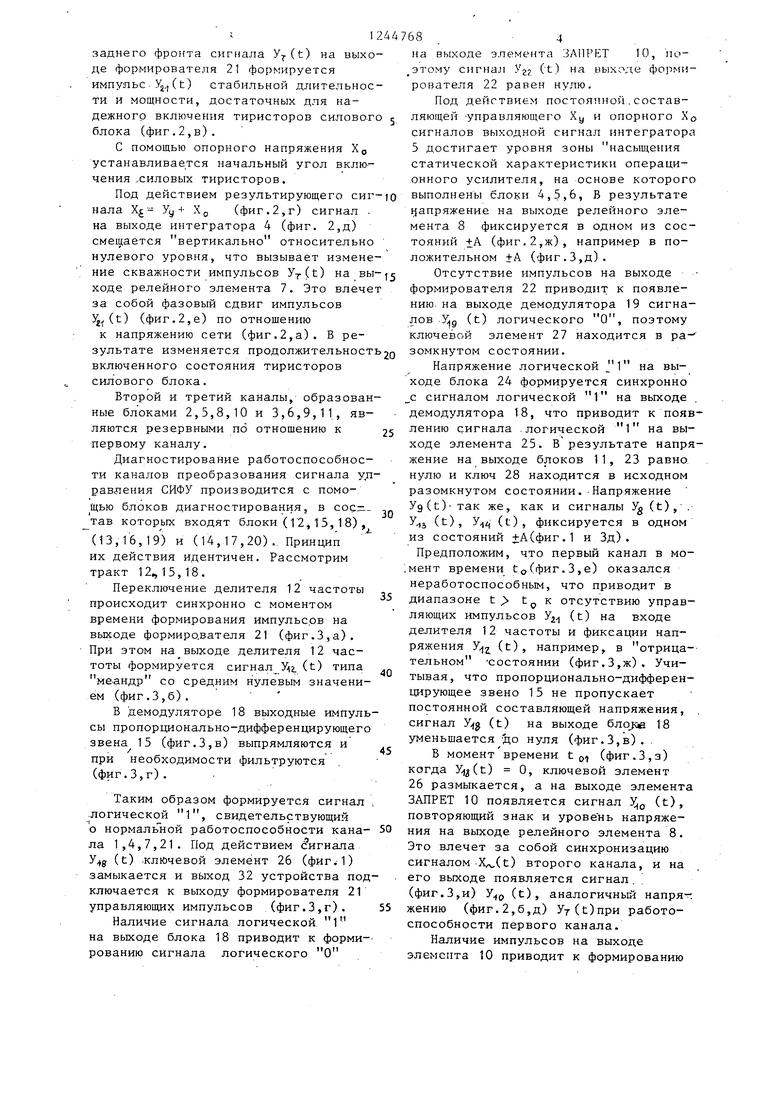

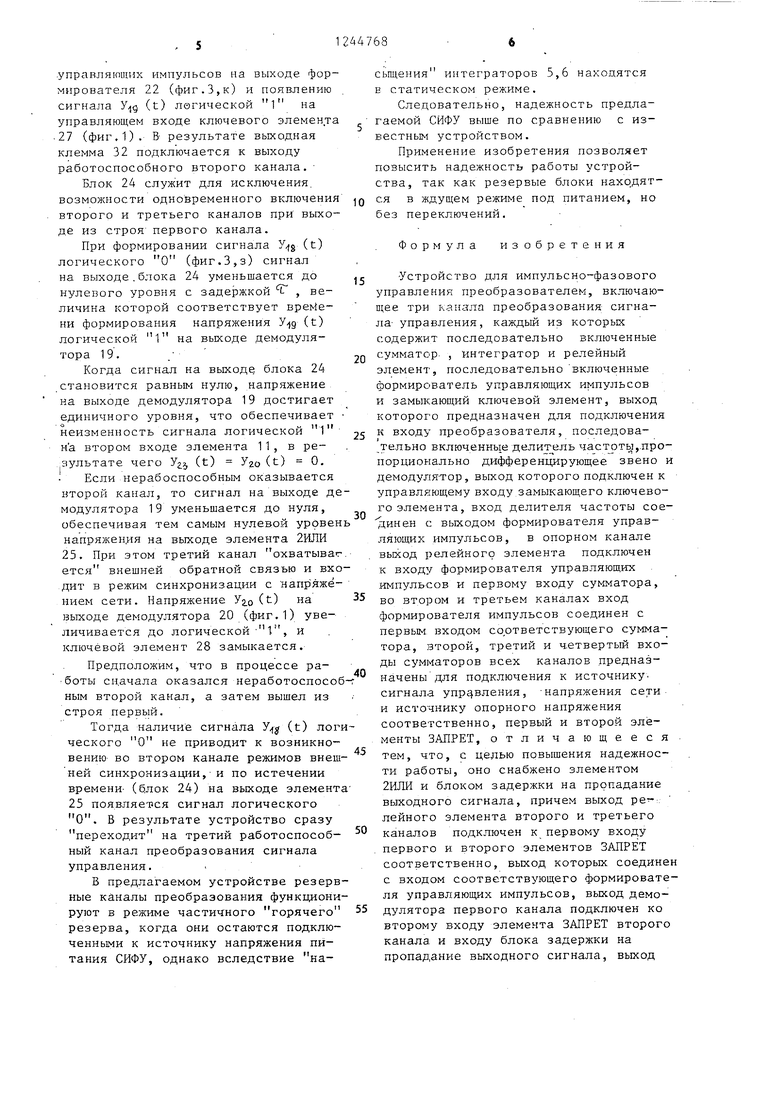

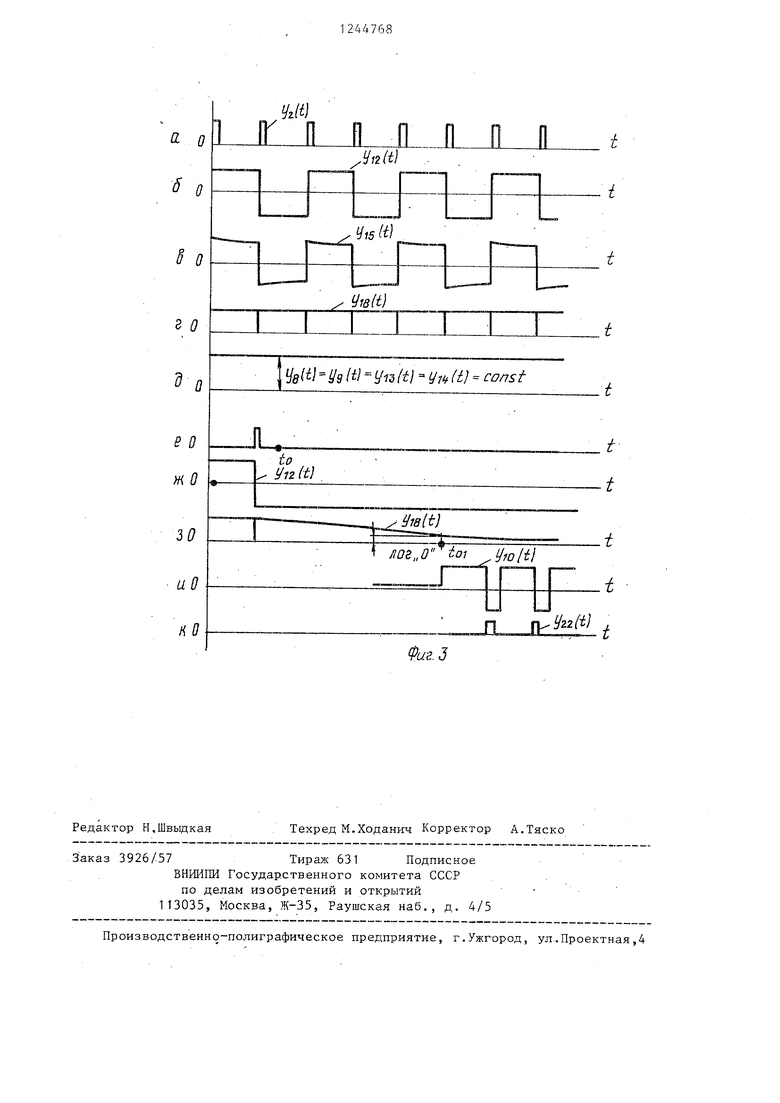

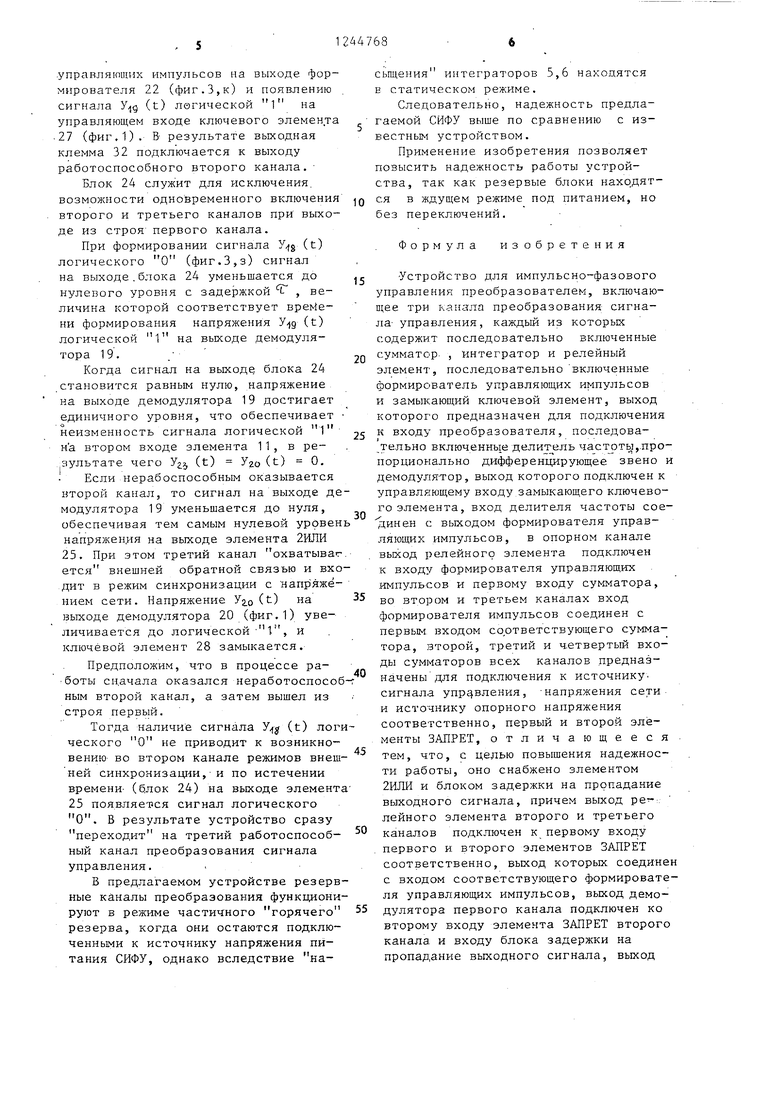

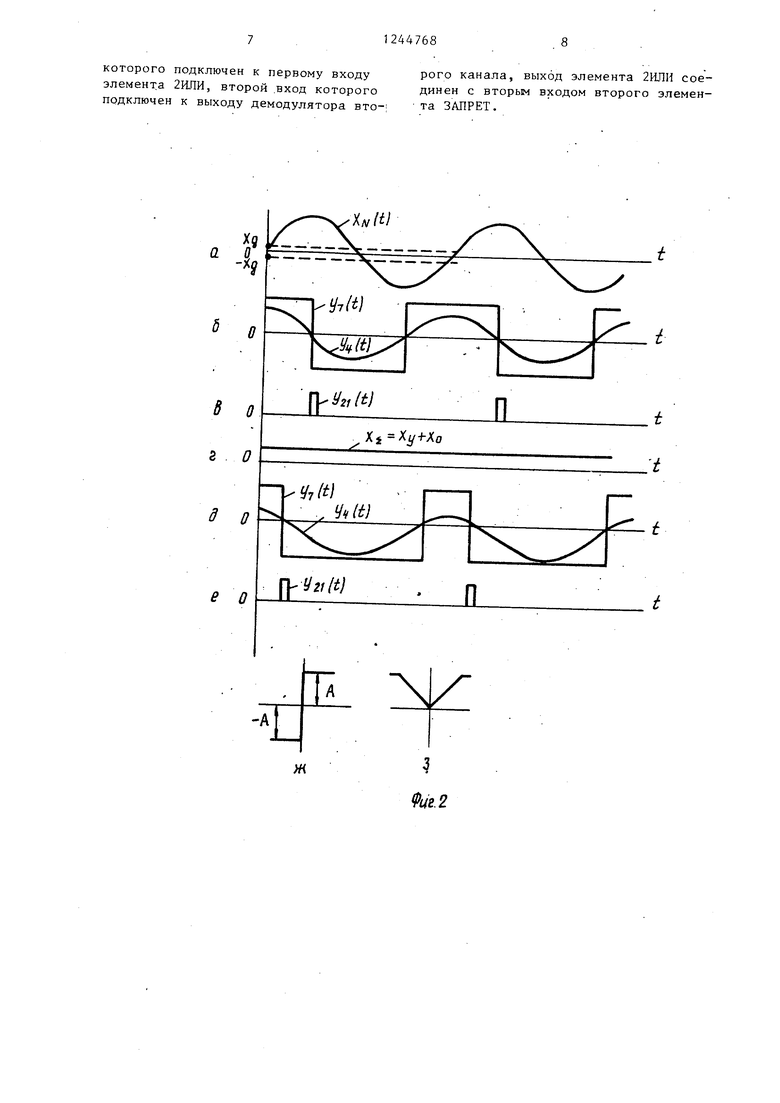

На фиг. 1 представлена функциональная схема устройства; на фиг.2 и 3 - временные диаграммы ее сигналов.

В состав устройства (фиг.1) входят сумматоры 1,2, 3, интеграторы 4, 5, 6, релейные элементы 7, 8,9, элементы ЗАПРЕТ 10,11, делители 12,13,14 частоты, пропорционально-дифференцирующие звенья 15, 16, 17, демодуляторы 18, 19, 20, формировател} 21, 22, .23 управляющих импульсов, блок 24 задержки времени на пропадание выходного сигнала, элемент 2 ИЛИ 25, .нормально разомкнутые ключевые элементы 26, 27, 28, клеммы 29, 30, 31 для подключения источников сигнала о управления Ху, напряжения сети X(t) и опорного напряжения Х соответствен- но и выходная клемма 32.

Источник XQ служит для задания начального угла управления тиристорами силового блока (не показан),

С помощью сигнала X(t) осущест- , вляется синхронизация работы устройства с соответствующей фазой .напряжения сети.

Сигнал Ху осуществляет сдвиг управляющих импульсов тиристорами относительно напряжения X(t).

Интеграторы 4,5,6 имеют передаточную функцию W(P)1/Tp, где Т - постоянная времени.

Релейные элементы 7,8,9 имеют нулевое значение порогов переключения (фиг. 2,ж), а их выходной сигнал может меняться в пределах J;A.

Выходной сигнал элементов ЗАПРЕТ 10,11 повторяет форму импульсов на выходе релейных элементов 8,9 при отсутствии сигнала на втором входе и .равен нулю, если сигнал на втором входе элементов 10, 11 соответствует Уровню логич еской 1.

Формирователи 21, 22, 23 формируют импульсы заданной длительности и мощности, необходимой для перевода тиристоров силового блока в открытое Состояние.

.Делители 12, 13, 14 частоты (триггеры) имеют коэффициент деления, рав- иый2,0, а их выходной сигнал типа меандр характеризуется нулевым значением постоянной составляющей.

2447682

. Пропорционально-дифференцирую

5

0

5

0

5

0

5

0

W(P)

щие звенья 15,16,17 выполнены с передаточной функцией

TIP

Т7

. .

а постоянная времени Т выбирается с таким расчетом.;, чтобы передать переменную составляющую выходного сигнала делителя частоты без искажений.

Статическая характеристика демодуляторов IB, 19, 20 показана на фиг.2,3.

Сигнал на выходе блока 24 достигает уровня логической 1 синхронно с появлением логической 1 на его входе И-уменьшается до нулевого уровня с задержкой i по отношению к моменту времени формирования логического О.на выходе демодулятора 18.

Принцип работы устройства следующий.

Пе)вый канал, образованньш блоками 1,4,7,21, является основным каналом, преобразования сигнала,управления Ху и преднахначен для формирования уп- равляющих импульсов тиристоров силового блока, фазовый сдвиг которых по отношению к напряжению X(t) является функцией сигнала Ху.

При отсутствии сигнала Xrv(t) блоки 1,4,7 в совокупности образуют ав- токолебат ельную систему с частотно- широтно-импульсной модуляцией.

Наличие сигнала X(t) на входе 30 устройства приводит к синхронизации моментов переключения блока 7. с частотой напряжения сети устройства. Для этого амплитуда напряжения X (t) выбирается намного больше допустимого входного сигнала ;Хп(фиг. 2, а), определяемого линейным участком статической характеристики блоков 1,4,7. Напряжение X(t) приводит к формированию на входе интегратора 4 синусоидального сигнала У, (t) (фиг . 2,6), сдвинутого по отношению к синхронизирующему воздействию (фиг.2,а) на угол порядка (30-90) эл.град (в зависимости от параметров блоков 4,7 и характеристик синхронизирующего действия - амплитуды и частоты).

Переключение релейного элемента 7 происходит в моменты времени вьтол- нения условия J(t) О (фиг.2,б).

Синхронно, с моментом времени изменения знака импульсов на выходе блока 7 формирования переднего или

12

заднего фронта сигнала ) на выходе формирователя 21 фop нpyeтcя импульс ) стабильной длительности и мощности, достаточных для надежного включения тиристоров силового блока (фиг.2,в).

С помощью опорного напряжения Х,, устанавливается начальный угол включения ,силовых тиристоров.

Под действием результирующего сигнала Yy + Х, (фиг. 2, г) сигнал . на выходе интегратора 4 (фиг. 2,д) сме11(ается вертикально относительно нулевого уровня, что вызывает изменение скважности импульсов ) на выходе релейного элемента 7. Это влечет за собой фазовый сдвиг импульсов (t) (фиг.2,е) по отнощению

к напряжению сети (фиг.2,а). В результате изменяется продолжительность включенного состояния тиристоров силового блока.

Второй и третий каналы, образованные блоками 2,5,8,10 и 3,6,9,11, являются резервными по отношению к первому каналу.

Диагностирование работоспособности каналов преобразования сигнала у.п- равления CHOY производится с помо-; щью блоков диагностирования 5 в тав которых входят блоки (12,15,18),

(13,16,19) и (14, 17,20) .. Принцип их действия идентичен. Рассмотрим тракт ,18.

Переключение делителя 12 частоты происходит синхронно с моментом времени формирования импульсов на выходе формиро.вателя 21 (фиг.3,а). При этом на выходе делителя 12 частоты формируется сигнал У (t) типа мелндр со средним нулевым значением (фиг.3,6).

В демодуляторе 18 выходные импульсы пропордионально-дифференцирующего звена 15 (фиг.3,в) выпрямляются и при необходимости фильтруются (фиг.3,г).

Таким образом формируется сигнал , логической 1, свидетельствующий о нормальЪой работоспособности кана- 50 ла 1,4,7,21. Под действием сигнала (t) .ключевой элемент 26 (фиг.1) замыкается и выход 32 устройства подключается к выходу формирователя 21 управляющих импульсов (фиг.3,г). 55

Наличие сигнала логической 1 на выходе блока 18 приводит к форми- рованию сигнала логического О

5

o

о

5

5

5

0 5

7684

на выходе элемента ЗАПРЕТ 10, по- этому сигнал (t) на выходе формирователя 22 равен нулю.

Под действием постоянной.составляющей -управляющего Ху и опорного XQ сигналов выходной сигнал интегратора 5 достигает уровня зоны насыщения статической характеристики операционного усилителя, на основе которого выполнены блоки 4,5,6, Б результате напряжение на выходе релейного элемента 8 фиксируется в одном из состояний ±А (фиг,2,ж), например в положительном +А (фиг.3,д).

Отсутствие импульсов на выходе формирователя 22 приводит к появлению, на выходе демодулятора 19 сигналов (t) логического О, поэтому ключевой элемент 27 находится в ра- зомкнутом состоянии.

Напряжение логической 1 на выходе блока 24 формируется синхронно с сигналом логической 1 на выходе . демодулятора 18, что приводит к появлению сигнала .логической 1 на выходе элемента 25. В результате напряжение на выходе блоков 11, 23 равно нулю и ключ 28 находится в исходном разомкнутом состоянии..Напряжение Y9(t)-TaK же, как и сигналы Yg(t),-. (t), (t) , фиксируется в одном из состояний +А(фиг.1 и Зд).

Предположим, что первьш канал в мо- ,мент времени Со(фиг.3,е) оказался неработоспособным, что приводит в диапазоне t t к отсутствию управляющих импульсов У (t) на входе делителя 12 частоты и фиксации напряжения . (t), например, в отрица-- тельном СОСТОЯНИИ (фиг.3,ж). Y4H- тывая, что пропорционально-дифференцирующее звено 15 не пропускает постоянной составляющей напряжения, сигнал (t) на выходе 18 уменьшается -до нуля (фиг.3,в). .

В момент времени t (фиг.3,з) когда Y)(t) О, ключевой элемент 26 размыкается, а на выходе элемента ЗАПРЕТ 10 появляется сигнал 5 (t), повторяющий знак и урове нь напряжения на выходе релейного элемента 8. Это влечет за собой синхронизацию сигналом .X(t) второго канала, и на его выходе появляется сигнал , (фиг.3,и) (t), аналогичный напря-г жению (фиг.2,б,д) Yr(t)npH работоспособности первого канала.

Наличие импульсов на выходе элемента 10 приводит к формированию

.управляюип х импульсов на выходе формирователя 22 (фиг.3,к) и появлению сигнала (t) логической 1 на управляющем входе ключевого элемента .27 (фиг.1). В- результате выходная клемма 32 подключается к выходу работоспособного второго канала.

Блок 24 служит для исключения, возможности одновременного включения второго и третьего каналов при выходе из строя первого канала.

При формировании сигнала (t) логического О (фиг.3,з) сигнал на выходе.блока 24 уменьшается до нулевого уровня с задержкой , величина которой соответствует вреМе- ни формирования напряжения Y-jg (t) логической 1 на выходе демодулятора 19.

Когда сигнал на выходе блока 24 становится равным нулю, напряжение на выходе демодулятора 19 достигает единичного уровня, что обеспечивает

на втором входе элемента 11, в ре- ; ультате чего (t) YZO (t) 0.

Если нерабоспособным оказывается второй канал, то сигнал на выходе демодулятора 19 уменьшается до нуля, обеспечивая тем самым нулевой уровень напряжения на выходе элемента 2ИЛИ 25. При этом третий канал охватываг-. ется внешней обратной связью и входит в режим синхронизации с напр яжё- нием сети. Напряжение У2.о (t) на выходе демодулятора 20 (фиг.1) увеличивается до логической , И ключевой элемент 28 замыкается.

Предположим, что в процессе ра- боты сначала оказался неработоспособным второй канал, а затем вышел из строя первый.

Тогда наличие сигнала (t) логического О не приводит к возникновению во втором канале режимов внешней синхронизации, и по истечении времени- (блок 24) на выходе элемента 25 появляется сигнал логического О. В результате устройство сразу

переходит на третий работоспособный канал преобразования сигнала управления.

В предлагаемом устройстве резервные каналы преобразования функционируют в режиме частичного горячего резерва, когда они остаются подключенными к источнику напряжения питания СИФУ, однако вследствие на

5

0

сьпцения интеграторов 5,6 находятся Е статическом режиме.

Следовательно, надежность предла- . гаемой CHOY выше по сравнению с известным устройством.

Применение изобретения позволяет повысить надежность работы устройства, так как резервые блоки нахо.дят- Q ся в ждущем режиме под питанием, но без переключений.

Формула изобретения

Устройство для импульсно-фазового управления преобразователем, включающее три канала преобразования сигнала- управления, каждый из которых содержит последовательно включенные сумматор , интегратор и релейный элемент, последовательно включенные формирователь управляющих импульсов и замыкающий ключевой элемент, выход которого предназначен для подключения

5 к входу преобразователя, последовательно включенные делитель частоты,.пропорционально дифференцирующее звено и демодулятор, выход которого подключен к управляющему входу замыкающего ключевого элемента, вход делителя частоты сое- динен с выходом формирователя управляющих импульсов, в опорном канале выход релейного элемента подключен к входу формирователя управляющих :импульсов и первому входу сумматора, во втором и третьем каналах вход формирователя импульсов соединен с первым входом соответствующего сумматора, второй, третий и четвертый входы сумматоров всех каналов дредназ- на.чены для подключения к источнику, сигнала управления, -напряжения сети и источнику опорного напряжения соответственно, первый и второй элементы ЗАПРЕТ, отличающееся тем, что, с целью повышения надежности работы, оно снабжено элементом 21-ШИ и блоком задержки на пропадание вьлходного сигнала, причем выход . лейного элемента второго и третьего каналов подключен к первому входу первого и второго элементов ЗАПРЕТ соответственно, выход которых соединен с входом соответствующего формирователя управляющих импульсов, выход демо5 дулятора первого канала подключен ко второму входу элемента ЗАПРЕТ второго канала и входу блока задержки на пропадание выходного сигнала, выход

0

5

0

5

0

которого подключен к первому входу элемента 2ИЛИ, второй .вход которого подключен к выходу демодулятора вто-;

рого канала, выход элемента 2ИЛИ соединен с вторым входом второго элемента ЗАПРЕТ.

| название | год | авторы | номер документа |

|---|---|---|---|

| СИСТЕМА УПРАВЛЕНИЯ ГРУППОЙ АСИНХРОННЫХ ЭЛЕКТРОПРИВОДОВ ВОДЯНЫХ НАСОСОВ | 2003 |

|

RU2251206C2 |

| Устройство для управления вентильным преобразователем | 1983 |

|

SU1094129A1 |

| МНОГОЗОННЫЙ РАЗВЕРТЫВАЮЩИЙ ПРЕОБРАЗОВАТЕЛЬ ДЛЯ ПЕРЕДАЧИ ЛОГИЧЕСКИХ ДАННЫХ ПО ОДНОПРОВОДНОЙ ЛИНИИ СВЯЗИ | 2001 |

|

RU2206922C2 |

| Цифровое устройство для управления машиной непрерывного литья заготовок | 1989 |

|

SU1632621A1 |

| Регулируемый тиристорный преобразователь переменного напряжения в переменное | 1980 |

|

SU951636A1 |

| ДАТЧИК НУЛЕВОГО ТОКА | 2009 |

|

RU2390906C1 |

| СИСТЕМА УПРАВЛЕНИЯ ГРУППОЙ ЭЛЕКТРОПРИВОДОВ С ПАРАЛЛЕЛЬНЫМИ КАНАЛАМИ РЕГУЛИРОВАНИЯ | 2014 |

|

RU2565598C1 |

| Устройство для релейного управления тиристорным преобразователем тягового электропривода постоянного тока,подключенным к питающей сети через входной фильтр | 1984 |

|

SU1193023A1 |

| Устройство для импульсно-фазового управления преобразователем | 1983 |

|

SU1094127A1 |

| Система управления | 1984 |

|

SU1211688A1 |

Изобретение относится к электротехнике, а именно к системам управ- -ления вторичных источников питания. Цель изобретения - повышение надежности. Устройство содержит три канала преобразования сигнала управления. выполненных на cyNMaTopax 1, , . . релейных элементах 7, 8, 9, элементах 10, 11 ЗАПРЕТ , делителях частоты 12, 13, 14, пропорционально-диффе- ренцируюпщх звеньях 15, 16, 17, демодуляторах 18, 19, 20, формирователях 21, 22, 23, нормально разомкнутых ключевых элементах 26, 27, 28. Введение блока 24 задержки времени на пропадание выходного сигнала не позволяет одновременное включение второго и третьего каналов при выходе - из строя первого канала. Резервные каналы преобразования функционируют в режиме частичного горячего резерва, когда они остаются подключенными к источнику напряжения питания системы управления, однако находятся в статическом режиме. Это повышает надежность устройства. 3 ил. 1C (Л Ко Ю 4 4ih sj Од 00 witl

Ц

а f

о

о

о

о

о

2fM

х

Xi

..

-У21М

п

,i Ч

А

ж

Ф14г.2

Авторы

Даты

1986-07-15—Публикация

1984-09-03—Подача