1 1

Изобретение относится к; электро- . ехнике, а именно к системам управения автономными инверторами с ши- отно-импульсной модуляцией и может быть использовано в частотно-регулиуемых электроприводах с широким иапазоном регулирования и управления от микропроцессоров или мини-ЭВМ.

Целью изобретения является расшиение функциональных возможностей.

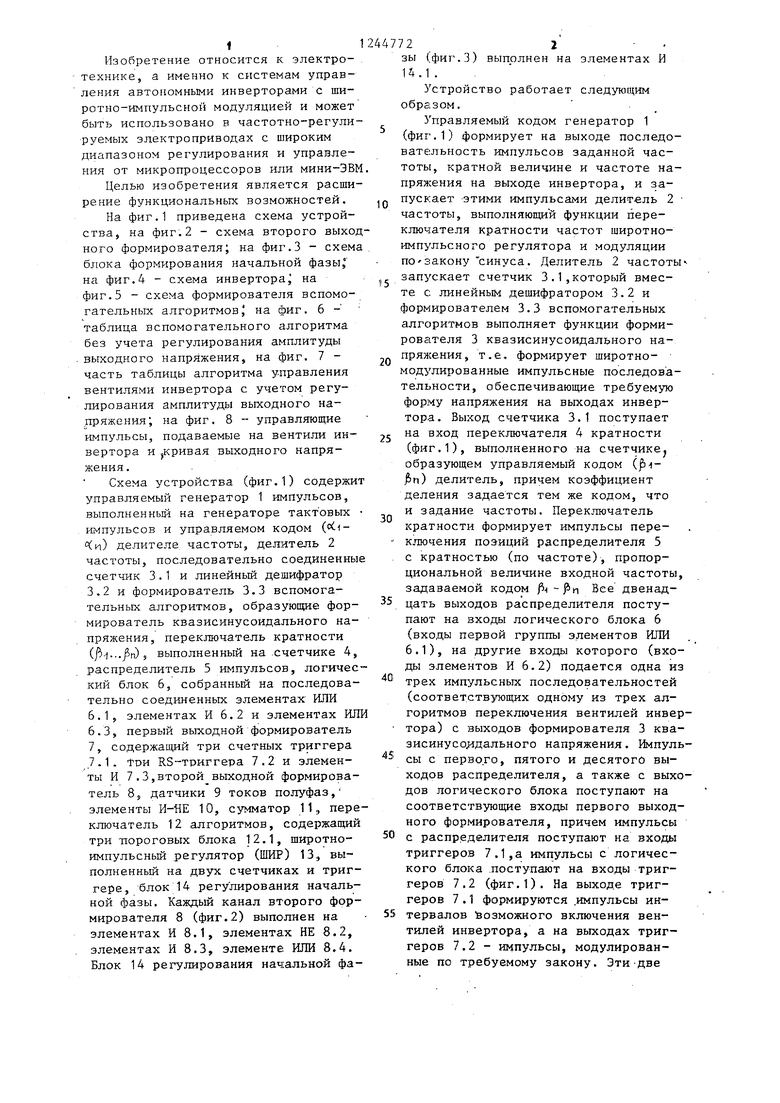

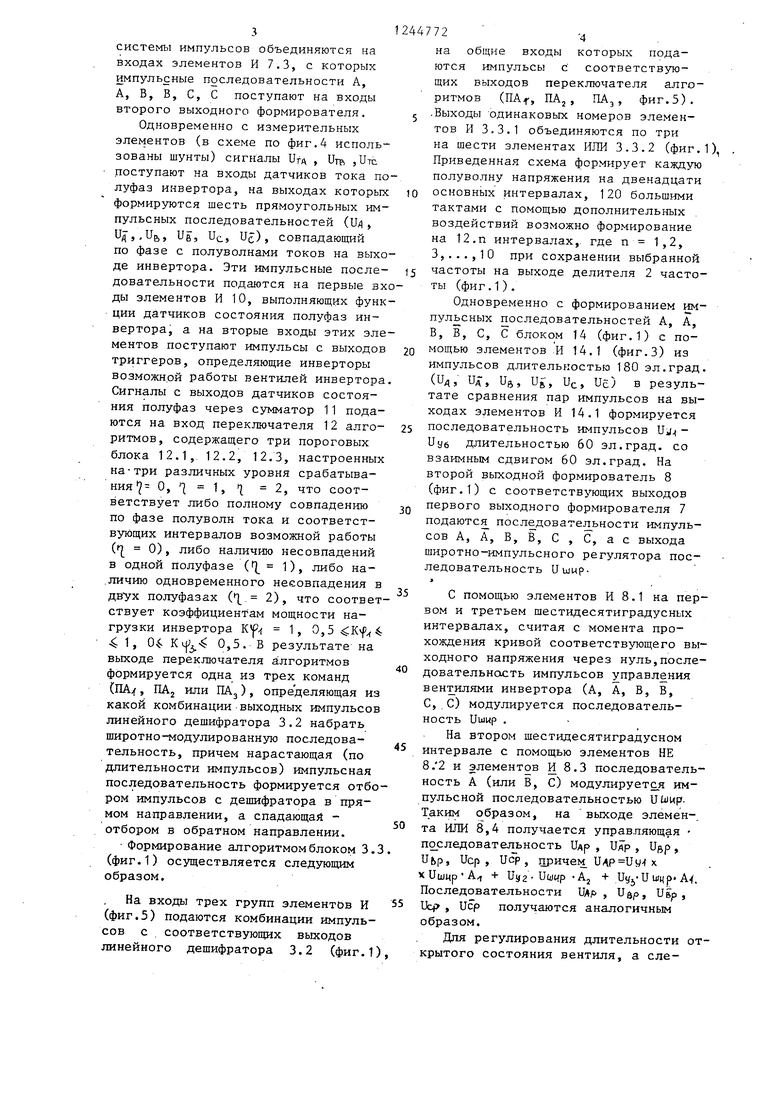

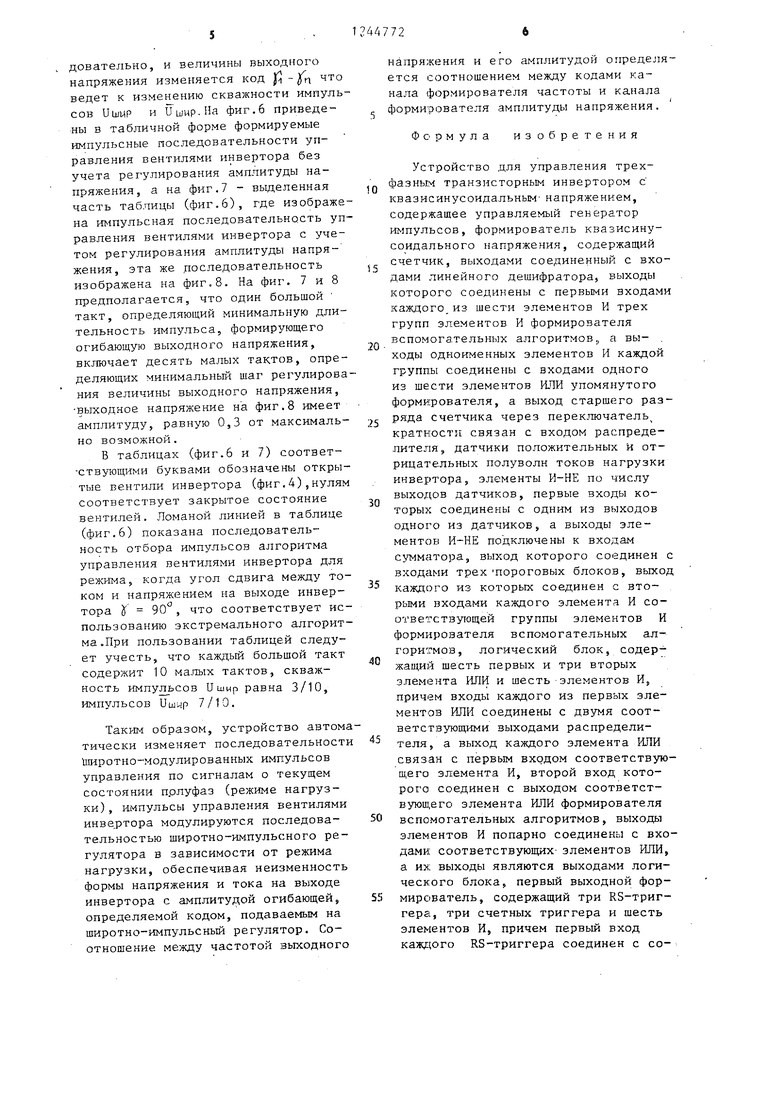

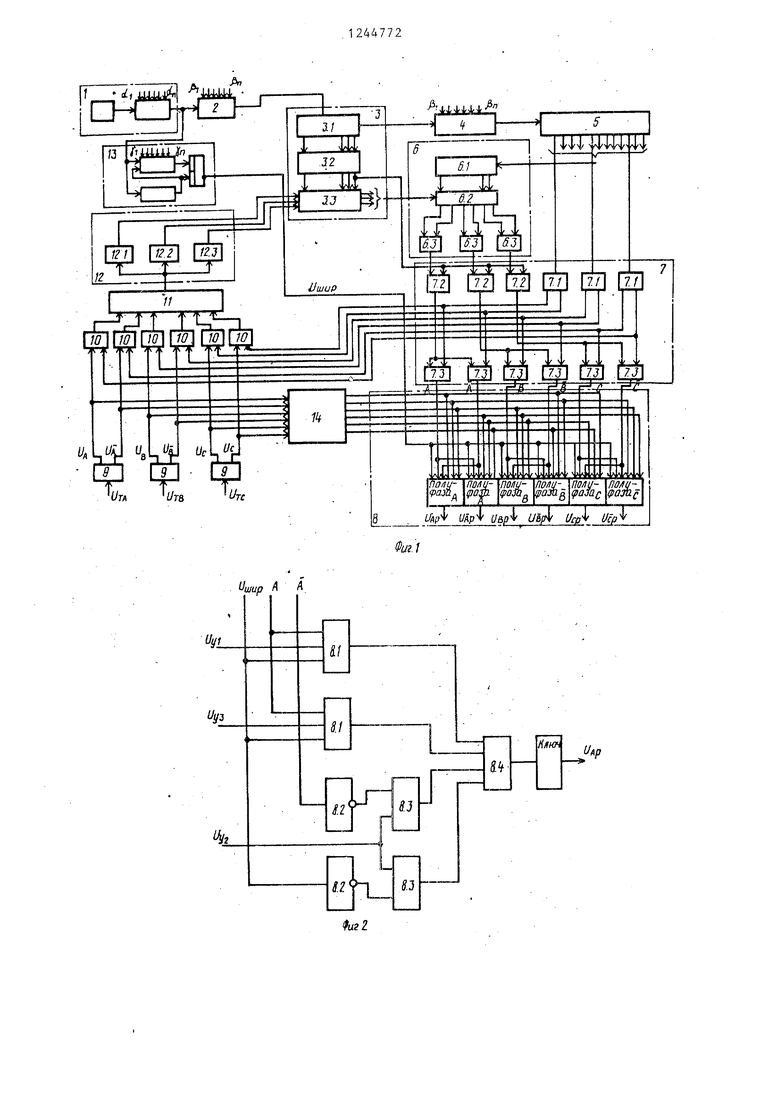

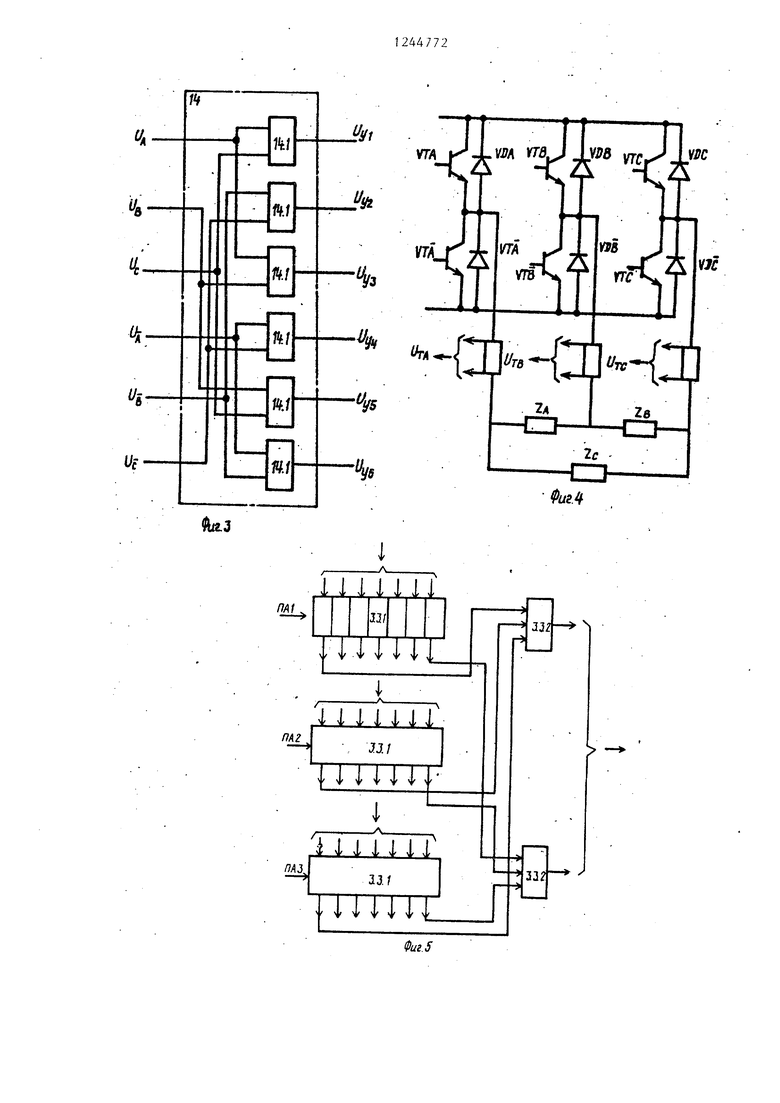

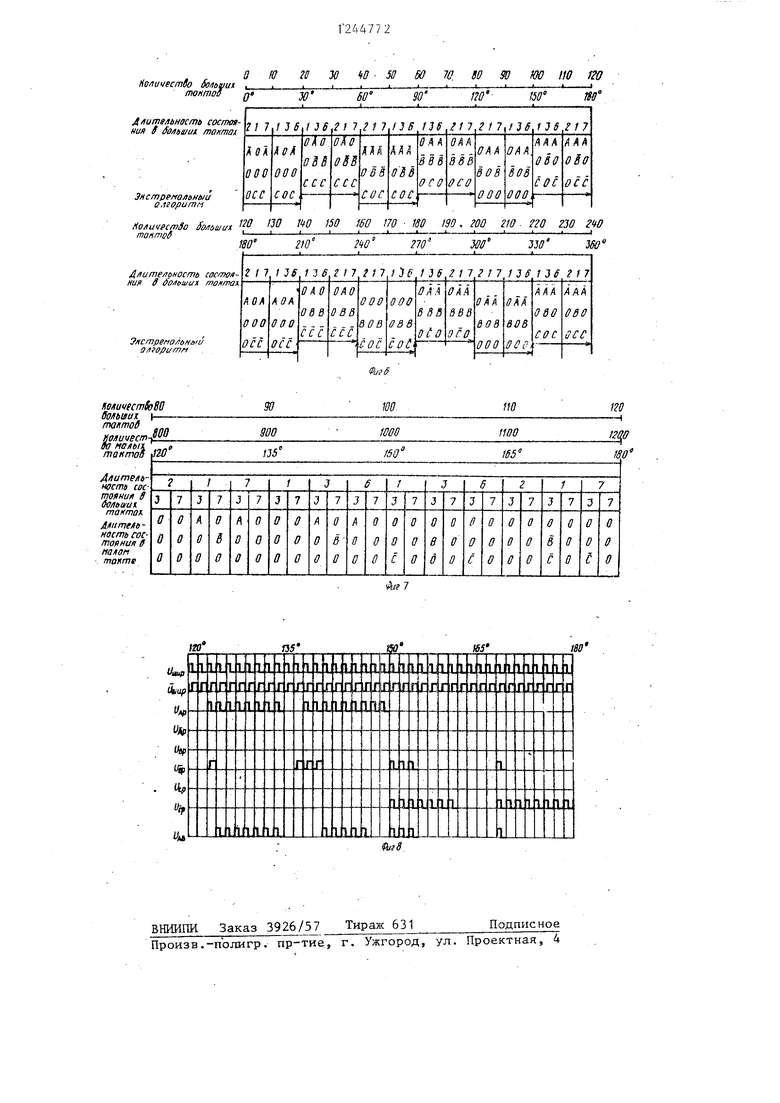

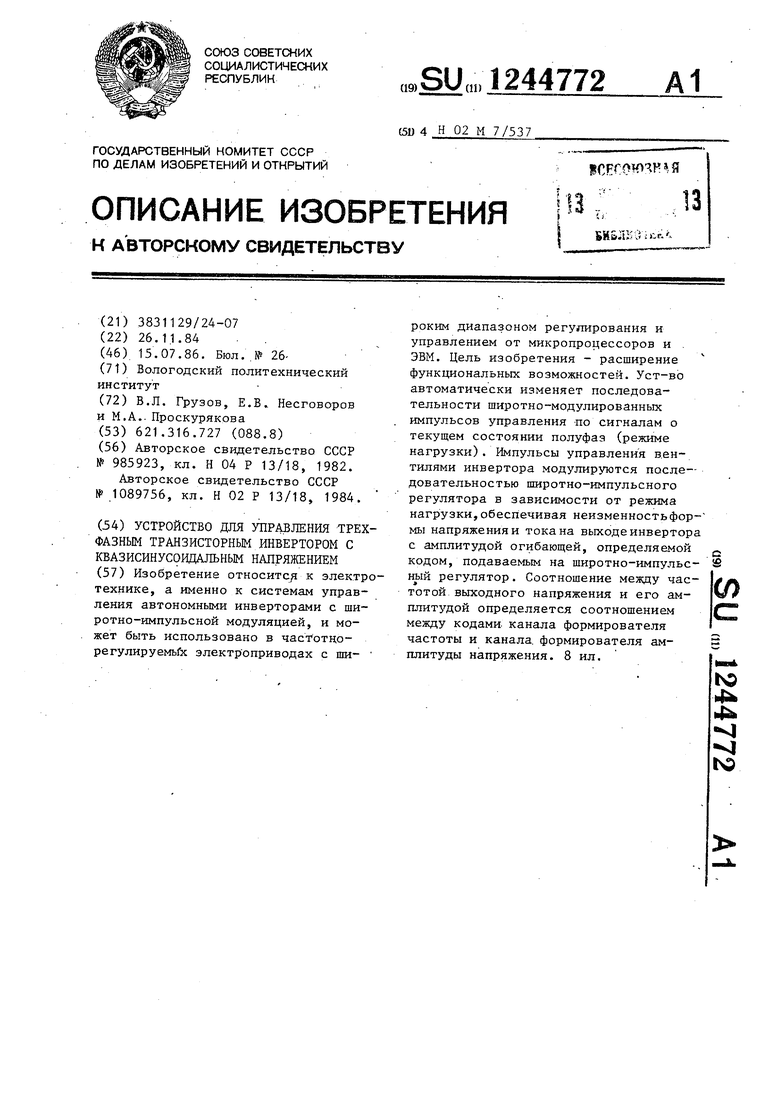

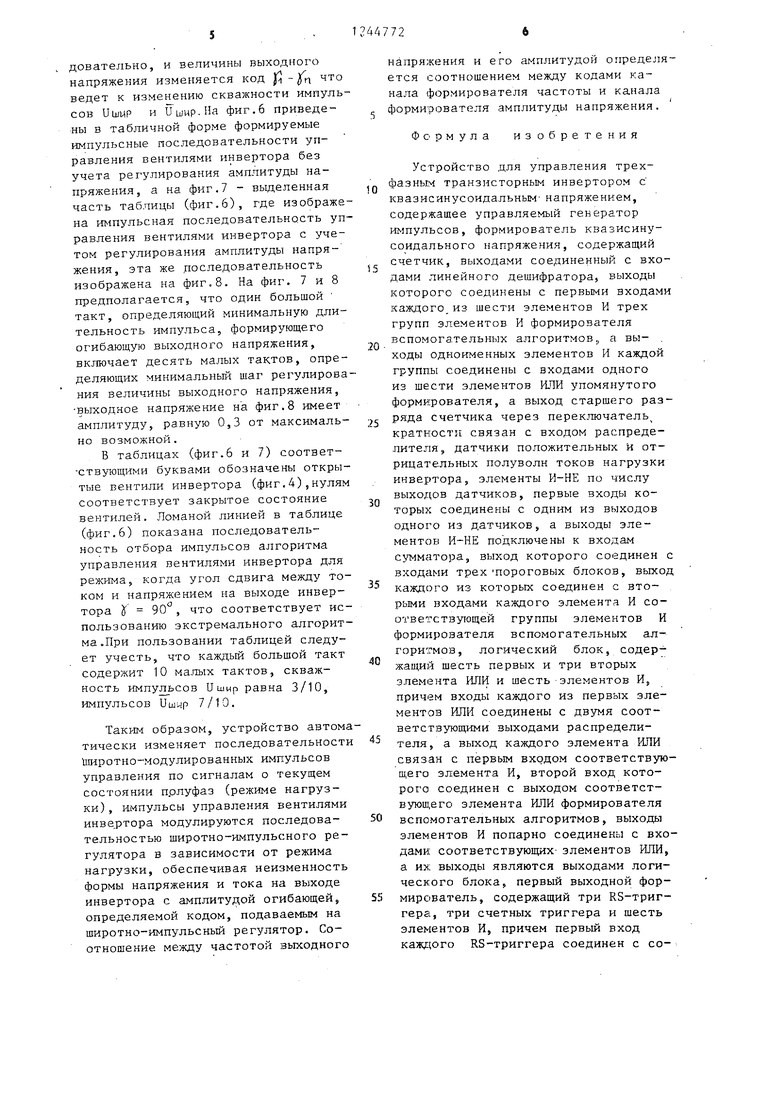

На фиг.1 приведена схема устройства j на фиг.2 - схема второго выходного формирователя; на фиг.З - схема блока формирования начальной фазы, на фиг.4 - схема инвертораj на фиг.З - схема формирователя вспомогательных алгоритмовJ на фиг. 6 - таблица вспомогательного алгоритма без учета регулирования амплитуды выходного напряжения, на фиг. 7 - часть таблицы алгоритма управления вентилями инвертора с учетом регулирования амплитуды выходного напряжения; на фиг. 8 - управляющие импульсы, подаваемые на вентили инвертора и Jкpивaя выходного напряжения.

Схема устройства (фиг.1) содержит управляемый генератор 1 И1 1пульсов, выполненный на генераторе такт овых импульсов и управляемом кодом (oC-i- о(и) делителе частоты, делитель 2 частоты, последовательно соединенные счетчик 3.1 и линейный дешифратор 3.2 и формирователь 3.3 вспомогательных алгоритмов, образующие формирователь квазисинусоидального напряжения, переключатель кратности ф-)...п)5 выполненный на .счетчике 4, распределитель 5 импульсов, логический блок 6, собранный на последовательно соединенных элементах РШИ 6.1, элементах И 6.2 и элементах ИЛИ 6.3, первый выходной фюрмирователь 7, содержащий три счетных триггера 7.1. Три RS-триггера 7.2 и элементы И 7.3,второй выходной формирователь 8,- датчики 9 токов полуфаз, элементы И-НЕ 10, сумматор 11,, переключатель 12 алгоритмов, содержащий три тюроговых блока 12.1, широтно- импульсный регулятор (ШИР) 13, вы- полненньш на двух счетчиках и триг- гере, блок 14 регулирования начальной фазы. Каждый канал второго формирователя 8 (фиг.2) выполнен на элементах И 8.1, элементах НЕ 8.2, элементах И 8.3, элементе ИЛИ 8.4. Блок 14 регулирования начальной фа447722

зы (фиг.З) выполнен на элементах И 14.1 . .

З стройство работает следующим образом.

5 правляемый кодом генератор 1 (фиг.1) формирует на выходе последовательность импульсов заданной частоты, кратной величине и частоте напряжения на выходе инвертора, и пускает Этими импульсами делитель 2 частоты, выполняющий функции переключателя кратности частот широтно- импульсного регулятора и модуляции по Закону синуса. Делитель 2 частоты

,ij запускает счетчик 3.1,который вместе с линейным дешифратором 3.2 и формирователем 3.3 вспомогательных алгоритмов выполняет функции формирователя 3 квазисинусоидального на- пряжения, т.е. формирует широтно- модулированные импульсные последовательности, обеспечивающие требуемую форму напряжения на выходах инвертора. Выход счетчика 3.1 поступает

25 на вход переключателя 4 кратности (фиг.1), выполненного на счетчике, образующем управляемый кодом (fn- п) делитель, причем коэффициент деления задается тем же кодом, что и задание частоты. Переключатель кратности формирует импульсы переключения позиций распределителя 5 с кратностью (по частоте), пропорциональной величине входной частоты, задаваемой кодом /i -ji Все двенад35 дать выходов распределителя поступают на входы логического блока 6 (входы первой группы элементов ИЛИ 6.1), на другие входы которого (входы элементов И 6.2) подается одна из трех импульсных последовательностей (соответствующих одному из трех алгоритмов переключения вентилей инвертора) с выходов формирователя 3 ква- зисинусодадального напряжения, импульсы с первого, пятого и десятого выходов распределителя, а также с выходов логического блока поступают на соответствующие входы первого выходного ф ормирователя, причем импульсы

с распределителя поступают на входы триггеров 7.1,а импульсы с логического блока .поступают на входы триггеров 7.2 (фиг.1). На выходе триггеров 7.1 формируются .импульсы ин- 55 тервалов возможного включения вентилей инвертора, а на выходах триггеров 7.2 - импульсы, модулированные по требуемому закону. Эти-две

30

4Q.

45

50

системы импульсов объединяются на входах элементов И 7.3, с которых импульсные последовательности А, А, В, В, С, С поступают на входы второго выходного формирователя. Одновременно с измерительных элементов (в схеме по фиг.4 использованы шунты) сигналы и-рд , UTB jUic поступают на входы датчиков тока по луфаз инвертора, на выходах которых формируются шесть прямоугольных импульсных последовательностей (Щ, Uflj-Up,, UB, Uc, Uc), совпадающий по фазе с полуволнами токов на выходе инвертора. Эти импульсные последовательности подаются на первые вхды элементов И 10, выполняющих функции датчиков состояния полуфаз инвертора, а на вторые входы этих элементов поступают импульсы с выходов триггеров, определяющие инверторы возможной работы вентилей инвертора Сигналы с выходов датчиков состояния полуфаз через сумматор 11 подаются на вход переключателя 12 алгоритмов, содержащего три пороговых блока 12.1, 12.2, 12.3, настроенных на-три различных уровня срабатывания 7 О 1 1 1 2, что соответствует либо полному совпадению по фазе полуволн тока и соответствующих интервалов возможной работы С 0), либо наличию несовпадений в одной полуфазе (Т 1), либо на- .личию одновременного несовпадения в двух полуфазах (. 2), что соответствует коэффициентам мощности нагрузки инвертора К р 1, 0,5 :Kvf 41,0 fi- 0,5. В результате на выходе переключателя алгоритмов формируется одна из трех команд (ПА , IIAj или riAj), определяющая из какой комбинации.выходных импульсов линейного дешифратора 3.2 набрать широтно-модулированную последовательность, причем нарастающая (по длительности импульсов) импульсная последовательность формируется отбором импульсов с дешифратора в прямом направлении, а спадающай - отбором в обратном направлении.

Формирование алгоритмом блоком 3.3 (фиг.1) осуществляется следующим образом.

На входы трех групп элементов И (фиг.5) подаются комбинации импульсов с соответствующих выходов линейного дешифратора 3.2 (фиг.1

0

5

0

5

5

0

0

5

на общие входы которых подаются импульсы с соответствующих выходов переключателя алгоритмов (ПА, IIAj , ELAj , фиг.5). .Выходы одинаковых номеров элементов И 3.3.1 объединяются по три на шести элементах ИЛИ 3.3.2 (фиг.1), Приведенная схема формирует каждую полуволну напряжения на двенадцати основных интервалах, 120 большими тактами с помощью дополнительных воздействий возможно формирование на 12.П интервалах,- где п 1,2, 3,...,10 при сохранении выбранной частоты на выходе делителя 2 частоты (фиг.1).

Одновременно с формированием tM- пульсных последовательностей А, А,

B,В, С, С блоко|М 14 (фиг.1) с помощью элементов Е 14.1 (фиг.З) из импульсов длительностью 180 эл.град. (Пд, ид-, U5, Ug, Uc, Uc) в результате сравнения пар импульсов на выходах элементов И 14.1 формируется последовательность импульсов Пуб длительностью 60 эл.град. со взаимным сдвигом 60 эл.град. На второй выходной формирователь 8 (фиг.1) с соответствующих выходов первого выходного формирователя 7 подаются последовательности импульсов А, А, В, В, С , С, а с выхода широтно-импульсного регулятора последовательность Uuiup

С помощью элементов И 8.1 на первом и третьем шестидесятиградусных интервалах, считая с момента прохождения кривой соответствующего выходного напряжения через нуль,после- довательноьсть импульсов управления вентилями инвертора (А, А, В, В,

C,С) модулируется последовательность ишир .

На втором шестидесятиградусном интервале с помощью элементов НЕ 8. 2 и элементов И 8.3 последовательность А (или В, С) модулируется импульсной последовательностью UUiwp- Таким образом, на выходе элемен-, та ИЛИ 8,4 получается управляющая последовательность Плр , Идр , U/jp , Ubp, Ucp , Ucp , причем ( X xUuJup A + Uya-UwHp Aj + Uyj-Umnp-A. Последовательности UAP , Ugp, USp , Ut4 , Ucp получаются аналогичным образом.

Для регулирования длительности открытого состояния вентиля, а еледовательно, и величины выходного напряжения изменяется код )и - п что ведет к изменению скважности импульсов иымР и UuHp.lia фиг.6 приведены в табличной форме формируемые импульсные последовательности управления вентилями инвертора без учета регулирования амплитуды напряжения, а на фиг.7 - вьщеленная часть таблицы (фиг.6), где изображена импульсная последовательность управления вентилями инвертора с учетом регулирования амплитуды напряжения, эта же последовательность изображена на фиг.8. На фиг. 7 и 8 предполагается, что один большой такт, определяющий минимальную длительность импульса, формирующего огибающую выходного напряжения, включает десять малых тактов, определяющих минимальный шаг регулирования величины выходного напряжения, выходное напряжение на фиг.8 имеет амплитуду, равную 0,3 от максималь- но возможной.

В таблицах (фиг.6 и 7) соответ- ствующими буквами обозначены откры- Tbie вентили инвертора (фиг. Д),нулям соответствует закрытое состояние вентилей. Ломаной линией в таблице (фиг.6) показана последовательность отбора импульсов алгоритма управления вентилями инвертора для режима, когда угол сдвига между током и напряжением на выходе инвертора Ji 90 , что соответствует использованию экстремального алгоритма.При пользовании таблицей следует учесть, что каждый большой такт содержит 10 малых тактов, скважность импульсов и тир равна 3/10, импульсов ишчр 7/10.

Таким образом, устройство автоматически изменяет последовательности йиротно-модулированных импульсов управления по сигналам о текущем состоянии прлуфаз (режиме нагрузки), импульсы управления вентилями инвертора модулируются последовательностью широтно-импульсного регулятора в зависимости от режима нагрузки, обеспечивая неизменность формы напряжения и тока на выходе инвертора с амплитудой огибающей, определяемой: кодом, подаваемым на широтно-импульсный регулятор. Соотношение между частотой выходного

.

напряжения и его амплитудой определяется соотношением между кодами канала формирователя частоты и канала формирователя амплитуды напряжения.

Формула изобретения

Устройство для управления трехфазным транзисторным инвертором с квазисинусоидальным- напряжением, содержащее управляемый генератор импульсов, формирователь квазисинусоидального напряжения, содержащий счетчик, вгз1ходами соединенный с входами линейного дешифратора, выходы которого соединены с первыми входами каждого из шести элементов И трех групп элементов И формирователя вспомогательных алгоритмов,, а вы- . ходы одноименных элементов И каждой группы соединены с входами одного из шести элементов ИЛИ упомянутого формирователя, а выход старшего разряда счетчика через переключатель кратности связан с входом распределителя, датчики положительных и отрицательных полуволн токов нагрузки инвертора, элементы И-НЕ по числу выходов датчиков, первые входы которых соединены с одним из выходов одного из датчиков, а выходы элементов И-НЕ поЬ,ключены к входам сумматора, выход которого соединен с входами трех пороговых блоков, выход каждого из которых соединен с вторыми входами каждого элемента И соответствующей группы элементов И формирователя вспомогательных алгоритмов, логический блок, содержащий шесть первых и три вторых элемента ИЛИ и шесть элементов И, причем входы каждого из первых элементов ИЛИ соединены с двумя соответствующими выходами распределителя, а выход каждого элемента ИЛИ связан с первым входом соответствующего элемента И, второй вход которого соединен с выходом соответст- вуюш,его элемента ИЛИ формирователя вспомогательных алгоритмов, выходы элементов И попарно соединены с входами соответствующих- элементов ИЛИ, а их выходы являются выходами логического блока, первый выходной формирователь, содержащий три RS-триг- гера, три счетных триггера и шесть элементов И, причем первый вход каждого RS-триггера соединен с соответствующим выходом логического блока, а вторые входы RS-триггеров связаны с выходом старшего разряда линейного дешифратора, входы счет- ных триггеров соединены с первым, пятым и десят ым выхода ми распределителя соответственно, каждый выход счетных триггеров соединен с вторым входом соответствующего элемента . И-НЕ и с первым входом соответствующего элемента И выходного формирователя, выход каждого RS-триггера соединен С вторыми входами двух соответствующих элементов И, а выход каж- дого элемента И является выходом управления частотой и формой одной из полуфаз напряжения (А,-А, В, В, С, С) первого выходного формирователя, отличающееся тем, что, с целью расширения функциональных возможностей, оно снабжено делителем частоты, входом соединенным с выходом управляемого генератора импульсов, а выходом связанного с входом счетчика формирователя ква- зисинусоидального напряжения, щирот- но-импульсным регулятором, блоком регулирования начальной фазы и вторым выходным формирователем, причем выход управляемого генератора импульсов соединен со счетными входами первого (управляемого) и второго (неуправляемого) счетчиков широтно- импульсного регулятора, выход первого счетчика соединен с первым входом RS-триггера, выход второго счетчика соединен с вторым входом RS-триггера и с установочным входом первого счетчика, параллельные входы кото- рого являются входами управления амплитудой напряжения преобразователя, а инверсный выход RS-т риггера является выходом широтно-импульсно- го регулятора, блок регулирования начальной фазы содержит шесть элементов И, первые входы первого и третьего элементов И соединены с выходом положительной полуволны датчика тока фазы Ау первые входы четвертого и шестого элементов И соединены с выходом отрицательной полуволны датчика тока фазы В, первый вход второго элемента И и второй вход шестого элемента И соеди

5 10 15 20 25 зо „

5

5

нены с выходом положительной полуволны датчика фазы С,второй вход третьего элемента И и первый вход пятого элемента И соединены с выходом отрицательной полуволны датчика тока А,, второй вход первого элемента И и второй вход пятого элемента И соединены с выходом положительной полуволны датчика тока фазы В, второй вход второго элемента И и второй вход четвертого элемента И соединены с выходом отрицательной полуволны датчика тока фазы С, а выходы элементов И с первого по шестой являются выходами блока регулирования начальных фаз для управления полуфаэами А, S, В, В, С, С соовет- ственно, второй выходной формирователь содержит шесть однотипных блоков формирования сигналов управления полуфаз, каждый из которых содержит четьфе элемента И, два элемента НЕ, элемент ИЛИ и ключ, причем первые входы первого и второго элементов И соединены с выходом управления соответствующей полуфазой первого выходного формирователя, вход первого элемента НЕ соединен с выходом управления противофазным каналом первого выходного формирователя, второй вход первого элемента И соединен с выходом блока регулирования начальной фазы соответствующей полуфазы, второй

вход второго элемента И соединен с выходом блока регулирования начальной фазой, соответствующего фазе,

сдвинутой на -Г-1Г по отношению к данной фазе, а третьи входы первого и второго элементов И и вход второго элемента НЕ связаны с выходом широт- но-импульсного регулятора, выходы первого и второго элементов- НЕ соединены с первыми входами третьего и четвертого элементов И, вторые входы которых связаны с выходом блока регулирования начальной фазы противофазной в сравнении с данной, выходы всех элементов И связаны с входами элемента ИЛИ, выход которого соединен с входом ключа, а выход ключа является выходом управления соответствующей полуфазой.

6/и Ura i/л

170/1иftaf

no/ttj- пони- nofiy- 9оза„ yajas фаЗа/;

поли- /paAf

шир л А

Uyi

8.

иуз

8.1

S.2

. % i Mp4 t/apl

Фиг 1

«

HnHjft

О

и.

в

УС

Ш к Хш

УяУ л Г А

tHtrit

W

,

43

чГП

2д

Ze

2с

ФигЛ

Ноличестйо So/ibyui тактов

Ю W X iiO 5S SO 10. SO

/iums/ii nacmt состоя- ния 9 УоАыиии maKfnoi

Энстренолйныи o.isopumfi

/ о/ч1честЗо SoMtuux Ш М 150 ISO 70 W 130, Ш 210. гО Z30 ZW тантоб -:- - ,,- -,- -;- -:-

т° 210 240 270 т Jji т

4лите/ йносгпб састоя- HUfi ff топтан.

yficfJip8 ant)Hf)ft uifmfumfi

Ши( больаил I-

да

т

ns -I

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровое устройство для управления инвертором с квазисинусоидальным напряжением | 1983 |

|

SU1089756A1 |

| Способ управления трехфазным мостовым инвертором,работающим на двигатель переменного тока,и устройство для его осуществления | 1984 |

|

SU1270850A1 |

| Способ управления трехфазным мостовым инвертором и устройство для управления трехфазным мостовым инвертором | 1981 |

|

SU1032592A1 |

| Устройство для управления автономнымиНВЕРТОРОМ | 1979 |

|

SU830631A1 |

| Устройство для управления трехфазным автономным инвертором | 1983 |

|

SU1144179A1 |

| Устройство для управления частотно-регулируемым трехфазным инвертором | 1984 |

|

SU1365305A1 |

| Устройство для управления автономным инвертором | 1990 |

|

SU1810973A1 |

| Устройство для управления трехфазным мостовым инвертором | 1986 |

|

SU1501233A1 |

| Ступенчатый регулятор мощности трехфазного напряжения | 1990 |

|

SU1756874A1 |

| Способ цифрового управления многофазным инвертором | 1989 |

|

SU1683154A1 |

Изобретение относите к электротехнике, а именно к системам управления автономными инверторами с ши- ротно-импульсной модуляцией, и может быть использовано в частотно- регулируемь х электроприводах с ши- роким диапазоном регулирования и управлением от микропро1 ессоров и . ЭВМ. Цель изобретения - расширение функциональных возможностей. Уст-во автоматически изменяет последовательности широтно-модулированных импульсов управления по сигналам о текущем состоянии полуфаз (режиме нагрузки). Импульсы управления в.ен- тилями инвертора модулируются после-- довательностью пшротно-импульсного регулятора в зависимости от режима нагрузки,обеспечивая неизменностьфор- мы напряжения и тока на выходе инвертора с амплитудой огибающей, определяемой кодом, подаваемым на широтно-импульс- ный регулятор. Соотношение между частотой выходного напряжения и его амплитудой определяется соотношением между кодами канала формирователя частоты и канала, формирователя амплитуды напряжения. 8 ил. с SS со tsd 4ib 4 «Ч Ю

| Цифровое устройство для управления инвертором напряжения | 1981 |

|

SU985923A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Цифровое устройство для управления инвертором с квазисинусоидальным напряжением | 1983 |

|

SU1089756A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1986-07-15—Публикация

1984-11-26—Подача