(54) ЦИФРОВОЕ УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ИНВЕРТОРОМ НАПРЯЖЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровое устройство для управления инвертором с квазисинусоидальным напряжением | 1983 |

|

SU1089756A1 |

| Устройство для управления транзисторным мостовым инвертором | 1982 |

|

SU1102009A1 |

| Устройство для управления резонансным инвертором | 1982 |

|

SU1102012A1 |

| Фазометр мгновенных значений | 1981 |

|

SU980015A1 |

| Устройство для управления трехфазным транзисторным инвертором с квазисинусоидальным напряжением | 1984 |

|

SU1244772A1 |

| Устройство для управления трехфазным мостовым инвертором | 1984 |

|

SU1297194A1 |

| Способ управления трехфазным мостовым инвертором,работающим на двигатель переменного тока,и устройство для его осуществления | 1984 |

|

SU1270850A1 |

| Устройство для поверки цифровых измерителей девиации фазы | 1990 |

|

SU1781651A1 |

| Устройство для коррекции шкалы времени | 1991 |

|

SU1781669A1 |

| Устройство для регулирования скорости электродвигателя | 1984 |

|

SU1267375A1 |

Изобретение ОТНОСИТСЯ к электротехнике, а именно к системам управ- . ления автономными инверторами напряжения, и «эжет быть использовано в частотно-регулируемых электроприводах переменного .тока с ,цифровым уп равленим.

Известно устройство управления автономными инверторами с широтно импульсной модуляцией, обеспечивдюinjee синхронизацию несущей и выходной частоты и периодическое,переключение кратности этих частот. Устройство содержит заданмций генератор, делитель частоты, генераторы опорного и модулирующего напряжений, формирователи, распределитель и переключатель кратности частот 1.

Недостатком этого устройства является использование аналоговых операций при формировании управляющих импульсов и команд на переключение кратности,что приводит к снижению . стабильности и усложнению схемл.

Известно также устройство управления трехфазным тиристорным преобразователем частоты, содержащее преобразователе аналог - код, задатчик частоты, формирователи, «распределитель, логическую схему и схему пёрекщочения кратности. Это устройство осуществляет формирование выходных сигналов на цифровом принципе. С2.

Недостатками известного устройст:;ва являются сложность схемы и формирование команд на переключение кратности частот в функции уровня входного сигнала, в результате чего поддерживать требуемую кратность, частот

10 в процессе регулирования частоты практически невозможно./

Нсшболее близкое к предлагаемому по технической сущности и достигаемому результату цифровое устройство

15 для утфавления инвертором напряжения содержит преобразователь код - частота, два реверсивных счетчика с д оифраторами, формирователь такто.вых интервалов, распределитель и

20 переключатель кратности С 31.

Одн:ако это устройство обладает сложностьюf ш званной нерациональным использованием счётчикоч. При необходимости формирования трехфазной

25 системы управляющих импульсов здесь .потребуется двенадцать реверсивных счетчиков и на выходе распределителя сложная схема формирователя. Кроме того, э такой системе образованы зак-,

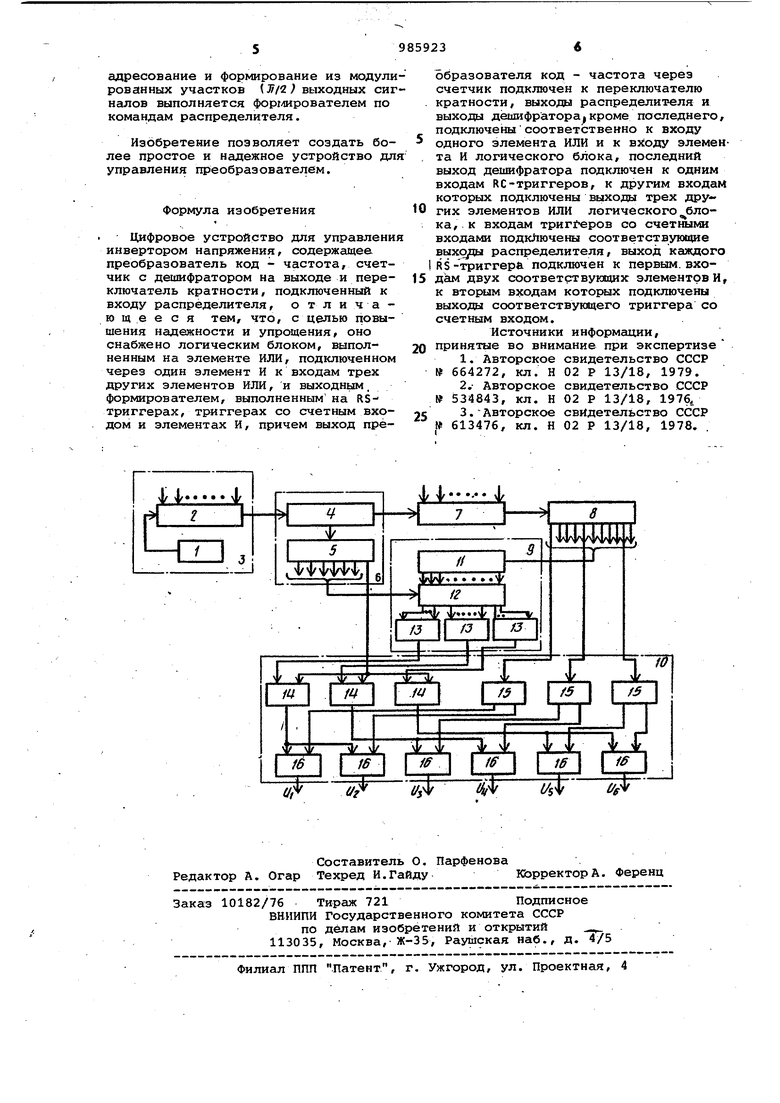

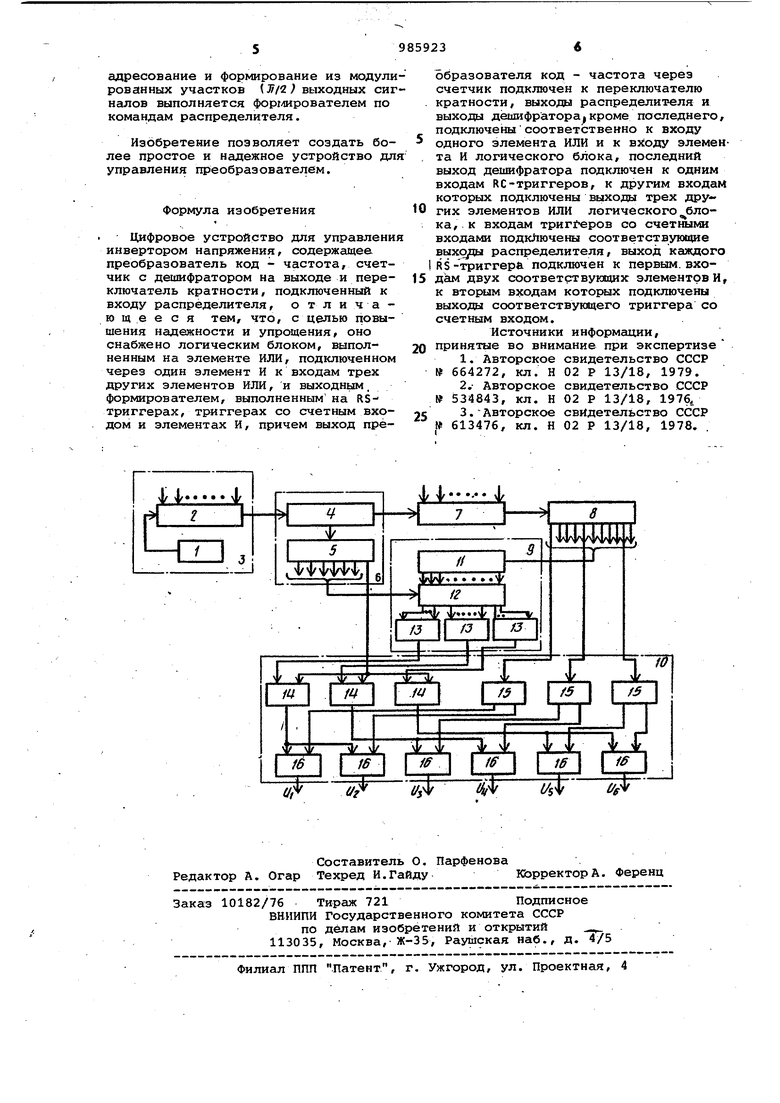

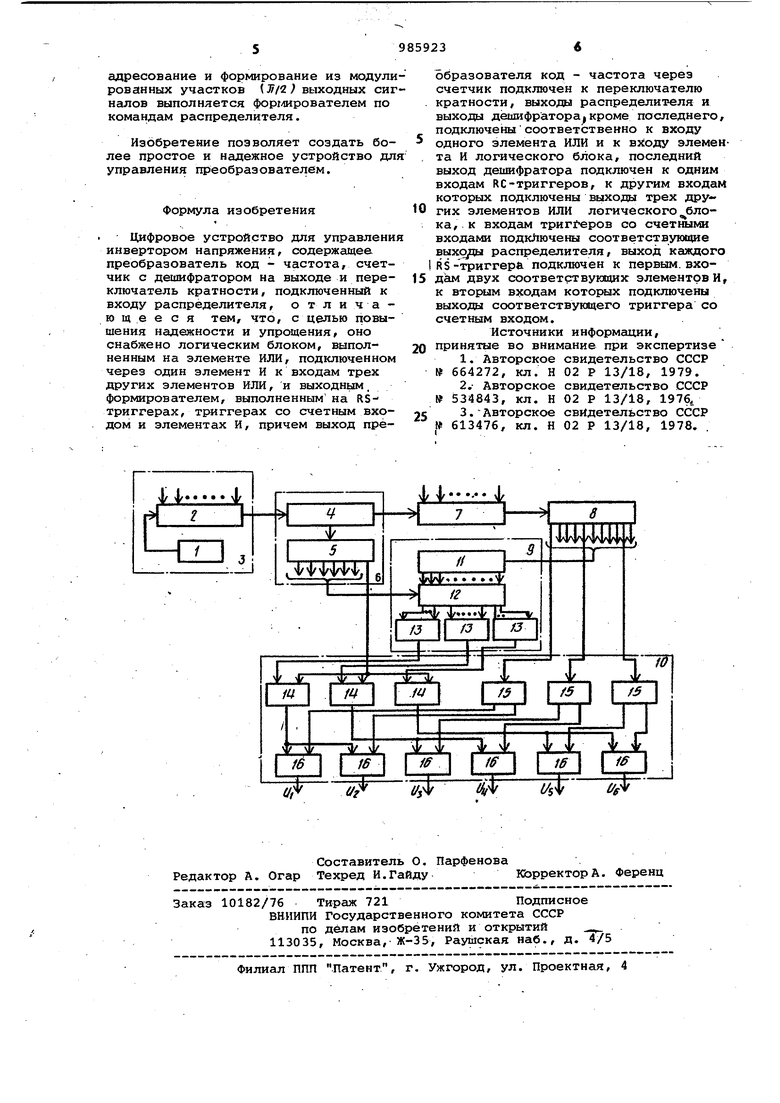

30 кнутые контура, например вход прёобразователя аналог - код - вход, преобразователя код - частота - выхо преобразователя код - частота - вход преобразователя аналог - код, а это может из-за запаздывания привести к нарушению тактовой синхронизации всей системы и к появлению сбоев. . Цель изобретения - повышение надежности и упрощение устройства управления инвертором напряжения. Указанная цель достигается тем, что цифровое устройство для управле ния инвертором напряжения снабжено логическим блоком, выполненным на элементе ИЛИ, подключенном через один элемент И к входам трех других элементов ИЛИ, и выходным формирователем, выполненным на RS-триггерах, триггерах со счетным входом и элементах И,причем выход преобразователя код - частота через счетчик подключей к переключателю кратности, выходы распределителя и выходы дешифратора, кроме последнего, подключены соответственно к входу одного элемента ИЛИ и к элемента И логического блока, последний выход дешиф ратора подключен к одним входам ftsтриггеров, к другим входам которых подключены выходы трех элементов ИЛИ логического блока, к входам триггеров со счетными входами подключены соответствующие выходы распределителя, выход каждого RS-триггера подключен к первым входам двух соответствующих элементов И, к вторым входам которых подключены выходы соответствующего триггера со счетным входом. Hal чертеже приведена схема устрой ства. Ус -ройство содержит генератор 1 тактовой частоты, подключенный к уп равляемому делителю 2 частоты,,составляющие преобразователь 3 код частота, счетчик 4, линейный дешифратор 5, формирователь б квазисинусоидального напряжения, переключатель 7 кратности, распределитель 8, логический блок 9, формировател 10, элементы ИЛИ 11, элементы И 12f элементы ИЛИ 13, триггеры 14, триггеры со счетным входом 15 и элементы И 16. Устройство работает следующим об разом. Импульсы с выхода генератора 1 тактовой частоты поступают на счетны вход счетчика 2 импульсов, на парал лельные входы которого при каждом его переполнении записывается инвер ный код требуемой частоты (,Таким образом, реализуется простая схема управляемого делителя частоты ц совокупности с генератором тактовой частоты выполняющего функции преобразователя 3 код - частота. Сигнал с выхода преобразователя код частота поступает на вход счетчика 4 который вместе с. линейным дешифратором 5 образует схему формирователя 6 квазисинусоидального напряжения. При каждом переполнении счетчика сигналы с его выхода поступают на вход цифрового переключателя 7, выполненного на счетчике образующем управляемый кодом {d,oty,,,.,df, ) делитель, причем изменение коэффициента деления згщается тем же кодом, что и задание частоты. Переключатель кратности формирует сигналы переключения позиций распределителя 8 с кратностью, пропорциональной величине входной частоты, задаваемой кодом. Все двенадцать выходов распределителя поступают в логический блок 9, куда подводятся и выходы дешифратора. Далее импульсы с .логического блока поступают на входы формирователя 10, на вцходах которого вырабатывается трехфазная система импульсов U-( - Ug, модулированных по синусоидальному закону и поступающих в выходные каскады для управления вентилями инвертора. Выходы распределителя через элементы ИЛИ 11 поступают на входы элементов И 12, к другим входам которых подсоединены выходы дешифратора. В результате отбор сигналов с выхода дешифратора 5 осуществляется импульсами распределителя. Схема устройства приведена для случая аппроксимации половины периода синусоидального выходного напряжения двенадцатью интервалами (ступенями. Для этого случая используются 1, 3, 7, 13, 20, 28 выходы линейного даишфратора при емкости счетчика 32. Причем нарастающая полуволна формируется отбором выходных сигналов дешифратора в прямом направлении, а спадающая часть полуволны - отбором в обратном направлении. Сигналы с выходов тр.ех групп элементов И логического блока, объединенные через элементы ИЛИ 13, поступают на входы RS-триггеров 14 формирователя 10, надругие входы этих триггеров подается сигнал с 31 выхода дешифратора. Одновременно с нулевого, четвертого и десятого выходов распределителя импульсы подаются на счетные входы триггеров 16 формирователя. Формирование управляющих модулированных по синусоидальному закону импульсов и адресование их по рабочим вентилям инвертора осу- . ществляется элементами И 16 формирователя . Таким образом, на одном счетчике с дешифратором формируется модуляция по синусоидальному закону управляющих напряжений всех вентилей инвертора, отбор во времени этих напряжений осуществляется логическим блоком по сигналам с распределителя, а

Авторы

Даты

1982-12-30—Публикация

1981-06-19—Подача