Изобретение относится к вычислительной технике, в частности к устройствам ввода-вывода, может быть использовано для ввода-вывода дискретной информации в ЦВМ и является усовершенствованием п.о авт.св. №.1136173.

Цель изобретения - увеличение быстродействия устройства.

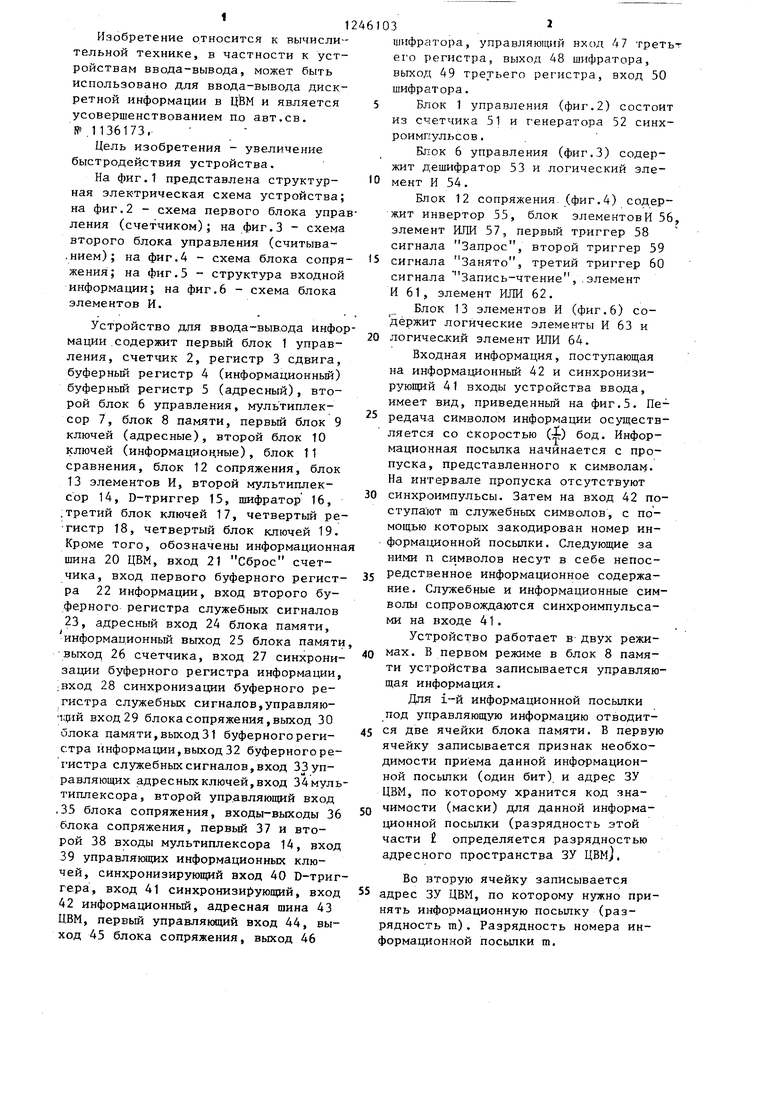

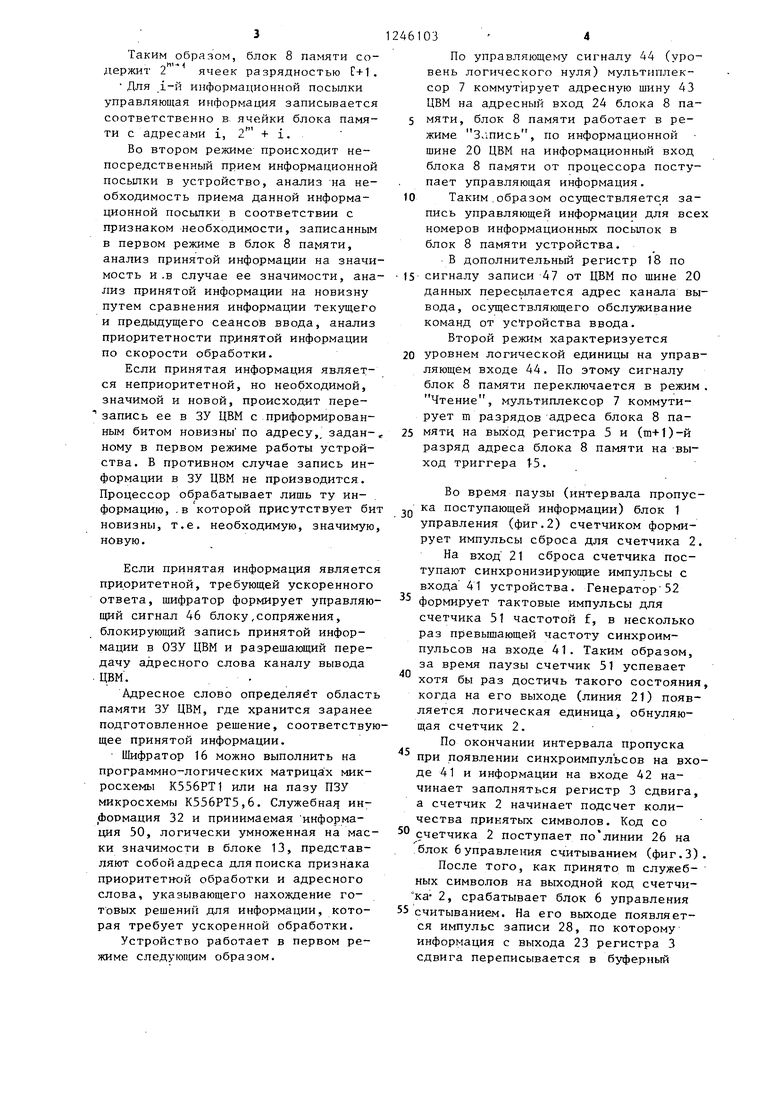

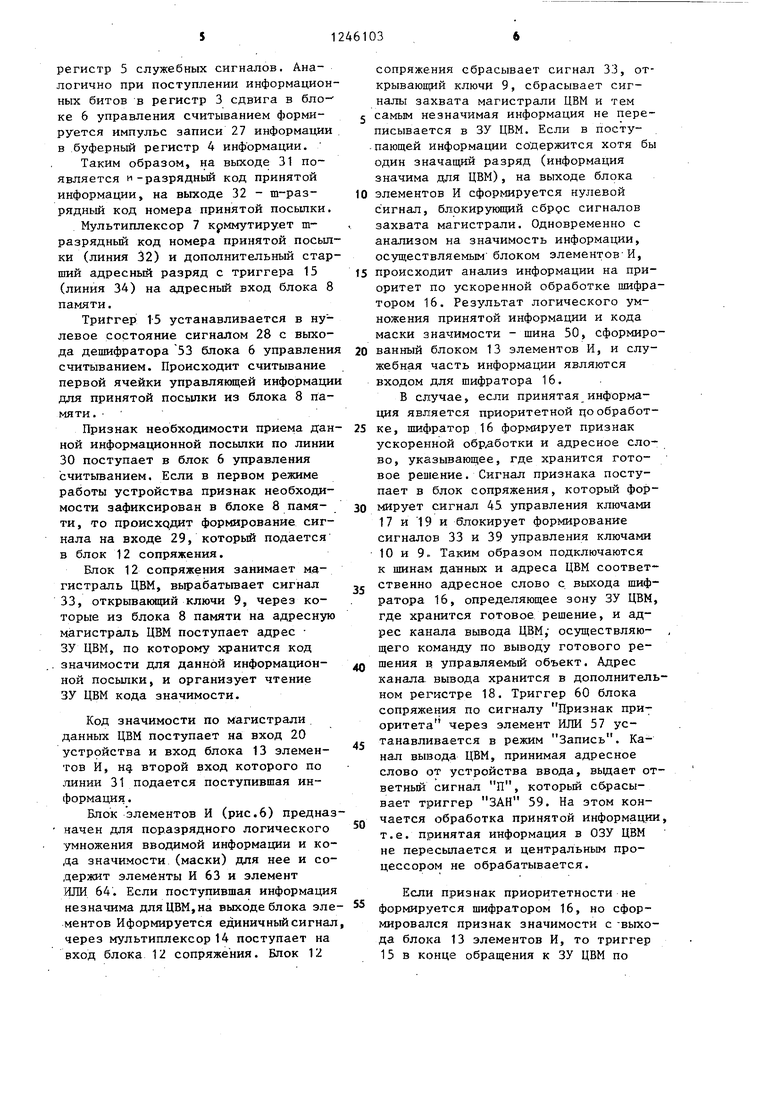

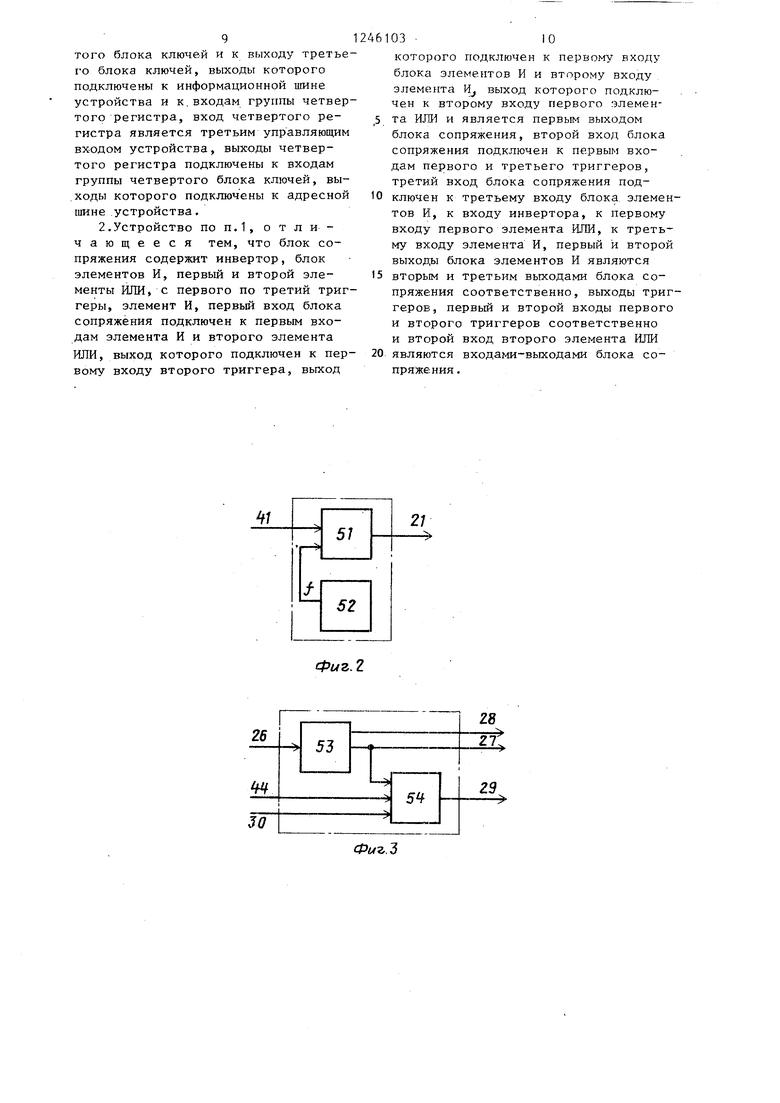

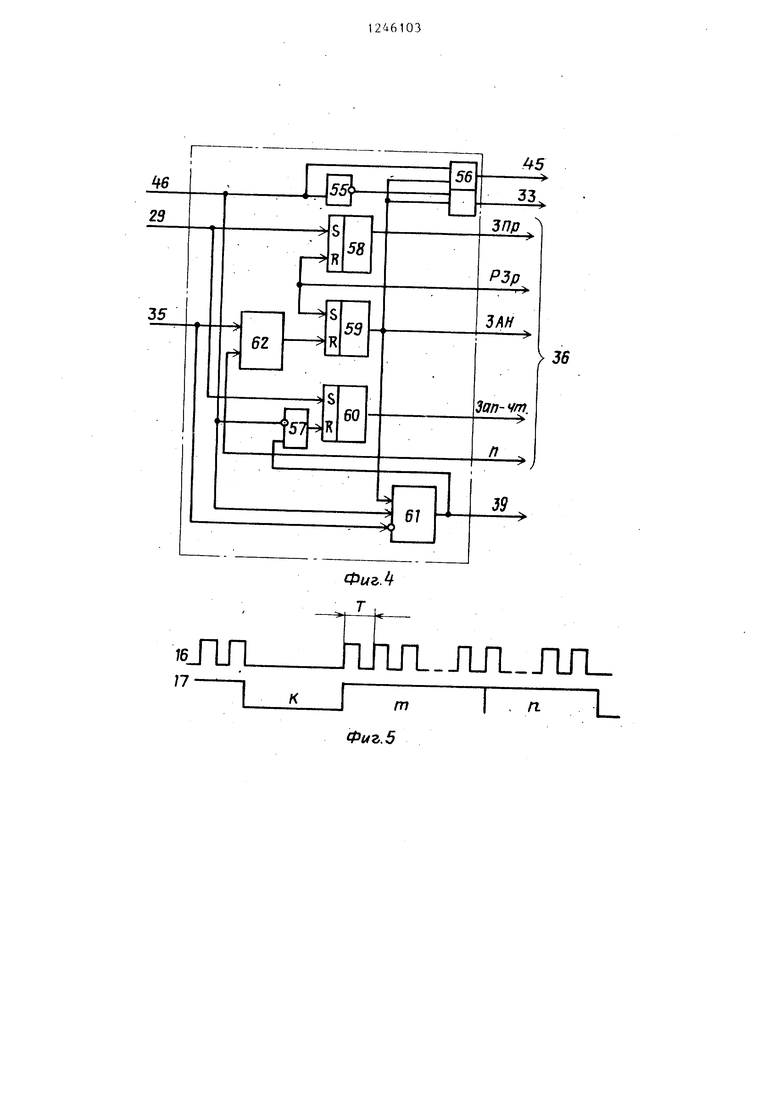

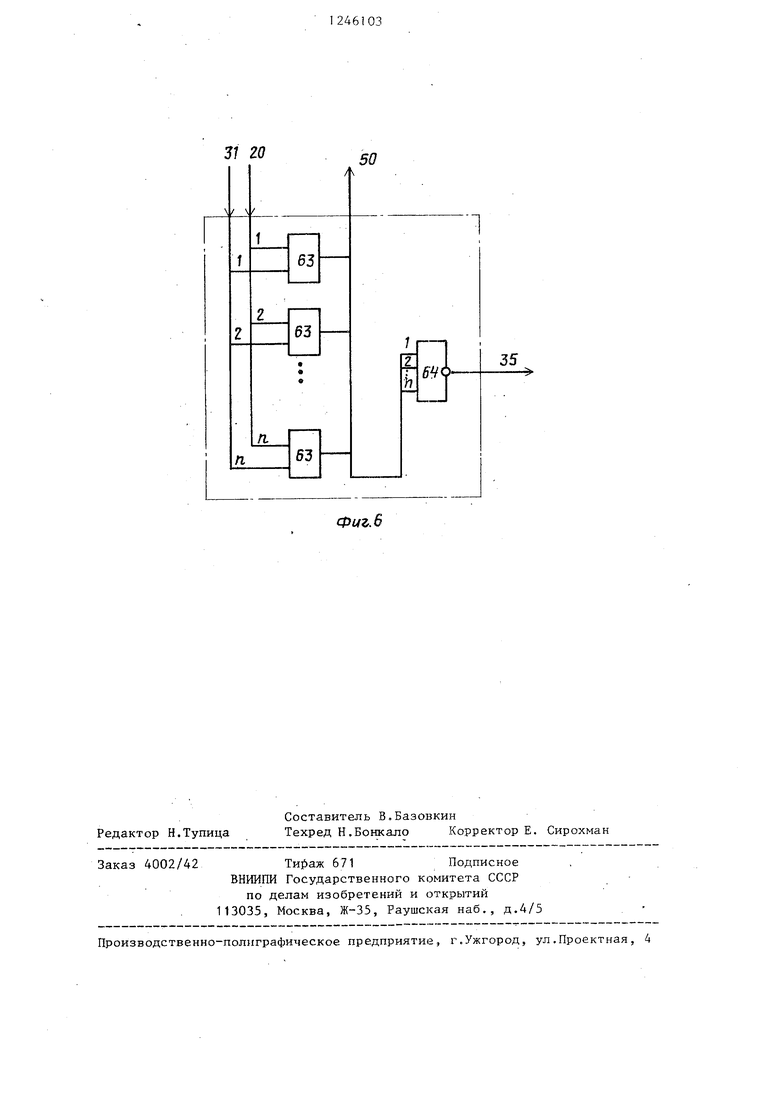

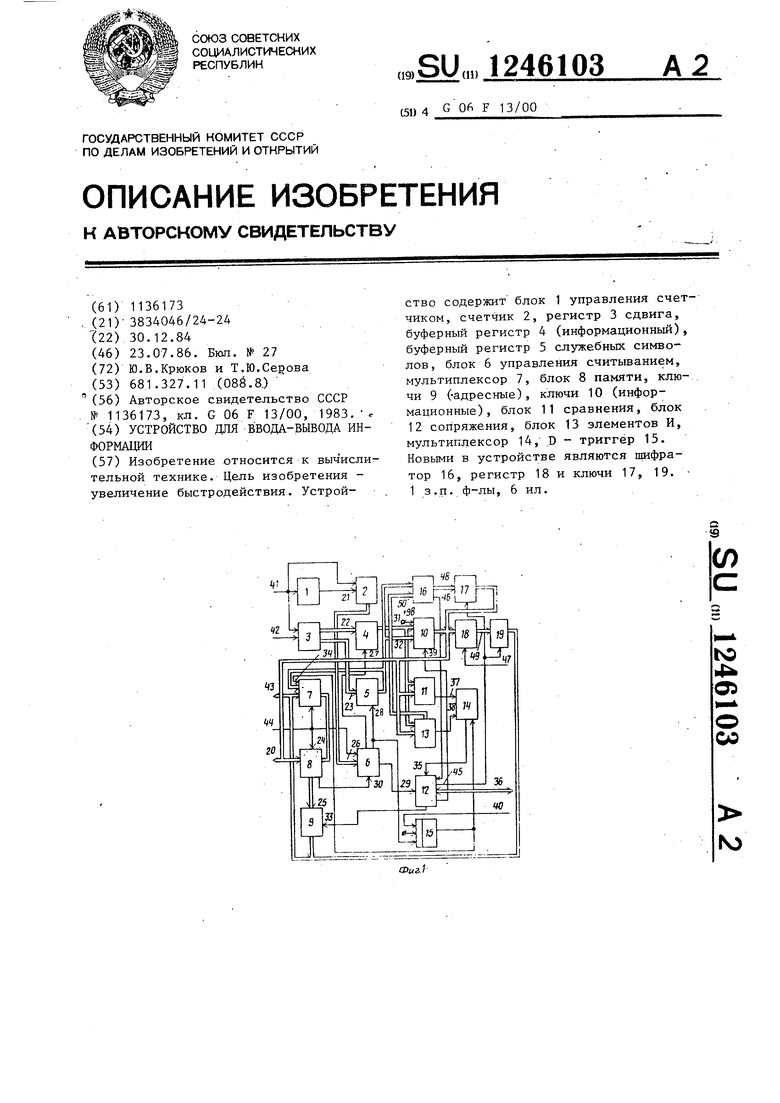

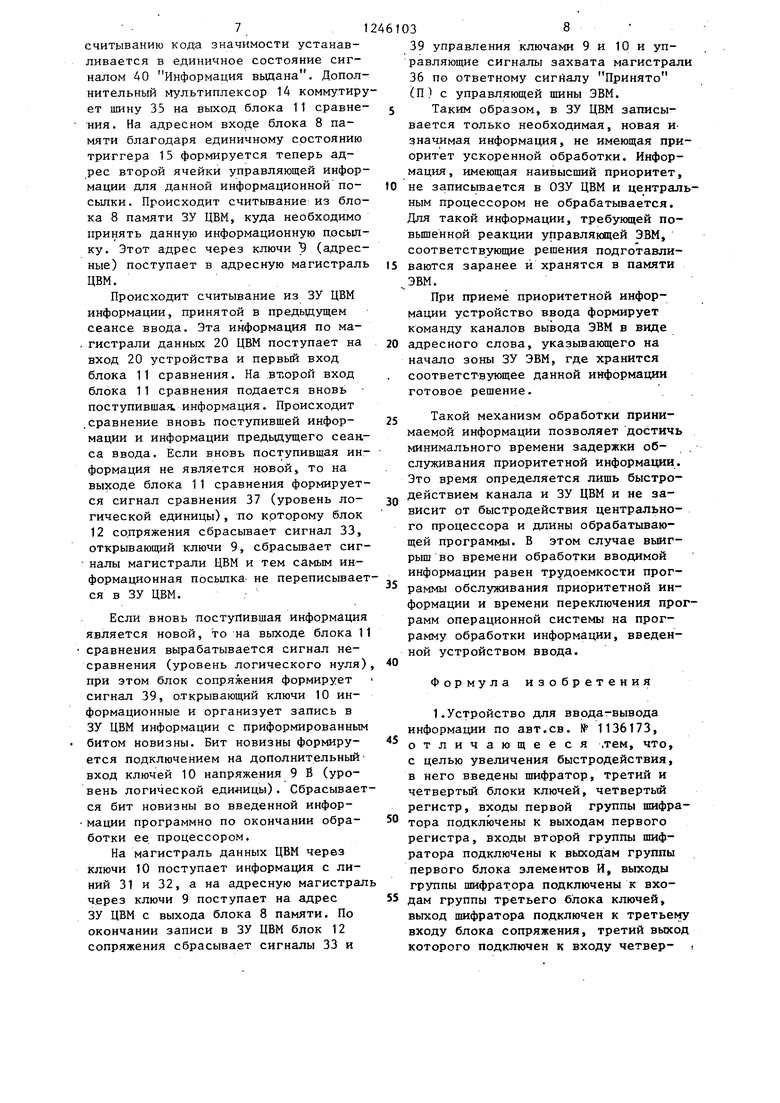

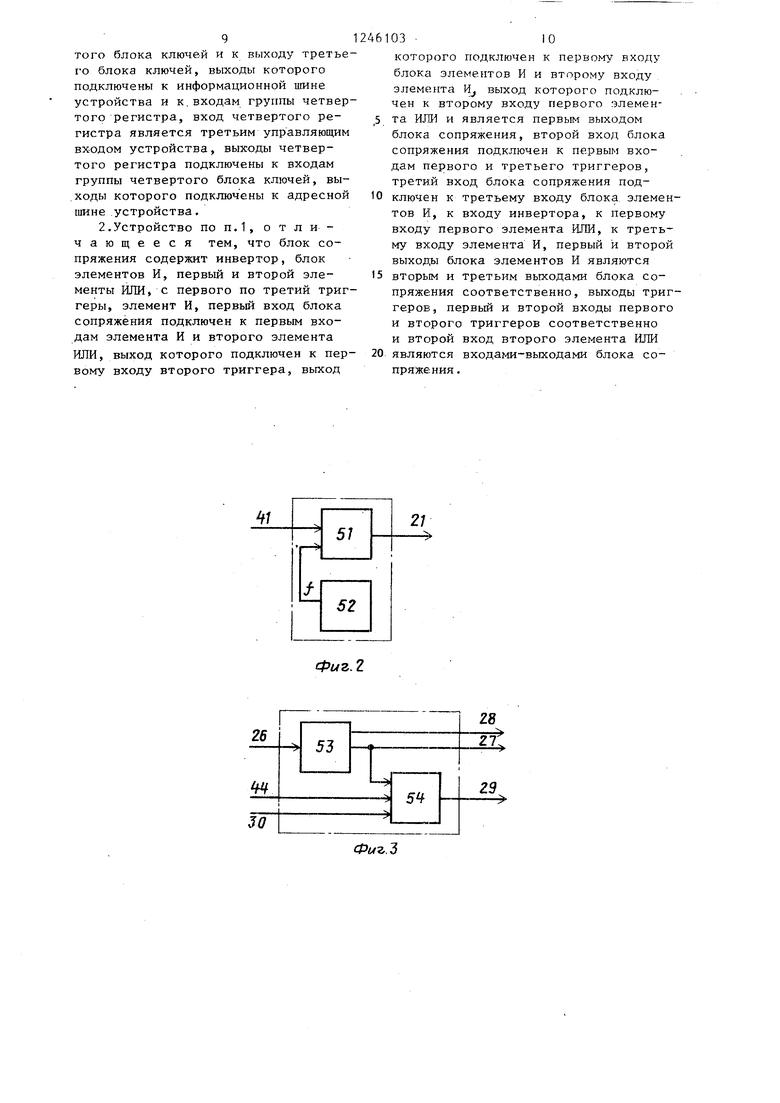

На фиг.1 представлена структурная электрическая схема устройства; на фиг.2 - схема первого блока управления (счетчиком); на фиг.3 - схема второго блока управления (считыва- .нием); на фиг.4 - схема блока сопряжения; на фиг.5 - структура входной информации; на фиг.6 - схема блока элементов И.

Устройство для ввода-выв.ода информации содержит первый блок 1 управления, счетчик 2, регистр 3 сдвига, буферный регистр 4 (информационньй) буферный регистр 5 (адресный), второй блок 6 управления, мультиплексор 7, блок 8 памяти, первый блок 9 ключей (адресные), второй блок 10 ключей (информационные), блок 11 сравнения, блок 12 сопряжения, блок 13 элементов И, второй мультиплексор 14, D-триггер 15, шифратор 16, :третий блок ключей 17, четвертый ре- гистр 18, четвертый блок ключей 19. Кроме того, обозначены информационна шина 20 ЦВМ, вход 21 Сброс счетчика, вход первого буферного регист- ра 22 информации, вход второго буферного регистра служебных сигналов 23, адресный вход 24 блока памяти, информационный выход 25 блока памяти выход 26 счетчика, вход 27 синхронизации буферного регистра информации, :вход 28 синхронизации буферного регистра служебных сигналов,управляю- 1;р1Й вход 29 блока сопряжения, выход 30 блока памяти,выход 31 буферного регистра информации,выход 32 буферного регистра служебных сигналов,вход 33 управляющих адресных ключей,вход 34муль типлексора, второй управляющий вход ,35 блока сопряжения, входы-выходы 36 блока сопряжения, первый 37 и второй 38 входы мультиплексора 14, вход 39 управляющих информационных ключей, синхронизирующий вход 40 D-триг гера, вход 41 синхронизи)ующий, вход 42 информационньй, адресная шина 43 ЦВМ, первый управляющий вход 44, выход 45 блока сопряжения, выход 46

0

5

0

шифратора, управляющий вход 47 третьт его р егистра, вь1ход 48 шифратора, выход 49 третьего регистра, вход 50 шифратора.

Блок 1 управления (фиг.2) состоит Из счетчика 51 и генератора 52 синхроимпульсов ,

Бл:ок 6 управления (фиг.З) содержит дешифратор 53 и логический элемент И 54.

Блок 12 сопряжения, (фиг.4) содержит инвертор 55, блок элементов И 56, элемент ИЛИ 57, первый триггер 58 сигнала Запрос, второй триггер 59 5 сигнала Занято, третий триггер 60 сигнала Запись-чтение,.элемент И 61, элемент ИЛИ 62.

Блок 13 элементов И (фиг.6) содержит логические элементы И 63 и 0 логичес-кий элемент ИЛИ 64.

Входная информация, поступающая на информационный 42 и синхронизирующий 41 входы устройства ввода, имеет вид, приведенный на фиг.5. Це- 5 редача символом информации осуществляется со скоростью (:) бод. Информационная посылка начинается с пропуска, представленного к символа. На интервале пропуска отсутствуют 0 синхроимпульсы. Затем на вход 42 поступают m служебных символов, с помощью которых закодирован номер информационной посылки. Следующие за ними п символов несут в себе непосредственное информационное содержание. Служебные и информационные символы сопровождаются синхроимпульсами на входе 41.

Устройство работает в двух режимах. В первом режиме в блок 8 памяти устройства записывается управляющая информация.

Для i-й информационной посылки под управляющую информацию отводит- 5 ся две ячейки блока памяти. В первую ячейку записывается признак необходимости приема данной информационной посылки (один бит) и адрес ЗУ ЦВМ, по которому хранится код зна- чимости (маски) для данной информационной посыпки (разрядность этой части определяется разрядностью адресного пространства ЗУ ЦВм,

Во вторую ячейку записывается 5 адрес ЗУ ЦВМ, по которому нужно принять информационную посылку (разрядность т). Разрядность номера информационной посылки т.

31246

Таким образом, блок 8 памяти содержит ячеек разрядностью Е+1 .

Для Д-й информационной посылки управляющая информация записывается соответственно в ячейки блока памя- 5 ти с адресами i, + i.

Во втором режиме происходит непосредственный прием информационной посылки в устройство, анализ на необходимость приема данной информа- 10 ционной посыпки в соответствии с признаком необходимости, записанным в первом режиме в блок 8 памяти, анализ принятой информации на значимость и .в случае ее значимости, ана- -15 ЛИЗ принятой информации на новизну путем сравнения информации текущего и предыдущего сеансов ввода, анализ приоритетности принятой информации по скорости обработки.20

Если принятая информация является неприоритетной, но необходимой, значимой и новой, происходит пере- запись ее в ЗУ ЦВМ с приформирован- ным битом новизны по адресу,, задан-, 25 ному в первом режиме работы устройства. В противном случае запись информации в ЗУ ЦВМ не производится. Процессор обрабатывает лишь ту информацию, .в которой присутствует бит 30 новизны, т.е. необходимую, значимую, новую.

Если принятая информация является приоритетной, требующей ускоренного

40

45

ответа, шифратор формирует управляю- щий сигнал 46 блоку,сопряжения, блокирующий запись принятой информации в ОЗУ ЦВМ и разрешающий передачу адресного слова каналу вывода ЦВМ.

Адресное слово определяет область памяти ЗУ ЦВМ, где хранится заранее подготовленное решение, соответствующее принятой информации.

Шифратор 16 можно выполнить на программно-логических матрицах микросхемы К556РТ1 или на пазу ПЗУ микросхемы К556РТ5,6. Служебная инормация 32 и принимаемая информаия 50, логически умноженная на мае- 50 ки значимости в блоке 13, представляют собойадреса для поиска признака приоритетной обработки и адресного слова, указывающего нахождение готовых решений для информации, кото- 55 рая требует ускоренной обработки.

Устройство работает в первом режиме следующим образом.

5

0 5 0

5 0

0

5

0 5

103 4

По управляющему сигналу 44 (уровень логического нуля) мультиплексор 7 коммутирует адресную шину 43 ЦВМ на адресный вход 24 блока 8 памяти, блок 8 памяти работает в режиме Злпись, по информационной шине 20 ЦВМ на информационный вход блока 8 памяти от процессора поступает управляющая информация.

Таким .образом осуществляется запись управляющей информации для всех номеров информационных посылок в блок 8 памяти устройства.

В дополнительный регистр 18 по сигналу записи 47 от ЦВМ по шине 20 данных пересьшается адрес канала вывода, осуществляющего обслуживание команд от устройства ввода.

Второй режим характеризуется уровнем логической единицы на управляющем входе 44. По этому сигналу блок 8 памяти переключается в режим . Чтение, мультиплексор 7 коммутирует m разрядов адреса блока 8 памяти на выход регистра 5 и (т+1)-й разряд адреса блока 8 памяти на выход триггера 15.

Во время паузы (интервала пропуска поступающей информации) блок 1 управления (фиг.2) счетчиком формирует импульсы сброса для счетчика 2.

На вход 21 сброса счетчика поступают синхронизирующие импульсы с входа 41 устройства. Генератор 52 формирует тактовые импульсы для счетчика 51 частотой f, в несколько раз превышающей частоту синхроимпульсов на входе 41. Таким образом, за время паузы счетчик 51 успевает хотя бы раз достичь такого состояния, когда на его выходе (линия 21) появляется логическая единица, обнуляющая счетчик 2.

По окончании интервала пропуска при появлении синхроимпульсов на входе 41 и информации на входе 42 начинает заполняться регистр 3 сдвига, а счетчик 2 начинает подсчет количества принятых символов. Код со счетчика 2 поступает по линии 26 на блок 6 управления считыванием (фиг.З).

После того, как принято m служебных символов на выходной код счетчика- 2, срабатывает блок 6 управления считыванием. На его выходе появляется импульс записи 28, по которому информация с выхода 23 регистра 3 сдвига переписывается в буферный

регистр 5 служебных сигналов. Аналогично при поступлении информационных битов в регистр 3 сдвига в блоке 6 управления считыванием формируется импульс записи 27 информации в буферный регистр 4 информации.

Таким образом, на выходе 31 появляется и-разрядньш код принятой информации, на выходе 32 - т-раз- рядный код номера принятой посьшки.

Мультиплексор 7 коммутирует га- разрядный код номера принятой посылки (линия 32) и дополнительный старший адресный разряд с триггера 15 (линия 34) на адресный вход блока 8 памяти.

Триггер 15 устанавливается в нулевое состояние сигналом 28 с выхода дешифратора 53 блока 6 управлени считыванием. Происходит считывание первой ячейки управляющей информаци для принятой посылки из блока 8 памяти.

Признак необходимости приема данной информационной посьшки по линии 30 поступает в блок 6 управления считыванием. Если в первом режиме работы устройства признак необходимости зафиксирован в блоке 8 памяти, то происхцдит формирование сигнала на входе 29, который подается в блок 12 сопряжения.

Блок 12 сопряжения занимает магистраль ЦВМ, вырабатьшает сигнал 33, открывающий ключи 9, через которые из блока 8 памяти на адресную магистраль ЦВМ поступает адрес - ЗУ ЦВМ, по которому хранится код значимости для данной информационной посылки, и организует чтение ЗУ ЦВМ кода значимости.

Код значимости по магистрали данных ЦВМ поступает на вход 20 устррйства и вход блока 13 элементов И, нд. второй вход которого по -гшнии 31 подается поступившая информация .

Блок элементов И (рис.6) предназначен для поразрядного логического умножения вводимой информации и кода значимости (маски) для нее и содержит элементы И 63 и элемент 1ИЛИ 64. Если поступившая информация незначима для ЦВМ,на выходе блока элементов Иформируется единичный си гнал через мультиплексор 14 поступает на вход блока 12 сопряжения. Блок 12

сопряжения сбрасывает сигнал 33, открывающий ключи 9, сбрасывает сигналы захвата магистрали ЦВМ и тем 5 самым незначимая информация не переписывается в ЗУ ЦВМ. Если в посту- пающей информации содержится хотя бы один значащий разряд (информация значима для ЦВМ), на выходе блока 10 элементов И сформируется нулевой сигнал, блокирующий сбррс сигналов захвата магистрали. Одновременно с анализом на значимость информации, осуществляемым блоком элементов И, 15 происходит анализ информации на приоритет по ускоренной обработке шифратором 16. Результат логического умножения принятой информации и кода маски значимости - шина 50, сформиро- 0 ванный блоком 13 элементов И, и служебная часть информации являются входом для шифратора 16.

В случае, если принятая информация является приоритетной цо обработS ке, шифратор 16 формирует признак ускоренной обработки и адресное слово, указывающее, где хранится готовое решение. Сигнал признака поступает в блок сопряжения, который фор0 мирует сигнал 45 управления ключами 17 и 19 и блокирует формирование сигналов 33 и 39 управления ключами 10 и 9.. Таким образом подключаются к шинам данных и адреса ЦВМ соответ

5 ственно адресное слово с выхода шифратора 16, определяющее зону ЗУ ЦВМ, где хранится готовое решение, и адрес канала вывода ЦВМ; осуществляющего команду по выводу готового реQ шения I управляемьй объект. Адрес

канала вывода хранится в дополнительном регистре 18. Триггер 60 блока сопряжения по сигналу Признак приоритета через элемент ИЛИ 57 усj танавливается в режим Запись. Канал вывода ЦВМ, принимая адресное слово от устройства ввода, выдает ответный сигнал П, который сбрасывает триггер ЗАН 59. На этом конQ чается обработка принятой информации, т.е. принятая информация в ОЗУ ЦВМ не пересыпается и центральным процессором не обрабатывается.

Если признак приоритетности не формируется шифратором 16, но сформировался признак значимости с -выхода блока 13 элементов И, то триггер 15 в конце обращения к ЗУ ЦВМ по

считыванию кода значимости устанавливается в единичное состояние сигналом 40 Р1нформация вьщана. Дополнительный мультиплексор 14 коммутирует шину 35 на выход блока 11 сравнения. На адресном входе блока 8 памяти благодаря единичному состоянию триггера 15 формируется теперь адрес второй ячейки управляющей информации для данной информационной посылки . Происходит считьгоание из блока 8 памяти ЗУ ЦВМ, куда необходимо принять данную информационную посылку. Этот адрес через ключи (адресные) поступает в адресную магистраль ЦВМ.

Происходит считывание из ЗУ ЦВМ информации, принятой в предыдущем сеансе ввода. Эта информация по магистрали данных 20 ЦВМ поступает на вход 20 устройства и первый вход блока 11 сравнения. На вт.орой вход блока 11 сравнения подается вновь поступившая информация. Происходит

сравнение вновь поступившей информации и информации предыдущего сеанса ввода. Если вновь поступившая ин- формация не является новой, то на выходе блока 11 сравнения формируется сигнал сравнения 37 (уровень логической единицы), по которому блок 12 сопряжения сбрасывает сигнал 33, открывающий ключи 9, сбрасьшает сигналы магистрали ЦВМ и тем самым информационная Посылка не переписывается в ЗУ ЦВМ.

Если вновь поступившая информация является новой, то на выходе блока 11 сравнения вырабатывается сигнал несравнения (уровень логического нуля), при этом блок сопряжения формирует сигнал 39, открывающий ключи 10 инормационные и организует запись в ЗУ ЦВМ информации с приформированным битом новизны. Бит новизны формируется подключением на дополнительный ход ключей 10 напряжения 9 В (уроень логической еди«ицы). Сбрасывается бит новизны во введенной инфор- мации программно по окончании обработки ее процессором.

На магистраль данных ЦВМ через ключи 10 поступает информация с линий 31 и 32, а на адресную магистраль через ключи 9 поступает на адрес ЗУ ЦВМ с выхода блока 8 памяти. По окончании записи в ЗУ ЦВМ блок 12 сопряжения сбрасывает сигналы 33 и

0

5

39 управления ключами 9 и 10 и управляющие сигналы захвата магистрали 36 по ответному сигналу Принято (П) с управляющей шины ЭВМ.

Таким образом, в ЗУ ЦВМ записывается только необходимая, новая и- значимая информация, не имеющая приоритет ускоренной обработки. Информация , имеющая наивысший приоритет, не записывается в ОЗУ ЦВМ и центральным процессором не обрабатывается. Для такой информации, требующей повышенной реакции управляицей ЭВМ, соответствуюш 1е решения подготавливаются заранее и хранятся в памяти ЭВМ.

При приеме приоритетной информации устройство ввода формирует команду каналов вывода ЭВМ в виде адресного слова, указывающего на начало зоны ЗУ ЭВМ, где хранится соответствующее данной информации готовое решение.

Такой механизм обработки принимаемой информации позволяет достичь минимального времени задержки обслуживания приоритетной информации. Это время определяется лишь быстродействием канала и ЗУ ЦВМ и не зависит от быстродействия центрального процессора и длины обрабатывающей программы. В этом случае выигрыш во времени обработки вводимой информации равен трудоемкости прог- раммы обслуживания приоритетной информации и времени переключения программ операционной системы на программу обработки информации, введенной устройством ввода.

0

5

0

Формула изобретения

1.Устройство для ввода-вывода информации по авт.св. № 1136173, отличающееся ,тем, что, с целью увеличения быстродействия, в него введены шифратор, третий и четвертьй блоки ключей, четвертый регистр, входы первой группы шифратора подключены к выходам первого регистра, входы второй группы шифратора подключены к выходам группы первого блока элементов И, выходы группы шифратора подключены к вхо- ам группы третьего блока ключей, выход шифратора подключен к третьему входу блока сопряжения, третий выход которого подключен к входу четвер-

того блока ключей и к выходу третьего блока ключей, выходы которого подключены к информационной шине устройства и к.входам группы четвер того регистра, вход четвертого регистра является третьим управляющим входом устройства, выходы четвертого регистра подключены к входам группы четвертого блока ключей, выходы которого подключены к адресной 11шне устройства.

2.Устройство по П.1, отличающееся тем, что блок сопряжения содержит инвертор, блок элементов И, первый и второй элементы ИЛИ, с первого по третий триг геры, элемент И, первый вход блока сопряжения подключен к первым входам элемента И и второго элемента ИЛИ, выход которого подключен к пер вому входу второго триггера, выход

246103 10

которого подключен к первому входу блока элементов И и второму входу элемента И, выход которого подключен к второму входу первого гэлемен- 5 та ИЛИ и является первым выходом блока сопряжения, второй вход блока сопряжения подключен к первым входам первого и третьего триггеров, третий вход блока сопряжения под- 10 ключен к третьему входу блока элементов И, к входу инвертора, к первому входу первого элемента ИЛИ, к треть- му входу элемента И, первый и второй выходы блока элементов И являются 5 вторьпч и третьим выходами блока сопряжения соответственно, выходы триггеров, первый и второй входы первого и второго триггеров соответственно и второй вход второго элемента ИЛИ

20 являются входами-выходами блока сопряжения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ввода-вывода информации | 1983 |

|

SU1136173A1 |

| Устройство для ввода информации в ЭВМ | 1982 |

|

SU1043620A1 |

| Устройство ввода информации в ЭВМ | 1981 |

|

SU974365A2 |

| Устройство для сопряжения телеграфных линий связи с ЦВМ | 1988 |

|

SU1603392A1 |

| Устройство внешних каналов | 1988 |

|

SU1695313A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1990 |

|

SU1702380A1 |

| Устройство для сопряжения цифровой вычислительной машины (ЦВМ) с абонентами | 1984 |

|

SU1234843A1 |

| Устройство для сопряжения ЦВМ с внешним устройством | 1989 |

|

SU1661779A1 |

| Устройство для сопряжения ЦВМ с группой абонентов | 1988 |

|

SU1559349A1 |

| Микропроцессор для вводавывода данных | 1976 |

|

SU618733A1 |

Изобретение относится к вычислительной технике. Цель изобретения - увеличение быстродействия. Устройство содержит блок 1 управления счетчиком, счетчик 2, регистр 3 сдвига, буферный регистр 4 (информационный), буферный регистр 5 служебных символов, блок 6 управления считыванием, мультиплексор 7, блок 8 памяти, ключи 9 (-адресные), ключи 10 (информационные), блок 11 сравнения, блок 12 сопряжения, блок 13 элементов И, мультиплексор 14, D - триггер 15. Новыми в устройстве являются пшфра- тор 16, регистр 18 и ключи 17, 19. 1 3.п. ф-лы, 6 ил. 41 I I « (/) Ю 4 О 00 14

4/

2/

Фиг.2

Фм.З

6 17

ijin

Фиг.

, Т ,.

гшл.

1

т

п.

Фиг.5

31 го

Фиг. 6

Редакт op Н.Тупица

Составитель В.Базовкин

Техред Н.Вонкало Корректор Е. Сирохман

4002/42

671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

| Устройство для ввода-вывода информации | 1983 |

|

SU1136173A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| с | |||

Авторы

Даты

1986-07-23—Публикация

1984-12-30—Подача