Изобретение относится к вычислительной технике, в частности к системам обмена информацией между периферийными устройствами и оперативным запоминающим устройством (ОЗУ) ЦВМ, и может быть использовано в системах обмена данными, имеющих один путь доступа к ОЗУ.

Цель изобретения - повышение быстродействия устройства,

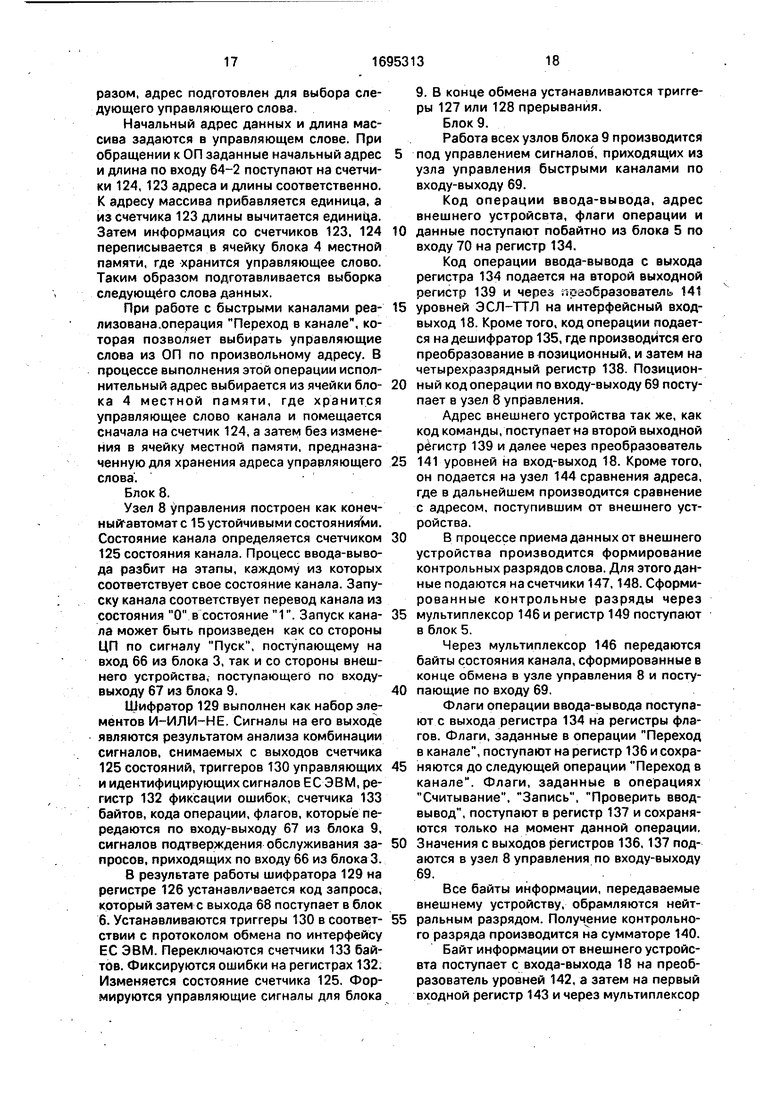

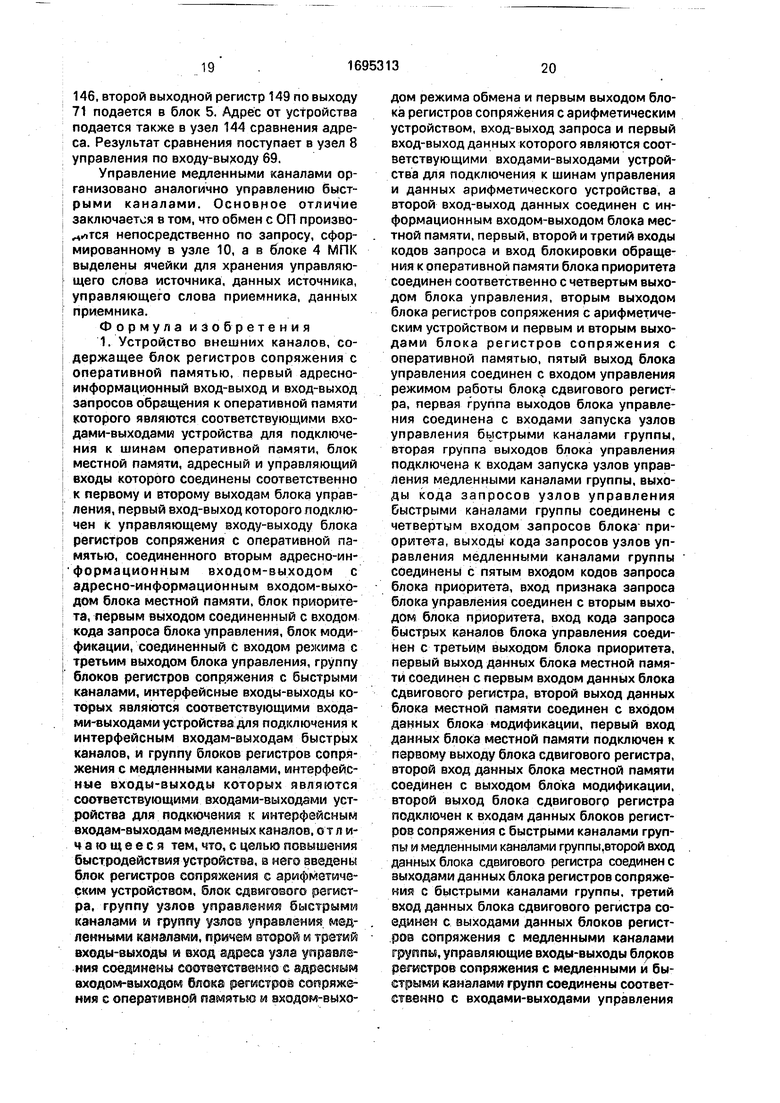

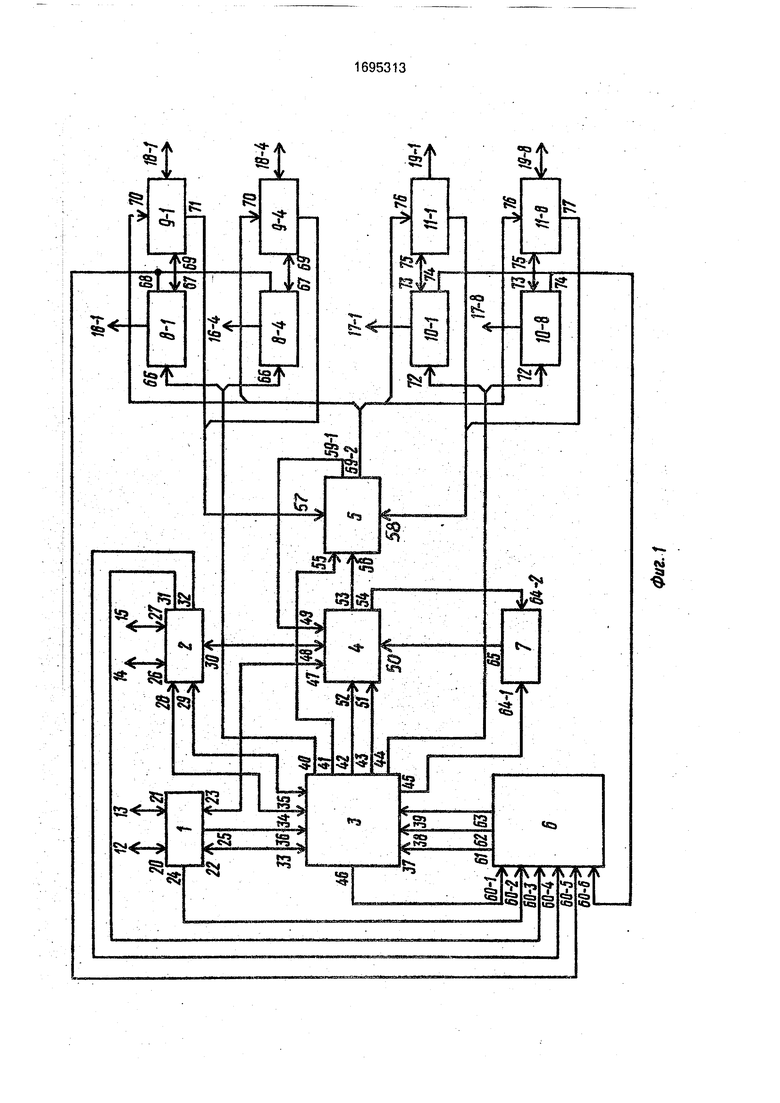

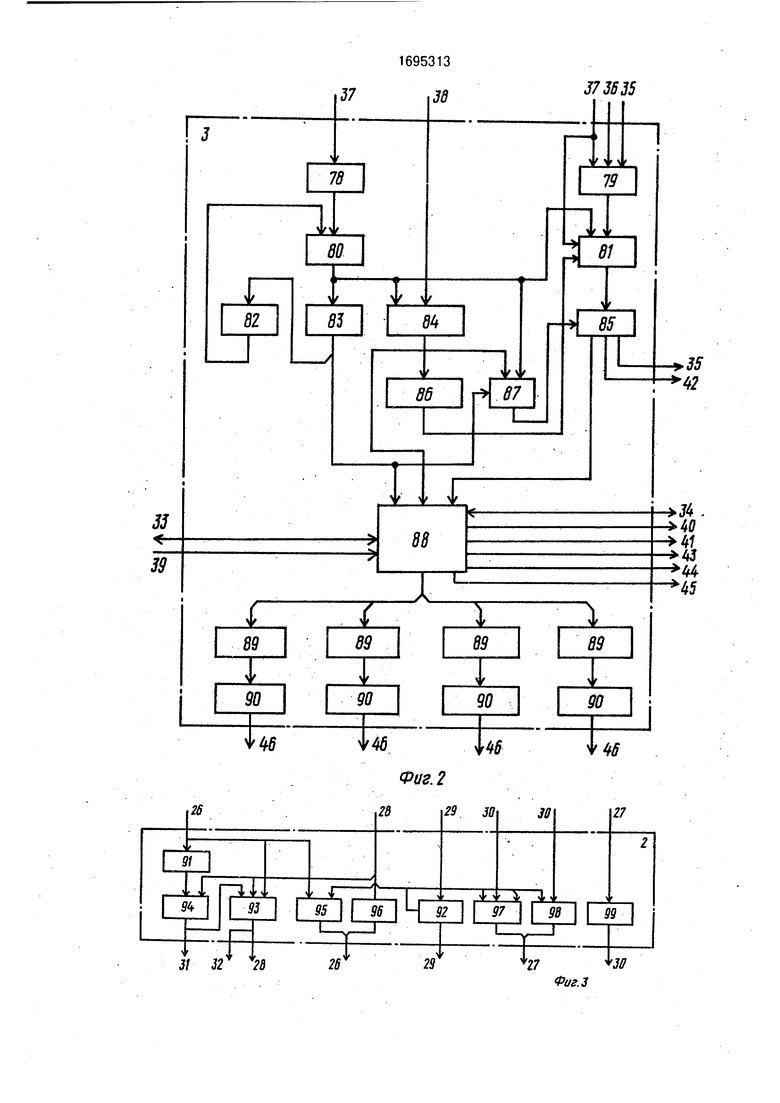

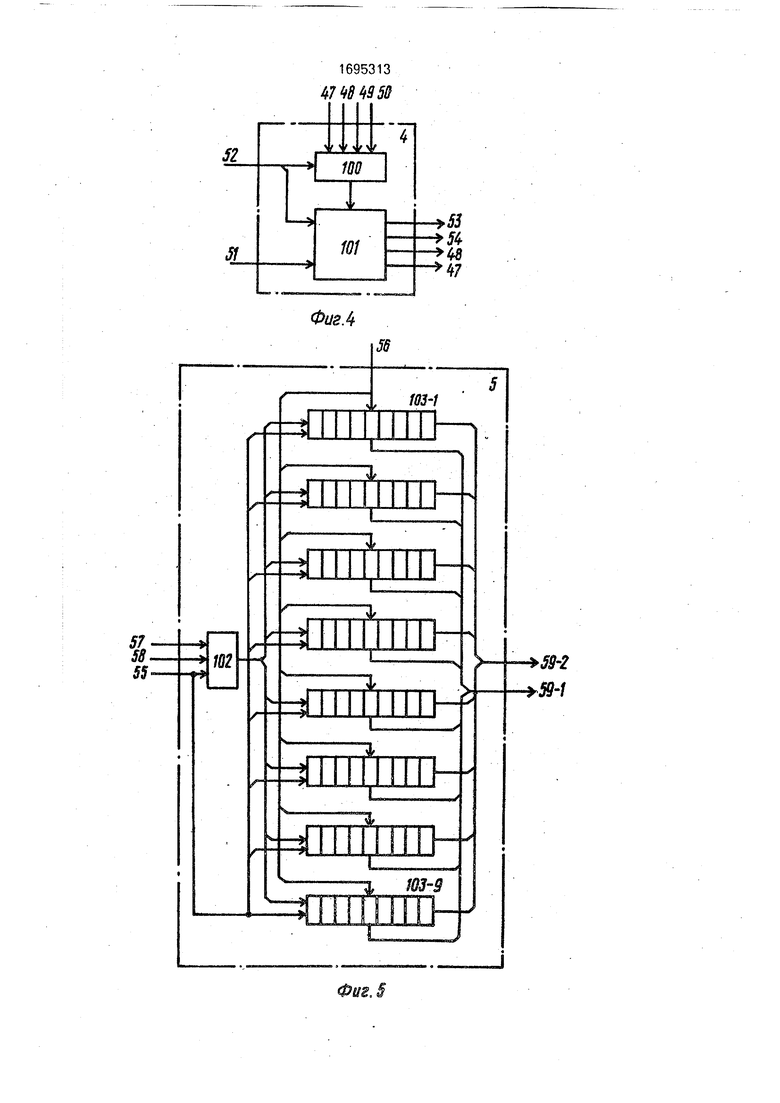

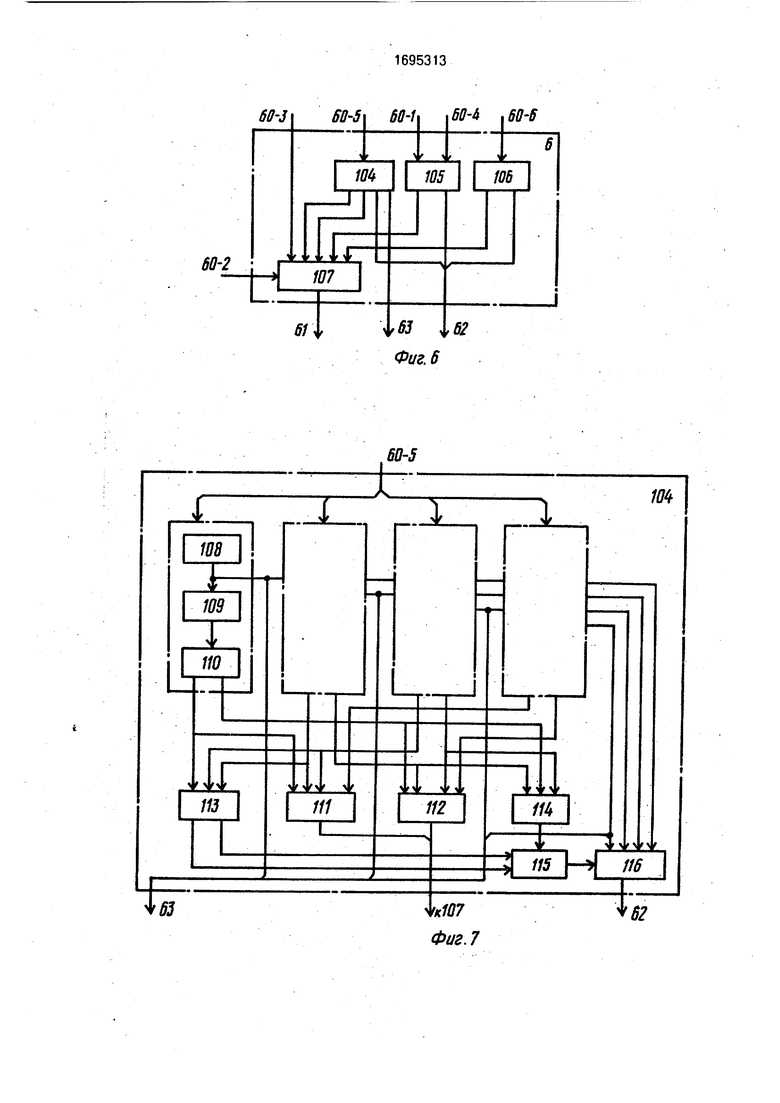

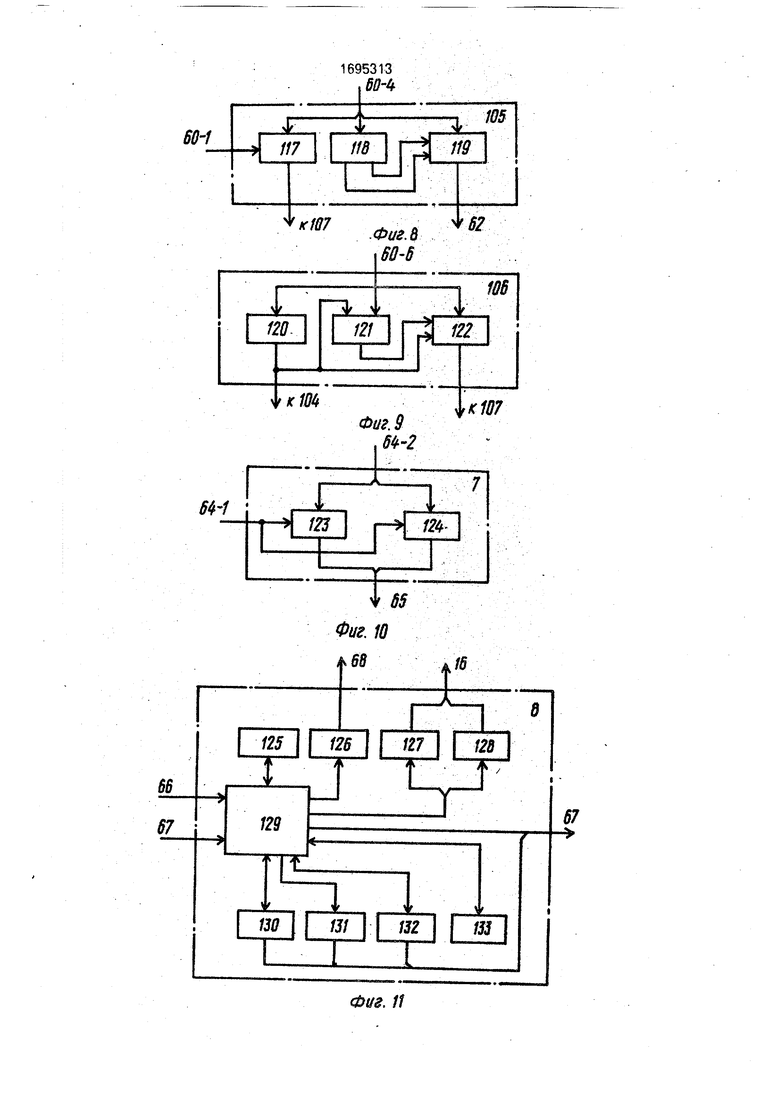

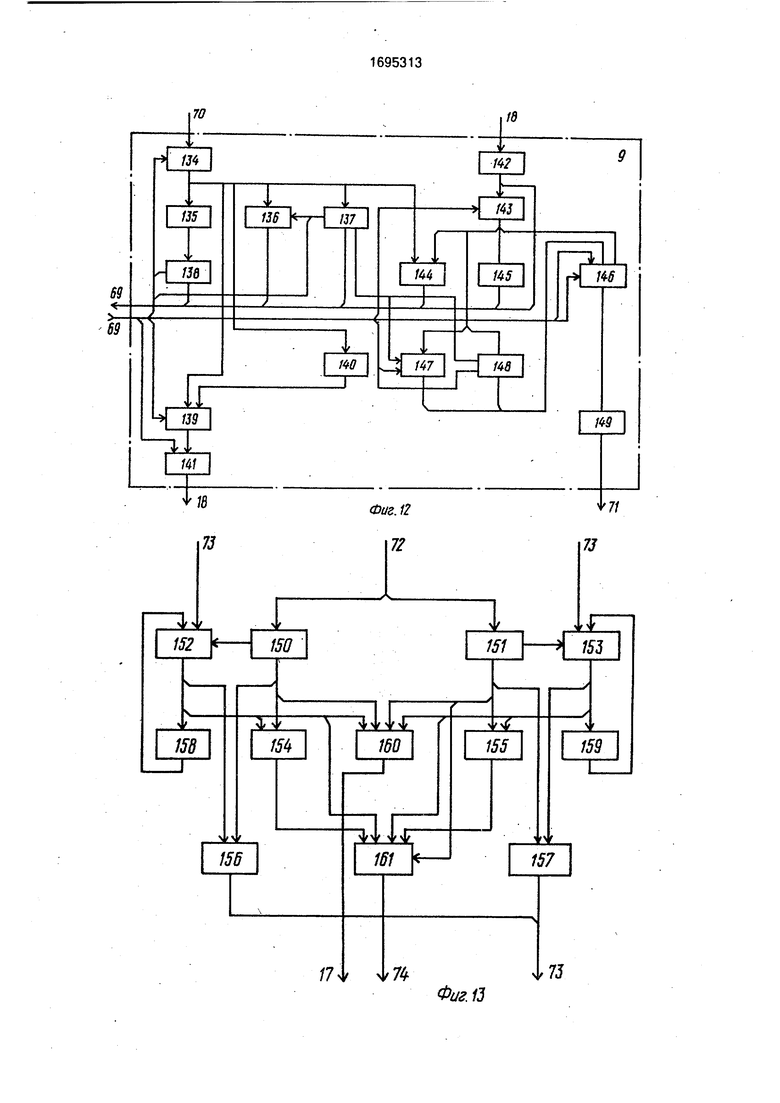

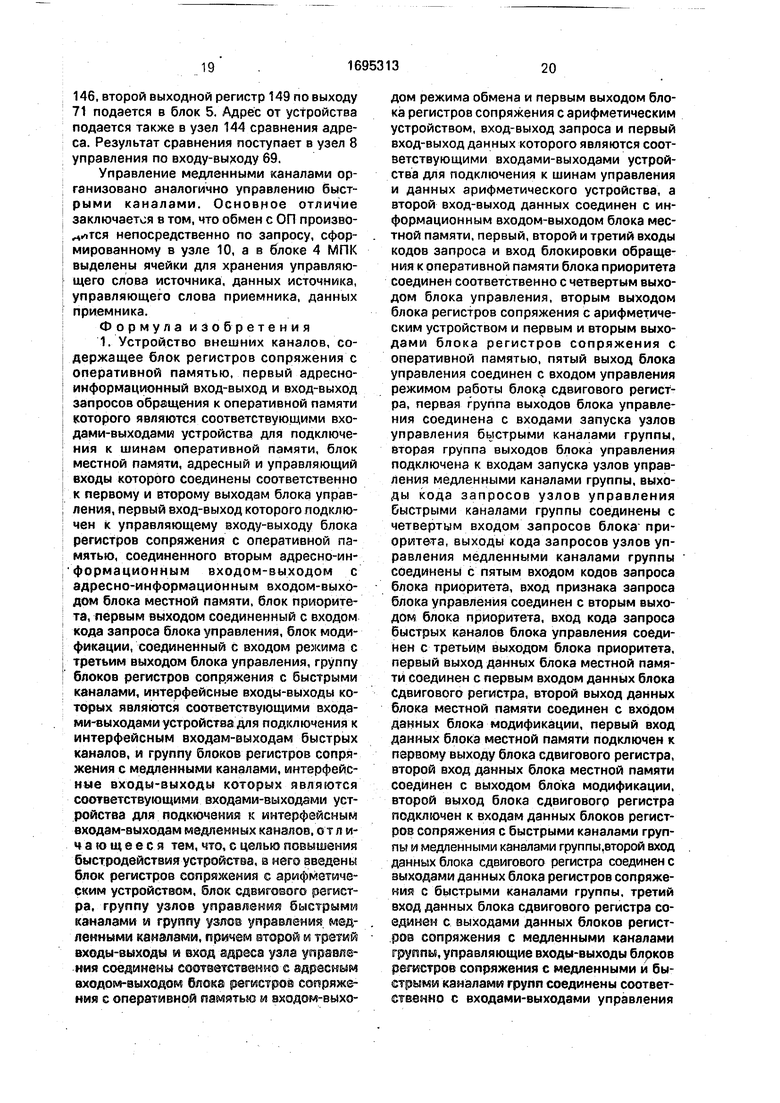

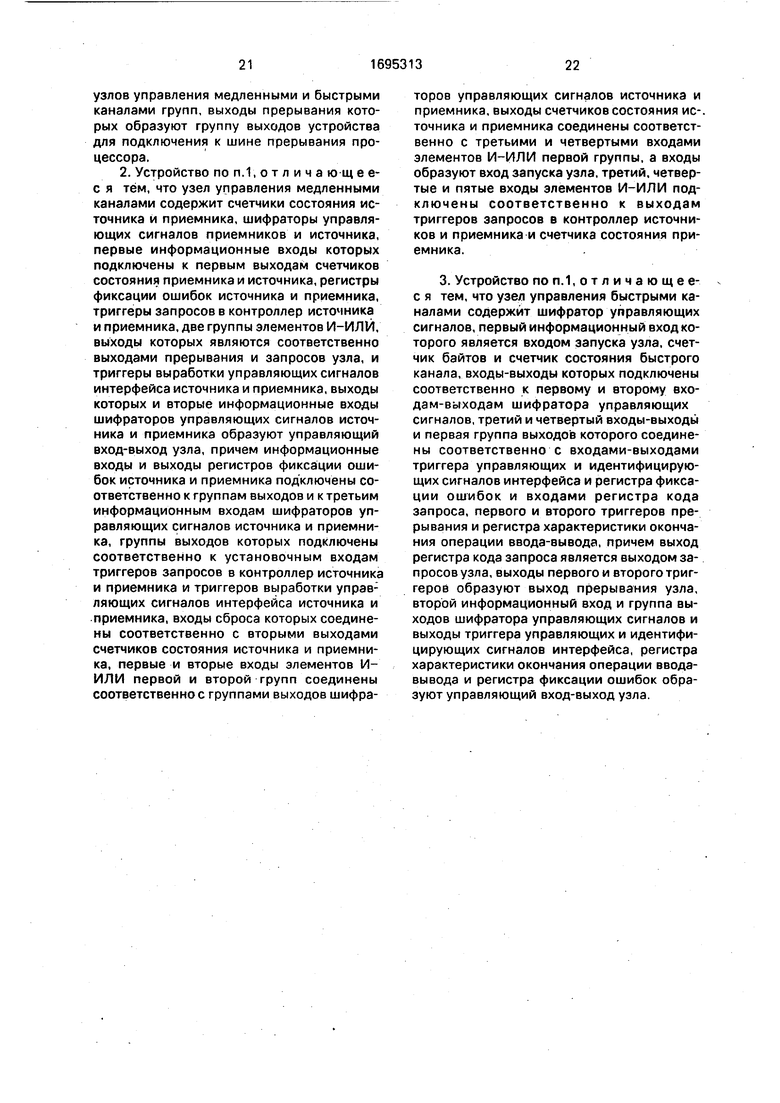

На фиг.1 изображена блок схема уст- ройсвта; на фиг.2 - блок управления; на фиг.З - блок регистров сопряжения с оперативной памятью (ОП); на фиг.4 - блок местной памяти; на фиг.5 - блок сдвигового регистра; на фиг.6 - блок приоритета; на фиг.7 - узел приоритета быстрых каналов; на фиг.8 - узел приоритета обращение к ОП;

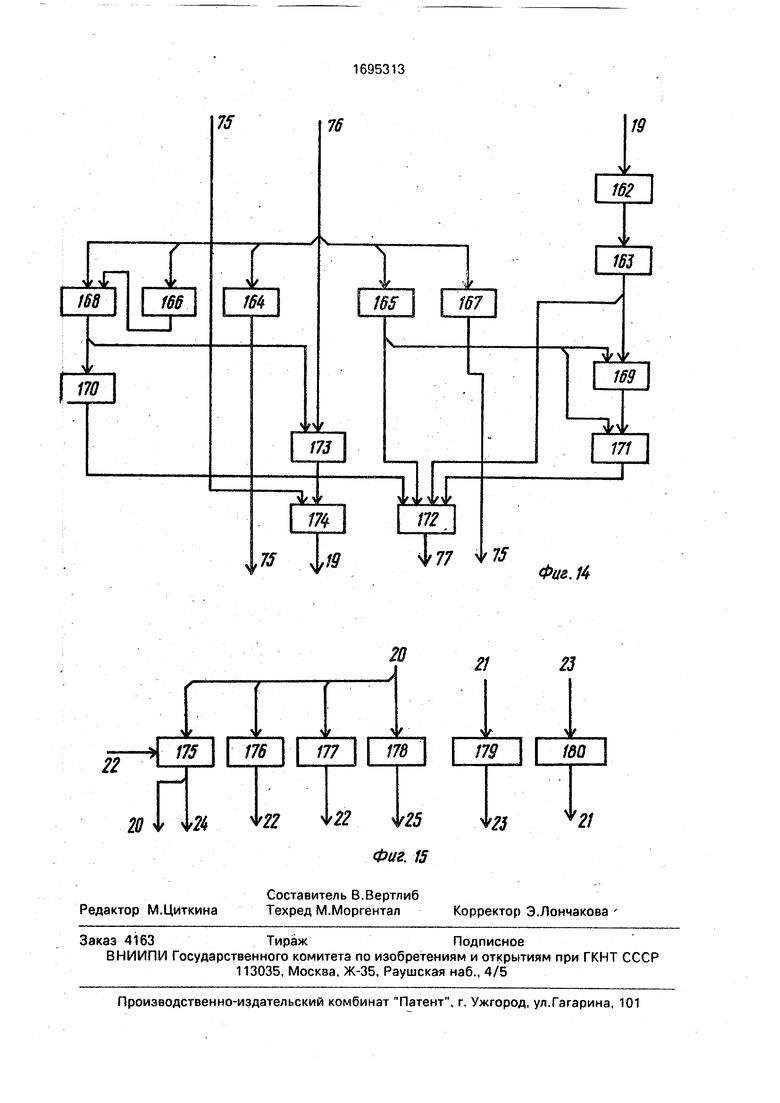

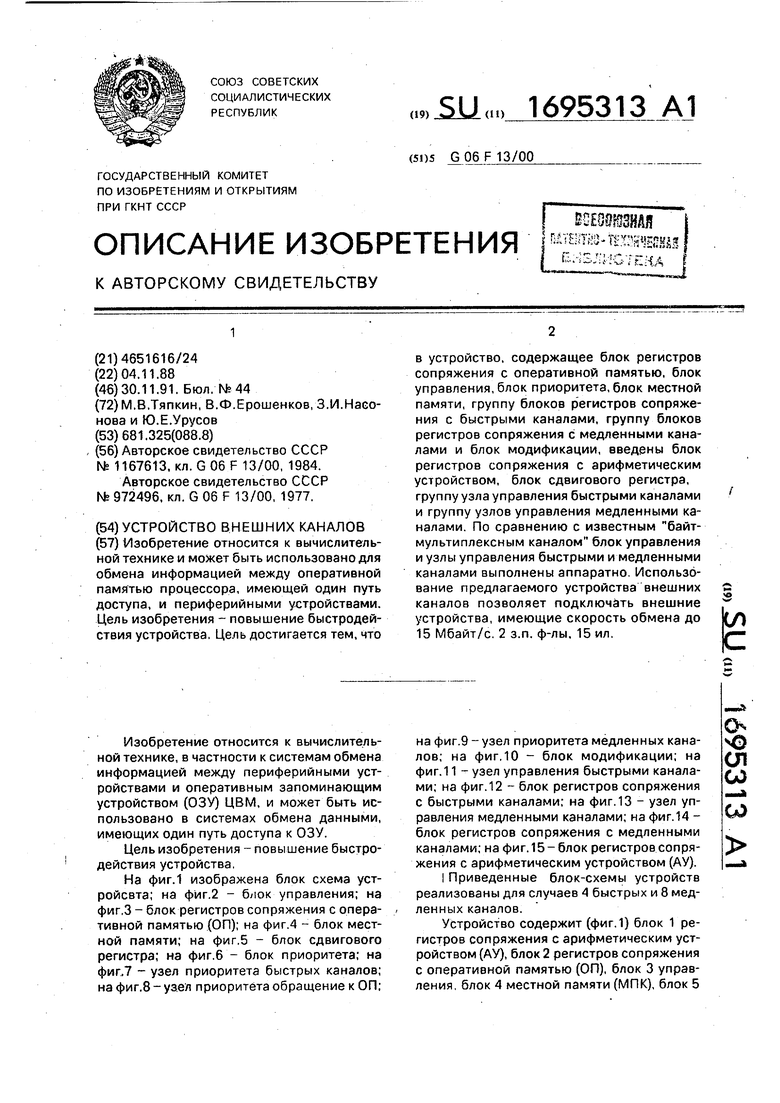

на фиг.9 - узел приоритета медленных каналов; на фиг.10 - блок модификации; на фиг.11 - узел управления быстрыми каналами; на фиг. 12 - блок регистров сопряжения с быстрыми каналами; на фиг. 13 - узел управления медленными каналами; на фиг. 14 - блок регистров сопряжения с медленными каналами; на фиг. 15-блок регистров сопряжения с арифметическим устройством (АУ).

I Приведенные блок-схемы устройств реализованы для случаев 4 быстрых и 8 медленных каналов.

Устройство содержит (фиг.1) блок 1 регистров сопряжения с арифметическим устройством (АУ), блок 2 регистров сопряжения с оперативной памятью (ОП), блок 3 управления, блок 4 местной памяти (МПК), блок 5

сь о

ел

W

-А

с

сдвигового регистра, блок 6 приоритета, блок 7 модификации, узлы 8 управления быстрыми каналами группы, блоки 9 регистров сопряжения с быстрыми каналами группы, узлы 10 управления медленными каналами, блоки 11 регистров сопряжения с медленными каналами.

Устройство имеет шину 12 запроса на обмен информацией с арифметическим устройством (АУ), шину 13 данных, шину 14 запросов обмена с оперативной памятью (ОП), адресно-информационную шину 15, выходы 16 сигналов прерывания узлов 8 управления быстрыми каналами, выходы 17 сигналов прерывания узлов 10 управления медленными каналами, интерфейсные входы-выходы 18 быстрых каналов, интерфейсные входы-выходы 19 медленных каналов. На фиг.1 показаны линии 20-77 связей между блоками.

Блок 3 управления (фиг,2) содержит первую группу элементов ИЛИ 78, мультиплексор 79 адреса, первый шифратор 80 управляющих сигналов, второй шифратор 81 управляющих сигналов, вторую группу элементов ИЛИ 82, регистр 83 тактов операций, регистр 84 кода операций, регистр 85 адреса, дешифратор 86 кода операций, третий шифратор 87 управляющих сигналов, четвертый шифратор 88 управляющих сигналов, счетчики 89 состояний быстрых каналов, шифратор 90 запросов быстрых каналов.

Блок 2 регистра сопряжения с ОП (фиг.З) содержит сдвиговый регистр 91, регистр 92 хранения адреса местной памяти, триггер 93 блокировки обращения к ОП, триггер 94 чтения оперативной памяти, триггер 95 запроса к ОП, триггер 96 признака записи-чтения ОП, регистр 97 адреса ОП, регистр 98 записи данных, регистр 99 считывания данных.

Блок 4 местной памяти (фиг.4) содержит мультиплексор 100 данных, запоминающее устройство 101.

Блок 5 сдвигового регистра (фиг.5) содержит мультиплексор 102, сдвиговые регистры 103.

Блок б приоритета (фиг.6) содержит узел 104 приоритета быстрых каналов, узел 105 приоритета обращения к ОП, узел 106 приоритета медленных каналов, селектор 107 признаков запросов.

Узел 104 приоритета быстрых каналов содержит(фиг.7) регистр 108 кода запросов, дешифратор 109, селектор 110 типа запроса, первую группу элементов ИЛИ 111, вторую группу элементов ИЛИ 112, первый селектор 113 номера канала, второй селектор 114 номера канала, шифратор 115, мультиплексор 116 кода запроса.

Узел 105 приоритета обращения к ОП (фиг.8) содержит группу элементов ИЛИ-И

117, селектор 118 номера канала, мультиплексор 119 кода запроса.

Узел 106 приоритета медленных каналов (фиг.9) содержит группу элементов ИЛИ 120, селектор 121 номера канала, мульти0 плексор 122 кода запроса.

Блок 7 модификации (фиг. 10) содержит счетчик 123 длины массива данных, счетчик 124 адреса обращения к ОП.

Узел 8 управления быстрыми каналами

5 (фиг.11) содержит счетчик 125 состояния быстрого канала, регистр 126 кода запроса, первый триггер 127 прерывания, второй триггер 128 прерывания, шифратор 129 управляющих сигналов, триггеры 130управля0 ющих и идентифицирующих сигналов интерфейса ЕС ЭВМ, регистр 131 характеристики окончания операции ввода-вывода, регистр 132 фиксации ошибок, счетчик 133 байтов.

5Блок 9 регистров сопряжения с быстрыми каналами-(фиг. 12) содержит первый входной регистр 134, дешифратор 135 команд, первый регистр 136 флагов, второй регистр-137 флагов, регистр 138 команд,

0 первый выходной регистр 139, восьмивхо- довой сумматор 140 по модулю два, преобразователь 141 уровней ЭСЛ-ТТЛ, преобразователь 142 уровней ТТЛ-ЭСЛ, второй входной регистр 143, узел 144 срав5 нения адреса, элемент ИЛИ 145, мультиплексор 146, счетчик 147 числа единиц младшей половины слова, счетчик 148 числа единиц старшей половины слова, второй выходной регистр 149.

0 Узел 10 управления медленными каналами содержит (фиг. 13) счетчик 150 состояния канала-источника, счетчик 151 состояния канала-приемника, шифратор 152 управляющих сигналов канала-источни5 ка, шифратор 153 управляющих сигналов канала-приемника, триггер 154 запросов в контроллер канала-источника, триггер 155 запросов в контроллер канала-приемника, триггер 156 выработки управляющих сигна0 лов интерфейса ИРПР канала-источника, триггер 157 выработки управляющих сигналов интерфейса ИРПР канала-приемника, регистр 158 фиксации ошибок канала-источника, регистр 159 фиксации ошибок канала5 приемника, группу элементов И-ИЛИ 160 для выдачи прерываний процессору, группу элементов И-ИЛИ 161 для выработки приоритета и команды-запроса в контроллер.

Блок 11 регистров сопряжения с медленными каналами содержит (фиг 14)преобразователя 162 уровней ТТЛ-ЭСЛ, регистр 163 приема, регистр 164 флагов канала-источника, регистр 165 флагов канала-приемника, счетчик 166 количества байтов в последнем слове канала-источника, счетчик 5 167 количества байтов в последнем слове канала-приемника, сумматор 168 по модулю два канала-источника, сумматор 169 по модулю два канала-приемника, счетчик 170 формирования контрольных разрядов слова 10 канала-источника, счетчик 171 формирования контрольных разрядов слова канала- приемника, мультиплексор 172 для выдачи байтов информации и состояния в контроллер, регистр 173 выдачи, преобразователь 15 174 уровней ЭСЛ-ТТЛ.

Блок 1 регистров сопряжения с АУ (фиг. 15) содержит триггер 175 запроса АУ, первый эмиттерный повторитель 176 управляющих сигналов, второй эмиттерный по- 20 вторитель 177 управляющих сигналов, вентильный шестиразрядный регистр 178 адреса местной памяти, 72-разрядный вентильный регистр 179 данных, 72-разрядный вентильный выходной регистр 180 данных. 25

Блок 1 предназначен для обмена данными между АУ и блоком 4 местной памяти. Обмен данными производится при запуске операции ввода-вывода и при завершении операции ввода-вывода.30

Блок 2 обеспечивает обмен данными между ОП и блоком 4 и выполняет следующие операции: формирует запрос обращения к ОП, сохраняет адрес ОП и данные из ячейки блока 4 на время пересылки данных 35 из блока 2 в ОП, сохраняет адрес ячейки блока 4 при операции считывания, формирует запрос обращения ОП к блоку 4, сигнал блокировки обращения к ОП при занятом блоке 3, обеспечивает временное согласо- 40 вание асинхронно работающего блока 3 и ОП.

Блок 3 обеспечивает обмен данными между АУ и блоком 4 МП К, ОП и блоком 4 МПК,быстрыми и медленными каналами 9,11 45 и блоком 4 МП К. Обмен организуется в ответ на запросы, поступающие со стороны АУ, ОП-каналов.

Блок 4 местной памяти каналов предназначен для хранения управляющей ин- 50 формации и данных, участвующих в обмене.

Блок 5 сдвигового регистра обеспечивает обмен информацией местной памяти и блоков 9, 11 сопряжения с каналами.

Блок 6 приоритета предназначен для 55 выделения наиболее приоритетного запроса при наличии запросов от нескольких источников. Источниками запросов являются в данном случае четыре узла 8 управления быстрыми каналами, восемь узлов 10 управления медленными каналами, четыре счетчика 89 состояния канала в блоке 3, триггер 175 запроса в блоке 1, триггер 94 в блоке 2.

Блок 7 модификации предназначен для вычисления исполнительного адреса оперативной памяти, по которому производится выборка или запись данных, участвующих в обмене, либо вычислении адреса, по которому выбирается управляющее слово из оперативной памяти. В блоке 7 модификации производится также подсчет количества слов, участвующих в обмене.

Узел 8 предназначен для выработки управляющих сигналов, необходимых для обмена данными между блоком 9 и внешними устройствами, блоком 9 и блоком 5 сдвигового регистра, для генерации запросов на обслуживание, для выработки сигналов прерывания к ЦП по окончанию операций ввода- вывода, для фиксации ошибок, возникающих в процессе, для формирования слова состояния канала.

Блок 9 выполняет следующие функции: сохраняет байт данных во время передачи- приема из канала к внешнему устройству и в обратном направлении, сохраняет код операции ввода-вывода, флаги операции ввода-вывода; производит сверку байта данных, сравнение адреса устройства.прихо- дящего от устройства, заказанного в операции ввода-вывода; формирует контрольные разряды слова, обеспечивает электрическое согласование уровней, свертку байта данных.

Работа всех узлов блока 9 производится под управлением сигналов, приходящих из узла 8 по входу-выходу 69.

Устройство работает следующим образом.

По команде с процессора производится запуск каналов. При запуске быстрых каналов из процессора записывается адрес управляющего слова, начальный адрес канальной программы в оперативной памяти. Адрес управляющего слова поступает с входа-выхода 13 устройства в блок 1 на вход-выход 21, управляющие сигналы (запрос на обмен с устройством, признак операции записи, адрес ячейки местной памяти, признак запуска канала) с входа-выхода 12 устройства на вход-выход 20. В блоке 1 устанавливается триггер 175 запроса АУ и по выходу 24 подается на вход 60-2 блока 6. Если запрос является приоритетным, то код запроса и признак запроса с выходов 62, 61 блока 6 соответственно поступают в блок 3, где организуется операция по записи адреса управляющего слова в блок 4 местной памяти каналов. Адрес ячейки блока 4 местной памяти из блока 1 с

выхода 25 подается в блок 3, другие управляющие сигналы поступают из блока 1 в блок 3 с выхода 22. На выходе 43 блока 3 формируются управляющие сигналы (запись) для блока 4. Адрес управляющего слова поступает из блока 1 с входа-выхода 23 в блок 4. Адрес блока 4 ячейки местной памяти, в которую производится запись, определяет, какой из четырех каналов будет запущен.

Процесс обмена информацией между каналом и периферийным устройством разбит на этапы, каждому из которых соответствует свое состояние канала. Состояние канала определяется состоянием счетчиков 89, 125 состояний быстрых каналов в блоке

3,в узле 8 и сигналами управления на входе-выходе 18 интерфейса, связывающего канал и периферийное устройство. Запуск канала приводит к изменению состояния счетчиков канала, в результате чего начинается первый этап ввода-вывода.

На первом этапе (для быстрых каналов) в результате изменения состояния счетчика 89 в блоке 3 организуется обращение к оперативной памяти по адресу, указанному при запуске канала, и из ОП в ячейку блока 4 местной памяти канала записывается управляющее слово канала (УСК).

Процесс выборки УСК проводится как выполнение двух запросов. Первый запрос формируется при переходе счетчика 89 в блоке 3 в состояние 1. При выполнении первого запроса в оперативную память (ОП) из устройства высших каналов передается адрес и признак чтения оперативной памяти, формируется и запоминается адрес ячейки блока 4 местной памяти, в которую записывается УСК, устанавливается сигнал блокировки обращения к ОП, счетчик 89 переводится в следующие состояния.

Код запроса с выхода 46 блока 3 поступает в блок 6, Если на момент поступления запроса нет сигнала блокировки обращения к ОП, приходящего из блока 2 с выхода 32, и запрос является приоритетом, то выбранный код запроса с выхода 62 и признак запроса с выхода 61 блока 6 поступают в блок 3. В блоке 3 организуется операция по выполнению запроса. В процессе операции формируется временная последовательность управляющих сигналов для блоков 2,

4,формируется адрес ячейки блока 4 местной памяти. Под действием управляющих сигналов адрес управляющего слова поступает из блока 4 по входу-выходу 48 в блок 2 на вход-выход 30 и затем на вход-выход 27. В блоке 2 на входе-выходе 26 устанавливается запрос к ОП, на выходе 32 - сигнал блокировки обращения к ОП. 8 блок 2 записывается адрес блока 4 ячейки местной памяти каналов, в которую должно быть считано УСК. Кроме того, в блоке 3 производится переключение счетчика 89. На этом операция завершается, блок 3 готов к обслуживанию следующего запроса.

После того как запрос обращения к ОП принят к исполнению, на вход-выход 14 устройства приходит сигнал, гасящий данный

0 запрос и устанавливающий в режим сдвига сдвиговый регистр 91 в блоке 2. Через четырнадцать тактов после прихода этого сигнала на выходе 31 блока 2 устанавливается запрос, который проходит через блок 6 при5 оритета и поступает в блок 3. В блоке 3 организуется следующая операция, завершающая выбор УСК и запуск канала. В процессе этой операции под действием последовательности управляющих сигна0 лов, выработанных в блоке 3, производится запись УСК в ячейку блока 4 местной памяти канала, снимается сигнал блокировки обращения к ОП в блоке 2, счетчик 89 в блоке 3 переводится в следующее состояние, что

5 приводит к появлению сигнала запуска узла 8управления, котрорый поступаете выхода 40 блока 3 на вход 66 узла 8.

В узле 8 управления имеется свой счетчик 125 состояния канала, который под дей0 ствием сигнала запуска переходит в следующее состояние. Переход счетчика 125 состояния в следующее состояние приводит к формированию запроса на выходе 68 узла 8, который затем поступает в блок 6

5 на вход 60-5 и далее в блок 3.

Первым запросом после запуска канала со стороны ЦП является запрос на передачу УСК в канал. В УСК содержатся адрес периферийного устройства, с которым будет

0 производиться обмен,, код команды ввода- вывода (стандартной для данного интерфейса и периферийного устройства), флаги, определяющие режим работы канала, начальный адрес массива данных в ОП, длина

5 массива.

В ходе выполнения данного запроса от канала УСК из блока 4 с выхода 53 поступает в блок 5 по входу бб.Затем с выхода 59-2 три первые байта УСК последовательно переда0 ются в блок 9 на вход 70. Адрес периферийного устройства, код команды ввода-вывода и флаги, переданные в этих байтах, фиксируются на соответствующих регистрах 138, 136 или 137 в блоке 9. Дешифрованный код

5 команды из блока 9 подается с входа-выхода 69 на вход-выход 67 в узел 8 управления. В узел 8 поступают управляющие сигналы с интерфейса канала.

Под действием этих сигналов и с учетом состояния счетчика 125 в узяе 8 управления

начинают формироваться управляющие сигналы, обеспечивающие проведегние начальной выборки устройства. В процессе начальной выборки периферийному устройству передается адрес устройства, команды ввода-вывода. В ответ на устройства получают служебную информацию, на основе анализа которой определяется возможность обмена данными.

Если дальнейший обмен невозможен или не требуется, то процесс ввода-вывода прекращается - канал переходит в определенное состояние и формирует сигнал прерывания ЦГТ. Сигнал прерывания передается с выхода 16 узла 8 управления.

Если процесс требует дальнейшего продолжения, то в зависимости от направления обмена прозводятся следующие действия. При передаче от канала к периферийному устройству организуется запрос к ОП по начальному адресу данных. Код запроса, сформированный в узле 8 управления, с выхода 68 поступает в блок 6 и далее с выхода 63 на вход 39 блока 3. Данный код запроса не участвует в розыгрыше приоритета, он лишь транслируется через блок 6. Поступив в блок 3, этот код запроса вызывает переключение счетчика 89 в блоке 3 в состояние б. Переход счетчика в состояние 6 приводит к появлению кода запроса на выход 46 блока 3, который попадает в блок бис учетом приоритета поступает в блок 3. В блоке 3 организуется операция по выполнению данного запроса. В процессе выполнения данного запроса из ячейки блока 4 местной памяти каналов, хранящей УСК, считывается начальный адрес массива данных. Этот адрес поступает в блок 2 на вход-выход 30 из блок 4, а также в блок 7 на вход 64-2. В блок 7 поступает информация о длине массива, также хранящаяся в УСК. В блоке 3 помимо управляющих сигналов, обеспечивающих работу блоков 2, 4, 7, формируется адрес ячейки блока 4 местной памяти каналов,который записывается в блок 2, Организуется обращение к ОП аналогично тому, как оно организовано при считывании УСК, В блоке 7 производится модификация адреса и длины массива - к адресу прибавляется единица, из длины вычитается единица, Модифицированные адрес и длина массива записываются в ячейку блока 4 местной памя-чч каналов, где хранится УСК, На этом операция заканчивается.

После того как данные приходят из ОП, организуется запрос от блока 2, в ходе выполнения которого слово данных автоматически передается в ячейку блока 4 местной памяти канала данного канала и затем побайтно через блок 5, блок 9 в перфорированное устройство по итерфейсной шине 18. При обслуживании данного запроса производится переключение счетчика 89 в блок 3,

что приводит к формированию запроса на вызов следующего слова из ОП. Процесс повторяется до тех пор, пока не будет передан весь массив данных, указанный в УС. Процесс побайтной выдачи производится

по запросам, поступающим из узла 8 управления.

При необходимости, если установлен соответствующий флаг, по окончании работы с одним УСК может быть выбран кз ОП

без участия ЦП следующий УСК и т.д.

По завершении обмена канал и периферийное устройство обмениваются служебной информацией (стандартной для

интерфейса ЕС ЭВМ), которая записывается в соответствующую ячейку блока местной памяти каналов, после чего формируется сигнал прерывания к ЦП.

При передаче от периферийного устройства к каналу производится побайтный прием данных в ячейку блока 4 местной памяти канала. Байт данных в сопровождении управляющих сигналов поступает на вход-выход 18 блока 9, управляющие сигналы

транслируются в узел 8 управления В узле 8 под действием этих сигналов вырабатываются управляющие сигналы, разрешающие прием данных на регистры 143, 149 блока 9, и формируется код запроса на прием байта

данных в блок 4 местной памяти каналов. После того как код запроса попадает в блок 3, организуется операция по его выполнению. В ходе выполнения этой операции из ячейки блока 4 местной памяти каналов,

предназначенной для хранения и накопления данных, байт данных, полученный от периферийного устройства, с выхода 71 блока 9 подается на вход 57 блока 5. Затем все слово сдвигается на один байт, и содержимое блока 5 вновь записывается в блок 4 местной памяти каналов, в ячейку данных. В узле 8 производится подсчет числа байтов, принятых от периферийного устройства. После того как будет принято 8 байтов (полное слово), которое вызывает не только запись последнего байта, но и переключение счетчика 89 в блоке 3, что, в свою очередь, вызывает формирование запроса в блоке 3 о записи слова из блока 4 местной

памяти каналов в ОП.

Запись полного слова производится в блок 4 местной памяти каналов в буферную ячейку, что позволяет продолжить обмен с периферийным устройством и не дожидаться, пока слово будет считано в ОП.

Процесс приема данных также заканчивается обменом служебной информацией и форированием сигналов прерывания к ЦП.

При запуске медленных каналов в ячейку блока 4 местной памяти каналов соответствующего канала записывается управляющее слово канала, в котором содержатся флаги, определяющие режим работы канала, начальный адрес массива и длина массива данных. Поскольку медленные каналы ориентированы на интерфейс ИРПР и разделены на приемник и источник, передавать команду ввода-вывода не требуется. Так же, как в быстрых каналах, после запуска канала присходит изменение состояния канала - изменяется состояние счетчиков 150, 151 состояния канала в узле 10 и устанавливаются соответствующие управляющие сигналы на выходе 19 интерфейса. При передаче от канала к периферийному устройству в узле 10 формируется код запроса к ОП, по которому считывается слово данных в блок 4. Код запроса к ОП выдается с выхода 74 узла 10 и поступает в блок 6 на вход 60-6. Дальнейший путь прохождения запроса и операций по его выполнению аналогичен выполнению запроса, поступающего от быстрых каналов с выхода 46 блока 3. В итоге выполнения данного запроса слово данных считывается из блока 4 в блок 5, байт данных из блока 5 с выхода 59-2 поступает на вход 76 блока 11 и затем на вход-выход 19. Туда же выдаются управляющие сигналы, сформированные в узле 10 и поступающие с входа-выхода 73 узла 10 в блок 11 на вход-выход 75. Вызов следующего байта происходит так же, как и в быстрых каналах по запросу, код которого формируется в узле 10 на основе анализа состояния канала и сигналов управления, приходящих от периферийного устройства.

При передаче в обратном направлении данные от устройства побайтно принимаются в медленный канал, накапливаются з ячейке блока 4 местной памяти каналов и затем передаются в ОП. По завершении обмена формируются сигналы прерывания, которые с выхода 17 поступают в ЦП.

Аппаратная реализация обслуживания запросов от различных источников и максимальное упрощение алгоритма по их выполнению позволило исключить цикл вызова слова микропрограммного управления и его модификацию, «за счет этого увеличить быстродействие устройства.

Блоки и узлы, входящие в устройство внешних каналов, работают следующим образом.

Блок 1.

При обмене данными между АУ и УВК на вход-выход 20 блока 1 подаются следующие сигналы: сигнал установки триггера 175, сигнал признака операции - запись с сумматора АУ в блок 4 или чтение из блока 4 в сумматор на эмиттерный повторитель 176, сигнал режима проведения операции (простоя, запись-чтение, или запись с одновременным запуском канала, или чтение со

0 сбросом канала на эмиттерный повторитель 177), шестиразрядный адрес ячейки местной памяти на регистр 178. На шину 12 устройства через вход-выход 20 подключен выход триггера 175. Выход триггера 175

5 подключен также через выход 24 запроса к входу 60-2 блока 6 приоритета.

Сигнал признака записи-чтения и сигнал режима выполнения операции (состояние 11р) через эмиттерные повторители 176,

0 177 поступают на вход-выход 22, а адрес ячейки блока 4 местной памяти через вентильный, регистр 178 на выход 25. Вход-выход 22 подключен к входу-выходу 33 блока 3, с которого поступает сигнал сброса триг5 гера 175 после того, как запрос на обмен принят к исполнению.

Адрес ячейки местной памяти, пройдя вентильный регистр 178, с выхода 25 поступает в блок 3 на вход-выход 36.

0 На вход-выход 21 данных с шины 13 устройства подается 72р. Код сумматора АУ, который через вентильный регистр 179 и вход-выход 24 поступает на вход 35 в блок 4 местной-памяти. Данные из местной памяти

5 проходят через вход-выход 23, регистр 180, вход-выход 21. Блок 2.

При записи данных из ячейки блока 4 в ОП на вход-выход 28 из блока 3 управления

0 подаются сигналы, разрешающие прием адреса обращения к ОП на регистр 97 и данных на регистр 98 и сигналы, устанавливающие триггер 95 запроса к ОП. Этим сигналом устанавливается также триггер 93 обраще5 ния к ОП. После того как данные будут переписаны в ОП на вход-выход 26, со стороны ОП поступает сигнал, сбрасывающий триггер 93 и триггер 95. Операция записи в блоке 2 .заканчивается и блок освобождается

0 для проведения следующей операции.

При чтении данных из ОП в блок 4 МПК на вход-выход 88 подаются сигналы, разрешающие прием адреса обращения к ОП на регистр 97 и сигналы, устанавливающие

5 триггер 95 запроса к ОП, триггер 96 признак чтения, триггер 93 блокировки обращения к ОП. Кроме того, на вход-выход 28 поступает сигнал, разрешающий прием адреса ячейки блока 4 МПК на регистр 92, в которую будет произведена запись данных. Адрес ячейки

блока 4 МПК подается на вход-выход 29 из блока 3.

После того как адрес обращения к ОП принят к исполнению, со стороны ОП по входу-выходу 26 поступает сигнал, сбрасывающий триггер 95 и переводящий регистр 91 в режим сдвига. Через 14 тактов на выходе регистра 91 устанавливается сигнал, разрешающий прием данных на регистр 99. Этот же сигнал устанавливает триггер 94 запроса чтения оперативной памяти, который с входа 31 поступает в блок 6 приоритетов. При обслуживании данного запроса производится считывание адреса ячейки блока 4 МПК из регистра 92, сброс триггеров 94 и 93. Данные с регистра 99 поступают в ячейку блока МПК. Блок 2 освобождается для следующего обращения к ОП.

Блок 3.

В блоке 3 организуется операция по выполнению приоритетного запроса. Признак и код приоритетного запроса поступают на входы 46 и 47 блока 3. На первой группе элементов ИЛИ 78 формируется обобщенный признак наличия активного запроса. Обобщенный признак активного запроса поступает на шифратор 80, где, в зависимости от сигнала блокировки операций, вырабатывается сигнал, разрешающий прием кода запроса на регистр 84 кода операций, прием кода адреса блока 4 МПК в регистр 85 через шифратор 81. Кроме того, этот сигнал подается на четырехразрядный сдвиговый регистр 83 тактов операции. С выходов этого регистра снимаются временные опера: ции в шифраторы 87, 88, где используются для формирования управляющих сигналов. Кроме того, эти сигналы поступают на вторую группу элементов ИЛИ 82. На этой группе формируется сигнал, блокирующий начало следующей операции. - Код запроса, принятый на регистр 84 кода операции, интерпретируется как код операции. С выхода регистра 84 код поступает на дешифратор 86 кода операции, на шифраторы 87, 88 управляющих сигналов.

На дешифраторе 86 производится выделение сигналов, в зависимости от кода операции, которые затем участвуют в формировании адреса местной памяти. На шифраторе 87, в зависимости от кода операции и временных меток, формируется сигнал, разрешающий запись адреса местной памяти каналов в регистр 85 адреса. Адрес местной памяти каналов поступает либо на мультиплексор 79 на вход 36 из блока 1, либо на вход 35 из блока 2. В зависимости от признака выполняемой операции, через мультиплексор 79 проходит тот или иной адрес и подается на шифратор 81. Через

шифратор 81 адрес может пройти без изменения и поступить на регистр 85 адреса либо модифицироваться в младших разрядах в зависимости от кода выполняемой операции. С регистра 85 адрес местной памяти каналов поступает в блок 4 с выхода 42. в блок 2 с выхода 35, в шифратор 88 управляющих сигналов.

В шифратор 88 в зависимости от кода

0 операции, такта операции, адреса блока 4 МПК вырабатываются управляющие сигналы для блоков 1, 2, 4, 5, 7, 8, 10. При обслуживании запросов от арифметического устройства для формирования сигналов уп5 равления в шифраторе 38 используются сигналы режима операции, поступающие на вход-выход 83 из блока 1. В шифраторе 78 вырабатываются сигналы управления счетчиками состояния селекторных каналов 89.

0 При формировании этих сигналов используются запросы селекторных каналов, которые поступают на вход, 39, минуя блок 6 приоритета.

Код со счетчиков 89 поступает на де5 шифратор 90. При переходе счетчика 89 в состояние 2, 5, 6 на выходе дешифратора 90 формируется код запроса к оперативной памяти. С выхода 46 он подается на первый вход 60-1 запроса блока 6 приоритета.

0Блок 4.

Блок 4 содержит запоминающее устройство 101 в 64 ячейки по 72 разряда. 32 ячейки с младшими адресами закрепляются за быстрыми каналами, со старшими адресами

5 - за медленными каналами. За каждым быстрым каналом закрепляется восемь ячеек, которые используются для хранения адреса управляющего слова, хранения управляющего слова канала, буферизации данных

0 приходящих-уходящих в оперативную память, буферизации данных, участвующих в обмене с каналом, хранении слова .состояния канала. Три ячейки из восьми оставлены в резерве. За каждым медленным каналом

5 закреплено четыре ячейки местной памяти. Они распределяются следующим образом: одна ячейка для хранения управляющего слова передающей части медленного канала, одна - для хранения данных, предназна0 ченных для передачи, одна - для хранения управляющего слова приемной части медленного канала, одна - для хранения принимаемых данных, В ячейки, предназначенные для хранения данных, в конце обмена записыва5 ются слова состояния передающей и приемной частей соответственно.

Информация, предназначенная для записи в блок 4 местной памяти каналов, поступает на входы 47,48,49,50 мультиплексораЮО. На вход 52 ЗУ 101 подается адрес ячейки,сформированной в блоке 3 управления. На вход 51 подаются управляющие сигналы, определяющие режим работы мультиплексора 100 и ЗУ 101. Информация с выходов 47, 48, 53, 54 подается в блоки 1, 2, 5, 7 Соответственно.

Блок 5.

Слово (72 р) из блока 4 местной памяти поступает на вход 56. Под действием управляющих сигналов, поступающих на вход 55 из блока 3, оно записывается в сдвиговые регистры 103-1 -103-9. Запись организуется таким образом. В один регистр записывается по одному разряду из каждого байта слова. Со старших разрядов регистра байт слова по выходу 59-2 подается в блоки 9,11. После записи информации в блоки 9, 11, регистры по сигналу из блока 3 на вход 54 переводятся в режим сдвига и за один такт производится сдвиг слова на один байт. С выхода 59-1 слово может быть считано в блок 4 местной памяти.

Байт данных из блоков 9,11 подается на входы 57, 58 мультиплексора 102. С выхода мультиплексора 102 данные поступают на сдвиговые входе регистров 103.

Блок 6.

, Код запроса поступает от узлов 8 управ- ления быстрых каналов по входу 60-5, от каждого канала в свой регистр 108 узла 104. С выхода регистра 108 код запроса подается на мультиплексор 116, на выход 63 и на дешифратор 109. На дешифраторе 109 двоичный код запроса преобразуется 8 двоичный позиционный и подается в селектор 110, где производится разделение запросов на два типа. Первый тип запросов - это запросы, возникающие на этапе начальной выборки устройства и при завершении обмена, второй тип - запросы, возникающие в процессе обмена данными. Запросы первого типа являются менее приоритетными по сравнению с запросами второго типа, т.к. не требуют большой скорости выполнения. Сигналы о наличии запросов первого или второго типа с селекторов 110 поступают в селекторы 113, 114 соответственно. Кроме того, они подаются на две группы элементов ИЛИ 111,112. С выходов элементов 111,112 снимаются признаки наличия данного запроса.

Селекторы 113,114 построены однотипно. На них производится выборка одного и того же типа запросов из наиболее приоритетного канала. Приоритет по каналам жестко закреплен. Наиболее приоритетным является канала с младшим номером, наименее приоритетным - со старшим номером. Сигналы с селекторов 113, 114 поступают в шифраторы 115, где формируется сигнал управления мультиплексором 116. В зависимости от него мультиплексор 116 пропускает код запроса с выбранного наиболее приоритетного канала. Коды запросов четырех счетчиков состояния каналов в блоке 3 с входа 60-1 поступают на группу 117 элементов ИЛИ-И узла 105 по входу 60-4 на эту же группу подается сигнал блокировки обращения к ОП из блока 2. Если сигнал блоки0 ровки отсутствует, то на выходе группы элементов ИЛИ-И 117 устанавливается признак наличия запроса обращения к ОП. Коды запросов поступают на селектор 118, где производится выборка наиболее при5 оритетного канала, т.е. формируются управляющие сигналы для мультиплексора 119. Приоритет между каналами жестко закреплен и убывает по мере увеличения номера канала. В блоке 6 приоритета признаки запро0 сов разного типа с узлов 104,105,106 поступают в селектор 107 признаков запросов, туда же поступает признак запросов с блоков 1, 2 по входам 60-2, 60-3. В селекторе 107 производится выборка наиболее при5 оритетного типа запроса. Приоритет между типами запросов распределен следующим образом. Первыми выполняются запросы чтения ОП, пришедшие из блока 2 на вход 60-3, затем запросы быстрых каналов, по0 ступающие с узла 104, возникающие на этапе обмена данными (запросы второго типа), затем запросы обращения к ОП (сформированные в узле 105). Следующими по приоритету идут запросы быстрых каналов,

5 поступающие с узла 104, возникающие на этапе начала и конца операций ввода-вывода (первого типа), затем запросы медленных каналов, поступающие с узла 106, наконец, запросы блока 1, приходящие на вход 60-2.

0 Признак приоритетного запроса по выходу 61 поступает в блок 3. Туда же по выходу 62 отдается выбранный код запроса.

По выходу 63 в блок 3 выдаются коды запросов быстрых каналов, вызывающие

5 переключение счетчиков 89 быстрых каналов. Эти запросы участвуют непосредственно в формировании операции в блоке 3 и поступают на свое, индивидуальное для каждого канала оборудование.

0 Блок 7.

Начальный адрес канальной программы (массив управляющих слов в оперативной памяти) записывается с сумматора АУ в блок 4 местной памяти каналов. При операциях,

5 связанных с запуском канала, этот адрес передается в ОП и одновременно поступает на счетчик 124 по входу 64-2. По сигналу с входа 64-1 из блока 3 к адресу прибавляется единица, после чего он записывается в блок 4 местной памяти каналов. Таким образом, адрес подготовлен для выбора следующего управляющего слова.

Начальный адрес данных и длина массива задаются в управляющем слове. При обращении к ОП заданные начальный адрес и длина по входу 64-2 поступают на счетчики 124, 123 адреса и длины соответственно. К адресу массива прибавляется единица, а из счетчика 123 длины вычитается единица. Затем информация со счетчиков 123, 124 переписывается в ячейку блока 4 местной памяти, где хранится управляющее слово. Таким образом подготавливается выборка следующего слова данных.

При работе с быстрыми каналами реализована операция Переход в канале, которая позволяет выбирать управляющие слова из ОП по произвольному адресу. В процессе выполнения этой операции исполнительный адрес выбирается из ячейки блока 4 местной памяти, где хранится управляющее слово канала и помещается сначала на счетчик 124, а затем без изменения в ячейку местной памяти, предназначенную для хранения адреса управляющего слова .

Блок 8.

Узел 8 управления построен как конеч- ныйгавтоматс 15 устойчивыми состояниями. Состояние канала определяется счетчиком 125 состояния канала. Процесс ввода-вывода разбит на этапы, каждому из которых соответствует свое состояние канала. Запуску канала соответствует перевод канала из состояния О в состояние 1. Запуск канала может быть произведен как со стороны ЦП по сигналу Пуск, поступающему на вход 66 из блока 3, так и со стороны внешнего устройства, поступающего по входу- выходу 67 из блока 9.

Шифратор 129 выполнен как набор элементов И-ИЛИ-НЕ. Сигналы на его выходе являются результатом анализа комбинации сигналов, снимаемых с выходов счетчика 125 состояний, триггеров 130 управляющих и идентифицирующих сигналов ЕС ЭВМ, регистр 132 фиксации ошибок, счетчика 133 байтов, кода операции, флагов, которые передаются по входу-выходу 67 из блока 9, сигналов подтверждения обслуживания запросов, приходящих по входу 66 из блока 3.

В результате работы шифратора 129 на регистре 126 устанавливается код запроса, который затем с выхода 68 поступает в блок 6. Устанавливаются триггеры 130 в соответствии с протоколом обмена по интерфейсу ЕС ЭВМ. Переключаются счетчики 133 байтов. Фиксируются ошибки на регистрах 132. Изменяется состояние счетчика 125. Формируются управляющие сигналы для блока

9. В конце обмена устанавливаются триггеры 127 или 128 прерывания. Блок 9.

Работа всех узлов блока 9 производится под управлением сигналов, приходящих из узла управления быстрыми каналами по входу-выходу 69.

Код операции ввода-вывода, адрес внешнего устройсвта, флаги операции и

0 данные поступают побайтно из блока 5 по входу 70 на регистр 134.

Код операции ввода-вывода с выхода регистра 134 подается на второй выходной регистр 139 и через лраобразователь 141

5 уровней ЭСЛ-ТТЛ на интерфейсный вход- выход 18. Кроме того, код операции подается на дешифратор 135, где производится его преобразование в позиционный, и затем на четырехразрядный регистр 138. Позицион0 ный код операции по входу-выходу 69 поступает в узел 8 управления.

Адрес внешнего устройства так же, как код команды, поступает на второй выходной регистр 139 и далее через преобразователь

5 141 уровней на вход-выход 18. Кроме того, он подается на узел 144 сравнения адреса, где в дальнейшем производится сравнение с адресом, поступившим от внешнего устройства.

0 В процессе приема данных от внешнего устройства производится формирование контрольных разрядов слова. Для этого данные подаются на счетчики 147,148. Сформированные контрольные разряды через

5 мультиплексор 146 и регистр 149 поступают в блок 5.

Через мультиплексор 146 передаются байты состояния канала, сформированные в конце обмена в узле управления 8 и посту0 лающие по входу 69,

Флаги операции ввода-вывода поступают с выхода регистра 134 на регистры флагов. Флаги, заданные в операции Переход в канале, поступают на регистр 136 и сохра5 няются до следующей операции Переход в канале. Флаги, заданные в операциях Считывание, Запись, Проверить ввод- вывод, поступают в регистр 137 и сохраняются только на момент данной операции.

0 Значения с выходов регистров 136,137 подаются в узел 8 управления по входу-выходу 69.

Все байты информации, передаваемые внешнему устройству, обрамляются нейт5 ральным разрядом. Получение контрольного разряда производится на сумматоре 140. Байт информации от внешнего устройсвта поступает с входа-выхода 18 на преобразователь уровней 142, а затем на первый входной регистр 143 и через мультиплексор

146, второй выходной регистр 149 по выходу 71 подается в блок 5. Адрес от устройства подается также в узел 144 сравнения адреса. Результат сравнения поступает в узел 8 управления по входу-выходу 69.

Управление медленными каналами организовано аналогично управлению быстрыми каналами. Основное отличие заключается в том, что обмен с ОП произво- млтся непосредственно по запросу, сформированному в узле 10, а в блоке 4 МПК выделены ячейки для хранения управляющего слова источника, данных источника, управляющего слова приемника, данных приемника.

Формула изобретения 1. Устройство внешних каналов, содержащее блок регистров сопряжения с

оперативной памятью, первый адресноинформационный вход-выход и вход-выход запросов обращения к оперативной памяти

которого являются соответствующими входами-выходами устройства для подключения к шинам оперативной памяти, блок местной памяти, адресный и управляющий

входы которого соединены соответственно к первому и второму выходам блока управления, первый вход-выход которого подключен к управляющему входу-выходу блока регистров сопряжения с оперативной памятью, соединенного вторым адресно-ин- формационным входом-выходом с адресно-информационным входом-выходом блока местной памяти, блок приоритета, первым выходом соединенный с входом кода запроса блока управления, блок модификации, соединенный с входом режима с

третьим выходом блока управления, группу блоков регистров сопряжения с быстрыми каналами, интерфейсные входы-выходы которых являются соответствующими входами-выходами устройства для подключения к интерфейсным входам-выходам быстрых каналов, и группу блоков регистров сопряжения с медленными каналами, интерфейсные входы-выходы которых являются соответствующими входами-выходами устройства для подкючения к интерфейсным входам-выходам медленных каналов, от л и- чающееся тем, что, с целью повышения быстродействия устройства, в него введены блок регистров сопряжения с арифметическим устройством, блок сдвигового регистра, группу узлов управления быстрыми каналами и группу узлов управления медленными каналами, причем второй и третий входы-выходы и вход адреса узла управления соединены соответственно с адресным входом-выходом блока регистров сопряжения с оперативной памятью и входом-выходом режима обмена и первым выходом блока регистров сопряжения с арифметическим устройством, вход-выход запроса и первый вход-выход данных которого являются соответствующими входами-выходами устройства для подключения к шинам управления и данных арифметического устройства, а второй вход-выход данных соединен с информационным входом-выходом блока местной памяти, первый, второй и третий входы кодов запроса и вход блокировки обращения к оперативной памяти блока приоритета соединен соответственно с четвертым выходом блока управления, вторым выходом блока регистров сопряжения с арифметическим устройством и первым и вторым выходами блока регистров сопряжения с оперативной памятью, пятый выход блока управления соединен с входом управления режимом работы блока сдвигового регистра, первая группа выходов блока управления соединена с входами запуска узлов управления быстрыми каналами группы, вторая группа выходов блока управления подключена к входам запуска узлов управления медленными каналами группы, выходы кода запросов узлов управления Быстрыми каналами группы соединены с четвертым входом запросов блока приоритета, выходы кода запросов узлов управления медленными каналами группы соединены с пятым входом кодов запроса блока приоритета, вход признака запроса блока управления соединен с вторым выходом блока приоритета, вход кода запроса быстрых каналов блока управления соединен с третьим выходом блока приоритета, первый выход данных блока местной памяти соединен с первым входом данных блока сдвигового регистра, второй выход данных блока местной памяти соединен с входом данных блока модификации, первый вход данных блока местной памяти подключен к первому выходу блока сдвигового регистра, второй вход данных блока местной памяти соединен с выходом блока модификации, второй выход блока сдвигового регистра подключен к входам данных блоков регистров сопряжения с быстрыми каналами группы и медленными каналами группы.второй вход данных блока сдвигового регистра соединен с выходами данных блока регистров сопряжения с быстрыми каналами группы, третий вход данных блока сдвигового регистра соединен с выходами данных блоков регистров сопряжения с медленными каналами группу, управляющие входы-выходы блрков регистров сопряжения с медленными и быстрыми каналами групп соединены соответственно с входами-выходами управления

узлов управления медленными и быстрыми каналами групп, выходы прерывания которых образуют группу выходов устройства для подключения к шине прерывания процессора.

2. Устройство по п.1, о т л и ч а ю щ е е- с я тем, что узел управления медленными каналами содержит счетчики состояния источника и приемника, шифраторы управляющих сигналов приемников и источника, первые информационные входы которых подключены к первым выходам счетчиков состояния приемника и источника, регистры фиксации ошибок источника и приемника, триггеры запросов в контроллер источника и приемника, две группы элементов И-ИЛЙ, выходы которых являются соответственно выходами прерывания и запросов узла, и триггеры выработки управляющих сигналов интерфейса источника и приемника, выходы которых и вторые информационные входы шифраторов управляющих сигналов источника и приемника образуют управляющий вход-выход узла, причем информационные входы и выходы регистров фиксации ошибок источника и приемника подключены соответственно к группам выходов и к третьим информационным входам шифраторов управляющих сигналов источника и приемника, группы выходов которых подключены соответственно к установочным входам триггеров запросов в контроллер источника и приемника и триггеров выработки управ: ляющих сигналов интерфейса источника и приемника, входы сброса которых соединены соответственно с вторыми выходами счетчиков состояния источника и приемника, первые и вторые входы элементов И- ИЛИ первой и второй групп соединены соответственное группами выходов шифраторов управляющих сигналов источника и приемника, выходы счетчиков состояния ис-. точника и приемника соединены соответственно с третьими и четвертыми входами элементов И-ИЛИ первой группы, а входы образуют вход запуска узла, третий, четвертые и пятые входы элементов И-ИЛИ подключены соответственно к выходам триггеров запросов в контроллер источников и приемника и счетчика состояния приемника.

3. Устройство поп.1,отличающее- с я тем, что узел управления быстрыми каналами содержит шифратор управляющих сигналов, первый информационный вход которого является входом запуска узла, счетчик байтов и счетчик состояния быстрого канала, входы-выходы которых подключены соответственно к первому и второму входам-выходам шифратора управляющих сигналов, третий и четвертый входы-выходы и первая группа выходов которого соединены соответственно с входами-выходами триггера управляющих и идентифицирующих сигналов интерфейса и регистра фиксации ошибок и входами регистра кода запроса, первого и второго триггеров прерывания и регистра характеристики окончания операции ввода-вывода, причем выход регистра кода запроса является выходом запросов узла, выходы первого и второго триггеров образуют выход прерывания узла, второй информационный вход и группа выходов шифратора управляющих сигналов и выходы триггера управляющих и идентифицирующих сигналов интерфейса, регистра характеристики окончания операции ввода- вывода и регистра фиксации ошибок образуют управляющий вход-выход узла.

I

31 32 W2d

1

55+59-2

со

-

со If) а со

1695313

60-b

Ј

6Н

60-b

Ј

№

ffd

г

119

| название | год | авторы | номер документа |

|---|---|---|---|

| Система ввода-вывода для микропрограммируемой ЭВМ | 1988 |

|

SU1667084A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1280642A2 |

| Комбинированный канал | 1986 |

|

SU1405067A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1278867A2 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1405063A2 |

| Устройство для сбора данных о работе ЭВМ | 1982 |

|

SU1121679A1 |

| Устройство для сопряжения периферийных устройств с процессором и оперативной памятью | 1983 |

|

SU1156084A1 |

| Устройство для сопряжения процессора с каналами связи | 1978 |

|

SU763882A1 |

| Устройство для управления вводом-выводом | 1989 |

|

SU1735859A1 |

| Устройство для обмена информацией между цифровой вычислительной машиной и внешними устройствами | 1981 |

|

SU1003066A1 |

Изобретение относится к вычислительной технике и может быть использовано для обмена информацией между оперативной памятью процессора, имеющей один путь доступа, и периферийными устройствами. Цель изобретения - повышение быстродействия устройства. Цель достигается тем, что в устройство, содержащее блок регистров сопряжения с оперативной памятью, блок управления, блок приоритета, блок местной памяти, группу блоков р егистров сопряжения с быстрыми каналами, группу блоков регистров сопряжения с медленными каналами и блок модификации, введены блок регистров сопряжения с арифметическим устройством, блок сдвигового регистра, группу узла управления быстрыми каналами и группу узлов управления медленными каналами. По сравнению с известным байт- мультиплексным каналом блок управления и узлы управления быстрыми и медленными каналами выполнены аппаратно. Использование предлагаемого устройства внешних каналов позволяет подключать внешние устройства, имеющие скорость обмена до 15 Мбайт/с. 2 з.п. ф-лы, 15 ил. и

к№7

6И

123

Фиг. 10

.Фиг. и

+ 6

,№-2 Т-

Шt

М

Фиг. 11

Ю

73

Фиг. 13

| Мультиплексный канал | 1984 |

|

SU1167613A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Байт-мультиплексный канал | 1981 |

|

SU972496A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-11-30—Публикация

1988-11-04—Подача