Изобретение относнтся к области вычислительной техники и может быть использовано при построении многопрограммных и многопроцессорных вычирпительных систем, а также управляюпшх и

вычислительных систем с разветвленной сетью абонентов.

Известен микропроцессор, содержащий последовательный сумматор, входную и выходную последовательные.шины, буферные регистры, логический блок и блок управления с запоминающим устройством (ЗУ) микропрограмм 1. Обработка входной информации в нем производится в соответствии с микрооперацией, выбираемой из ЗУ, работой которого управляет логический блок, а ветвление и ход выполняемой программы определяются управляюашми словами, поступающими на вход логического блока.

Недостатками этого микропроцессора является то, что при построении устройства ввода-вывода на его основе требуется значительное число дополнительных внеиших схем (устройство управления, устройство прерывания и т.д.), а также отсутствие гибкости за счет

того, что архитектура и соединения внешних схем определяют жесткую структуру такого устройства ввода-вывода.

Известен также микропроцессор используемый для организации системы ввода-вывода информации-содержащей устройство управления, регистр микрокоманды, соединенный с арифметико-логическим устройством, и оперативную память чисел, соединенную с устройством сопряжения 2.

Недостатком этого микропроцессора является снижение быстродействия за счет использования единой магистрали между памятью, центральным процессором и процессорами ввода-вывода.

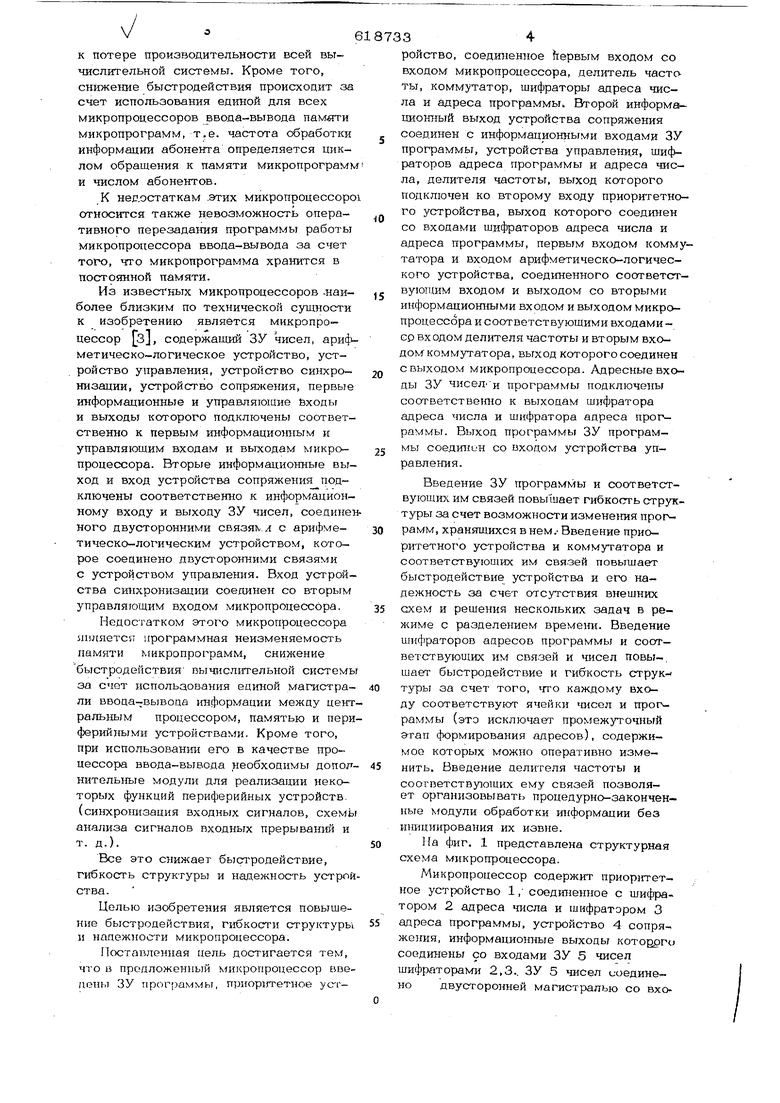

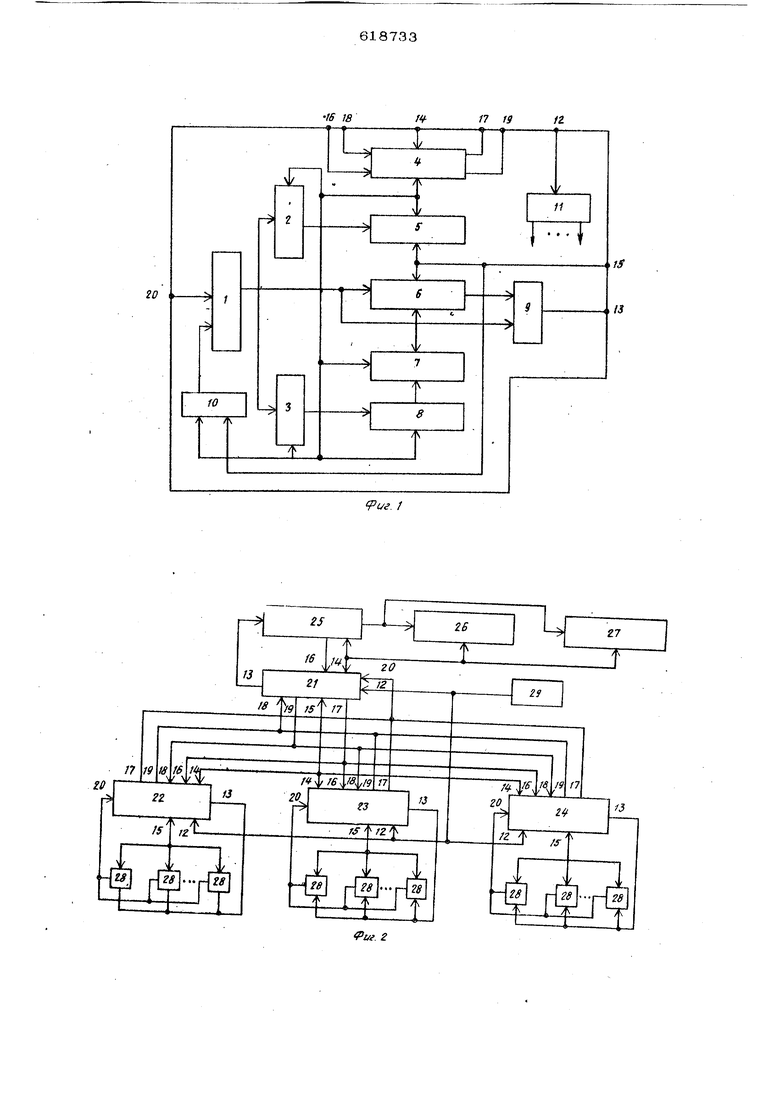

При этом в двухъярусной вычислительной системе во время выдачи информации в периферийные устрсйства из микропроцессоров ввода-вывода магистр)аль обмена информацией занята, и, слеаовательно, работа центрального процессора с памятью невозможна, что приводит 6 к потере производительности всей вычислительной системы. Кроме того, снйже1ше быстродействия происходит за счет использования единой для всех микропроцессоров ввода-вывода памяти микропрограмм, т.е. частота обработки информации абонента определяется циклом обращения к памяти микропрограмм и числом абонентов. К недостаткам .этих микропроцессоро относится также невозможность оперативного перезадания программы работы микропроцессора ввода-вывода за счет того, что микропрограмма хранится в постоянной памяти. Из известных микропроцессоров -наиболее близким по технической сущности к изобретению является микропроцессор з, содержащий ЗУ чисел, арифметическо-логическое устройство, устройство управления, устройство синхронизации, устройство сопряжения, первые информационные и управляющие Ьходьг и выходы которого подключены соответственно к первым 1шформациого1ым и управляющим входам и выходам микропроцессора. Вторые информационные выход и вход устройства сопряжения подключены соответственно к информационному входу и выходу ЗУ чисел, соединен ного двусторонними связяк л с арифметическо-логическим устройством, которое соединено двусторонними связями с устройством управления. Вход устройства синхронизации соединен со вторым управляющим входом микропроцессора. Недостатком этого микропроцессора 5П)ляетс17 программная неизменяемость памяти микроцрограмм, снижение быстродействия вычислительной системы за счет использования единой магистрали ввода-вывода 1шформации между цент ральным процессором, памятью и пери ферийными устройствами. Кроме того, при использовании его в качестве процессора ввода-вывода необходимы допол нительные модули для реализации некоторых функций периферийных устройств, (синхронизация входных сигналов, схемь анализа сигналов входных прерываний и т. д.). Все это снижает быстродействие, гибкость структуры и надежность устрой ства. Целью изобретения является повышение быстродействия, гибкости структуры и надежности микропроцессора. Поставленная цель достигается тем, что в предложенный микропроцессор введены ЗУ программы, приоритетное уст34ройство, соединенное первым входом со входом микропроцессора, делитель часто ты, коммутатор, шифраторы адреса числа и адреса программы. Второй информационный выход устройства сопряжения соединен с информационными входами ЗУ программы, устройства управления, шифраторов адреса программы и адреса числа, делителя частоты, выход которого подключен ко второму входу приоритетного устройства, выход которого соединен со входами шифраторов адреса числа и адреса программы, первым входом коммутатора и входом арифметическо-логического устройства, соед1шенного соответствующим входом и выходом со вторыми информационными входом и выходом микропроцессора и соответствующими входами- С9 входом делителя частоты и вторым входом коммутатора, выход которого соединен с выходом микропроцессора. Адресные входы ЗУ чисели программы подключены соответственно к выходам шифратора адреса числа и шифратора адреса программы. Выход программы ЗУ программы соединен со входом устройства управления. Введение ЗУ программы и соответствующих им связей повышает гибкость структуры за счет возможности изменения прог рамм, хранящихся в нем/ Введение приоритетного устройства и коммутатора и соответствующих им свя.зей повышает быстродействие устройства и его надежность за счет отсутствия внешних схем и решения нескольких задач в режиме с разделением времени. Введение шифраторов адресов программы и соответствующих им свя.зей и чисел повы-. шает быстродействие и гибкость струк- туры за счет того, что каждому входу соответствуют ячейки чисел и программы (это исключает промежуточный этап формирования адресов), содержимое которых можно оперативно изменить. Введение делителя частоты и соогветствуюших ему связей позволяет организовывать процедурно-законченные модули обработки информации без инициирования их извне. 1{а фиг. 1 представлена структурная схема микропроцессора. Микропроцессор содержит приоритетное устройство 1 , соединенное с шифратором 2 адреса числа и шифратором 3 адреса программы, устройство 4 сопряжения, информацнош-гые выходы КОТОЕОГО соединены 90 входами ЗУ 5 чисел шифраторами 2,3.. ЗУ 5 чисел соединено двусторонней магистралью со входами арифметическо-логического устройства 6, ко Bxonatvf которого Tioncoeamie но устройство управления 7, ко входам которого подсоединено ЗУ 8 программы. Выход устройства 6 соеаинен со входом коммутатора 9, а к его другому входу подсоединен выход приоритетного устройства 1. К одним входам устройства

Iподсоединены выходы делителя 10частоты, ко входам которого подсоединень выходы устройств 4 и 6. В состав микропроцессора также входит устройство

IIсинхронизации, вход которого соединен со вторым управляющим входом 12 микропроцессора.

Выход коммутатора 9 соединен с вМходом 13 микропроцессора. Вход устройства 4 соединен с первыми информааио ными входами и выходами 1 4 микропроцессора. Выход устройства О- соединен со вторыми информационными входами и выходами 15 микропроцессора. К управляющим входам и выхоцам устройства 4 подсоединены соответственно управляющие входы и выходы 16-19 микропроцессора, а ко входам устройства 1 вхоц 20 микропроцессора.

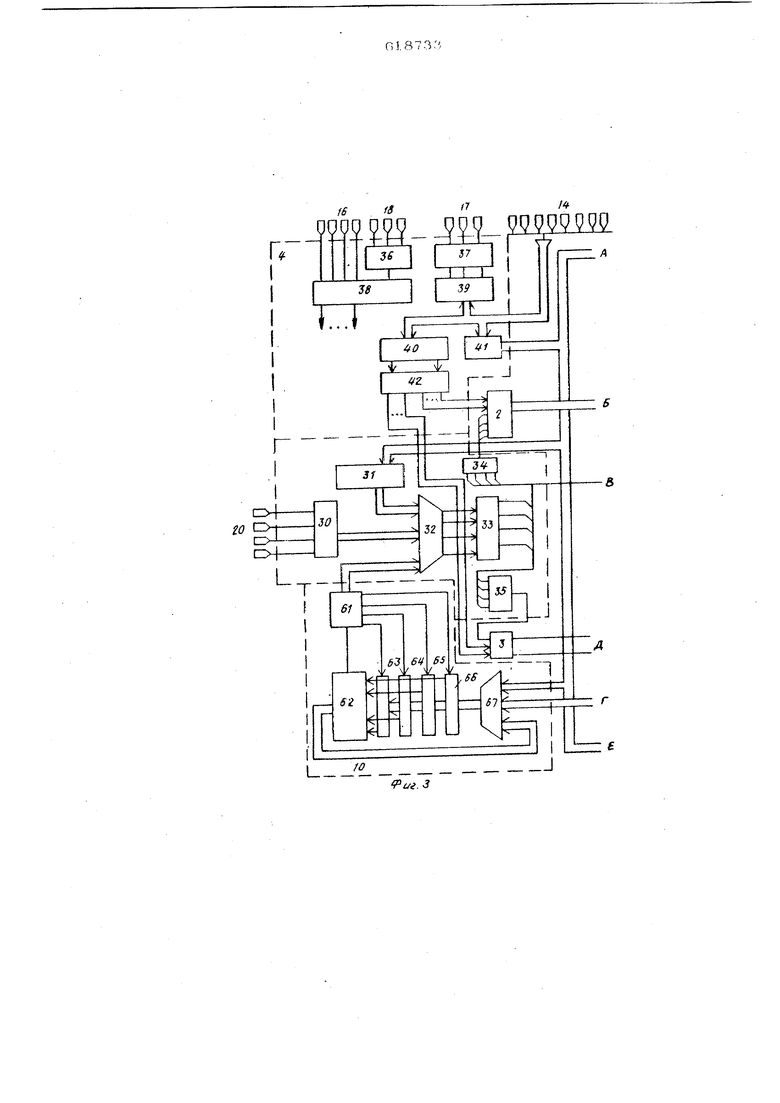

На фиг. 2 представлен вариант вычислительной системы, содержащей микропроцессоры 21-24, соединенные jJaгистралями входами и выхоцами 12- 20 с центральным процессором 25, оперативным запоминающим устройством (ОЗУ) 26, постоянным, запоминающим устройством (ПЗУ) 27, периферийными устройствами 28 и генерштором сиихросигналов 2 9.

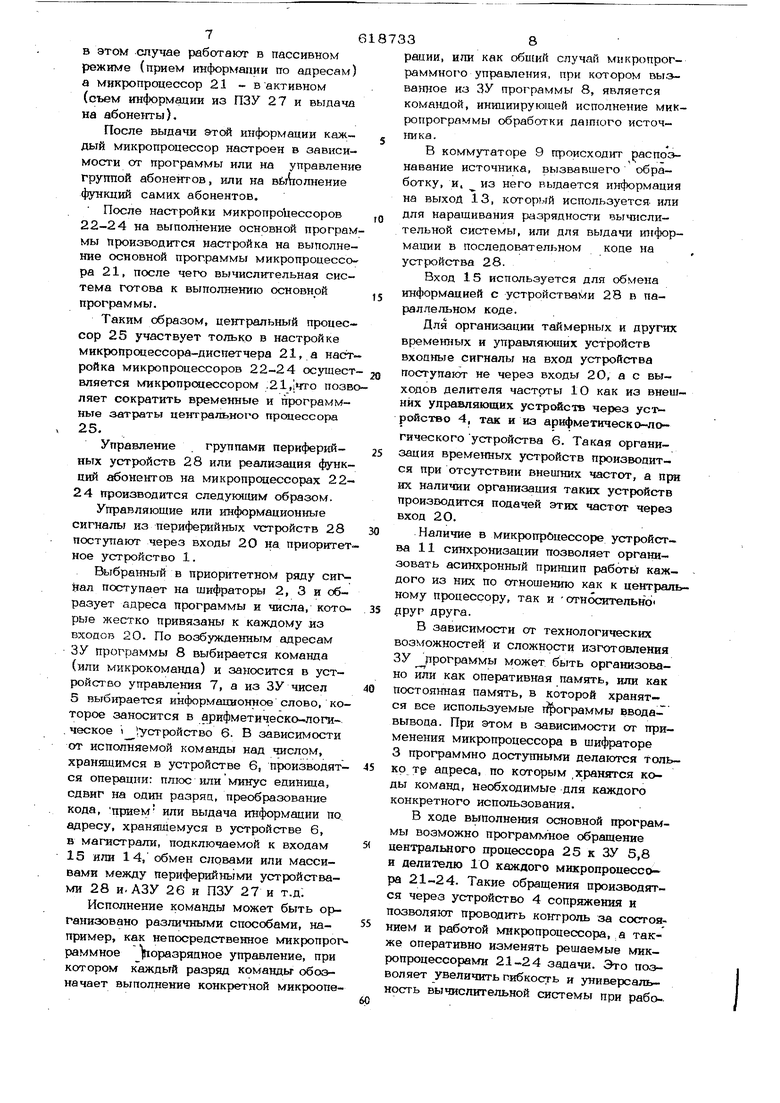

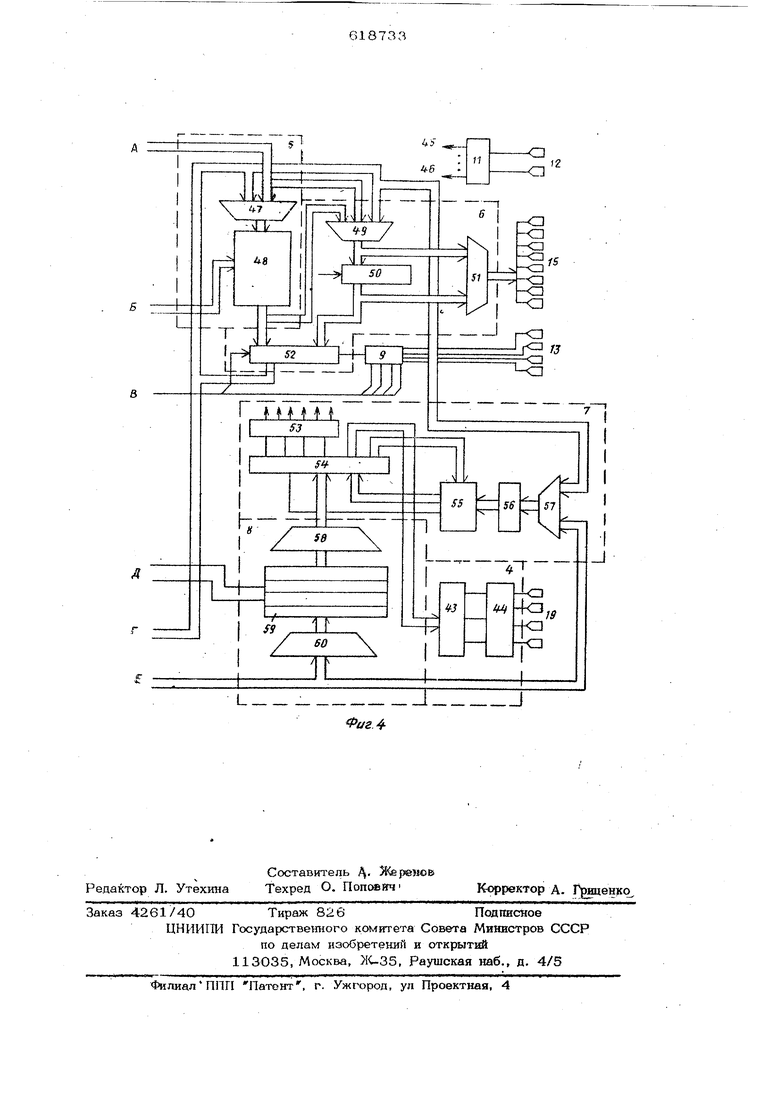

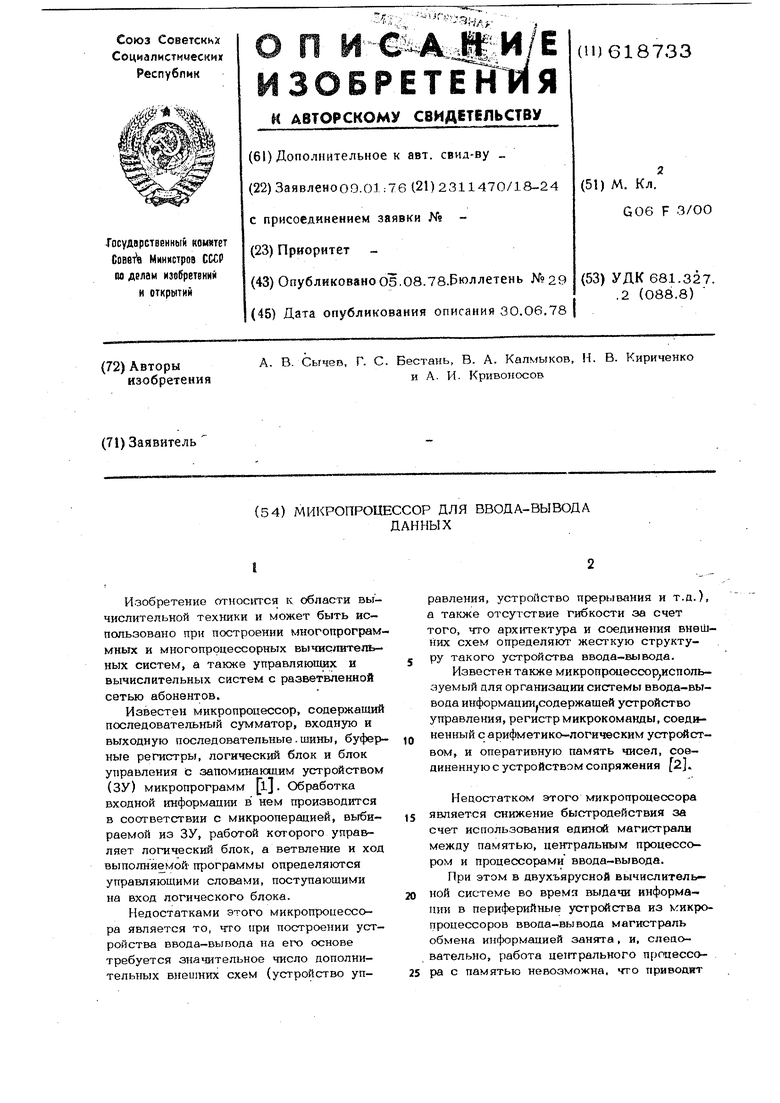

На фиг. 3 и 4 прецставлен вариант функциональной,схемы микропроцессора

Приоритетное устройство 1 содержит входной регистр 30, регистр уелоВИЙ 31, мультиплексор 32, приоритетный регистр 33, вентили числа и адреса 34,35.

Устройство сопряжения 4 содержит вхоцной дешифратор 36, выходной

дешифратор 37, дешифратор 38 внешних микроопераций , регистр 39, адресный регистр 40, входной буфер 41, дешифратор адреса 42, входные регистры 43 и дешифратор 44, Цифрами 45, 46 обоэначеньг выходы устройства 11 (фиг.4).

ЗУ -чисел 5 содержит мультиплексор 47, матр1щу памяти 48.

Арифметическо-логическое устройство 6 содержит мультиплексор 49, регистр- аккумулятор 50, выходной мультиплексор 51, сумматор 52.

Устройство управления 7 содержит дешифратор 53 микроопераций, регистр

54 микроопераций, (1еши(ратор Г)Г, услвий, регистр 56 УСЛОВ1Ш и мультиплексор 57.

ЗУ программы 8 включает мультиплексор 58, матрицу памяти 59 и муль плексор 60.

Делитель 10 содержит коммутатор 61, сумматор 62, статические регистры 63-в6 к мультиплексор 67.

Микропрсжессор работает следующим образом.

Выполняемые микропроцессором функции и режим работы определяются содержимым ЗУ 8 программы.

Например, микропроцессор 21 выполняет функции диспетчеризации и сопряжения между пет-ральным процессором 25, ЗУ 26,27 и микропроцессорами ввода-вывода 22-24. В соответствии с этим в ЗУ 8 программы каждого микропроцессора 21-24 записывается такая программа, которая настраивает его на выполнение конкретных задач. При этом в вычислительной системе центральный процессор 25 выбирает программу и константы из ПЗУ устройства 27 и заносит их в ЗУ 8 программы и ЗУ 5 чисел микропроцессора 21, который в этом случае работает в пассивном режиме. npHHHNfaeMan программа настраивает микропроцессор 21 на организацию выдачи программ и констант в режиме с разцелением времени из устройства 27 в микропроцессоры 22-24, а константы являются начальными адресами ПЗУ 27 к ЗУ 5 и 8 микропроцессоров 22-24. Выдача информации производится по входам 14 последовательно, т.е. сначала выдается адрес, а затем информация, которая будет записана по этому адрюсу. aзпeлeние этой информации производится подачей соответствующих микрокоманд по входам 16.

После приема этой информации микропроцессор 21 организует выдачу програ гм и констант из ОЗУ 26 и ПЗУ 27 в микропроцессорь 22-24 в режиме с разделением врюмени.

Выдача информации из микропроцессора 21 осуществляется по выходу 15, а прием информации в микропроцессоры 22-24 - по входу 14. Селектирование микропрсщессоров 22-24 и выдача соответствующих управляющих микрокоманд производится на выходы 16,18 микропроцессоров 22-24 из шин, подключаемых к входам 17,19 микропроцессора 21. Микропроцоссорь 22-24

в этом случае работают в пассивном режиме (прием информации по адресам) а микропроцессор 21 - в активном (съем информации из ПЗУ 27 и выдача на абоненты).

После выдачи этой информации каждый микропроцессор настроен в зависимости от программы или на управление группой абонентов, или на вЬ олнение функций самих абонентов.

После настройки микропроцессоров 22-24 на выполнение основной программы производится настройка на выполнение основной программы микропроцессора 21, после чего вычислительная система готова к выполнению основной программы.

Таким образом, центральный процессор 25 участвует только в настройке микропроцессора-диспетчера 21, а настройка микропроцессоров 22-24 осущест вляется микропроцессором .21,|что позвляет сократить временные и программные затраты центрального процессора 25.

Управление группами периферийных устройств 28 или реализация функций абонентов на микропродессорах 2224 производится следуюишм образом.

Управляющие или информационные сигналы из периферийных vcтpoйcтв 28 поступают через входы 20 на приоритетное устройство 1.

Выбранный в приоритетном ряду сигнал поступает на шифраторы 2, 3 я образует адреса программы и числа, которые жестко привязаны к каждому из входов 20. По возбужденным адресам ЗУ программы 8 выбирается команда (или микрокоманда) и заносится в устройство управления 7, а из ЗУ чисел 5 выб1фается информационное слово, которое заносится в арифметическо-логи. ческое ( .устройство 6. В зависимости от исполняемой команды над числом, хранящимся в устройстве 6, производятся операции: плюс или минус единица, сдвиг на один разряц, преобразование кода, прием или выдача информации по адресу, хранящемуся в устройстве 6, в магистрали, подключаемой к входам 15 или 14, обмен словами или массивами между периферийньгми устройствами 28 и. АЗУ 26 и ПЗУ 27 и т.д;

Исполнение команды может быть организовано различными способами, например, как непосредственное микропрограммное юразрядное управление, при котором каждый разряд команды обозначает выполнение конкретной микрооперации, или как обший случай микропрограммного управления, при котором ВЫ.Эванноа из ЗУ программы 8, является командой, инициирующей исполнение микропрограммы обработки дашюго источника.

В коммутаторе 9 происходит распознавание источника, вызвавшего обработку, и. из него выдается информация на выход 13, который используется или для наращивания разрядности вычислительной системы, или для выдачи информации в последовательном коде на устройства 28..

Вход 15 используется для обмена информацией с устройствами 28 в параллельном коде.

Для организации тай мерных и других временных и управляющих устройств BxooHbJe сигналы на вход устройства поступают не через входы 20, а с выходов делителя частоты 1О как из внешних управляющих устройств через устройство 4, так и из арифметическо-логического устройства 6. Такая организация временных устройств производится при отсутствии внешних частот, а пр их наличии орга газация таких устройств производится подачей этих частот через вход 2О.

Наличие в микропроцессоре устройства 11 синхронизации позволяет организовать асинхронный принцип работы каждого из них по отношению как к централному процессору, так и -относительно рруг друга.

В зависимости от технологических возможностей и сложности изготовления ЗУ ррограммы может быть организовано или как оперативная память, или как постоянная память, в которой хранятся все используемые гфограммы вводавывода. При этом в зависимости от применения микропроцессора в шифраторе 3 программно доступными делаются только Tg адреса, по которым , хранятся коды комавд, необходимые для каждого конкретного использования.

В ходе выполнения основной гфограммы возможно программное обращение центрального процессора 25 к ЗУ 5,8 и делителю 10 каждого микропроцессор ра 21-24. Такие обращения производятся через устройство 4 сопряжения и позволяют проводить контроль за состоянием и работой MitKpoпроцессора, а также оперативно изменять решаемые микропроцессорами 21-24 задачи. Это позволяет увеличить гибкость и универсальность вычислительной системы при рабо-. те с периферийнь мн устройствами, используе ыми только на отде/гьных участках времени, а также повыскгь надежность системы за счет того, что управляющая программа отказавшего микропроцессора передается исправному. Прк этом в качестве коммутатора между периферийными устройствами и микропроцессорами ввода-вывода может быть использован предложенный микропродессор. Формула изобретения Микропроцессор для ввода-вывода дан ных, содержащий запоминающее устройсФ во чисел, ариф етическо-логическое устройство, устройство управления, устройство синхронизации, устройство сопряжения, первые информацио)гаые и управляющие входы и выходы которого подключены соответственно к первым информацио ным и управляющим входам м и выхо дам микропроцессора, вторые информационные выход и вход устройства сопряжения подключены соответственно к информационному входу и выходу запоминающего устройства чисел, соединенного двусторонними связями с арифметическилогическим- устройством, которое сое динено двусторонними связями с устройством управления, вход устройства синхронизации соединен со вторым управлаюпшм входом микропроцессора, о т.л вчаюшийся тем, что, с целью повышения быстродействия, гибкости структуры и надежности, в него введены запоминающее устройство программы приоритетное устройство, соединенное первым входом со входом микропроцессора, делитель частоты , коммутатор. шифраторы адреса щгсла и ддроса программы; причем второй инфорглапионный выход устройства с -пряжения соединен с информационными входами запоминак шего устройства программы, устройства управления, шифраторов адреса программы и ацреса числа,и делителя частоты, выход которого подключен ко второму вхоау приоритетного устройства, выход которого соединен со входами шифраторов адреса числа и адреса программы, первым входом коммутатора и входом арифметическо-логического устройства, соеиииенного соответствующим вxoдo f и выходом со вторыми информационными входом и выходом микропрсщессора и соответствующими входами - со входом делителя частоты и вторым входом коммутатора, выход которого соединен с выходом, микропроцессора; адресные ВХОДЫ запоминающих устройств чисел и программы подключены соответственно к выходам шифратора адрюса числа и шифратора адреса программы; выход запоминающего устройства программы соединен со входом устройства управления. Источники информации, принятые во внимание при экспертизе: 1.Патент США № 3878514, кл. 34CU172.5, М.кл. Q 06 F 9/16, 975. , 2.Чеглаков Л. В. и др. Специализированная ЦВМ на микропроцессорах. Журнал Электронная техника , серия 11, выпуск 2, 1975. 3.Журнал Электроника, перевод английского Ne 26, 1974, Мир, тр. 6О-89.

IS 18

17 19

11

/4

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор | 1983 |

|

SU1213485A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Устройство для сопряжения эвм с абонентами | 1984 |

|

SU1215114A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1136162A1 |

| Микропрограммное устройство для ввода-вывода информации | 1983 |

|

SU1144099A1 |

| Микропрограммное устройство для приоритетного обслуживания группы абонентов | 1984 |

|

SU1302277A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1156073A1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Программируемый контроллер | 1990 |

|

SU1714599A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

20

13

/4

18

ЩШШ

5

Риг.З

.J

Фаг

Авторы

Даты

1978-08-05—Публикация

1976-01-09—Подача