(54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С САМОКОНТРОЛЕМ

| название | год | авторы | номер документа |

|---|---|---|---|

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО ИЗОБРАЖЕНИЙ | 1990 |

|

RU2047921C1 |

| Репрограммируемое постоянное запоминающее устройство | 1989 |

|

SU1695384A1 |

| Устройство для управления динамической памятью | 1987 |

|

SU1524089A1 |

| Динамическое запоминающее устройство | 1983 |

|

SU1166177A1 |

| Устройство для управления динамической памятью | 1990 |

|

SU1783582A1 |

| Устройство для ввода-вывода аналоговых сигналов | 1981 |

|

SU1015369A1 |

| Динамическое запоминающее устройство с восстановлением информации | 1989 |

|

SU1689990A1 |

| Устройство адресации к динамической памяти | 1987 |

|

SU1444785A1 |

| Устройство для измерения интервалов времени | 1990 |

|

SU1739361A1 |

| Буферное запоминающее устройство на полупроводниковых динамических элементах памяти | 1987 |

|

SU1525744A1 |

1

Изобретение отнбсится к автоматике и вычислительной технике, в частности к запоминающим устройствам.

Известно запоминающее устройство на однотранзисторных ячейках памяти, которое содержит динамические запоминающие 5 элементы (ЗЭ), для сохранения информации, в которых требуется периодически проводить регенерацию хранимой информации 1.

Недостаток устройства состоит в том, что оно не используется во время регене- ю рации информации, которая составляет значительную часть от всего времени работы устройства.

Наиболее близким к предлагаемому по технической сущности является запоминаю- 15 щее устройство с использованием итеративных кодов, содержащее матрицу ЗЭ из основных строк и столбцов, в которую включены дополнительные строка и столбец ЗЭ. Информация, записываемая в дополнитель- jo ную строку и столбец, кодируется таким образом, чтобы в каждом столбце и каждой строке матрицы число логических единиц было четным (нечетным). При считывании осуществляется проверка четности по строке и столбцу. Если четность не реализуется, то это свидетельствует о том, что ячейка, находящаяся на пересечении соответствующих строк столбца, содержит ложную информацию и сигнал при считывании должен быть проинвертирован 2.

Недостаток устройства - невозможность применения в устройстве однотранзисторных динамических запоминающих элементов.

Цель изобретения - повышение точности контроля.

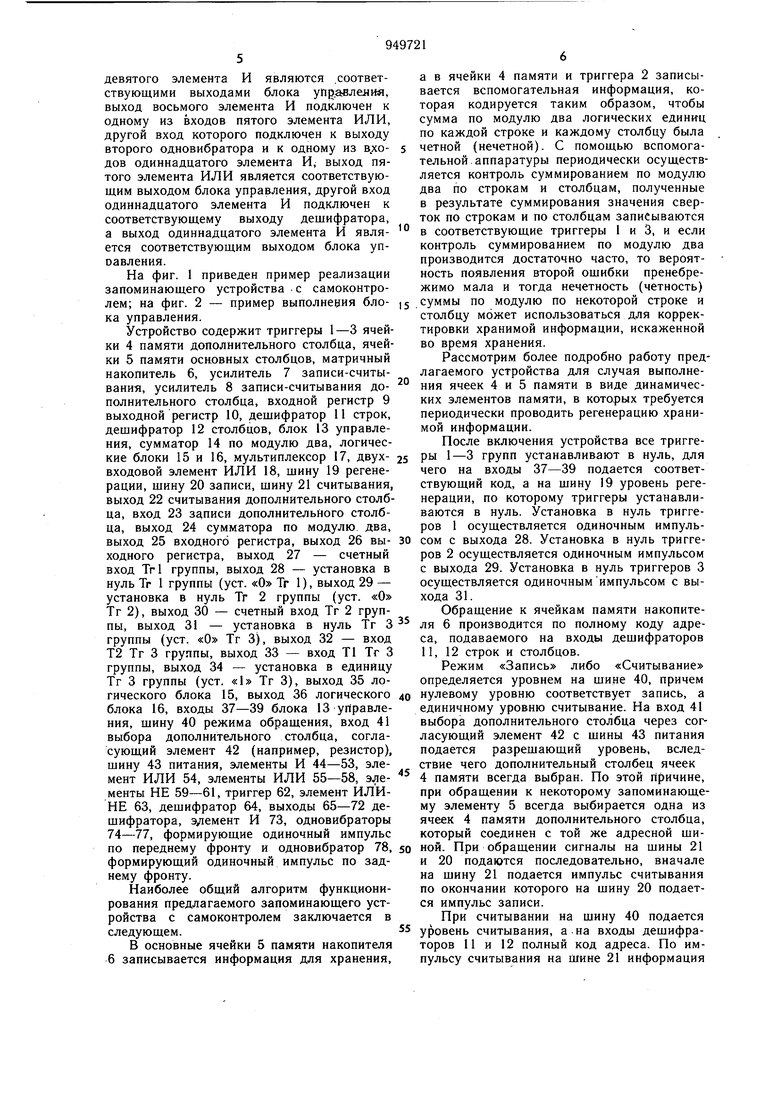

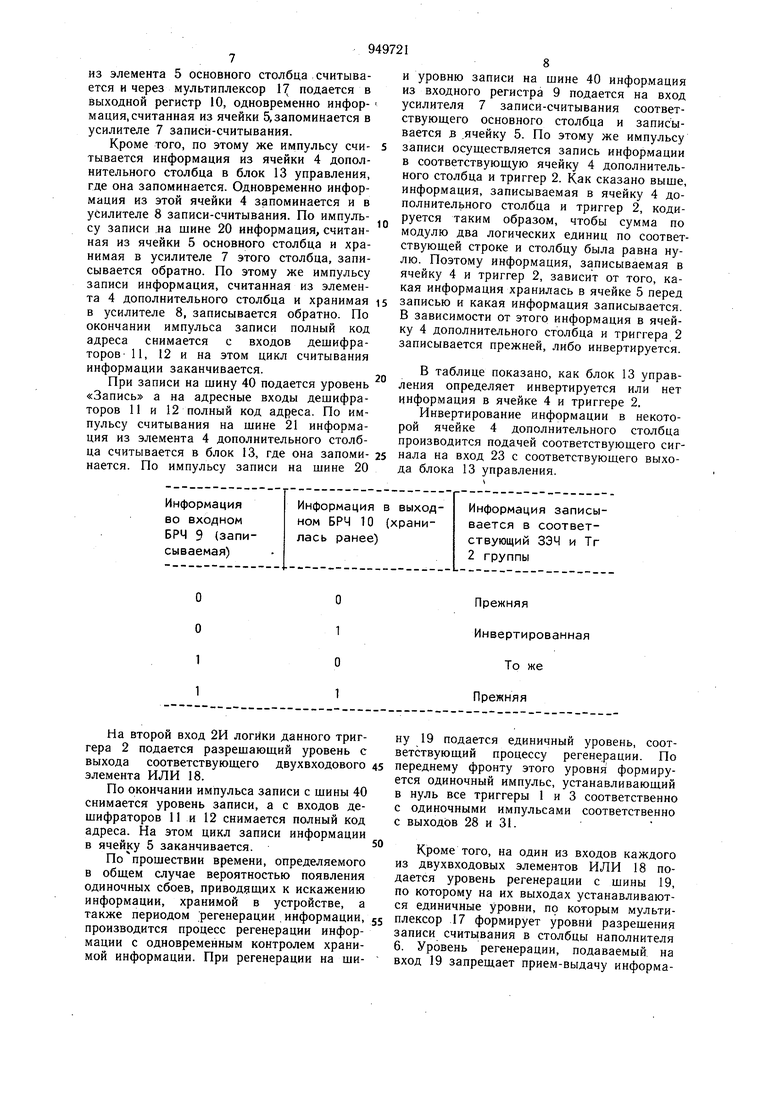

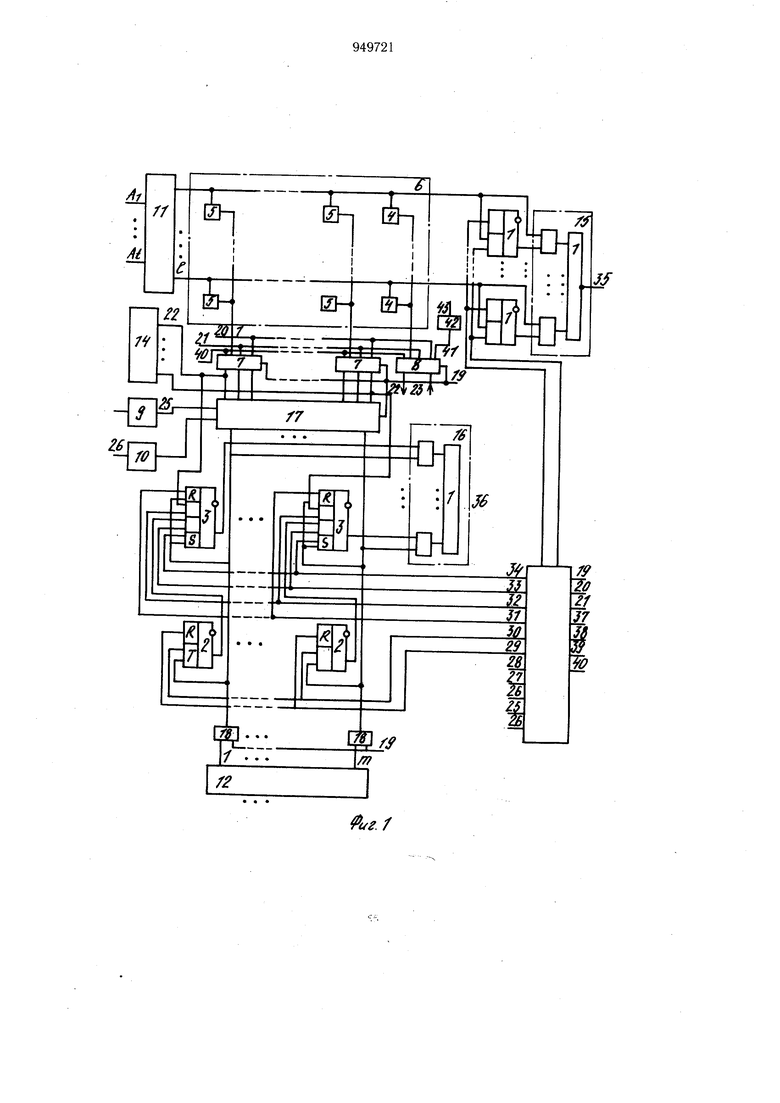

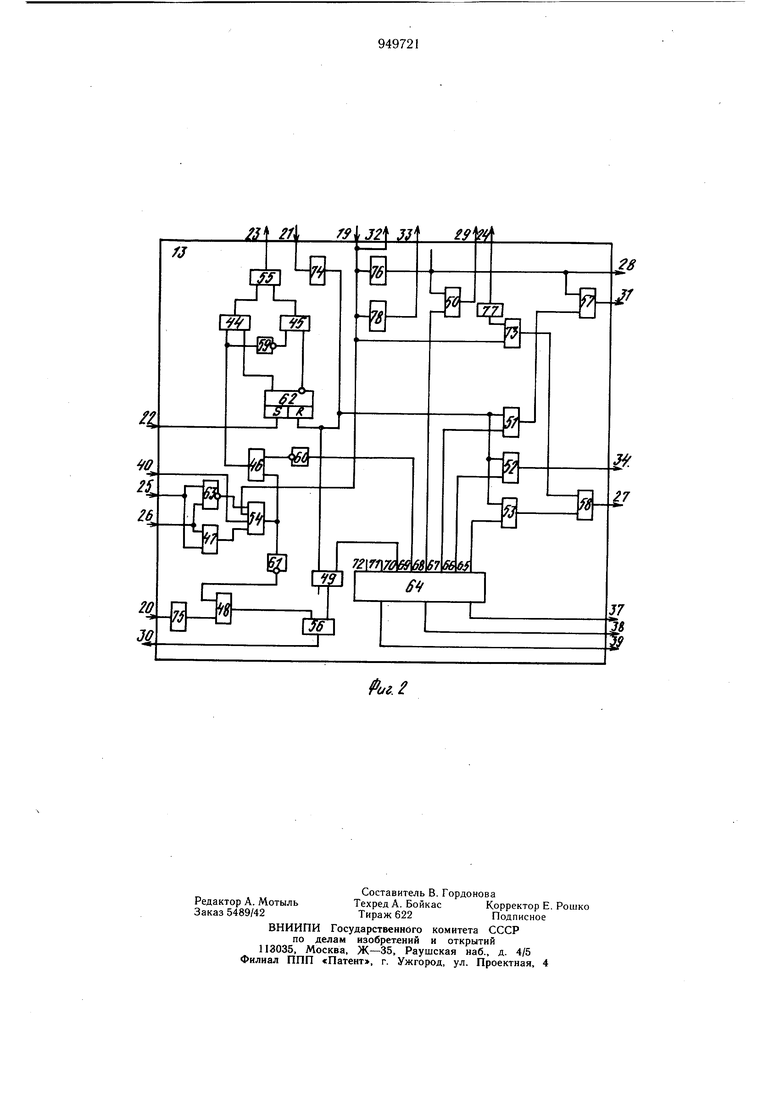

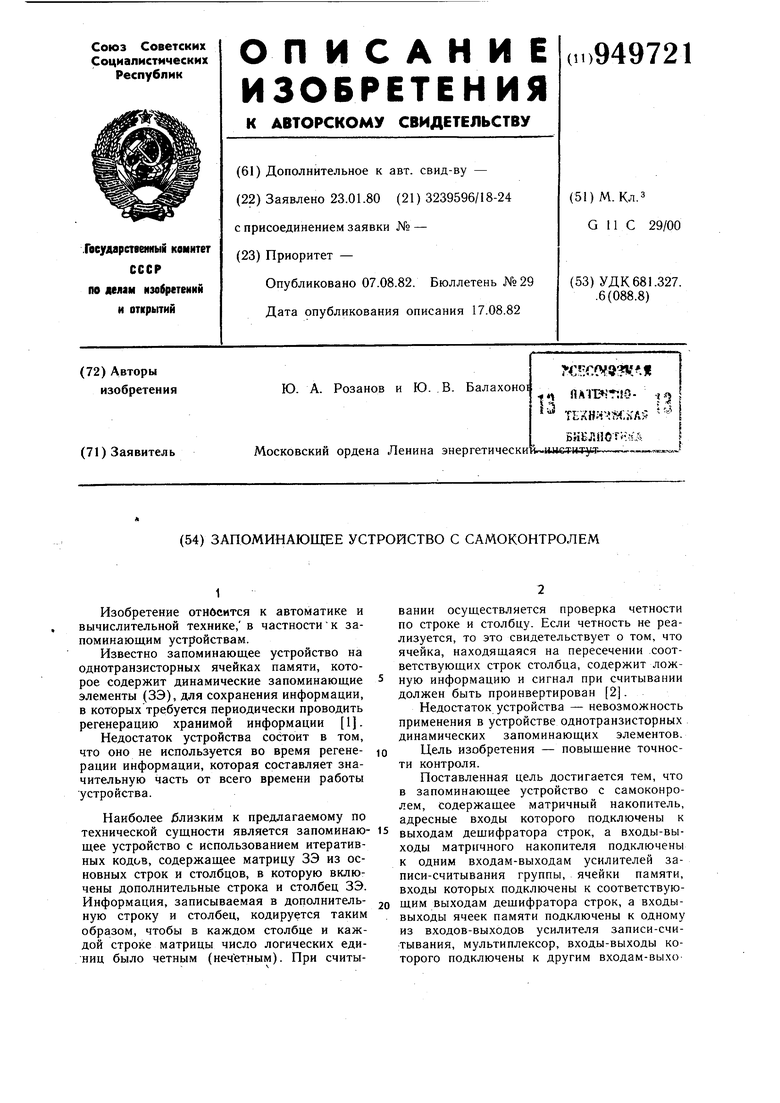

Поставленная цель достигается тем, что в запоминающее устройство с самоконролем, содержащее матричный накопитель, адресные входы которого подключены к выходам дешифратора строк, а входы-выходы матричного накопителя подключены к одним входам-выходам усилителей записи-считывания группы, ячейки памяти, входы которых подключены к соответствующим выходам дешифратора строк, а входывыходы ячеек памяти подключены к одному из входов-выходов усилителя записи-считывания, мультиплексор, входы-выходы которого подключены к другим входам-выхо дам усилителей записи-считывания группы, вход мультиплексора подключен к выходу. входного регистра, вход которого является входом устройства, выход мультиплексор ра подключен к входу выходного регистра, выход которого является выходом устройства, -один управляющий вход мультиплексора подключен к управляющему входу усилителей записи-воспроизведения и является управляющим входом устройства, сумматор по модулю два, входы которого подключены к входам-выходам мультиплексора, дешифратор столбцов, дополнительно введены группы триггеров, логические блоки, блок управления и элементы ИЛИ, первые входы которых подключены к выходам дешифратора столбцов, а вторые входы элементов ИЛИ объединены и являются вторым управляющим входом устройства, выходы элементов ИЛИ подключены к другим управляющим входам мультиплексора, одни входы триггеров первой группы подключены к соответствующим выходам дещифратора строк, другие входы триггеров первой группы подключены к соответствующим выходам блока управления, выходы триггеров первой группы подключены к одним из входов первого логического блока, вторые входы которых подключены к соответствующим выходам дешифратора строк, выход первого логического блока является первым управляющим выходом устройства, одни входы триггеров второй группы подключены к выходам соответствующих элементов ИЛИ, другие входы триггеров второй группы подключены к соответствующим выходам блока управления, а выходы триггеров второй группы подключены к первым входам триггеров третьей группы, вторые входы которых подключены к соответствующим входам сумматора rio модулю два, третьи входы триггеров третьей группы подключены к выходам соответствующих элементов ИЛИ, другие входы триггеров третьей группы подключены к соответствующим выходам блока управления, а выходы триггеров третьей группы подключены к одним вхо-, дам второго логического блока, другие входы которого подключены к. выходам соответствующих элементов ИЛИ, выход второго логического блока является вторым управляющим выходом устройства. Кроме того, блок управления содержит элементы И, элементы ИЛИ, элементы НЕ, одновибраторы, элемент ИЛИ-НЕ, триггер и дешифратор, входы которого являются соответствующими входами блока управления, один из входов первого элемента И подключен к одному из выходов триггера, второй выход которого подключен к одном-у из входов второго элемента И, другой вход первого элемента И подключен к выходу третьего элемента Инк входу первого элемента НЕ, выход которого подключен -к другому входу второго элемента И, выход первого элемента И подключен к одному из входов первого элемента ИЛИ, другой вход которого подключен к выходу второго элемента И, выход первого элемента ИЛИ является соответствующим выходом блока управления, один вход третьего элемента И подключен к выходу второго элемента НЕ, вход которого подключен к соответствующему выходу дешифратора, другой вход третьего элемента И подключен к входу третьего элемента НЕ и к выходу второго элемента ИЛИ, первый вход которого подключен к выходу четвертого элемента И, выход третьего элеменTia НЕ подключен к одному входу пятого элемента И, выход которого подключен к одному из входов третьего элемента ИЛИ, другой вход пятого элемента И подключен к выходу первого одновибратора, вход которого является соответствующим входом блока управления, одни входы четвертого элемента И и элемента ИЛИ-НЕ объединены и являются соответствующими входом блока управления, другие входы четвертого элемента И и элемента ИЛИ-НЕ объединены и являются соответствующим входом блока управления, другие входы четвертого элемента И и элемента ИЛИ-НЕ объединены и являются соответствующим входом блока управлений, выход элемента ИЛИ-НЕ подключен к второму входу втордро элемента ИЛИ, третий вход которого является соответствующим входом блока управления, четвертый вход второго элемента ИЛИ подключен к входам второго и третьего одновибраторов, к одному из входов шестого элемента И и является соответствующим входом блока управления, выходы второго и третьего одновибраторов являются соответствующими выходами блока управления, другой вход шестого элемента И подключен к выходу четвертого одновибратора, вход которого является соответствующим входом блока управления, один из входов триггера является соответствующим входом блока управления, другой вход триггера подключен к одним входам седьмого, восьмого, девятого и десятого элементов И, к выходу пятого одновибратора, вход которого является соответствующим входом блока управления, другие входы седьмого, восьмого, девятого и Десятого элементов И подключены к соответствующим выходам дешифратора, выход седьмого элемента И подключен к другому входу третьего элемента ИЛИ, выход которого является соответствующим выходом блока управления, выход шестого элемента И подключен к одному из входов четвертого элемента ИЛИ, другой вход которого подключен к выходу десятого элемента И, выход четвертого элемента ИЛИ и девятого элемента И являются .соответствующими выходами блока уП).авления, выход восьмого элемента И подключен к одному из входов пятого элемента ИЛИ, другой вход которого подключен к выходу второго одновибратора и к одному из в.ходов одиннадцатого элемента И, выход пятого элемента ИЛИ является соответствующим выходом блока управления, другой вход одиннадцатого элемента И подключен к соответствующему выходу дещифратора, а выход одиннадцатого элемента И является соответствующим выходом блока упоавления. На фиг. 1 приведен пример реализации запоминающего устройства с самоконтролем; на фиг. 2 - пример выполнения блока управления. Устройство содержит триггеры 1-3 ячейки 4 памяти дополнительного столбца, ячейки 5 памяти основных столбцов, матричный накопитель 6, усилитель 7 записи-считывания, усилитель 8 записи-считывания дополнительного столбца, входной регистр 9 выходной регистр 10, дещифратор 11 строк, дешифратор 12 столбцов, блок 13 управления, сумматор 14 по модулю два, логические блоки 15 и 16, мультиплексор 17, двухвходовой элемент ИЛИ 18, шину 19 регенерации, шину 20 записи, шину 21 считывания, выход 22 считывания дополнительного столбца, вход 23 записи дополнительного столбца, выход 24 сумматора по модулю, два, выход 25 входного регистра, выход 26 выходного регистра, выход 27 - счетный вход Тг 1 группы, выход 28 - установка в нуль Тг 1 группы (уст. «О Тг 1), выход 29 - установка в нуль Тг 2 группы (уст. «О Тг 2), выход 30 - счетный вход Тг 2 группы, выход 31 - установка в нуль Тг 3 группы (уст. «О Тг 3), выход 32 - вход Т2 Тг 3 группы, выход 33 - вход Т1 Тг 3 группы, выход 34 - установка в единицу Тг 3 группы (уст. «1 Тг 3), выход 35 логического блока 15, выход 36 логического блока 16, входы 37-39 блока 13 управления, шину 40 режима обращения, вход 41 выбора дополнительного столбца, согласующий элемент 42 (например, резистор), шину 43 питания, элементы И 44-53, элемент ИЛИ 54, элементы ИЛИ 55-58, элементы НЕ 59-61, триггер 62, элемент ИЛИНЕ 63, дешифратор 64, выходы 65-72 дешифратора, э;1емент И 73, одновибраторы 74-77, формирующие одиночный импульс по переднему фронту и одновибратор 78, формирующий одиночный импульс по заднему фронту. Наиболее общий алгоритм функционирования предлагаемого запоминающего устройства с самоконтролем заключается в следующем. В основные ячейки 5 памяти накопителя 6 записывается информация для хранения. а в ячейки 4 памяти и триггера 2 записывается вспомогательная информация, которая кодируется таким образом, чтобы сумма по модулю два логических едини ц по каждой строке и каждому столбцу была четной (нечетной). С помощью вспомогательной, аппаратуры периодически осуществляется контроль суммированием по модулю два по строкам и столбцам, полученные в результате суммирования значения сверток по строкам и по столбцам записываются в соответствующие триггеры 1 и 3, и если контроль суммированием по модулю два производится достаточно часто, то вероятность появления второй ощибки пренебрежимо мала и тогда нечетность (четность) суммы по модулю по некоторой строке и столбцу может использоваться для корректировки хранимой информации, искаженной во время хранения. Рассмотрим более подробно работу предлагаемого устройства для случая выполнения ячеек 4 и 5 памяти в виде динамических элементов памяти, в которых требуется периодически проводить регенерацию хранимой информации. После включения устройства все триггеры 1-3 групп устанавливают в нуль, для чего на входы 37-39 подается соответствующий код, а на щину 19 уровень регенерации, по которому триггеры устанавливаются в нуль. Установка в нуль триггеров 1 осуществляется одиночным импульсом с выхода 28. Установка в нуль триггеров 2 осуществляется одиночным импульсом с выхода 29. Установка в нуль триггеров 3 осуществляется одиночнымимпульсом с выхода 31. Обращение к ячейкам памяти накопителя 6 производится по полному коду адреса, подаваемого на входы дещифраторов 11, 12 строк и столбцов. Режим «Запись либо «Считывание определяется уровнем на шине 40, причем нулевому уровню соответствует запись, а единичному уровню считывание. На вход 41 выбора дополнительного столбца через СОР ласующий элемент 42 с щины 43 питания подается разрешающий уровень, вследствие чего дополнительный столбец ячеек 4 памяти всегда выбран. По этой причине, при обращении к некоторому запоминающему элементу 5 всегда выбирается одна из ячеек 4 памяти дополнительного столбца, который соединен с той же адресной щиной. При обращении сигналы на шины 21 и 20 подаются последовательно, вначале на шину 21 подается импульс считывания по окончании которого на шину 20 подается импульс записи. При считывании на щину 40 подается уровень считывания, а на входы дешифраторов 11 и 12 полный код адреса. По импульсу считывания на Щине 21 информация из элемента 5 основного столбца считывается и через мультиплексор l подается в выходной регистр 10, одновременно информация,считанная из ячейки 5,запоминается в усилителе 7 записи-считывания. Кроме того, по этому же импульсу считывается информация из ячейки 4 дополнительного столбца в блок 13 управления, где она запоминается. Одновременно информация из этой ячейки 4 запоминается и в уСилителе 8 записи-считывания. По импульсу записи на шине 20 информация, считанная из ячейки 5 основного столбца и хранимая в усилителе 7 этого столбца, записывается обратно. По этому же импульсу записи информация, считанная из элемента 4 дополнительного столбца и хранимая в усилителе 8, записывается обратно. По окончаний импульса записи полный код адреса снимается с входов дешифраторов 11, 12 и на этом цикл считывания информации заканчивается. При записи на шину 40 подается уровень «Запись а на адресные входы дешифраторов 11 и 12 полный код адреса. По импульсу считывания на шине 21 информация из элемента 4 дополнительного столбца считывается в блок 13, где она запоминается. По импульсу записи на шине 20 На второй вход 2И логики данного триггера 2 подается разрешающий уровень с выхода соответствующего двухвходового элемента ИЛИ 18. По окончании импульса записи с щины 40 снимается уровень записи, а с входов дешифраторов 11 и 12 снимается полный код адреса. На этом цикл записи информации в ячейку 5 заканчивается. По прошествии времени, определяемого в общем случае вероятностью появления одиночных сбоев, приводящих к искажению информации, хранимой в устройстве, а также периодом регенерации информации, производится процесс регенерации информации с одновременным контролем хранимой информации. При регенерации на шии уровню записи на шине 40 информация из входного регистра 9 подается на вход усилителя 7 записи-считывания соответствующего основного столбца и запись вается в .ячейку 5. По этому же импульсу записи осуществляется запись информации в соответствующую ячейку 4 дополнительного столбца и триггер 2. Как сказано выще, информация, записываемая в ячейку 4 дополнительного столбца и триггер 2, кодируется таким образом, чтобы сумма по модулю два логических единиц по соответ ствующей строке и столбцу была равна нулю. Поэтому информация, записываемая в ячейку 4 и триггер 2, зависит от того, какая информация хранилась в ячейке 5 перед записью и какая информация записывается, В зависимости от этого информация в ячейку 4 дополнительного столбца и триггера 2 записывается прежней, либо инвертируется. В таблице показано, как блок 13 управления определяет инвертируется или нет информация в ячейке 4 и триггере 2. Инвертирование информации в некоторой ячейке 4 дополнительного столбца производится подачей соответствующего сигнала на вход 23 с соответствующего выхода блока 13 управления. ну 19 подается единичный уровень, соответствующий процессу регенерации. По переднему фронту этого уровня формируется одиночный импульс, устанавливающий в нуль все триггеры 1 и 3 соответственно с одиночными импульсами соответственно с выходов 28 и 31. Кроме того, на один из входов каждого из двухвходовых элементов ИЛИ 18 подается уровень регенерации с шины 19, по которому на их выходах устанавливаются единичные уровни, по которым мультиплексор 17 формирует уровни разрещения записи считывания в столбцы наполнителя 6. Уровень регенерации, подаваемый на вход 19 запрещает прием-выдачу информации через мультиплексор 17. После подачи уровня регенерации на шину 19 и формирования указанных сигналов на входы дешифратора 11 строк подается комбинация части полного кода адреса, по которой выбирается соответствующая строка, По импульсу считывания информация считывается из всех ячеек 5 и соответствующей ячейки 4 данной строки. Информация, считанная из строки с выхода каждого усилителя 7, подается на один из входов 2И логики счетного входа Т2 соответствующего триггера 3, а на другой вход 2И логики счетного входа Т2 подается единичный уровень с выхода 32 блока 13 управления. Информация, считанная из ячеек 5 и 4 с выходов усилителей 7 и 8, подается на входы сумматора 14 по модулю два, а кроме того запоминается в усилителях записи считывания. Значение суммы по модулю два логических единиц по строке, с выхода 24 сумматора 14 по модулю два подается на соответствующий вход блока 13. Если сумма по модулю два логических единицпо строке равна единице, то на выходе24 сумматора 14 формируется импульс,по переднему фронту которого в блоке13 производится формирование одиночного импульса, поступающего с выхода 27 на один из входов 2И логики счетного входа каждого триггера и данный импульс устанавливает в единицу только триггер, соединенный с выбранной строкой, потому что только у этого триггера на втором входе 2И логики имеется разрещающий уровень. Если сумма по модулю два логических единиц по строке равна нулю, то на выходе 24 сумматора 14 по модулю два не формирует ся импульс, триггер 1 остается в нулевом состоянии. По импульсу «Запись на шине 20 производится запись информации, считанной из ячеек 5 и 4 данной строки и хранимой в схемах регенерации усилителей записи считывания обратно в ячейки 5 и 4. J По окончании импульса записи комбинация части полного кода адреса, подаваемая на входы дещифратора 11, снимается и на этом цикл регенерации информации в данной строке закончен. После окончания описанного цикла регенерации на входы дещифратора строк подается другая комбинация полного адреса, по которой выбирается следующая строка и т. д. Описанная последовательность регенерации информации в строках повторяется до тех пор, пока информация во всех строках не будет регенерирована, после чего уровень регенерации снимается.с шины 19. По заднему фронту .уровня регенерации на выходе 33 формируется одиночный импульс, который подается на один из входов 2И логики счетного входа Т1 каждого из триггеров 3, другой же вход 2И логики счетного входа TI данного триггера 3 соединен с единичным выходом соответствующего триггера 2. Поэтому по данному одиночному импульсу осуществляется занесение информации из триггера 2 в соответствующий ему триггер 3 по входу Т1. На этом процесс регенерации информации и контроля хранимой информации заканчивается. По окончании его в триггере 1 записаны злачения сумм по модулю два логических единиц соответствующих строк, а в триггерах 3 записаны значения, сумм по модулю два логических единиц соответствующих столбцов, Выход 35 логического блока 15 и выход 36 логического блока 16 соединены с соответствующими входами системы, в которую включено предлагаемое устройство, и при обращении к некоторой ячейке 5 значение сумм по модулю два логических единиц по выбранной строке и столбцу выдаются с указанных выходов в систему и используются для коррекции искаженной информации в ЗЭ устройства, а также могут быть использованы для упрощения, процедур контроля и диагностики устройства, одновременно может быть уменьщена и аппаратурная избыточность систем, в которые входит устройство, например, использованием для груп ы предлагаемых устройств одних и тех же блоков контроля и диагностики. Для улучщения контрольно-диагностических и эксплуатационных свойств предлагаемого устройства, в нем предусмотрены следующие дополнительные режимы работы, которые осуществляются подачей соответствующего кода на входы 19 и 37-40 блока 13 управления и последующего обращения к соответствующей ячейке 5. 1. Инвертирование информации в соответствующем элементе 4 дополнительного столбца. 2. Инвертирование информации в соответствующем триггере 1. 3.Инвертирование информации в соответствующем триггере 2. 4.Установка в единицу соответствующего триггера 3. 5.Установка в нуль соответствующего триггера 3. 6.Установка в нуль триггера 3 при включении. Для исчерпывающего описания всех особенностей предлагаемого устройства рассмотрим дополнительно организацию и работу БУ 13. Блок 13 управления работает при следующих условиях: при подаче соответствующего кода на входы 37-39 выбирается соответствующий выход дещифратора 64, на котором формируется единичный уровень; код для осуществления операций установки определенных элементов 4, триггеров 1-3 в необходимые состояния подается на входы дешифратора 64 перед импульсом считывания и снимается с этих входов по окончании импульса записи следующего за данным импульсом считывания; одновибраторы формируют импульсы с амплитудой и длительностью, необходимой для установки в соответствующие состояния триггеров 1-3; на выходе усилителя записи-считывания столбца формируется одиночный импульс при считывании информации из некоторого запоминающего элемента столбца, если в данном элементе записана логическая единица, если же записан нуль, то одиночный импульс не формируется.

Предлагаемое устройство с самоконтролем позволяет применять любые типы запоминающих элементов, в частности возможно применение элементов памяти. Для таких устройств использование изобретения повыщает точность контроля. Кроме того, эффективно используется присущая таким устройствам временная избыточность, необходимая для осуществления процесса регенерации информации.

Формула изобретения

первой группы подключены к соответствующим выходам блока управления, выходы триггеров первой группы подключены к одним из входов первого логического блока, вторые входы которых подключены к соответствующим выходам дешифратора строк, выход первого логического блока является первым управляющим выходом устройства, одни входы триггеров второй группы подключены к выходам соответствующих элементов ИЛИ, другие входы триггеров второй группы подключены к соответствующим выходам блока управления, а выходы триггеров второй группы подключены к первым входам триггеров третьей группы, вторые входы которых подключены к соответствующим входам сумматора по модулю два, третьи входы триггеров третьей группы подключены к выходам соответствующих элементов ИЛИ, другие входы триггеров третьей группы подключены к соответствующим выходам блока управления, а выходы триггеров третьей группы подключены к одним входам второго логического блока, другие входы которого подключены к выходам соответствующих элементов ИЛИ, выход второго логического блока является вторым

управляющим выходом устройства.

0 соответствующими входами блока управления, один из входов первого элемента И подключен к одному из выходов триггера, второй выход которого подключен к одному из входов второго элемента И, другой вход первого элемента И подключен к выходу третьего элемента Инк входу первого элемента НЕ, выход которого подключен к другому входу второго элемента И, выход первого элемента И подключен к одному из входов первого элемента ИЛИ, другой

0 вход которого подключен к выходу второго элемента И, выход первого элемента ИЛИ является соответствующим выходом блока управления, один вход третьего элемента И подключен к выходу второго элемента НЕ, вход которого подключен к соответствующему выходу дещифратора, другой вход третьего элемента И подключен к входу третьего элемента НЕ и к выходу второго элемента ИЛИ, первый вход которого подключён к выходу четвертого элемента И,

0 выход третьего элемента НЕ подключен к одному входу пятого элемента И, выход которого подключен к одному из входов третьего элемента ИЛИ, другой вход пятого элемента И подключен к выходу первого одновибратора, вход которого является соответствующим входом блока управлений, одни входы четвертого элемента И и элемента ИЛИ-НЕ объединены и являются соответствующим входом блока управления, другие входы четвертого элемента И и элемента ИЛИ-НЕ объединены и являются соответствующим входом блкока управления, выход элемента ИЛИ-НЕ подключен к второму входу второго элемента ИЛИ, третий вход которого является соответствующим входом блока управления, четвертый вход второго элемента ИЛИ подключен к входам второго и третьего одновибраторов, к одному из входов щестого элемента И и является соответствующим входом блока Ю управления, выходы второго и третьего одновибраторов являются соответствующими выходами блока управления, другой вход щестого элемента И подключен к выходу четвертого одновибратора, вход которого является соответствующим входом блока управления, один из входов триггера является соответствующим входом блока управления, другой вход триггера подключен к одним входам седьмого, восьмого, девятого и девятого элементов И, к вы- 2 ходу пятого одновибратора, вход которого является соответствующим входом блока управления. Другие входы седьмого, восьмого, девятого и десятого элементов И подключены к соответствующим выходам дещифратора, выход седьмого элемента И подключен к другому входу третьего элемента ИЛИ, выход которого является соответствующим выходом блока управления. выход шестого элемента И подключен к одному из входов четвертого элемента ИЛИ, другой вход которого подключен к выходу десятого элемента И, выход четвертого элемента ИЛИ и девятого элемента И являются соответствующими выходами блока управления, выход восьмого элемента И подключен к одному из входов пятого элемента ИЛИ, другой вход которого подключен к выходу второго одновибратора и к одному из входов одиннадцатого элемента и, выход пятого элемента ИЛИ являётся соответствующим выходом блока управления, другой вход одиннадцатого элемента И подключен к соответствующему выходу дещифратора, а выход одиннадцатого элемента И является соответствующим выходом блока управления. Источники информации, принятые во внимание при экспертизе 1. Гафаров П. М. и др. Запоминающее устройство емкостью 4096 бит на однотранзисторных ячейках памяти. - «Электронная промыщленность, 1978, вып. 8, с. 5-11. 2. Борисов В. С. и др. Избыточность в полупроводниковых запоминающих устройствах. Сборник. «Микроэлектроника и полупроводниковые приборы. Под ред. А. А. Васенкова и Я. А. Федотова. М., «Сов. радио, 1979, с. 217-219 (прототип) .

Г9

U2.f

Авторы

Даты

1982-08-07—Публикация

1981-01-23—Подача