f

Изобретение относится к контрольно- измерительной технике и может быть использовано для контроля активного сопротивления электрорадиоэлемеитов, электрооборудования и электрических цепей, в частности для контроля сопротивления обмоток электрических машин и аппаратов.

Цель .изобретения - повышение достоверности контроля путем улучшения помехоустойчивости устройства.

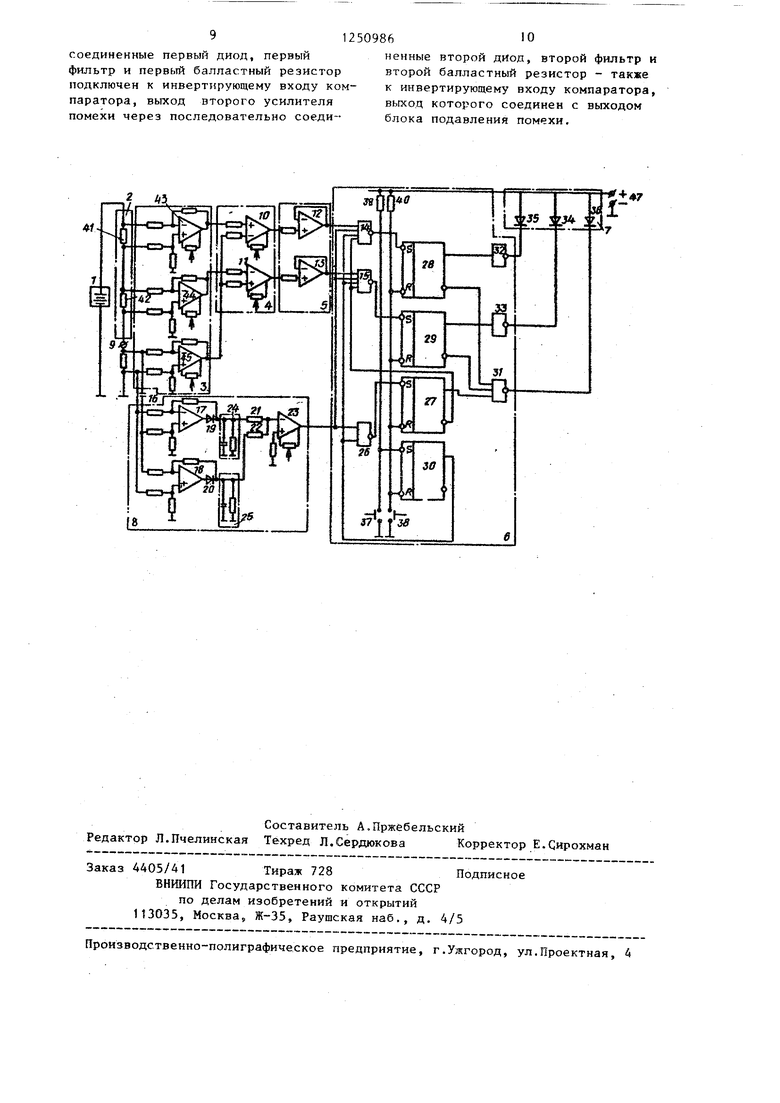

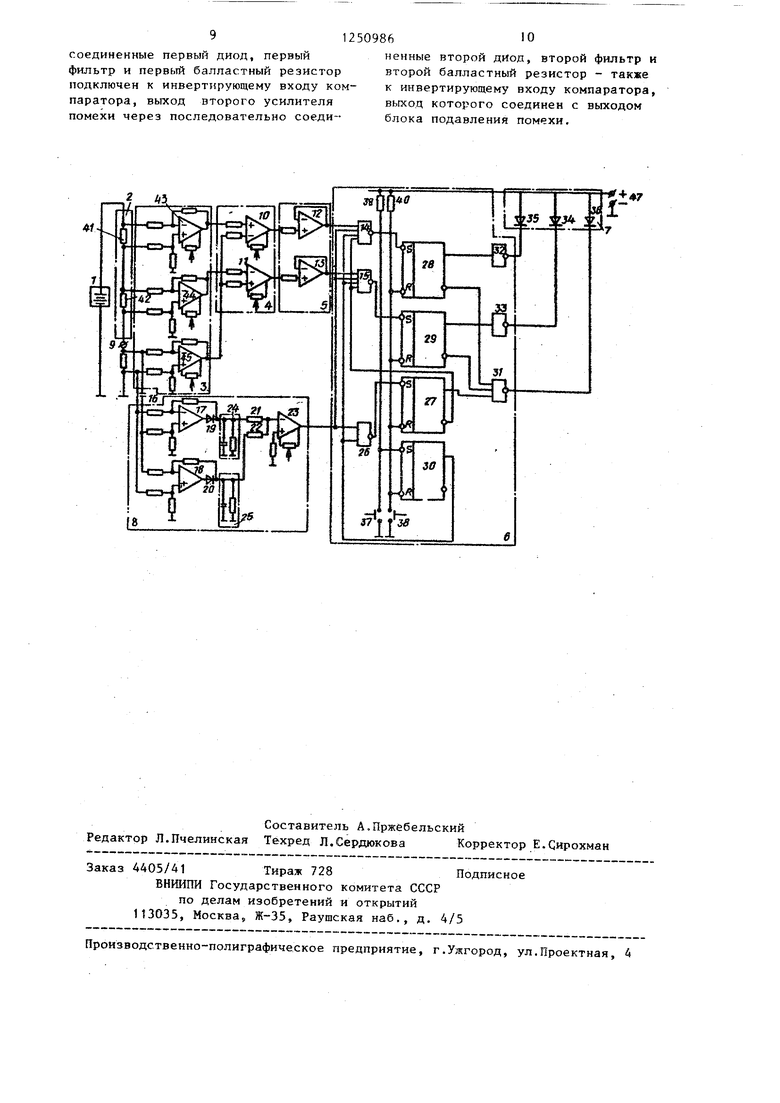

На чертеже приведена функциональная схема устройства.

to

Устройство содержит первый источник 1 постоянного напряжения, измерительную схему 2, блок 3 дифференциальных усилителей, двухпороговый компаратор 4, буферный блок 5, логический блок 6, индикатор 7, блок 8 подавления помехи, клемму 9 для подключения контролируемого сопротивления, первый 10 и второй 11 пороговые компараторы, первый 12 и вто-т рой 13 буферные повторители, первый 14 и второй 15 элементы И-НЕ, конденсатор 16, первый 17 и второй 18 усилители помехи, первый 19 и второй 20 диоды, первый 21 и второй 22 балластные резисторы, компаратор 23, первый 24 и второй 25 фильтры, третий элемент 26 И-НЕ, первый 27, второй 28, третий 29 и четвертый 30 RS-триггеры, четвертый элемент 31 И-НЕ, первый 32 и втр- рой 33 инверторы, первый 34, второй 35 и третий 36 светодиоды, кноп- ку 37 Пуск, кнопку 38 Исходное положение, первый 39 и второй 40 резисторы питания, первый 41 и второй 42 эталонные резисторы, первый 43, второй 44 и третий 45 дифференциальные усилители, контролируемое сопротивление 46, второй источник 47 постоянного напряжения и шину 48 Плюс логического блока, причем первый, второй, третий и четвертый выходы измерительной схемы 2 подключены соответственно к первому, второму, третьему и четвертому входам блока 3 дифференциальных усилителей, пятый вход которого присоединен к клеьше 9 для подключения контролируемого сопротивления, а шестой вход - к общей шине, первый, второй и третий выходы блока 3 диффереициаль ных усилителей подключены соответственно к первому, второму и третьему входам двухпороts

20

12509862

гового компаратора 4, первый и второй выходы которого подключены соответственно к первому и второму входам буферного блока 5, первый и второй выходы которого подключены соответственно к первому и второму входам логического блока 6, третий вход которого подключен к первому входу блока В подавления помехи, первый вход которого присоединен к общей шине, а второй через конденсатор 16 - к клемме 9 для подключения контролируемого сопротивления, первый, второй и третий выходы логического блока 6 подключены соответственно к первому, второму и третьему входам индикатора 7, а шина 48 П.пюс - к положительному полюсу второго источника 47 постоянного напряжения.

Логический блок содержит первый 14, второй 15, третий 26 и четвертый 31 элементы И-НЕ, первый 27, второй 28, третий 29 и четвертый 30. RS-триггеры, первьсй 32 и второй 33 инверторы, кнопку Пуск, кнопку Исходное положение, а также первый 39 и второй 40 резисторы питания, причем первые входы первого 14 и второго 15 элементов И-НЕ образуют соответственно первьй и второй входы логического блока 6, вторые входы соединены между собой и с первым входом третьего 26 элемента И-НЕ, который образует третий вход логи35 ческого блока 6. Третьи входы первого 14 и второго 15 элементов И-НЕ соединены между собой и подключены к второму входу третьего 26 элемента И-НЕ и прямому вьтходу четвертого

О RS-триггера 30, Четвертые входы первого 14 и второго 15 элементов И-НЕ соединены между собой и подключены к инверсному выходу первого RS-триггера 27, Выход первого 14 элемента

5 И-НЕ подключен к S-входу второго RS-триггера 28, выход второго 15 элемента И-НЕ - к S-входу третьего

25

30

RS-триггера 29, а выход четвертого 31 элемента И-НЕ образует третий

50 логического блока 6, Первые выводы первого 39 и второго 40 резисторов питания соединены между собой н подключены к шине 48 Плюс. Второй вывод первого резистора 39 пита55 ния подключен к S-входу четвертого RS-триггера и через кнопку Пуск - к общей шине, R-входы первого 27, второго 28, третьего 29 и четвертоRS-триггера 29, а выход четвертого 31 элемента И-НЕ образует третий

50 логического блока 6, Первые выводы первого 39 и второго 40 резисторов питания соединены между собой н подключены к шине 48 Плюс. Второй вывод первого резистора 39 пита55 ния подключен к S-входу четвертого RS-триггера и через кнопку Пуск - к общей шине, R-входы первого 27, второго 28, третьего 29 и четвертого 30 RS-триггеров соединены в одну точку, которая подключена к второму выводу второго резистора 40 питания и через кнопку Исходное положение к общей шине. Прямые выходы второ- го 28 и третьего 29 RS-триггеров подключены к входам первого 32 и второго 33 инверторов, выходы которых образуют соответственно первый и второй выходы логического блока 6, инверсные выходы второго 29 и третьего 30 RS-триггеров подключены соответственно к первому и второму входам четвертого элемента И-НЕ 31, третий вход которого присоединен к пря- мому выходу первого RS-триггера 27.

Блок 8 подавления помехи содержит первый 17 и второй 18 усилители помехи, первый 19 и второй 20 диоды, первь 21 и второй 22 балластные резисторы, компаратор 23, первый 24 и второй 25 фильтры, причем инвертирующий вход первого 17 усилителя помехи соединен с неинвертирующим

I

входом второго 18 усилителя помехи в общую точку, которая образует первый вход блока 8 подавления помехи, инвертируюя(ий вход второго 18 усилителя помехи соединен с неинвертирующим входом первого 17 усилителя помехи в общую точку, которая образует второй вход блока 8 подавления помехи, выход первого 17 усилителя помехи через диод, первый фильтр 24 и первый 21 балласт ныА резистор подключен к инвертирующему входу компаратора 23, выход второго 18 усилителя помехи через второй диод 20, второй фильтр 25 и второй 22 балластный резистор - так- же к инвертирующему входу компаратора 23, выход которого образует выход блока 6 подавления помехи.

Блок 3 дифференциальных усилителей состоит из первого 43, второго 44 и третьего 45 дифференциальных усили- телей,инвертирующие входы которых образуют соответственно первый, третий и пятый входы блока 3 дифференциальных усилителей, второй, четвер- тый и шестой входы - соответственно второй, четвертый и шестой входы блока 3 дифференциальных усилителей, а выходы - соответственно первый, второй и третий выходы блока 3 диффере циальных усилителей.

Контролируемое сопротивление 46 подключается между клеммой 9 для подключения контролируемого сопротивления и общей шиной.

Устройство функционирует следующим образом.

Подключается источник 1 питания и нажатием кнопки 38 Исходное положение :ia np.iMLnc выходах RS-триггеров 27-30 устанавливается нулево сигнал. При этом четвертый RS-триг- гер 30 блокирует первый 14, второй 1 и третий 26 элементы И-НЕ, на выхода которых устанавливаются сигналы 1. Сигналы 1 устанавливаются также на выходах инвертеров 32, 33 и четвертого элемента И-НЕ 31, в результате чего отсутствуют сигналы на индикаторах 34 - 36. Предположим, что до момента нажатия кнопки 37 Пуск на зажимах контролируемого сопротивления 46 обнаруживается сигнал помехи в виде переменных напряжений или в виде импульсов любой полярности, обусловленных наводками и внутренними переходными процессами. Тогда благодаря наличию буферных повторителей 12 и 13 напряжений (предназначенных для временного сдвига задержки сигналов) прохождение сигнала от зажимов контролируемого сопротивления 46 до входов элементов И-НЕ 14, 15 и 26 занимает больше времени со стороны дифференциального усилите- - ля 45, чем со стороны усилителей 17 и 18 помехи. При этом усилители 17 и 18 помехи усиливают сигнал помехи, причем первый усилитель 17 помехи реагирует на отрицательные перепады (всплеск) напряжения помехи, а второй усилитель t8 помехи - на положительные перепады (всплески) напряжения помехи, которые детектируются диодами 19 и 20 и в положительной полярности подаются через балластные сопротивления 21 и 22 к инвертирующему входу компаратора 23, который выдает на выходе сигнал О. В результате блокируются первый, второй и третий элементы И- НЕ 14, 15 и 26 и процесс контроля приостанавливается до тех пор, пока на зажимах контролируемого сопротивления 46 не исчезнут или затухнут помехи. После нажатия кнопки Пуск происходит разблокировка первого, второго и третьего элементов И-НЕ 14, 15 и 26 со стороны прямого выхода триггера 30, но блокировка этих же элементов со стороны компаратора 23

5

продолжается. Как только на зажимак контролируемого сопротивления 46 исчезнут сигналы помехи, на входах усилителей 17 и 18 помехи и на инвертирующем входе компаратора 23 установится нулевое напряжение. При этом компаратор 23, выход которого настроен на выдачу при нулевом напряжении на инвертирующем входе сигнала 1, разблокировывает элемен- ты И-НЕ 1А, t5 и 26.

Предположим, что контролируемое сопротивление 46 находится в пределах нормы. Тогда проходящий через сопротивления 41, 42 и 46 ток вызывает падение напряжения на зажимах сопротивления 46 больше, чем на зажимах сопротивления 42, и меньше, чем на зажимах сопротивления 41, При этом на выходах пороговых компара- торов 10 и 11 устанавливается сигнал О, который подается через буферные повторители 12 и 13, соответственно к первым входам элементов И- НЕ 14 и 15, на выходах которых со- храняются сигналы 1 а на выходе. третьего элемента И-НЕ 26 сигнал 1 меняется на О и перебрасывает первый RS-триггер 27 в единичное состояние. С инверсного выхода нулевым сигналом первый RS-триггер 27 блокирует логические элементы 14 и 15, а с прямого выхода единичным сигналом переводит четвертый элемент И-НЕ 31 в нулевое состояние. В результате высвечивается фотодиод 16, Это указьшает на то, что контролируемое сопротивление 46 находится в норме. Если контролируемое сопротивление 46 меньше нижнего предельного отклонения, т,е, меньше, чем сопротивление второго эталонного резистора 42, то падение напряжения на контролируемом сопротивлении 46 меньше, чем на эталонных резисто- pax AI и 42, при этом на выходе первого порогового компаратора 10 после сравнения напряжений сохраняется нулевой сигнал, а на выходе второго порогового компаратора 11 появляется сигнал 1. Так как на всех входах элемента И-НЕ 15 присутствуют единичные сигналы, то на выходе устанавливается нулевой сигнал, который подается к 8-входу третьего RS-тригге- ра 29 и перебрасывает его в единичное состояние. Сигнал 1 третьего RS-триггера 29 переводит второй ин1

Jo

1520 25 JQ 45 50 55

2509866

вертор 33 в нуле-вое состояние, при котором высвечивается фотодиод 34, указывая на то, что контролируемое сопротивление 46 ниже нижнего пре- 5 дельного отклонения. Одновременно

35

40

с инверсного выхода третьего RS-триггера 29 нулевым сигналом блокируется элемент И-НЕ 31, однако, хотя первый RS-триггер 27 тоже перебрасывается в единичное состояние, изменить состояния элемента И-НЕ 28 он не может, при этом с инверсного выхода RS-триггера 27 сигналом О блокируются элементы И-НЕ 15 и 14,

Если контролируемое сопротивление 46 больше верхнего отклонения, т.е. больше, чем сопротивление первого эталонного резистора 41, то падение напряжения на контролируемом сопротивлении 46 больше, чем на эталонных резисторах 41 и 42. Тогда на выходе второго порогового компаратора 11 после сравнения напряжений сохраняется нулевой сигнал, а на выходе первого порогового компаратора 10 появляется сигнал 1. Так как на всех входах элемента И-НЕ 14 присутствуют единичные сигналы, то на его вькоде устанавливается нулевой сигнал, подаваемый на S-вход второго RS-триггера 28, который перебрасывает его в единичное состояние. Второй RS-триггер 28 сигналом 1 с прямого выхода переводит первый инвертор 32 в нулевое состояние, при котором начинает высвечиваться фотодиод 35, указывая на то, что контролируемое сопротивление 46 выше верхнего предельного отклонения. Одновременно с инверсного выхода второго RS-триггера 28 нулевым сигналом блокируется четвертый элемент И-НЕ 31, однако, хотя первый RS-триггер 27 тоже перебрасывается в единичное состояние, изменить состояние четвертого элемента И-НЕ 28 не может. При этом с инверсного выхода первого RS-триггера 27 сигналом О блокируются первый и второй элементы И-НЕ 14 и 15.

Предлагаемое устройство в результате высокой помехоустойчивости на порядок повышает точность контроля, что позволяет расширить диапазон контролируемых сопротивлений как по видам сопротивлений проволочных резисторов обмоток электрических машин и аппаратов и т.д., так и по их величине, как в сторону малых, так и в сторону

больших сопротивлений. Принципиальная схема устройства проста в настройке и эксплуатации и не требует высокостабильного источника питания.

Формула изобретения

1. Устройство для контроля отклонений сопротивлений от заданных зон допуска, содержащее измерительную схесоединены между собой и с первым входом третьего элемента И-НЕ, кото рый соединен с третьим входом логического блока, третьи входы первого и второго элементов И-НЕ соединены между собой и подключены к второму входу третьего элемента И-НЕ и к пря мому выходу четвертого RS-триггера, четвертые входы первого и второго

му, блок дифференциальнь х усилителей, to элементов И-НЕ соединены между собой и подключены к инверсному выход первого RS-триггера, выход первого элемента И-НЕ подключен к S-входу второго RS-триггера, выход второго элемента -И-НБ - к S-входу третьего RS-триггера, выход третьего элемента И-НЕ - к S-входу первого RS-триг гера, а вьжод четвертого элемента И НЕ соединен с третьим выходом логического блока, первые выводы первог и второго резисторов питания соединены между собой и подключены к шине Плюс, второй вывод первого резистора питания подключен к S-вхсгду четвертого RS-триггера и через кноп ку Пуск - к общей ашие, R-входы первого, второго, третьего и четвер того RS-триггеров соединены между собой и подключены к второму выводу второго резистора питания и через кнопку Исходное положение - к общей шине, прямые выходы второго и третьего RS-триггеров подключены к входам соответственно первого и второго инверторов, выходы которых соединены соответственно с первым и вторым выходами логического блока инверсные выходы второго и третьего RS-триггеров подключены соответствен но к первому и второму входам четвер того элемента И-НЕ, третий вход которого присоединен к прямому выходу первого RS-триггера.

логический блок и источник постоянного напряжения, подключенный между входом измерительной схемы и общей шиной, отличающееся тем, что, с целью повышения достоверности контроля, в него введены блок подавления помехи, двухпороговый компаратор, индикатор и буферньй блок, причем первый, второй, третий и четвертый выходы измерительной схемы подклю чены соответственно к первому, второму, третьему и четвертому входам блока дифференциальных усилителей, пятый вход которого присоединен к клемме для подключения контролируемого сопро тивления, а шестой вход - к тине, первый, второй и третий выходы блока дифференциальных усилителей подключены соответственно к первому, второму и третьему входам двухпорого- вого компаратора, первый и второй выходы которого подключены соответственно к первому и второму входам буферного блока, первый и второй выходы которого подключены соответственно к первому и второму входам логического блока, третий вход которого подключен к выходу блока подавления помехи, первый вход которого присоединен к общей шине, а второй вход через конденсатор - к клемме для подключения контролируемого сопротивления, первый, второй и третий выходы логического блока подключены соответственно к первому, второму и третьему входам индикатора.

2. Устройство по п. 1, о т л и- чающееся тем, что логический блок содержит первый, второй, третий и четвертый элементы И-НЕ, первый, второй, третий и четвертый RS-триг- геры, первый и второй инверторы, кнопку Пуск, кнопку Исходное положение, первый и второй резисторы питания, шину Плюс и общую шину, причем первые входы первого и второ- го элементов И-НЕ соединены соответственно с первым и вторым входами логического блока, вторые входы

соединены между собой и с первым входом третьего элемента И-НЕ, который соединен с третьим входом логического блока, третьи входы первого и второго элементов И-НЕ соединены между собой и подключены к второму входу третьего элемента И-НЕ и к прямому выходу четвертого RS-триггера, четвертые входы первого и второго

15 20 25 jg

5

0

5

0

бой и подключены к инверсному выходу первого RS-триггера, выход первого элемента И-НЕ подключен к S-входу второго RS-триггера, выход второго элемента -И-НБ - к S-входу третьего RS-триггера, выход третьего элемента И-НЕ - к S-входу первого RS-триггера, а вьжод четвертого элемента И- НЕ соединен с третьим выходом логического блока, первые выводы первого и второго резисторов питания соединены между собой и подключены к шине Плюс, второй вывод первого резистора питания подключен к S-вхсгду четвертого RS-триггера и через кнопку Пуск - к общей ашие, R-входы первого, второго, третьего и четвертого RS-триггеров соединены между собой и подключены к второму выводу второго резистора питания и через кнопку Исходное положение - к общей шине, прямые выходы второго и третьего RS-триггеров подключены к входам соответственно первого и второго инверторов, выходы которых соединены соответственно с первым и вторым выходами логического блока, инверсные выходы второго и третьего RS-триггеров подключены соответственно к первому и второму входам четвертого элемента И-НЕ, третий вход которого присоединен к прямому выходу первого RS-триггера.

3. Устройство по п. чающееся тем, ления помехи содержит первый и второй усилители помехи, первый и второй диоды, балластные резисторы, компаратор и первый и второй фильтры, причем инвертирующий вход первого усилителя помехи соединен с неинвертирующим входом второго усилителя помехи и первым входом блока подавления помехи, инвертирующий вход, второго усилителя помехи соединен с неинвертирующим входом первого усилителя помехи и с вторым входом блока подавления помехи, выход первого усилителя помехи через последочательно

1, о т л и- что блок подавсоединенные первый диод, первый фильтр и первый балластный резистор подключен к инвертирующему входу компаратора, выход второго усилителя помехи через последовательно соединенные второй диод, второй фильтр и второй балластный резистор - также к инвертирующему входу компаратора, выход которого соединен с выходом блока подавления помехи.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для подавления импульсных помех | 1984 |

|

SU1256178A1 |

| Устройство для контроля логических и временных параметров сигналов | 1990 |

|

SU1777235A1 |

| Устройство для автоматизированного контроля параметров реле | 1985 |

|

SU1265704A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ИМПУЛЬСОВ | 2004 |

|

RU2256288C1 |

| Устройство для контроля импульсных трансформаторов в составе электронных блоков | 1987 |

|

SU1471158A1 |

| Способ определения входного сопротивления усилителя заряда и устройство для его осуществления | 1984 |

|

SU1205060A1 |

| Цифровой измеритель температуры | 1984 |

|

SU1224609A1 |

| Цифровой измеритель перемещений | 1987 |

|

SU1620947A1 |

| ИМПУЛЬСНЫЙ СТАБИЛИЗАТОР ПОСТОЯННОГО НАПРЯЖЕНИЯ ПОНИЖАЮЩЕГО ТИПА | 1991 |

|

RU2006062C1 |

| Электронный музыкальный звонок | 1988 |

|

SU1748176A1 |

Изобретение относится к области контрольно-измерительной техники и может быть использовано для контроля активного сопротивления электрорадиоэлементов, электрооборудования и электрических цепей, в частности для контроля сопротивления обмоток электрических машин и аппаратов. Целью изобретения является повышение достоверности контроля за счет улучшения помехоустойчивости устройства. Для этого в устройство введены блок подавления помехи, двухпороговый компаратор, индикатор и буферный блок. По- вьш1ение помехоустойчивости позволило на порядок повысить точность контроля и расширить диапазон контролируемых сопротивлений как по видам проволочных сопротивлений, резисторов, моток электрических машин и т.п., так и по их величине, т.е. в сторону малых и в сторону больших сопротивлений. Устройство просто в настройке и эксплуатации и не требует высокостабильного источника питания. 2 з.п.ф-лы, 1 ил. о SS (/)

| Устройство для измерения сопротивления | 1976 |

|

SU712763A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ОТКЛОНЕНИЙСОПРОТИВЛЕНИЙ РЕЗИСТОРОВ ОТ ЗАДАННЫХЗОН ДОПУСКА | 1972 |

|

SU453649A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1986-08-15—Публикация

1984-08-02—Подача