контроля fi, элемент ШГИ 5, блок управления 7, контрольные входа которого подключены через узел контроля 6 и элемент ИШ S соответстБенно к информацнонтмм и контрольным иыходам блоков контроля 4,,, , Устройство при ординарном потоке откатов обеспечивает исправление люОых (п-1)-кратных ошибок по каждоьгу выходу при п крат

Изобретение относится к вычислительной технике и автоматике и может быть использовано для построения надежных пифровых устройств.

Цель изобретения - повышение на- нежности и упрощение устройства.

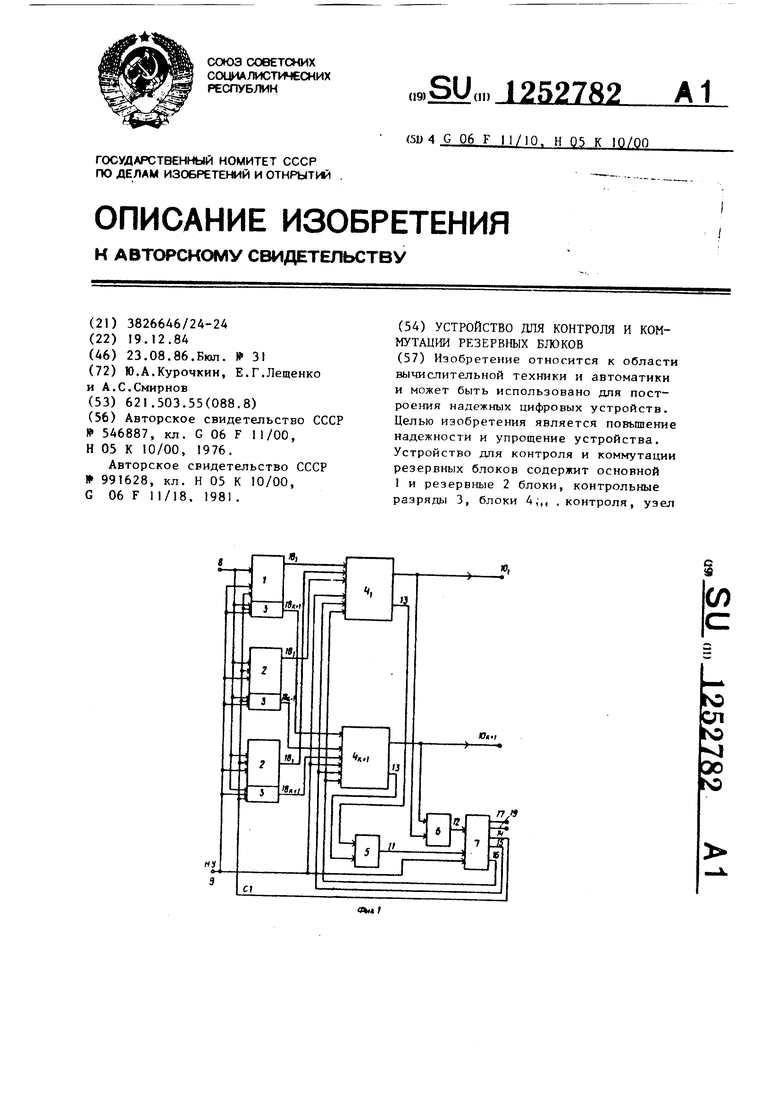

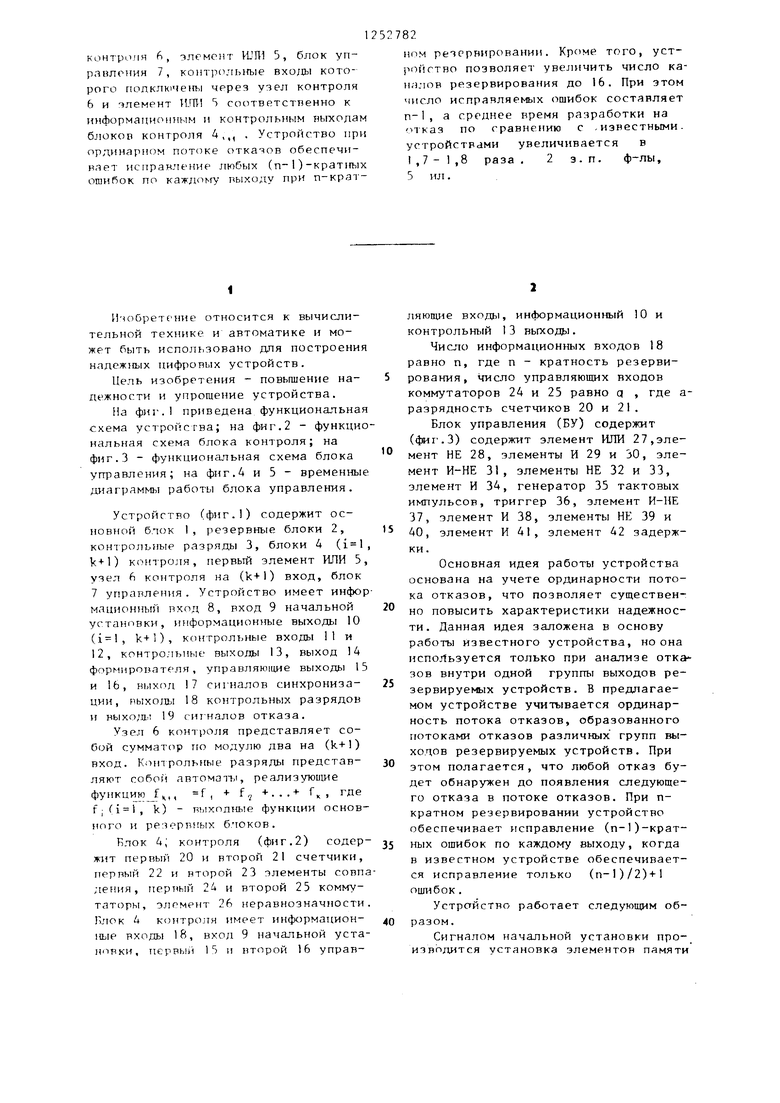

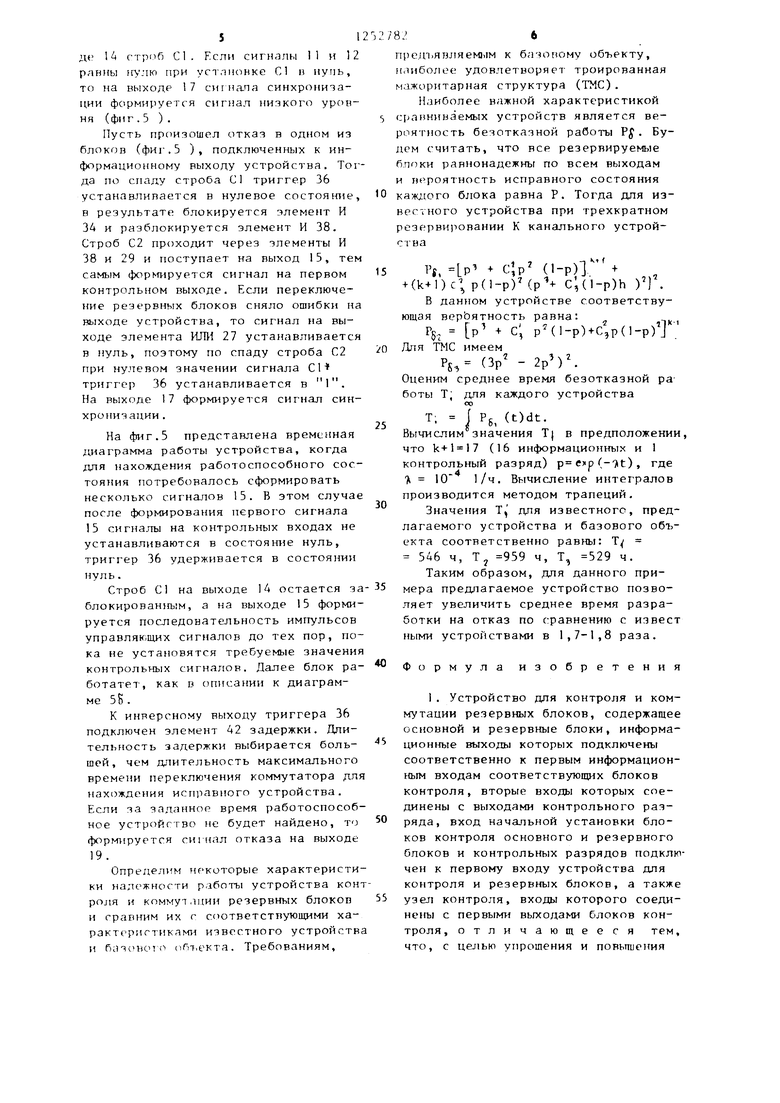

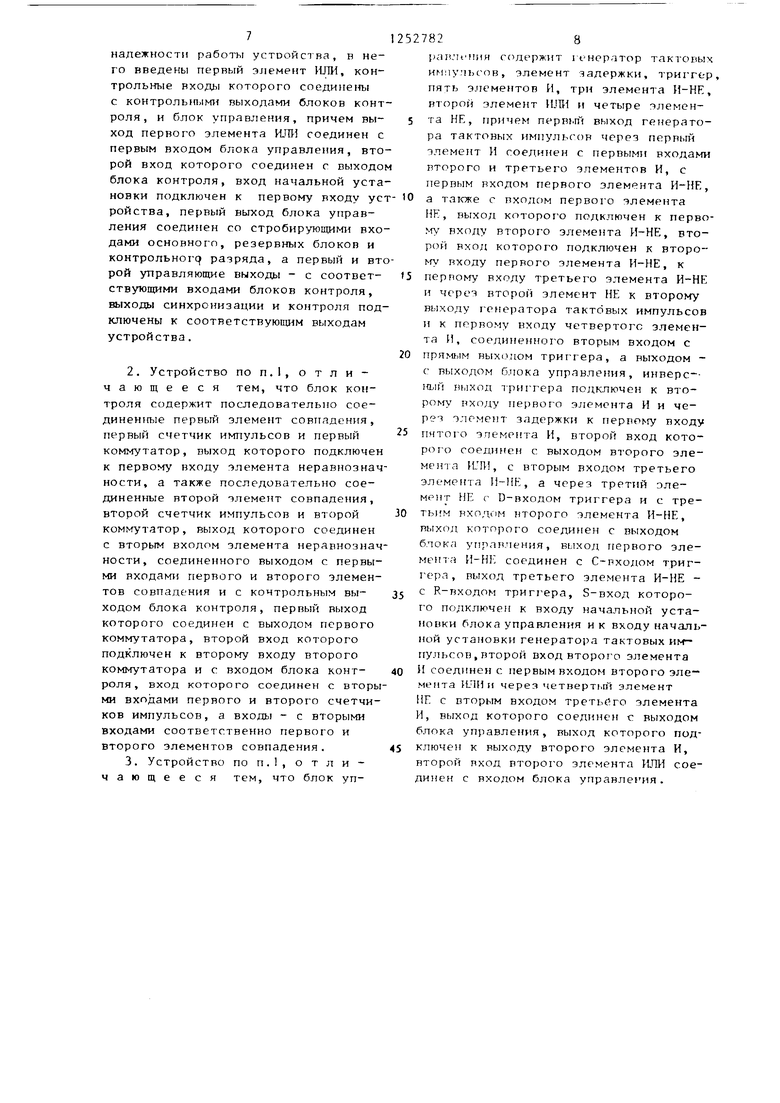

На фиг.1 приведена функциональная схема устройства; на фиг.2 - функциональная схема блока контроля; на фиг.З - функциональная схема блока управления; на фиг.4 и 5 - временные диаграммы работы блока управления.

Устройство (фиг.1) содержит основной блок I, резервные блоки 2, контрольные разряды 3, блоки 4 (, k+1) контроля, первый элемент ИЛИ 5, узел 6 контроля на (k+I) вход, блок 7 управления. Устройство имеет информационный пход 8, вход 9 начальной установки, информационные выходы 10 (, k+1), контрольные входы 11 и 12, контро.чьные выходь 13, выход 14 формирователя, управляющие выходы 15 и 16, выход 17 сигналов синхрониза- ции, пыхош) 18 контрольных разрядов и выхо, Д) 19 сит налов отказа.

Узел 6 контроля представляет собой сумматор по модулю два на (k+1) вход. Контрольные разряды представ- ляют собой автомап,, реализующие функцию 1,, f, + fj +... f, где fI({, k) - выходные функции основного и резервных блоков.

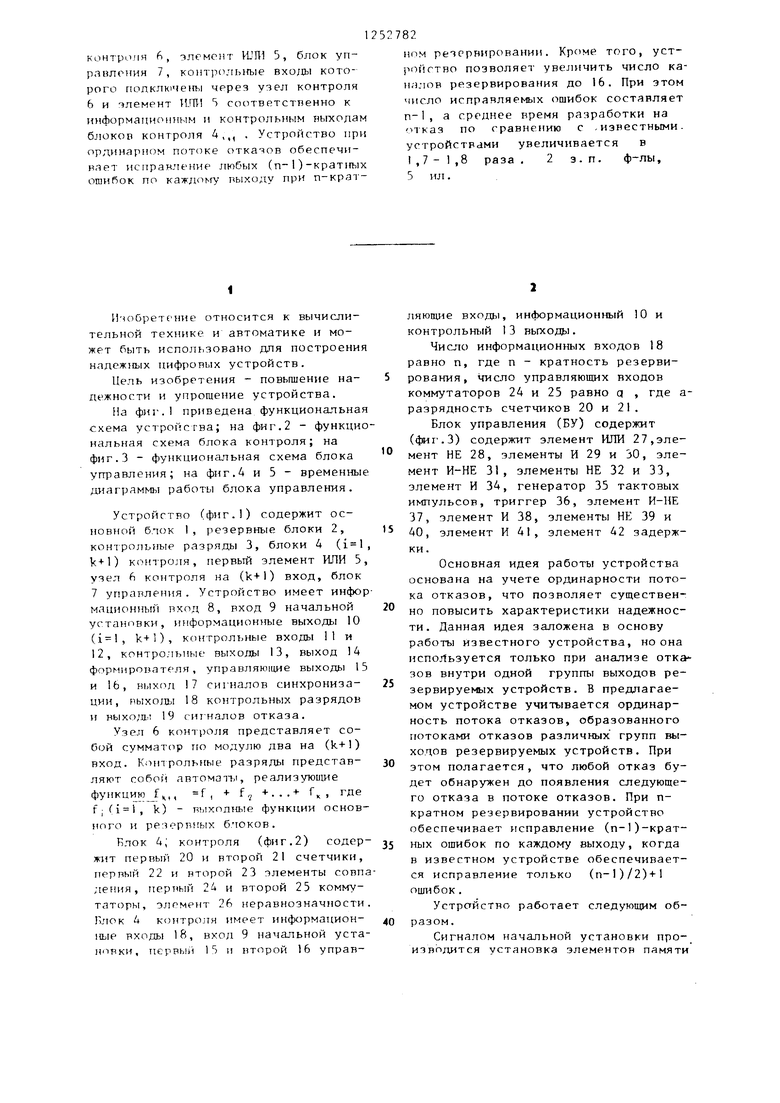

Блок 4; контроля (фиг.2) содер- жит первый 20 и второй 21 счетчики, первый 22 и второй 23 элементы совпадения, первый 24 и второй 25 коммутаторы, элемент 26 неравнозначности. )лок 4 контроля имеет информацион- ные входы 1В, вход 9 начальной установки, первый 15 и второй 16 управ52782

ном речерьировании. Кроме того, устройство позволяет увеличить число каналов резервирования до 16. При этом число исправляемых ошибок составляет п-1 , а среднее время разработки на о1каз по сравнению с ,известными- устройствами увеличивается в 1,7- 1,8 раза . 2 э. п. ф-лы, 5 ил.

ляющие входы, информационный 10 и контрольный 13 выходы.

Число информационных входов 18 равно п, где п - кратность резервирования, число управляющих входов коммутаторов 24 и 25 равно q , где а- разрядность счетчиков 20 и 21.

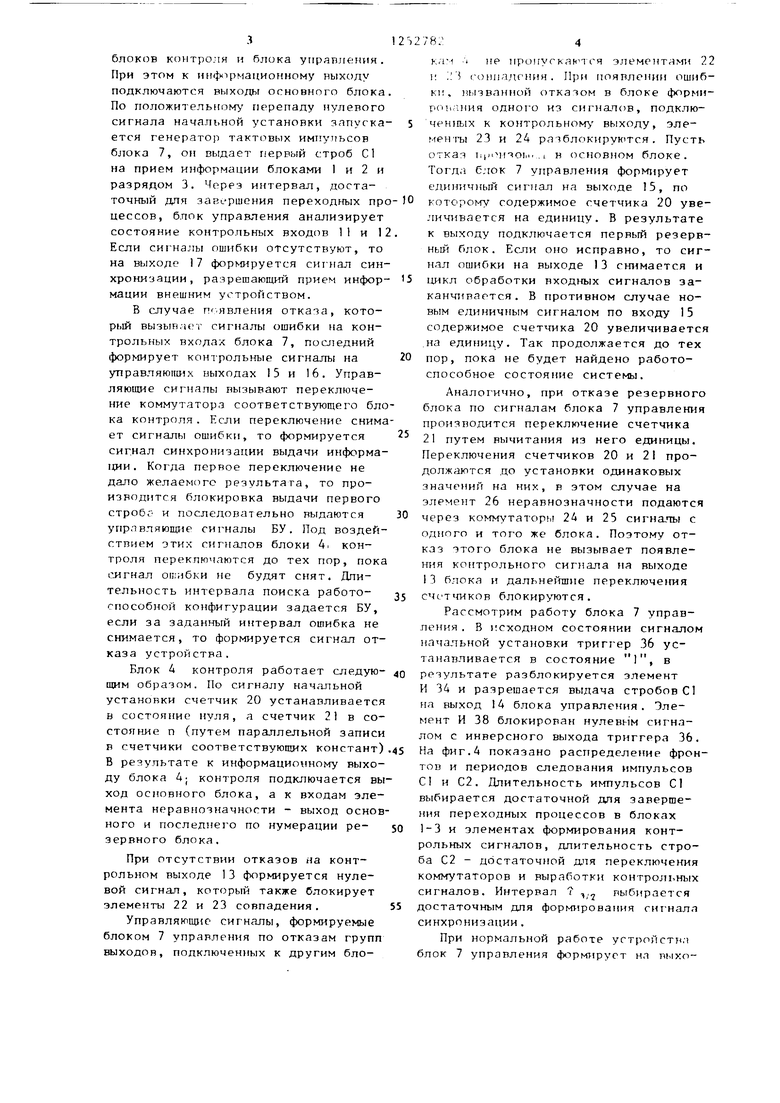

Блок управления (БУ) содержит (фиг .З) содержит элемент ИЛИ 27,элемент НЕ 28, элементы И 29 и 30, элемент И-НЕ 31 , элементы НЕ 32 и 33, элемент И 34, генератор 35 тактовых импульсов, триггер 36, элемент И-НЕ 37, элемент И 38, элементы НЕ 39 и 40, элемент И 41, элемент 42 задержки .

Основная идея работы устройства основана на учете ординарности потока отказов, что позволяет существенно повысить характеристики надежности. Данная идея заложена в основу работы известного устройства, но она используется только при анализе отка зов внутри одной группы выходов резервируемых устройств. В предлагаемом устройстве учитывается ординарность потока отказов, образованного потоками отказов различных групп выходов резервируемых устройств. При этом полагается, что любой отказ будет обнаружен до появления следующего отказа в потоке отказов. При п- кратном резервировании устройство обеспечивает исправление (п-1)-крат- ных ощибок по каждому выходу, когда в известном устройстве обеспечивает- ся исправление только (n-l)/2)-t-l ошибок .

Устройство работает следующим образом.

Сигналом начальной установки производится установка элементов памяти

3

блоков коу{троля и блока упрявлеяня. При этом к ия хтрмационному ныходу подключаются выходы основного блока По положительному перепаду пулевого сигнала начальной установки запуска- ется генератор тактов 1х импуньсов блока 7, оп выдает первый строб С1 на прием информации блоками I и 2 и разрядом 3. Через интервал, достаточный для зaвL pшeния переходных про цессов, блок управления анализирует состояние контрольных входов 11 и 12 Если сиг налы ошибки отсутствуют, то на выходе 17 формируется сит нал синхронизации, разрешающий прием инфор- нации внешним устройством.

В случае пг-явления отказа, который вызып. сигналы ошибки на контрольных входах блока 7, последний формирует контрольные сигналы на управляюпшх выходах 15 и 16. Управляющие сигналы вызывают переключение коммутатора соответствующего блока контроля. Если переключение снимает сигналы ошибки, то формируется сигнал синхронизации выдачи информации. Когда первое переключение не дало желаемого результата, то производится блокировка выдачи первого стробГ и последовательно выдаются уг1рпвляюш11е сигналы БУ. Под воздействием этих сигналов блоки 4i контроля переключаются до тех пор, пока с 1гнал оп;ибки не будят снят. Длительность интервала поиска работо- способной конфигурации задается БУ, если за заданный интервал ошибка не снимается, то формируется сигнал отказа устройства.

Блок Д контроля работает следую- щим образом. По сигналу начальной установки счетчик 20 устанавливается в состояние нуля, а счетчик 21 в состояние п (путем параллельной записи в счетчики соответствующих констант) В результате к информационному выходу блока 4; контроля подключается выход основного блока, а к входам элемента неравнозначности - выход основного и последнего по нумерации ре- зеррного блока.

При отсутствии отказов на контрольном выходе 13 формируется нулевой сигнал, который также блокирует элементы 22 и 23 совпадения.

Управляющие сигналы, формируемые блоком 7 управления по отказам групп выходов, подключенных к другим бло7 8 .4

ка- t не ироиугканп СИ элементами 2 и : гоппадгния. При появлении ошиб К1, iii)i3ванной отказом в блоке форми роь.-.ния одног о из сигналов, подключенных к контрольном, выходу, эле- мен тъ 23 и 24 разблокирун тся. Пусть отказ ,i. . 1 в основном блоке. Тогда блок 7 управления формирует единич){ьй сиглал на выходе 15, по которому содержимое счетчика 20 уве -чичивается на единицу. В результате к выходу подключается первый резервный блок. Ес-Пи оно исправно, то си1- нал ошибки на выходе )3 снимается и цикл обработки входных сигналов заканчивается. В противном случае новым единичным сигналом по входу 15 содержимое счетчика 20 увеличивается на единицу. Так продолжается до тех пор, пока не будет найдено работоспособное состояние системы.

Аналогично, при отказе резервного блока по сигналам блока 7 управления производится переключение счетчика 21 путем вычитания из него единицы. Переключения счетчиков 20 и 2I продолжаются до установки одинаковых значений на них, в этом случае на элемент 26 неравнозначности подаются через коммутаторы 24 и 25 сигналы с одного и того же блока. Поэтому отказ этого блока не вызывает появления контрольного сигнала па выходе I3 блока и дальнейшие переключения счетчиков блокируются.

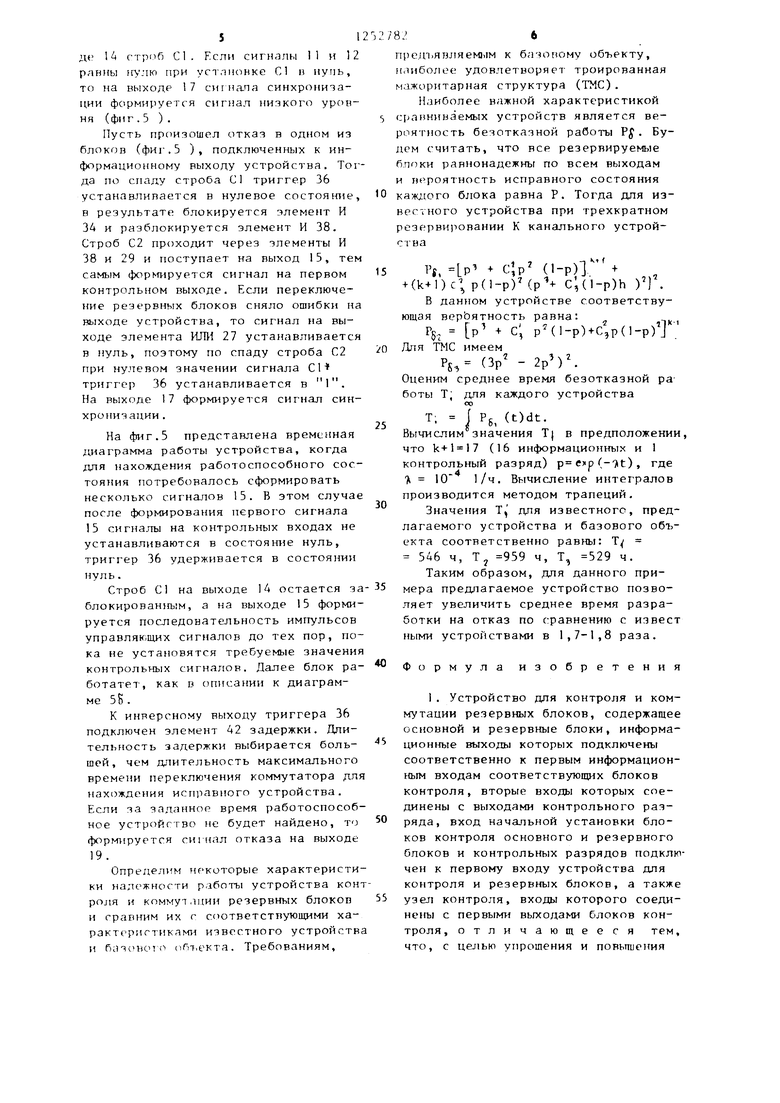

Рассмотрим работу блока 7 управления . В исходном состоянии сигналом начальной установки триггер 36 устанавливается в состояние 1, в результате разблокируется элемент И 34 и разрешается выдача стробовС1 на выход 14 блока управления. Элемент И 38 блокирован нулевым сигналом с инверсного выхода триггера 36. На фиг.4 показано распределение фронтов и периодов следования импульсов CI и С2. Длительность импульсов С1 выбирается достаточной для завершения переходных процессов в блоках 1-3 и элементах формирования контрольных сигналов, длительность строба С2 - достаточной для переключения коммутаторов и выработки коитрол1.ных сигналов. Интервал -. выбирается достаточнь1м для формирования сигнала синхронизации.

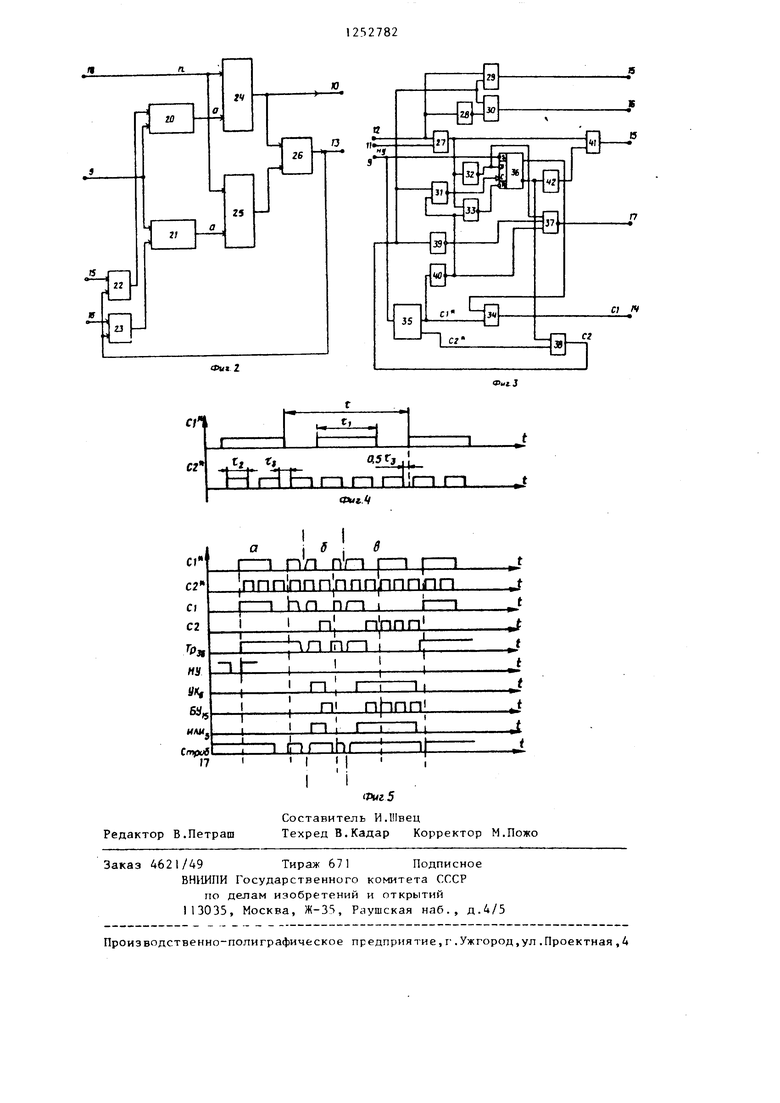

При нормальной работе устройстя.ч блок 7 управления формирует на пыходе 14 гтрмб С1. Если сигналы 11 и 12 равны 1гулю при устлнонке С1 п нупь, то на выходе 1 7 CKI Hti,na синхронизации формируется сигнал низкого урои- ня (фиг.5 ).

Пусть произошел отказ в одном из блоков (фИ1 .5 ), подключенных к информационному выходу устройства. Тогда по спаду строба С1 триггер 36 устанавливается в нулевое состояние, в результате блокируется элемент И 34 и разблокируется элемент И 38. Строб С2 проходит через элементы И 38 и 29 и поступает на выход 15, тем самым форьгируется сигнал на первом контрольном выходе. Если переключение резервных блоков сняло ошибки на выходе устройства, то сигнал на выходе элемента ИЛИ 27 устанавливается в нуль, поэтому по спаду строба С2 при нулевом значении сигнала С1 триггер 36 устанавливается в 1. На выходе 17 формируется сигнал синхронизации .

На фиг.5 представлена временная диаграмма работы устройства, когда для нахождения работоспособного состояния потребовалось сформировать несколько сигналов 15. В этом случае после формирования первого сигнала 15 сигналы на контрольных входах не устанавливаются в состояние нуль, триггер 36 удерживается в состоянии нуль.

Строб С1 на выходе 14 остается за блокированнь м, а на выходе 15 формируется последонат€ льность импульсов управляющих сигналов до тех пор, пока не установятся требуемые значения контрольных сигналов. Далее блок ра- ботатет, как в описании к диаграмме 5S .

К инверсному Bbixoziy триггера 36 подключен элемент 42 задержки. Длительность задержки выбирается большей, чем длительность максимального времени переключения коммутатора для нахождения исправного устройства. Если за заданное время работоспособное устройство не будет найдено, то формируется сигнал отказа на выходе 19.

Определ)1м некоторые характеристики надежности работы устройства контроля и коммутлции резервных блоков и сравним их с соответствующими характеристиками известного устройства и fiinoHOTf яГтт.екта. Требованиям,

2/8. 6

предп.являем1,1М к бачопому объекту, наиболее удовлетворяет троированная мажоритарная структура (ТМС).

Наиболее важной характеристикой 3 сравниваемых устройств является вероятность безотказной работы PJ. Будем считать, что все резервируемые блоки равнонадежны по всем выходам и вероятность исправного состояния

О каждого блока равна Р. Тогда для известного устройства при трехкратном резервировании К канального устройства

5 Ft. ЧР - С:Р (1-р)Г ,,

)c; р(1-р)Чр + c;{i-p)h ))

в данном устройстве соответствующая верЬятность равна:

pg,, р- 4 с; рЧ1-р)с ,р(1-р)

O Для ТМС имеем

PS, (зр - 2pЪ

Оценим среднее время безотказной ра боты Т; для каждого устройства

5 I Рб, (t)dt.

Вычислим значения Т) в предположении, что (16 информационных и 1 контрольный разряд) р ор (-Tit) , где Ik 10 1/Ч. Вычисление интегралов производится методом трапеций.

Значения Т, для известного, предлагаемого устройства и базового объекта соответственно равны: Т 546 ч, Т 959 ч. Т, 529 ч.

Таким образом, для данного при- 5 мера предлагаемое устройство позволяет увеличить среднее время разработки на отказ по сравнению с извест ными устройствами в 1,7-1,8 раза.

Формула изобретения

1. Устройство для контроля и коммутации резервных блоков, содержащее основной и резервные блоки, информационные выходы которых подключены соответственно к первым информационным входам соответствующих блоков контроля, вторые входы которых соединены с выходами контрольного раз0 ряда, вход начальной установки блоков контроля основного и резервного блоков и контрольных разрядов подключен к первому входу устройства для контроля и резервных блоков, а также

5 узел контроля, входы которого соединены с первыми выходами блоков контроля, отличающееся тем, что, с целью упрощения и повышения

5

7

надежности работы устройства, в него введены первый элемент ИЛИ, контрольные входы которого соединены с контроль1п,1мн выходами блоков контроля, и блок управления, причем выход первого элемента ИЛИ соединен с первым входом блока управления, второй вход которого соединен с выходом блока контроля, вход начальной установки подключен к первому входу уст ройства, первый блока управления соединен со стробирующими входами основного, резервных блоков и контрольного разряда, а первый и вто рой управляющие выходы - с соответствующими входами блоков контроля, выходы синхронизации и контроля подключены к соответствующим выходам устройства.

2.Устройство по п.1, о т л и - чающееся тем, что блок контроля содержит последовательно соединенные первый элемент совпадения, первый счетчик импульсов и первый коммутатор, выход которого подключен к первому входу элемента неравнозначности, а также последовательно соединенные второй элемент совпадения, второй счетчик импульсов и второй коммутатор, выход которого соединен

с BTOpbiM входом элемента неравнозначности, соединенного выходом с первыми входами первого и второго элементов совпадения и с контрольным выходом блока контроля, первый выход которого соединен с выходом первого коммутатора, второй вход которого подключен к второму входу второго ком1 гутатора и с входом блока контроля, вход которого соединен с вторыми входами первого и второго счетчиков импульсов, а входы - с вторыми входами соответственно первого и второго элементов совпадения.

3.Устройство по п.1, о т л и - чающееся тем, что блок уп527828

рсЧП. И Иия с(жержит генератор тактовых HM:iy;ibcoB, элемент задержки, триггер, пять элементов И, три элемента И-НЕ, второй элемент ИЛИ и четыре элемен- 5 та НЕ, Г1р)1чем первый выход генератора тактовых импульсов через первый элемент И соединен с первыми входами второго и третьего элементов И, с первым входом первого элемента И-НЕ, 10 а татсже с входом первого элемента

НЕ, выход которог о подключен к перво- Nrv входу второго элемента И-НЕ, вто- р(П) вход которого подключен к второ- входу первого элемента И-НЕ, к 5 перпом входу третьего элемента И-НЕ и через второй элемент НЕ к второму выходу генератора тактовых импульсов и к первому входу четвертого элемента И, соединенного вторым входом с 20 прям1.1м выходом триггера, а выходом - с выходом блока управления, инверс-- ный шлход триггера подключен к вто- poNfy входу первого элемента И и че- рет элемент задержки к neproNry входу 5 питого элемента И, второй вход которого соединен с выходом второго эле- Meina ИТГИ, с вторым входом третьего элемента И-НЕ, а через третий элемент НЕ г D-входом триггера и с тре- 0 тьим нходом второго элемента И-НЕ, выход которого соединен с выходом блока управления, вь1ход первого эле- меит .ч И-Н1 соединен с С-пходом триггера, выход третьего элемента И-НЕ - с R-входом триггера, S-вход которого подключен к входу начальной установки блока управления и к входу начальной установки генератора тактовых иьг- пульсов , второй вход второг о элемента 0 И соединен с первым входом второго элемента lUlH и через четвертой элемент НЕ с вторым входом третьего элемента И, выход которого соединен с выходом блока управления, выход которого под- 5 ключен к выходу второго элемента И, второй вход второго элемента ИЛИ соединен с входом блока управле1 ия.

25

Фиг I

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для коррекции ошибок | 1986 |

|

SU1352490A1 |

| Адаптивный восстанавливающий орган | 1984 |

|

SU1292216A1 |

| Устройство для управления переключением резервных блоков | 1984 |

|

SU1190557A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ДИНАМИЧЕСКИМ РЕЗЕРВИРОВАНИЕМ | 1990 |

|

RU2028677C1 |

| Устройство для магнитной записи цифровой информации | 1982 |

|

SU1037337A1 |

| Измерительная система с автоматическим контролем аналого-цифрового преобразования и блок задания нечувствительности | 1991 |

|

SU1837261A1 |

| Многоканальное регистрирующее устройство | 1988 |

|

SU1698899A1 |

| Устройство для отображения информации | 1978 |

|

SU883955A1 |

| Вероятностный преобразователь аналог-код | 1986 |

|

SU1363461A1 |

| Система коммутации | 1986 |

|

SU1403071A1 |

Изобретение относится к области вычислительной техники и автоматики и может быть использовано для построения надежных цифровых устройств. Целью изобретения является повышение надежности и упрощение устройства. Устройство для контроля и коммутации резервных блоков содержит основной I и резервные 2 блоки, контрольные разряды 3, блоки 4;,, , контроля, узел

В.Петраш

I I

Фиг5

Составитель

Техред В.Кадар Корректор М.Пожо

Заказ 4621/49 Тираж 671 Подписное ВНИИПИ Государственного комитета СССР

ITO делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб. , д.4/5

Производственно-полиграфическое предприятие,г.Ужгород,ул.Проектная,4

Авторы

Даты

1986-08-23—Публикация

1984-12-19—Подача