Изобретение относится к автоматике и вычислительной технике и может быть использовано для построения на-i дежных цифровых устройств.

Цель изобретения - повышение надежности устройства.

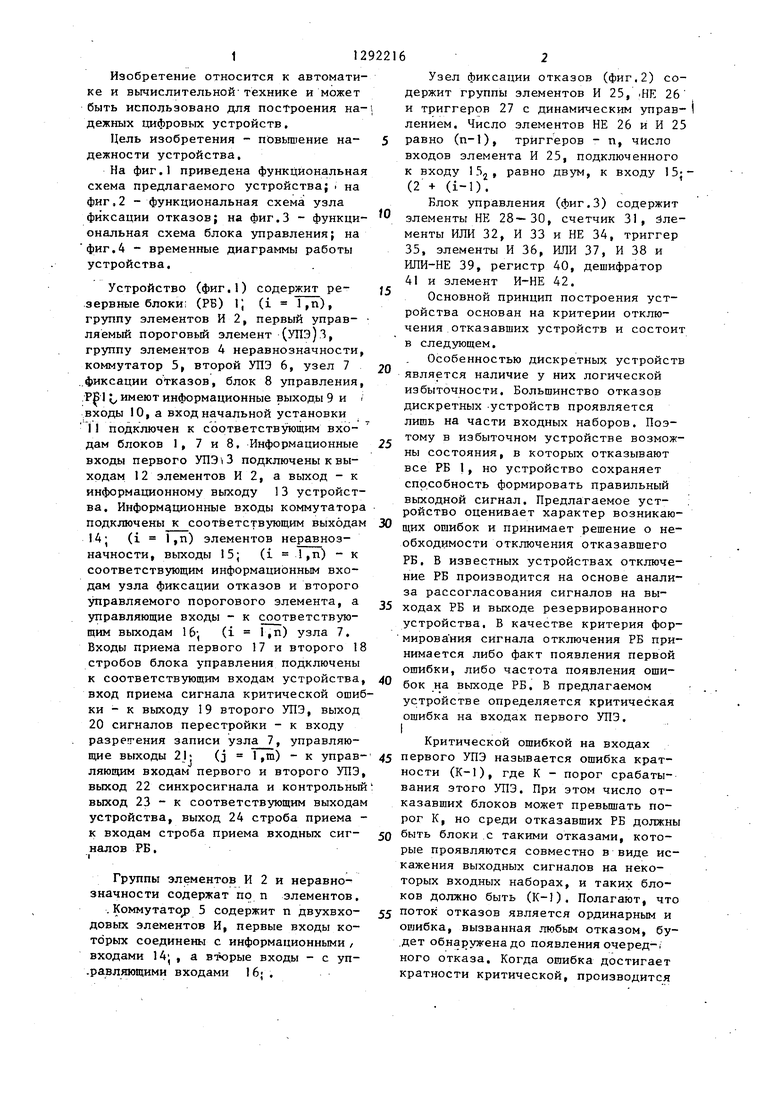

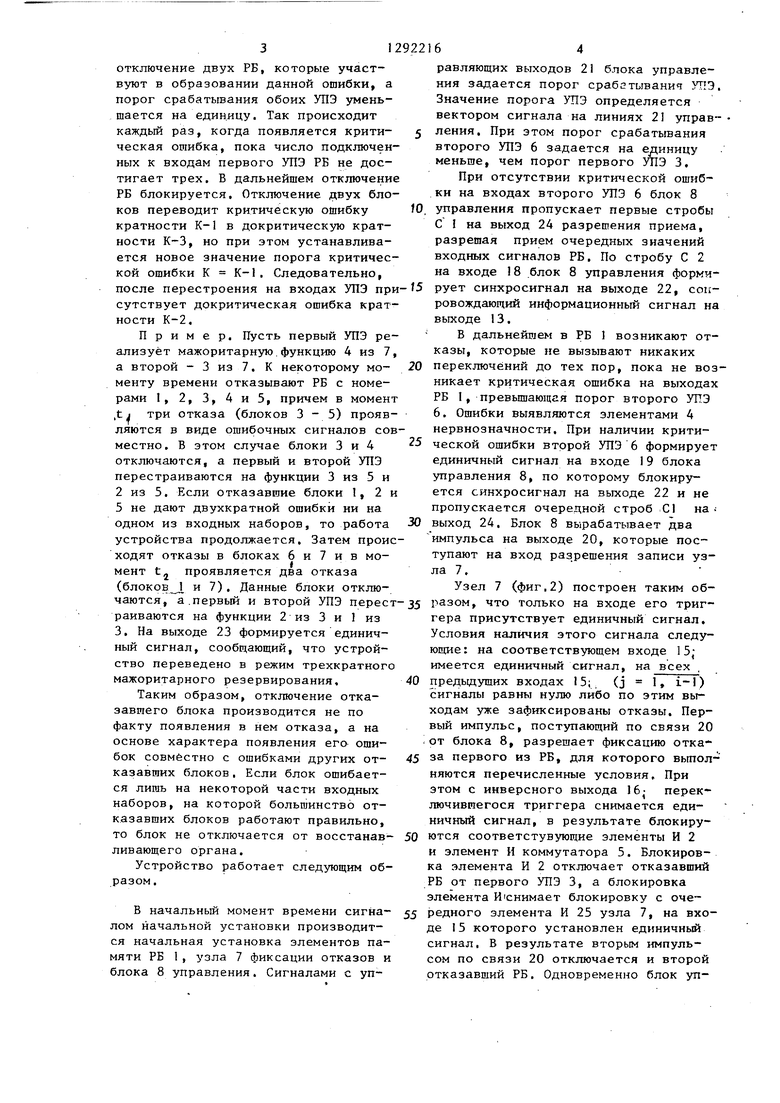

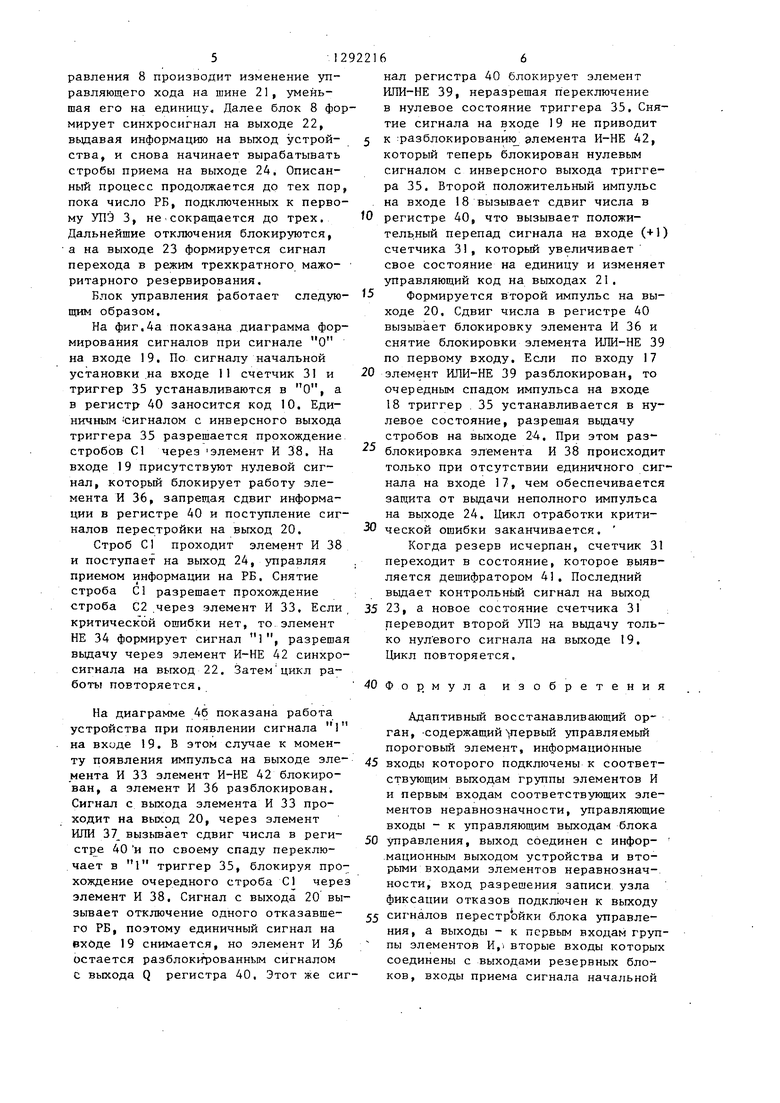

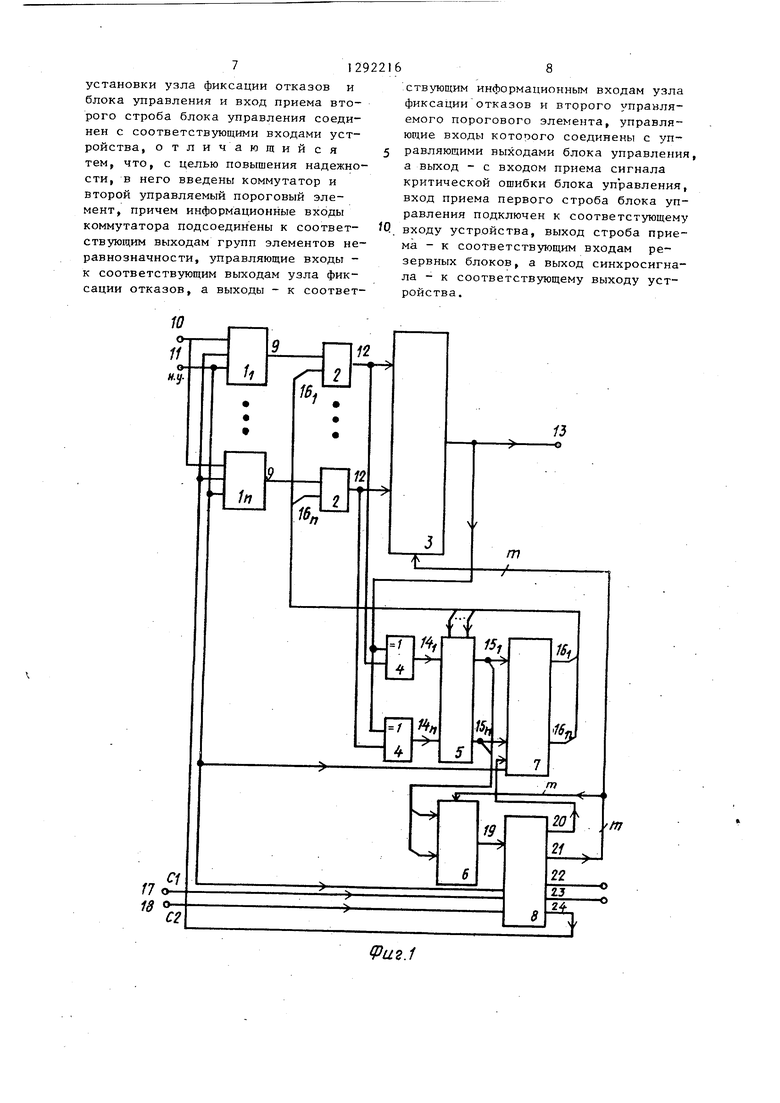

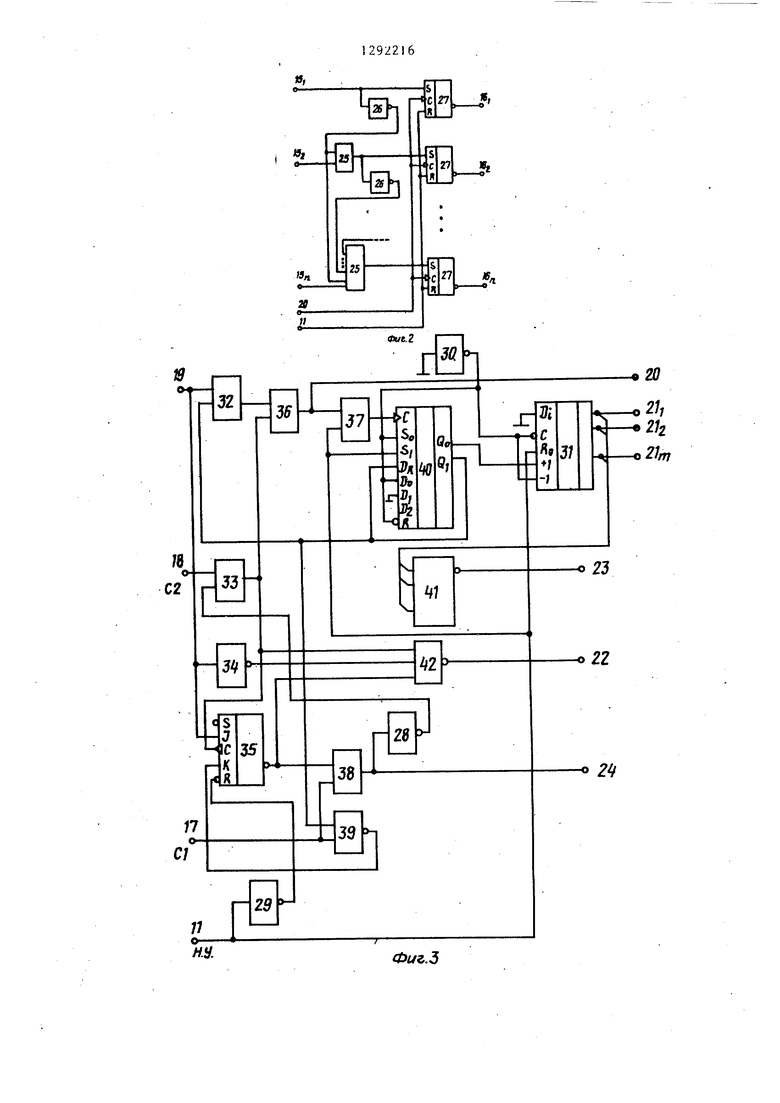

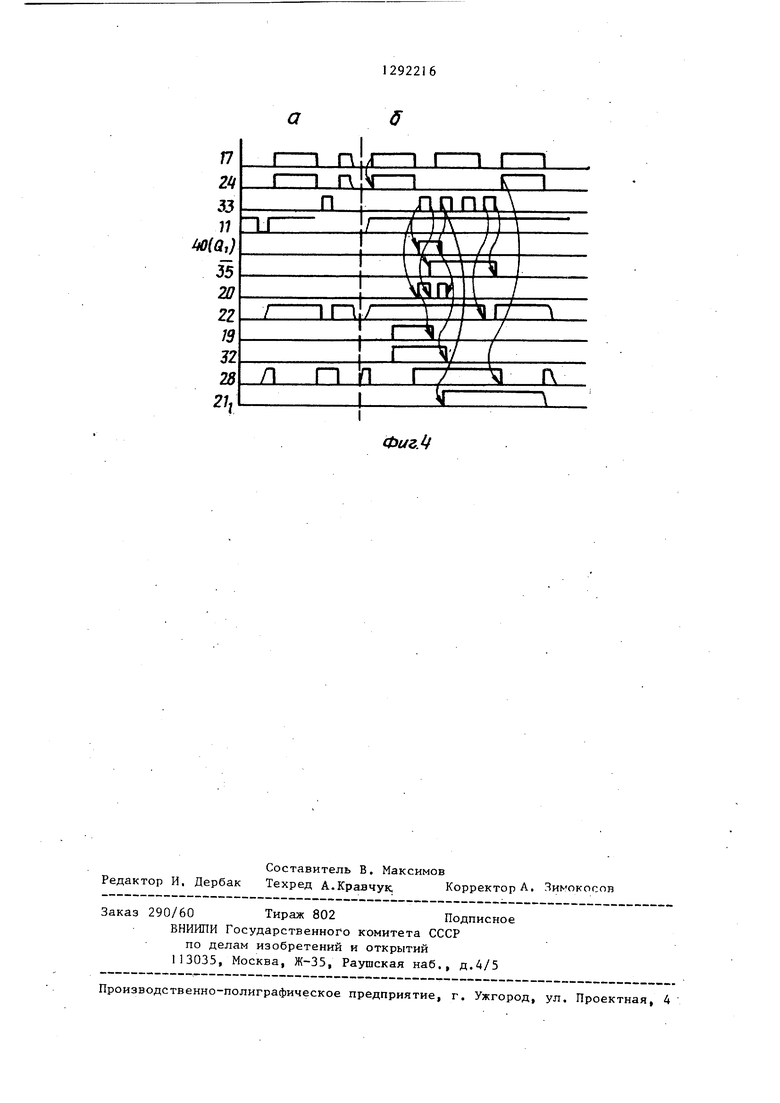

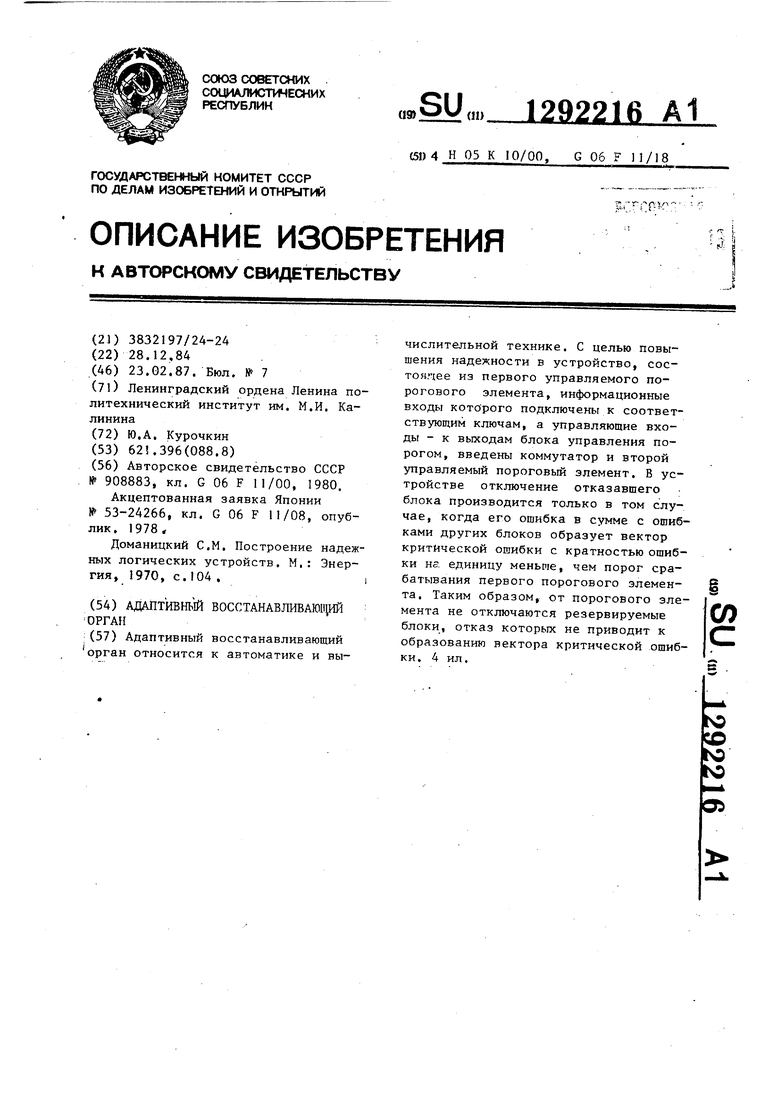

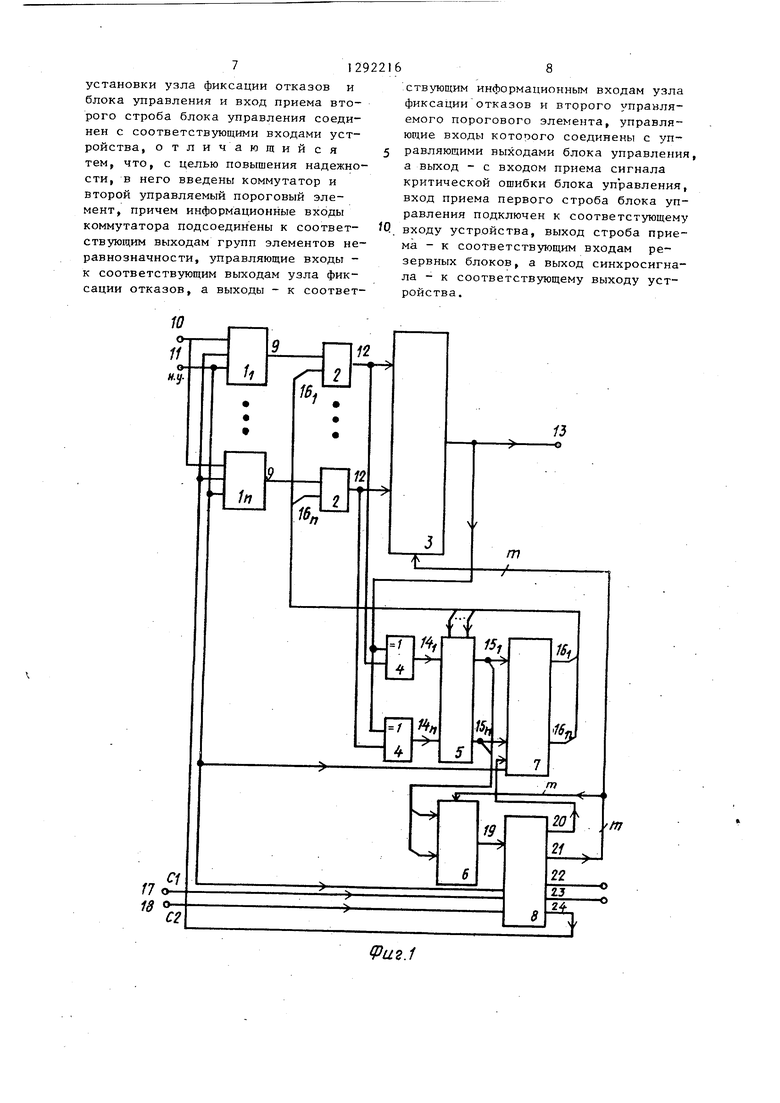

На фиг,1 приведена функциональная схема предлагаемого устройства; на фиг.2 - функциональная схема узла фиксации отказов; на фиг,3 - функциональная схема блока управления; на фиг,4 - временные диаграммы работы устройства.

Устройство (фиг,1) содержит резервные блоки; (РБ) 1| (i J,n), группу элементов И 2, первый управ- яемый пороговый элемент (УПЭ)З, группу элементов Д неравнозначности, оммутатор 5, второй УПЭ 6, узел 7 иксации отказов, блок 8 управления, Ё1J имеют информационные выходы 9 и i ходы 10, а вход начальной установки I1 подключен к соответствующим входам блоков 1, 7 и 8, Информационные входы первого подключены к выходам 12 элементов И 2, а выход - к информационному выходу 13 устройства. Информационные входы коммутатора подключены к соответствующим выходам 14; (i 1,п) элементов неравное- начности, выходы 15; (i 1,п) - к соответствующим информационным входам узла фиксации отказов и второго управляемого порогового элемента, а управляющие входы - к соответствую- щим выходам 16; (i 1,п) узла 7, Входы приема первого 17 и второго 18 стробов блока управления подключены к соответствующим входам устройства, вход приема сигнала критической ошибки - к выходу 19 второго УПЭ, выход 20 сигналов перестройки - к входу разрешения записи узла 7, управляющие выходы 2Ь (J 1 ,т) - к управляющим входам первого и второго УПЭ, выход 22 синхросигнала и контрольный выход 23 - к соответствующим выходам устройства, выход 24 строба приема - к входам строба приема входных сигналов РБ,

Группы элементов И 2 и неравнозначности содержат по п элементов,

.Коммутатор 5 содержит п двухвхо- довых элементов И, первые входы которых соединены с информационными / входами 14; , а вторые входы - с уп- -равляющими входами 16; ,

9221

i

0

15

20

25

30

35

40

45

50

55

62

Узел фиксации отказов (фиг,2) содержит группы элементов И 25, .НЕ 26 и триггеров 27 с динамическим управлением. Число элементов НЕ 26 и И 25 равно (п-1), триггеров - п, число входов элемента И 25, подключенного к входу 15, равно двум, к входу 15;- (2 -ь (i-1),

Блок управления (фиг.З) содержит элементы НЕ 28-30, счетчик 31, Зле- менты ИЛИ 32, И 33 и НЕ 34, триггер 35, элементы И 36, ИЛИ 37, И 38 и ШТИ-НЕ 39, регистр 40, дешифратор 41 и элемент И-НЕ 42,

Основной принцип построения устройства основан на критерии отключения отказавших устройств и состоит в следующем,

Особенностью дискретных устройств является наличие у них логической избыточности. Большинство отказов дискретных .устройств проявляется лишь на части входных наборов. Поэтому в избыточном устройстве возможны состояния, в которых отказывают все РБ 1, но устройство сохраняет способность формировать правильный

выходной сигнал. Предлагаемое устройство оценивает характер возникающих ошибок и принимает решение о необходимости отключения отказавшего РБ, Б известных устройствах отключение РБ производится на основе анализа рассогласования сигналов на выходах РБ и выходе резервированного устройства, В качестве критерия фор- мирова ния сигнала отключения РБ принимается либо факт появления первой ошибки, либо частота появления ошибок на выходе РБ, В предлагаемом устройстве определяется критическая ошибка на входах первого УПЭ, I

Критической ошибкой на входах первого УПЭ называется ошибка кратности (К-1), где К - порог срабатывания этого Л1Э, При этом число отказавших блоков может превьшгать порог К, но среди отказавших РБ должны быть блоки с такими отказами, которые проявляются совместно в виде искажения выходных сигналов на некоторых входных наборах, и таких блоков должно быть (К-1), Полагают, что поток отказов является ординарным и ошибка, вызванная любым отказом, бу- .дет обнаружена до появления очеред-, ного отказа. Когда ошибка достигает кратности критической, производится

312

отключение двух РБ, которые участвуют в образовании данной ошибки, а порог срабатывания обоих УПЭ уменьшается на единицу. Так происходит каждый раз, когда появляется крити- ческая ошибка, пока число подключенных к входам первого УПЭ РБ не достигает трех. В дальнейшем отключение РБ блокируется. Отключение двух блоков переводит критическую ошибку кратности К-1 в докритическую кратности К-3, но при этом устанавливается новое значение порога критической ошибки К К-1. Следовательно, после перестроения на входах УПЭ при сутствует докритическая ошибка кратности К-2.

Пример. Пусть первый УПЭ реализует мажоритарную.функцию 4 из 7, а второй - 3 из 7. К некоторому мо- менту времени отказывают РБ с номерами 1, 2, 3, 4 и 5, причем в момент ,tj три отказа (блоков 3-5) проявляются в виде ошибочных сигналов совместно. В этом случае блоки 3 и 4 отключаются, а первый и второй УПЭ перестраиваются на функции 3 из 5 и 2 из 5. Если отказавшие блоки 1, 2 и 5 не дают двухкратной ошибки ни на одном из входных наборов, то работа устройства продолжается. Затем происходят отказы в блоках 6 и 7 и в момент tj проявляется два отказа (блоков, и 7). Данные блоки отключаются, а.первый и второй УПЭ перест раиваются на функции 2 из 3 и 1 из 3. На выходе 23 формируется единичный сигнал, сообп;ающий, что устройство переведено в режим трехкратного мажоритарного резервирования.

Таким образом, отключение отказавшего блока производится не по факту появления в нем отказа, а на основе характера появления его ошибок совместно с ошибками других отказавших блоков, Если блок ошибается лишь на некоторой части входных наборов, на которой большинство отказавших блоков работают правильно, то блок не отключается от восстанавливающего органа.

Устройство работает следующим образом .

В начальный момент времени сигна- лом начальной установки производится начальная установка элементов памяти РБ 1, узла 7 фиксации отказов и блока 8 управления. Сигналами с уп

25

22

5 О, 5

0 35

5

30

0

45

0

164

равляющих выходов 2 i блока управления задается порог срабатывания УПЭ. Значение порога УПЭ определяется вектором сигнала на линиях 21 управ- ления. При этом порог срабатывания второго УПЭ 6 задается на е циницу меньше, чем порог первого УПЭ 3,

При отсутствии критиг еской ошибки на входах второго УПЭ 6 блок 8 управления пропускает первые стробы С I на выход 24 разрешения приема, разрешая прием очередных значений входных сигналов РБ. По стробу С 2 на входе 18 блок 8 управления формирует синхросигнал на выходе 22, соп - ровождающий информационный сигнал на выходе 13,

В дальнейшем в РБ 1 возникают отказы, которые не вызывают никаких переключений до тех пор, пока не возникает критическая ошибка на выходах РБ I, превьш1ающгя порог второго УПЭ 6, Ошибки выявляются элементами 4 нервнозначности. При наличии критической ошибки второй УПЭ 6 формирует единичный сигнал на входе 19 блока управления 8, по которому блокируется синхросигнал на выходе 22 и не пропускается очередной строб С1 на ; выход 24. Блок 8 вырабатывает два

импульса на выходе 20, которые поступают на вход разрешения записи узла 7 ,

Узел 7 (фиг,2) построен таким образом, что только на входе его триггера присутствует единичный сигнал. Условия наличия этого сигнала следующие: на соответствующем входе 15 имеется единичный сигнал, на всех

предыдущих входах 15;, (j 1, i-1) сигналы равны нулю либо по этим выходам уже зафиксированы отказы. Первый импульс, поступающий по связи 20 от блока 8, разрешает фиксацию отказа первого из РВ, для которого выполняются перечисленные условия. При этом с инверсного выхода 16 переключившегося триггера снимается единичный сигнал, в результате блокируются соответстувующие элементы И 2 и элемент И коммутатора 5, Блокировка элемента И 2 отключает отказавший РБ от первого УПЭ 3, а блокировка элемента И снимает блокировку с очередного элемента И 25 узла 7, на входе 15 которого установлен единичный сигнал, В результате вторым импульсом по связи 20 отключается и второй отказавший РБ. Одновременно блок уп512

равления 8 производит изменение управляющего хода на шине 21, уменьшая его на единицу. Далее блок 8 формирует синхросигнал на выходе 22, вьздавая информацию на выход устрой- ства, и снова начинает вырабатывать стробы приема на выходе 24, Описанный процесс продолжается до тех пор, пока число РБ, подключенных к первому УПЭ 3, не.сокращается до трех. Дальнейшие отключения блокируются, а на выходе 23 формируется сигнал перехода в режим трехкратного мажо- ритарного резервирования,

Блок управления работает следую- щим образом.

На фиг.4а показана диаграмма формирования сигналов при сигнале О на входе 9, По сигналу начальной установки .на входе 11 счетчик 31 и триггер 35 устанавливаются в О, а в регистр 40 заносится код 10, Единичным сигналом с инверсного выхода триггера 35 разрешается прохождение стробов С1 через элемент И 38, На входе 19 присутствуют нулевой сигнал, который блокирует работу элемента И 36, запрещая сдвиг информации в регистре 40 и поступление сигналов перестройки на выход 20,

Строб С1 проходит элемент И 38 и поступает на выход 24, управляя приемом информации на РБ, Снятие строба С1 разрешает прохождение строба С2 .через элемент И 33, Если критической ошибки нет, то элемент НЕ 34 формирует сигнал 1 , разрешая вьщачу через элемент И-НЕ 42 синхросигнала на выход 22, Затем цикл работы повторяется,

На диаграмме 4б показана работа устройства при появлении сигнала 1 на входе 19, В этом случае к моменту появления импульса на выходе элемента И 33 элемент И-НЕ 42 блокирован, а элемент И 36 разблокирован. Сигнал с выхода элемента И 33 проходит на выход 20, через элемент ИЛИ 37 вызьшает сдвиг числа в регистре 40 и по своему спаду переключает в 1 триггер 35, блокируя прохождение очередного строба С1 через элемент И 38, Сигнал с выхода 20 вызывает отключение одного отказавшего РБ, поэтому единичный сигнал на входе 19 снимается, но элемент И 3j6 остается разблокированным сигналом с выхода Q регистра 40, Этот же сиг

66

нал регистра 40 блокирует элемент ИЛИ-НЕ 39, неразрешая переключение в нулевое состояние триггера 35, Снятие сигнала на входе 19 не приводит к разблокированию элемента И-НЕ 42, который теперь блокирован нулевым сигналом с инверсного выхода триггера 35, Второй положительный импульс на входе 18 вызывает сдвиг числа в регистре 40, что вызывает положи- тель.ный перепад сигнала на входе () счетчика 31, который увеличивает свое состояние на единицу и изменяет управляющий код на выходах 2I,

Формируется второй импульс на выходе 20, Сдвиг числа в регистре 40 вызывает блокировку элемента И 36 и снятие блокировки элемента ШШ-НЕ 39 по первому входу. Если по входу 17 элемент ИЛИ-НЕ 39 разблокирован, то очередным спадом импульса на входе 18 триггер . 35 устанавливается в нулевое состояние, разрешая вьщачу стробов на выходе 24, При этом разблокировка элемента И 38 происходит только при отсутствии единичного сигнала на входе 17, чем обеспечивается защита от вьщачи неполного импульса на выходе 24, Цикл отработки критической ошибки заканчивается,

Когда резерв исчерпан, счетчик 31 переходит в состояние, которое выявляется дешифратором 41. Последний вьщает контрольной сигнал на выход 23, а новое состояние счетчика 31 ; переводит второй УПЭ на вьщачу только нул евого сигнала на выходе 19, Цикл повторяется.

Формула изобретения

Адаптивный восстанавливающий орган, Содержащий утервьш управляемый пороговый элемент, информационные

45 входы которого подключены к соответствующим выходам группы элементов И и первым входам соответствующих элементов неравнозначности, управляющие входы - к управляющим выходам блока

50 управления, выход соединен с инфор- -мационным выходом устройства и вто- рьти входами элементов неравнозначности, вход разрешения записи узла фиксации отказов подключен к выходу

55 сигналов перестройки блока управления, а выходы - к первым входам группы элементов И, вторые входы которых соединены с выходами резервных блоков, входы приема сигнала начальной

7129

установки узла фиксации отказов и блока управления и вход приема второго строба блока управления соединен с соответствующими входами устройства, отличающийся тем, что, с целью повышения надежности, в него введены коммутатор и второй управляемый пороговый элемент, причем информационные входы коммутатора подсоединены к соответствующим выходам групп элементов неравнозначности, управляющие входы - к соответствующим выходам узла фиксации отказов, а выходы - к соответ

8

ствующим информационным входам узла фиксации отказов и второго управляемого порогового элемента, управля- юпдие входы которого соединены с управляющими выходами блока управления, а выход - с входом приема сигнала критической ошибки блока управления, вход приема первого строба блока управления подключен к соответстующему входу устройства, выход строба приема - к соответствующим входам резервных блоков, а выход синхросигнала - к соответствующему выходу устройства.

fPU2.1

«,

i

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивное восстанавливающее устройство | 1986 |

|

SU1348837A1 |

| Устройство для коррекции ошибок | 1986 |

|

SU1352490A1 |

| Устройство для контроля и коммутации резервных блоков | 1984 |

|

SU1252782A1 |

| Устройство для восстановления информации в многоканальных вычислительных системах | 1986 |

|

SU1305683A1 |

| Устройство для управления режимом обмена мажоритарно-резервированной системы | 1983 |

|

SU1159182A1 |

| Резервированное устройство | 1991 |

|

SU1785089A1 |

| Резервированное вычислительное устройство | 1983 |

|

SU1200292A1 |

| Резервированная система | 1988 |

|

SU1584137A1 |

| Устройство для контроля программ | 1986 |

|

SU1332323A1 |

| УСТРОЙСТВО ПОИСКА И СЛЕЖЕНИЯ ЗА ШИРОКОПОЛОСНЫМ СИГНАЛОМ | 1981 |

|

SU1840035A1 |

Адаптивный восстанавливающий орган относится к автоматике и вычислительной технике. С целью повышения надежности в устройство, сос- из первого управляемого порогового элемента, информационные входы которого подключены к соответствующим ключам, а управляющие входы - к выходам блока управления порогом, введены коммутатор и второй управляемый пороговый элемент. В устройстве отключение отказавшего блока производится только в том случае, когда его ошибка в сумме с ошибками других блоков образует вектор критической ошибки с кратностью ошибки HS. единицу меньше, чем порог срабатывания первого порогового элемента. Таким образом, от порогового элемента не отключаются резервируемые блоки, отказ которых не приводит к образовании вектора критической ошибки. 4 ил.

я

С2

Н.У.

Фиг.З

| Аппарат для рафинирования расплавленных металлов от нерастворимых примесей | 1980 |

|

SU908883A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Веникодробильный станок | 1921 |

|

SU53A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Чугунный экономайзер с вертикально-расположенными трубами с поперечными ребрами | 1911 |

|

SU1978A1 |

| Построение надежных логических устройств | |||

| М,: Энергия, 1970, с.104 ,I | |||

Авторы

Даты

1987-02-23—Публикация

1984-12-28—Подача