Изобретение относится к вычислительной технике и автоматике и может быть использовано для построения надежных цифровых устройств.

Цель изобретения - повышение надежности резервированного устройства и достоверности его функционирования.

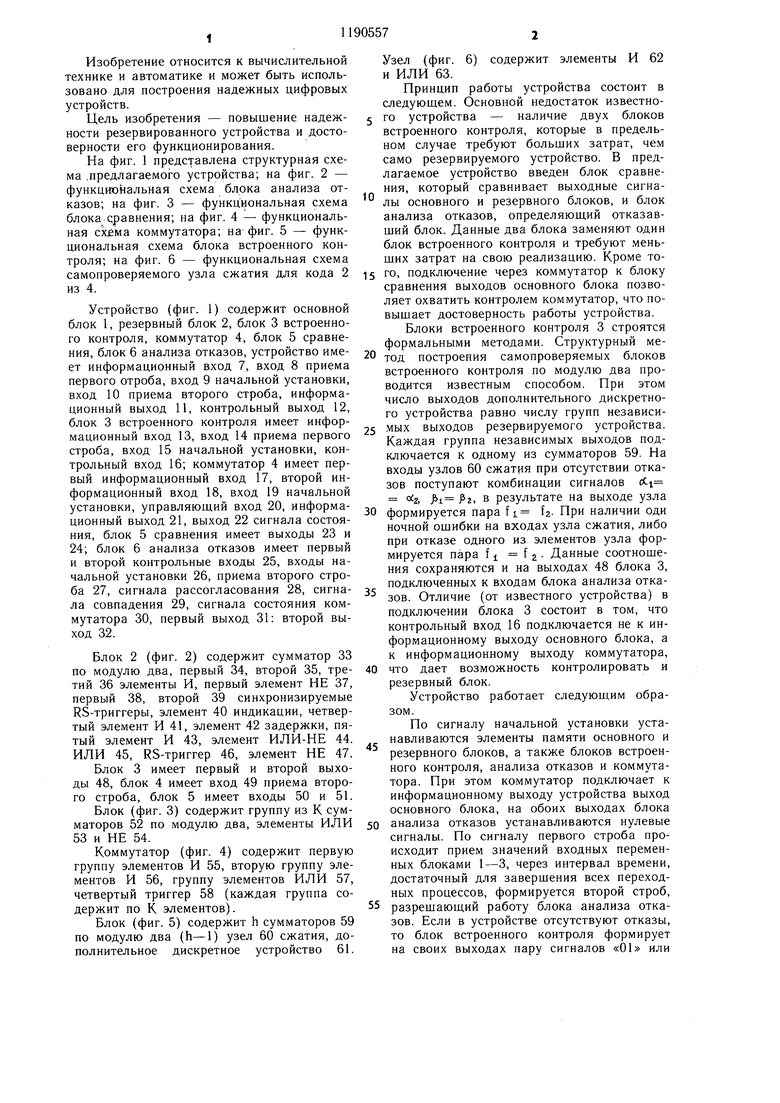

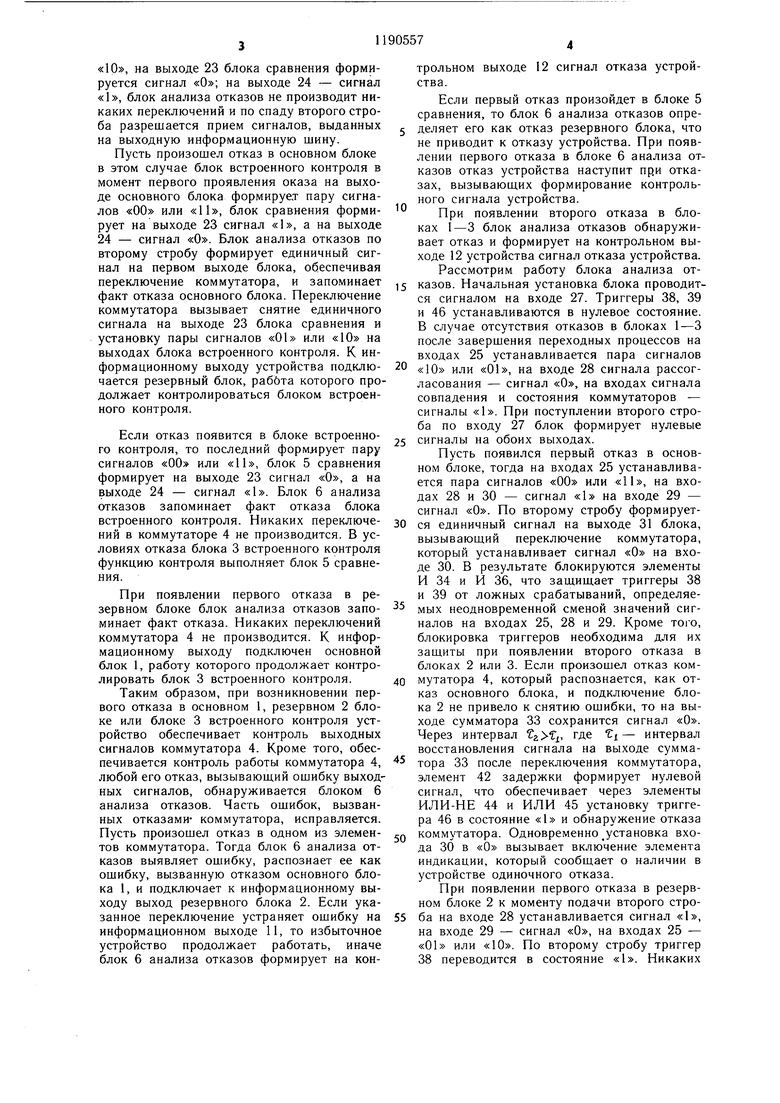

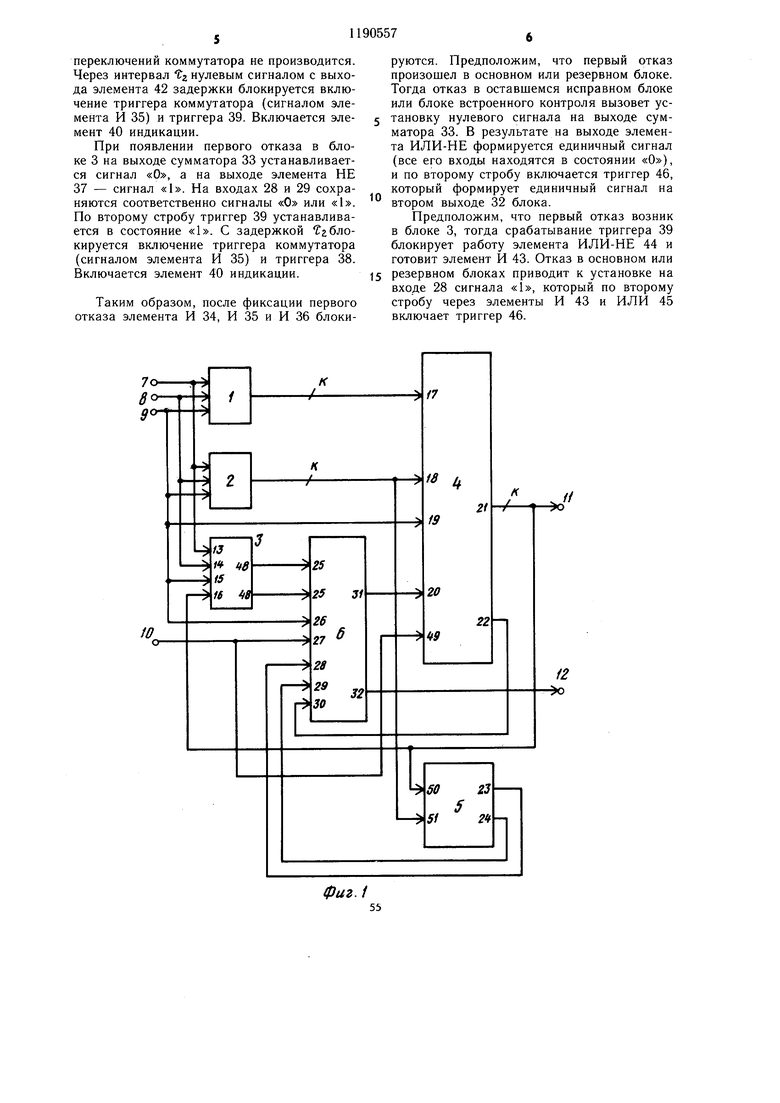

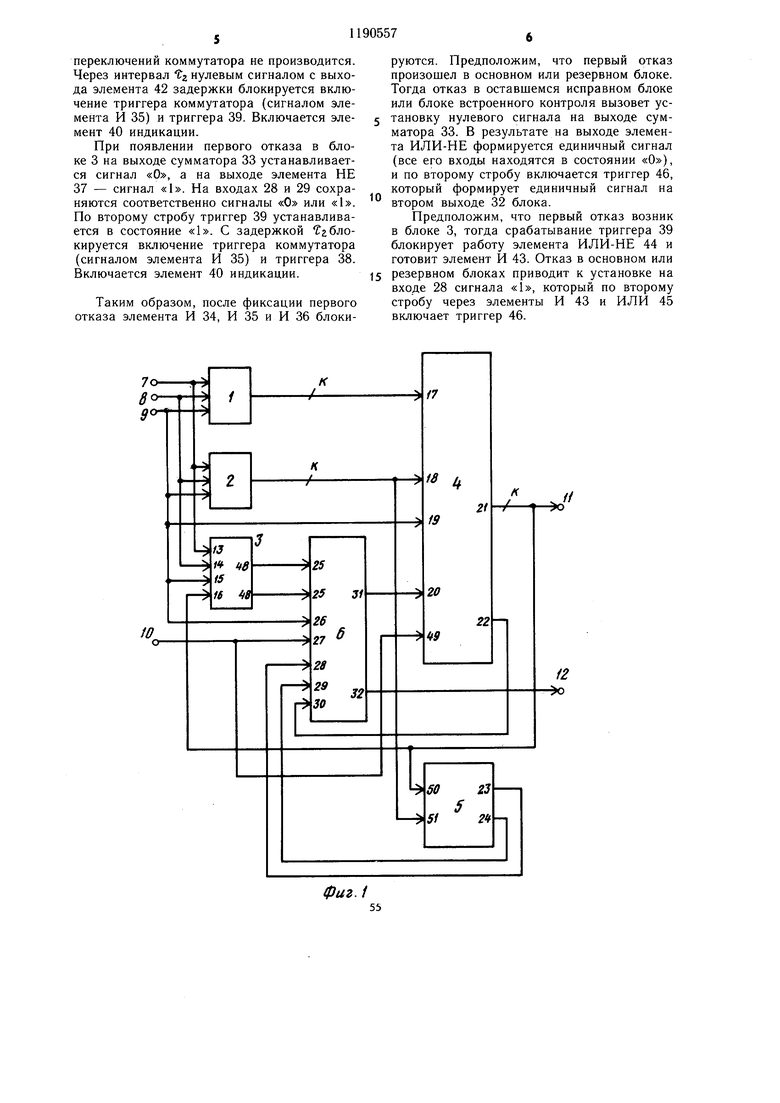

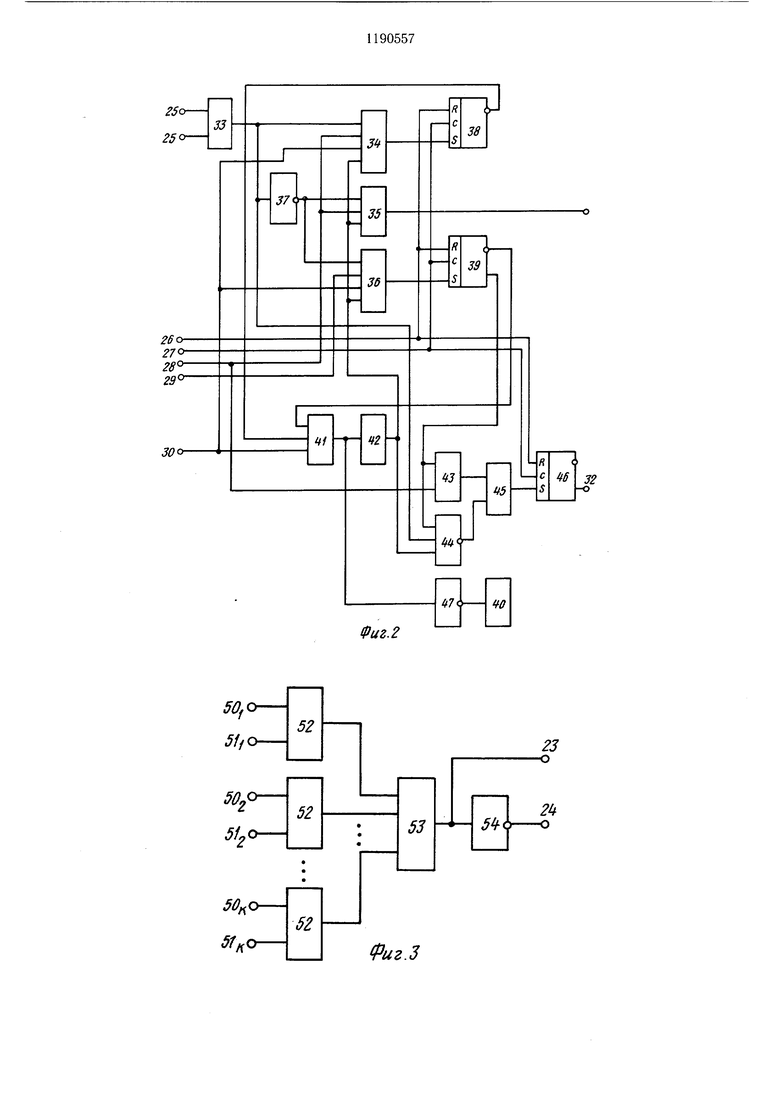

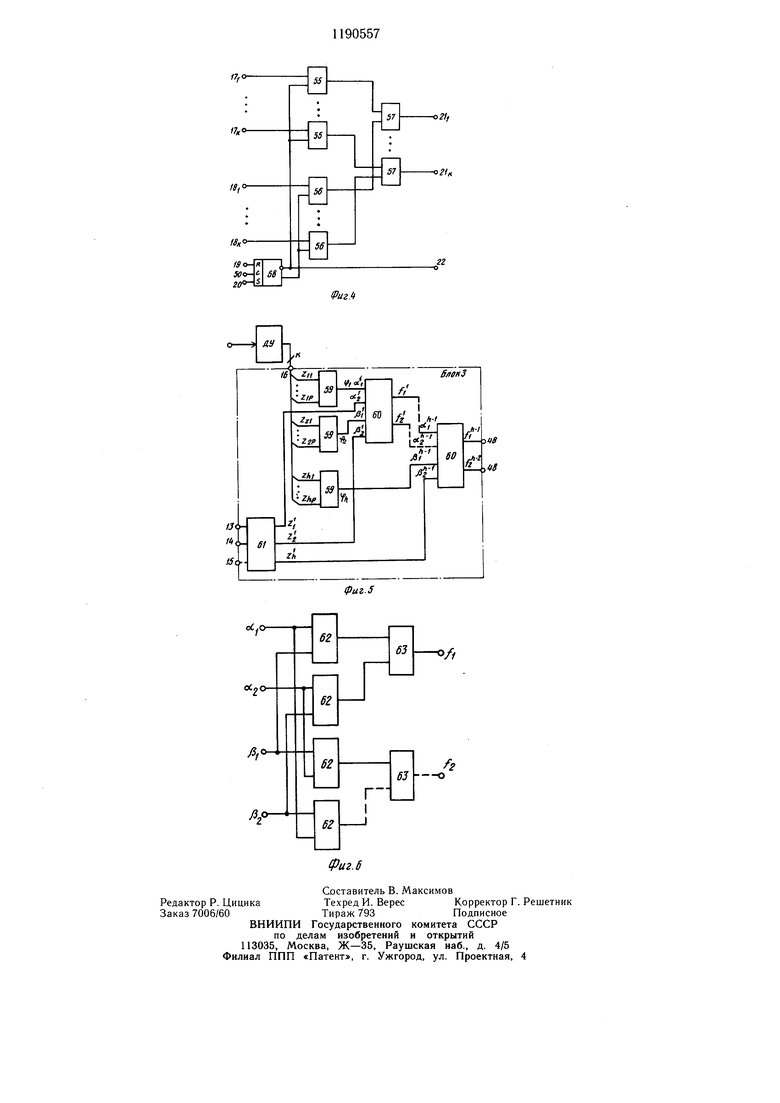

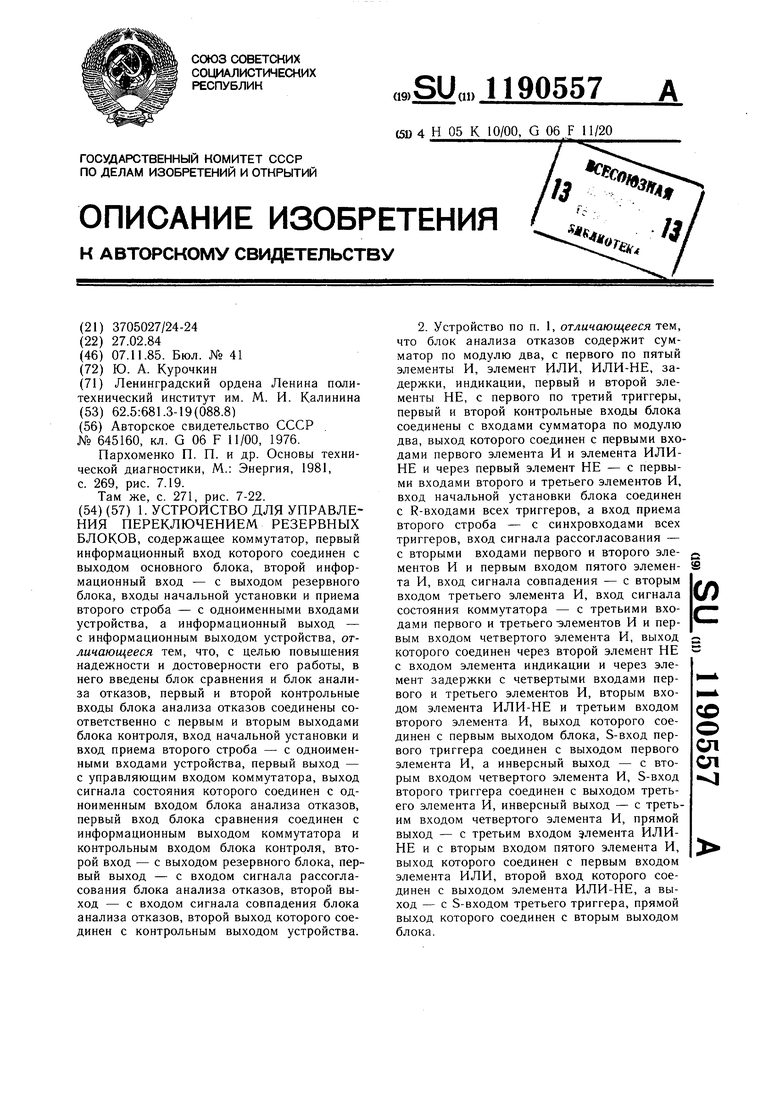

На фиг. 1 представлена структурная схема .предлагаемого устройства; на фиг. 2 - функциональная схема блока анализа отказов; на фиг. 3 - функциональная схема блока сравнения; на фиг. 4 - функциональная схема коммутатора; на фиг. 5 - функциональная схема блока встроенного контроля; на фиг. 6 - функциональная схема самопроверяемого узла сжатия для кода 2 из 4.

Устройство (фиг. 1) содержит основной блок 1, резервный блок 2, блок 3 встроенного контроля, коммутатор 4, блок 5 сравнения, блок 6 анализа отказов, устройство имеет информационный вход 7, вход 8 приема первого отроба, вход 9 начальной установки, вход 10 приема второго строба, информационный выход 11, контрольный выход 12, блок 3 встроенного контроля имеет информационный вход 13, вход 14 приема первого строба, вход 15 начальной установки, контрольный вход 16; коммутатор 4 имеет первый информационный вход 17, второй информационный вход 18, вход 19 начальной установки, управляющий вход 20, информационный выход 21, выход 22 сигнала состояния, блок 5 сравнения имеет выходы 23 и 24; блок 6 анализа отказов имеет первый и второй контрольные входы 25, входы начальной установки 26, приема второго строба 27, сигнала рассогласования 28, сигнала совпадения 29, сигнала состояния коммутатора 30, первый выход 31: второй выход 32.

Блок 2 (фиг. 2) содержит сумматор 33 по модулю два, первый 34, второй 35, третий 36 элементы И, первый элемент НЕ 37, первый 38, второй 39 синхронизируемые RS-триггеры, элемент 40 индикации, четвертый элемент И 41, элемент 42 задержки, пятый элемент И 43, элемент ИЛИ-НЕ 44. ИЛИ 45, RS-триггер 46, элемент НЕ 47.

Блок 3 имеет первый и второй выходы 48, блок 4 имеет вход 49 приема второго строба, блок 5 имеет входы 50 и 51.

Блок (фиг. 3) содержит группу из К сумматоров 52 по модулю два, элементы ИЛИ 53 и НЕ 54.

Коммутатор (фиг. 4) содержит первую группу элементов И 55, вторую группу элементов И 56, группу элементов ИЛИ 57, четвертый триггер 58 (каждая группа содержит по К элементов).

Блок (фиг. 5) содержит h сумматоров 59 по модулю два (h-1) узел 60 сжатия, дополнительное дискретное устройство 61.

Узел (фиг. 6) содержит элементы И 62 и ИЛИ 63.

Принцип работы устройства состоит в следующем. Основной недостаток известного устройства - наличие двух блоков встроенного контроля, которые в предельном случае требуют больщих затрат, чем само резервируемого устройство. В предлагаемое устройство введен блок сравнения, который сравнивает выходные сигналы основного и резервного блоков, и блок анализа отказов, определяющий отказавщий блок. Данные два блока заменяют один блок встроенного контроля и требуют меньщих затрат на свою реализацию. Кроме того, подключение через коммутатор к блоку сравнения выходов основного блока позволяет охватить контролем коммутатор, что повыщает достоверность работы устройства.

Блоки встроенного контроля 3 строятся формальными методами. Структурный метод построения самопроверяемых блоков встроенного контроля по модулю два проводится известным способом. При этом число выходов дополнительного дискретного устройства равно числу групп независимых выходов резервируемого устройства. Каждая группа независимых выходов подключается к одному из сумматоров 59. На входы узлов 60 сжатия при отсутствии отказов поступают комбинации сигналов i , Рг, в результате на выходе узла

0 формируется пара f i fa- При наличии оди ночной ошибки на входах узла сжатия, либо при отказе одного из элементов узла формируется пара f i f 2 Данные соотношения сохраняются и на выходах 48 блока 3, подключенных к входам блока анализа отказов. Отличие (от известного устройства) в подключении блока 3 состоит в том, что контрольный вход 16 подключается не к информационному выходу основного блока, а к информационному выходу коммутатора,

что дает возможность контролировать и резервный блок.

Устройство работает следующим образом.

По сигналу начальной установки устанавливаются элементы памяти основного и резервного блоков, а также блоков встроенного контроля, анализа отказов и коммутатора. При этом коммутатор подключает к информационному выходу устройства выход основного блока, на обоих выходах блока

0 анализа отказов устанавливаются нулевые сигналы. По сигналу первого строба происходит прием значений входных переменных блоками 1-3, через интервал времени, достаточный для заверщения всех переходных процессов, формируется второй строб,

5 разрешающий работу блока анализа отказов. Если в устройстве отсутствуют отказы, то блок встроенного контроля формирует на своих выходах пару сигналов «01 или

«10, на выходе 23 блока сравнения формируется сигнал на выходе 24 - сигнал «1, блок анализа отказов не производит никаких переключений и по спаду второго строба разрешается прием сигналов, выданных на выходную информационную шину.

Пусть произошел отказ в основном блоке в этом случае блок встроенного контроля в момент первого проявления оказа на выходе основного блока формирует пару сигналов «00 или «11, блок сравнения формирует на выходе 23 сигнал «1, а на выходе 24 - сигнал «О. Блок анализа отказов по второму стробу формирует единичный сигнал на первом выходе блока, обеспечивая переключение коммутатора, и запоминает факт отказа основного блока. Переключение коммутатора вызывает снятие единичного сигнала на выходе 23 блока сравнения и установку пары сигналов «01 или «10 на выходах блока встроенного контроля. К информационному выходу устройства подключается резервный блок, раббта которого продолжает контролироваться блоком встроенного контроля.

Если отказ появится в блоке встроенного контроля, то последний форм.ирует пару сигналов «00 или «11, блок 5 сравнения формирует на выходе 23 сигнал «О, а на выходе 24 - сигнал «1. Блок 6 анализа отказов запоминает факт отказа блока встроенного контроля. Никаких переключений в коммутаторе 4 не производится. В условиях отказа блока 3 встроенного контроля функцию контроля выполняет блок 5 сравнения.

При появлении первого отказа в резервном блоке блок анализа отказов запоминает факт отказа. Никаких переключений коммутатора 4 не производится. К информационному выходу подключен основной блок 1, работу которого продолжает контролировать блок 3 встроенного контроля.

Таким образом, при возникновении первого отказа в основном 1, резервном 2 блоке или блоке 3 встроенного контроля устройство обеспечивает контроль выходных сигналов коммутатора 4. Кроме того, обеспечивается контроль работы коммутатора 4, любой его отказ, вызывающий ошибку выходных сигналов, обнаруживается блоком 6 анализа отказов. Часть ошибок, вызванных отказами- коммутатора, исправляется. Пусть произошел отказ в одном из элементов коммутатора. Тогда блок 6 анализа отказов выявляет ошибку, распознает ее как ошибку, вызванную отказом основного блока 1, и подключает к информационному выходу выход резервного блока 2. Если указанное переключение устраняет ошибку на информационном выходе 11, то избыточное устройство продолжает работать, иначе блок 6 анализа отказов формирует на контрольном выходе 12 сигнал отказа устройства.

Если первый отказ произойдет в блоке 5 сравнения, то блок 6 анализа отказов определяет его как отказ резервного блока, что не приводит к отказу устройства. При появлении первого отказа в блоке 6 анализа отказов отказ устройства наступит пр.и отказах, вызывающих формирование контрольного сигнала устройства.

При появлении второго отказа в блоках 1-3 блок анализа отказов обнаруживает отказ и формирует на контрольном выходе 12 устройства сигнал отказа устройства. Рассмотрим работу блока анализа отказов. Начальная установка блока проводится сигналом на входе 27. Триггеры 38, 39 и 46 устанавливаются в нулевое состояние. В случае отсутствия отказов в блоках 1-3 после завершения переходных процессов на входах 25 устанавливается пара сигналов

0 «10 или «01, на входе 28 сигнала рассогласования - сигнал «О, на входах сигнала совпадения и состояния коммутаторов - сигналы «1. При поступлении второго строба по входу 27 блок формирует нулевые

5 сигналы на обоих выходах.

Пусть появился первый отказ в основном блоке, тогда на входах 25 устанавливается пара сигналов «00 или «11, на входах 28 и 30 - сигнал «1 на входе 29 - сигнал «О. По второму стробу формируется единичный сигнал на выходе 31 блока, вызывающий переключение коммутатора, который устанавливает сигнал «О на входе 30. В результате блокируются элементы И 34 и И 36, что защищает триггеры 38 и 39 от ложных срабатываний, определяемых неодновременной сменой значений сигналов на входах 25, 28 и 29. Кроме того, блокировка триггеров необходима для их защиты при появлении второго отказа в блоках 2 или 3. Если произошел отказ коммутатора 4, который распознается, как отказ основного блока, и подключение блока 2 не привело к снятию ошибки, то на выходе сумматора 33 сохранится сигнал «О. Через интервал , где Ci- интервал восстановления сигнала на выходе сумматора 33 после переключения коммутатора, элемент 42 задержки формирует нулевой сигнал, что обеспечивает через элементы ИЛИ-НЕ 44 и ИЛИ 45 установку триггера 46 в состояние «1 и обнаружение отказа

Q коммутатора. Одновременно установка входа 30 в «О вызывает включение элемента индикации, который сообщает о наличии в устройстве одиночного отказа.

При появлении первого отказа в резервном блоке 2 к моменту подачи второго строба на входе 28 устанавливается сигнал «1, на входе 29 - сигнал «О, на входах 25 - «01 или «10. По второму стробу триггер 38 переводится в состояние «1. Никаких

переключений коммутатора не производится. Через интервал t нулевым сигналом с выхода элемента 42 задержки блокируется включение триггера коммутатора (сигналом элемента И 35) и триггера 39. Включается элемент 40 индикации.

При появлении первого отказа в блоке 3 на выходе сумматора 33 устанавливается сигнал «О, а на выходе элемента НЕ 37 - сигнал «1. На входах 28 и 29 сохраняются соответственно сигналы «О или «1. По второму стробу триггер 39 устанавливается в состояние «1. С задержкой Тг блокируется включение триггера коммутатора (сигналом элемента И 35) и триггера 38. Включается элемент 40 индикации.

Таким образом, после фиксации первого отказа элемента И 34, И 35 и И 36 блоки70

фаг.1

руются. Предположим, что первый отказ произошел в основном или резервном блоке. Тогда отказ в оставшемся исправном блоке или блоке встроенного контроля вызовет установку нулевого сигнала на выходе сумматора 33. В результате на выходе элемента ИЛИ-НЕ формируется единичный сигнал (все его входы находятся в состоянии «О), и по второму стробу включается триггер 46, который формирует единичный сигнал на втором выходе 32 блока.

Предположим, что первый отказ возник в блоке 3, тогда срабатывание триггера 39 блокирует работу элемента ИЛИ-НЕ 44 и готовит элемент И 43. Отказ в основном или резервном блоках приводит к установке на входе 28 сигнала «1, который по второму стробу через элементы И 43 и ИЛИ 45 включает триггер 46.

ZSo335o

FiJ

38

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля и коммутации резервных блоков | 1984 |

|

SU1252782A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ДИНАМИЧЕСКИМ РЕЗЕРВИРОВАНИЕМ | 1990 |

|

RU2028677C1 |

| Устройство для коррекции ошибок | 1986 |

|

SU1352490A1 |

| Устройство для управления переключением резервных блоков | 1982 |

|

SU1091168A1 |

| УСТРОЙСТВО РЕЗЕРВИРОВАНИЯ РАДИОПЕРЕДАТЧИКА С ДИНАМИЧЕСКОЙ ЗАДЕРЖКОЙ | 2002 |

|

RU2221332C1 |

| Дублированная вычислительная система | 1990 |

|

SU1783528A1 |

| Устройство для управления переключением резервных блоков | 1989 |

|

SU1635186A1 |

| Адаптивный восстанавливающий орган | 1984 |

|

SU1292216A1 |

| МОДУЛЬНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2011 |

|

RU2474868C1 |

| Измерительная система с автоматическим контролем аналого-цифрового преобразования и блок задания нечувствительности | 1991 |

|

SU1837261A1 |

1.УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ПЕРЕКЛЮЧЕНИЕМ РЕЗЕРВНЫХ БЛОКОВ, содержащее коммутатор, первый информационный вход которого соединен с выходом основного блока, второй информационный вход - с выходом резервного блока, входы начальной установки и приема второго строба - с одноименными входами устройства, а информационный выход - с информационным выходом устройства, отличающееся тем, что, с целью повышения надежности и достоверности его работы, в него введены блок сравнения и блок анализа отказов, первый и второй контрольные входы блока анализа отказов соединены соответственно с первым и вторым выходами блока контроля, вход начальной установки и вход приема второго строба - с одноименными входами устройства, первый выход - с управляющим входом коммутатора, выход сигнала состояния которого соединен с одноименным входом блока анализа отказов, первый вход блока сравнения соединен с информационным выходом коммутатора и контрольным входом блока контроля, второй вход - с выходом резервного блока, первый выход - с входом сигнала рассогласования блока анализа отказов, второй выход - с входом сигнала совпадения блока анализа отказов, второй выход которого соединен с контрольным выходом устройства. 2. Устройство по п. 1, отличающееся тем, что блок анализа отказов содержит сумматор по модулю два, с первого по пятый элементы И, элемент ИЛИ, ИЛИ-НЕ, задержки, индикации, первый и второй элементы НЕ, с первого по третий триггеры, первый и второй контрольные входы блока соединены с входами сумматора по модулю два, выход которого соединен с первыми входами первого элемента И и элемента ИЛИНЕ и через первый элемент НЕ - с первыми входами второго и третьего элементов И, вход начальной установки блока соединен с R-входами всех триггеров, а вход приема второго строба - с синхровходами всех триггеров, вход сигнала рассогласования - с вторыми входами первого и второго эле ментов И и первым входом пятого элемента И, вход сигнала совпадения - с вторым (Л входом третьего элемента И, вход сигнала состояния коммутатора - с третьими входами первого и третьего элементов И и первым входом четвертого элемента И, выход которого соединен через второй элемент НЕ с входом элемента индикации и через элемент задержки с четвертыми входами первого и третьего элементов И, вторым входом элемента ИЛИ-НЕ и третьим входом со о сд второго элемента И, выход которого соединен с первым выходом блока, S-вход первого триггера соединен с выходом первого 01 элемента И, а инверсный выход - с вторым входом четвертого элемента И, S-вход второго триггера соединен с выходом третьего элемента И, инверсный выход - с третьим входом четвертого элемента И, прямой выход - с третьим входом элемента ИЛИНЕ и с вторым входом пятого элемента И, выход которого соединен с первым входом элемента ИЛИ, второй вход которого соединен с выходом элемента ИЛИ-НЕ, а выход - с S-входом третьего триггера, прямой выход которого соединен с вторым выходом блока.

- / of70f °29

m

30 or505ff(

50 5io

t6

«J

32

45

470 40

Фиг.2

а

«J

tfj

| Авторское свидетельство СССР | |||

| Устройство для указания неисправности в дублированных дискретных автоматах | 1976 |

|

SU645160A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Пархоменко П | |||

| П | |||

| и др | |||

| Основы технической диагностики, М.: Энергия, 1981, с | |||

| Нож для надрезывания подошвы рантовой обуви | 1917 |

|

SU269A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Там же, с | |||

| Искроудержатель для паровозов | 1920 |

|

SU271A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

Авторы

Даты

1985-11-07—Публикация

1984-02-27—Подача