1

Изобретение относится к вычислительной и контрольно-измерительной технике и может быть использовано при разработке автоматизированных систем контроля цифровых узлов различной радиоэлектронной аппаратуры.

Известна система контроля цифровых узлов АТ5 -960, содержащая управляющую вычислительную машину, соединенную с устройством ввода-вывода и через устройство управления с устройством функциональной проверки, подключенным к объекту контроля, а также коммутаторы, блоки измерителей, источники питания и блоки управления, причем устройство функциональной проверки содержит блоки согласования, состоящие из регистра установок, компараторов и ключей.

Однако эта система характеризуется повышенной сложностью и обладает ограниченным быстродействием ij .

Наиболее близкой по технической сущности к изобретению является сист« 1а для контроля электрических параметров

цифровых узлов, содержащая вычислитель, блок ввода-вывода, блок сопряжения, блоки согласования, блок управления, цифроаналоговые преобразователи, блоки памяти, элементы И, компараторы, регистры установок и коммутаторы 2 J .

Недостатком известной системы являются ограниченные функциональные возможности, обусловленные тем, что в этой системе для организации диагности10ки неисправностей цифровых узлов (поиск отказавших элементов узлов с заданной глубиной поиска) необходимо составлять проверочные тесты, диагностирующие неисправность, которые требуют дополни15тельного объема памяти на несколько порядков большего, чем объем памяти, необходимых для хранения проверочных тестов, обнаруживающих неисправность на выходах цифровых узлов, что делает

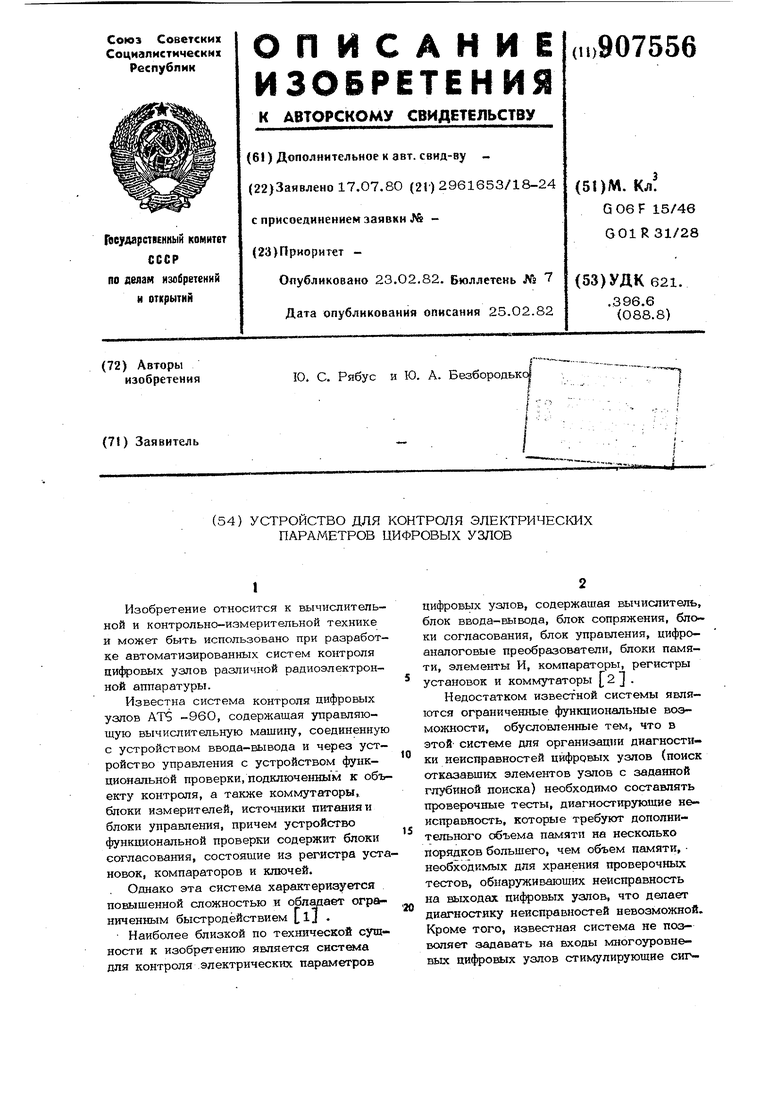

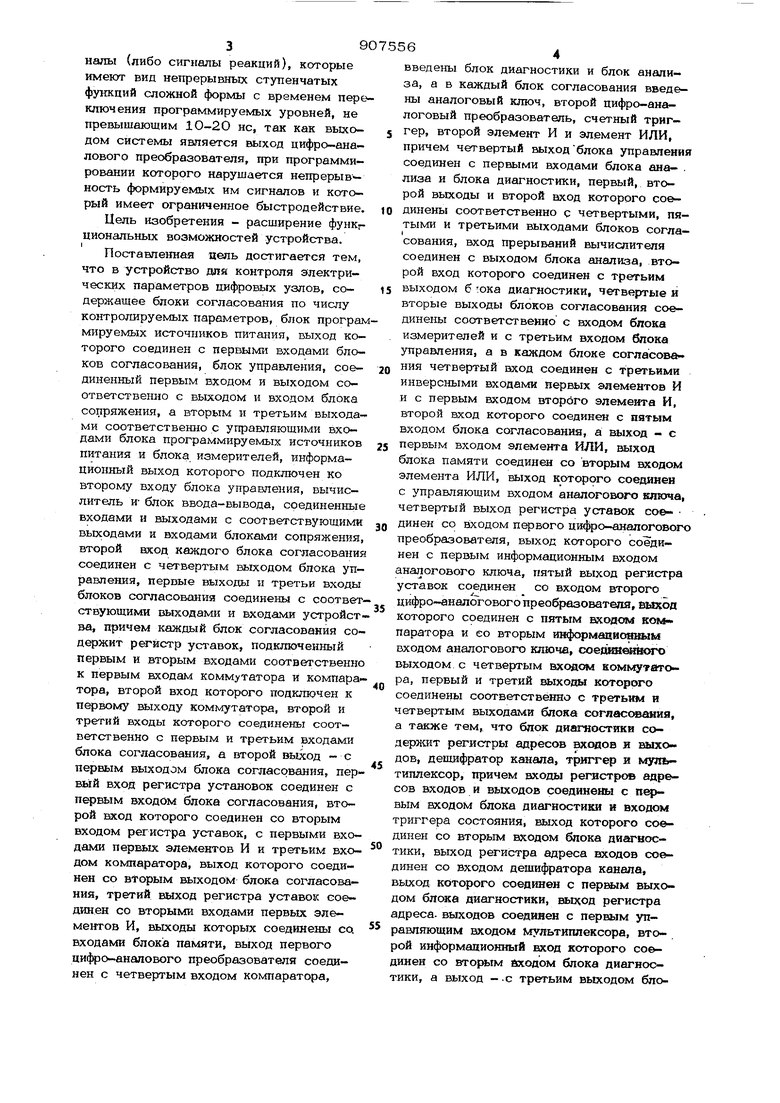

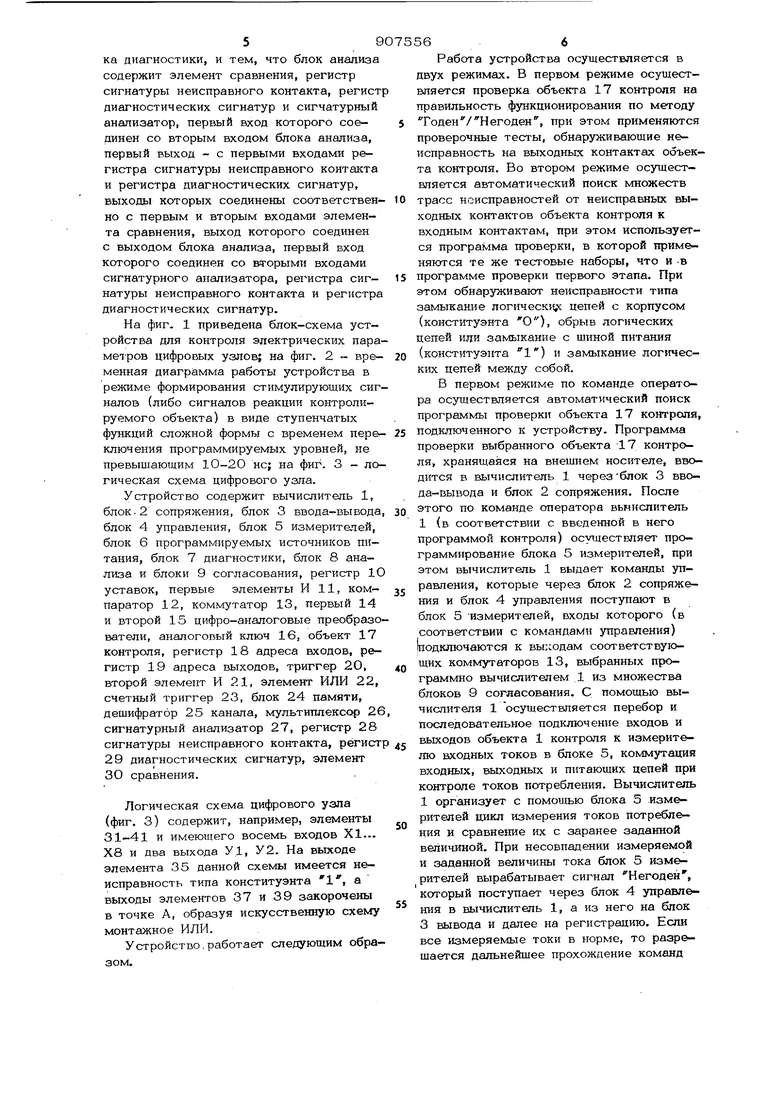

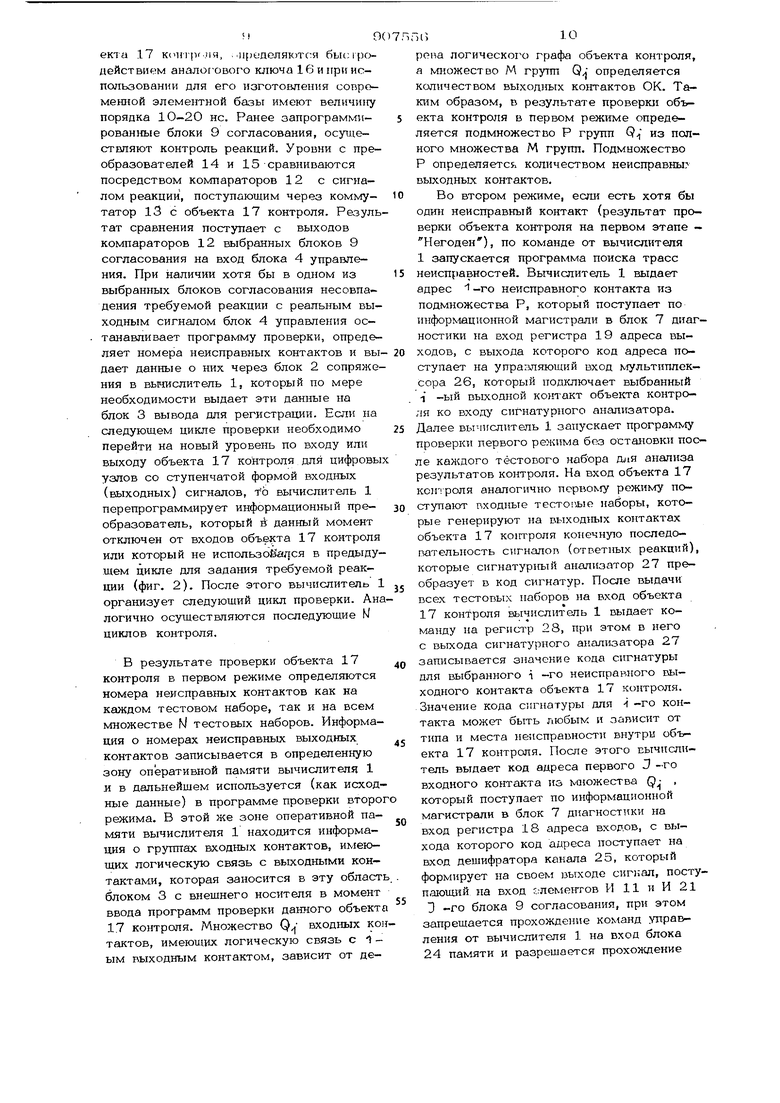

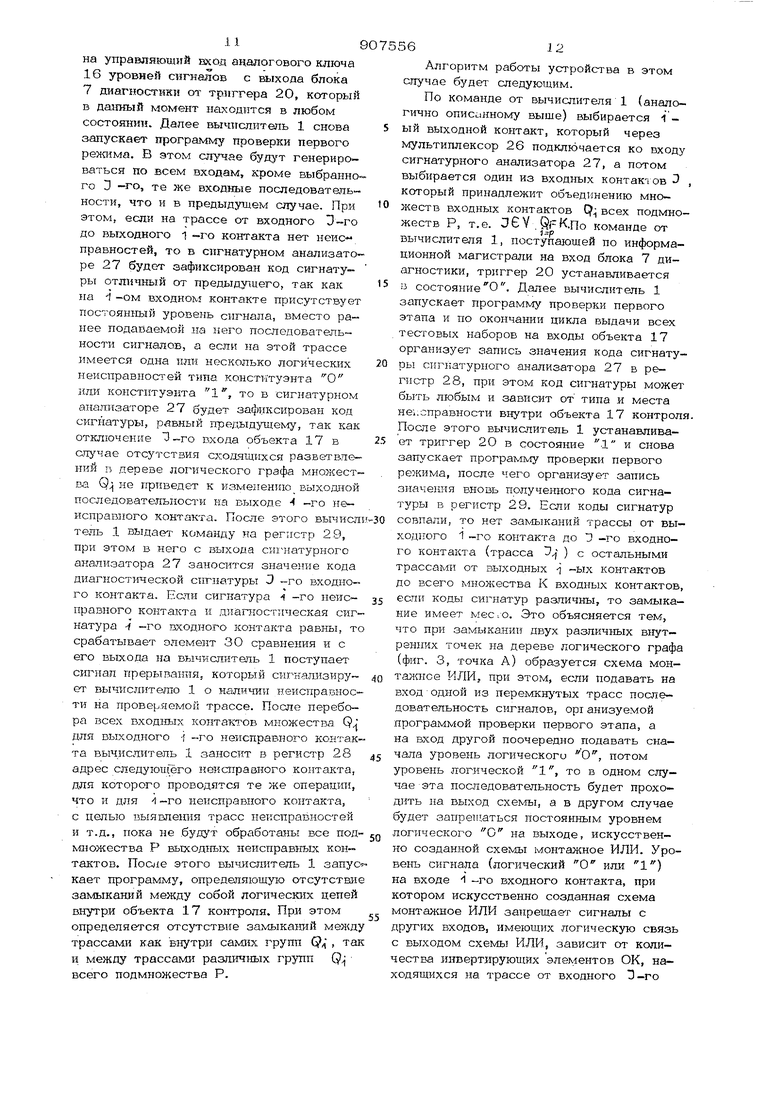

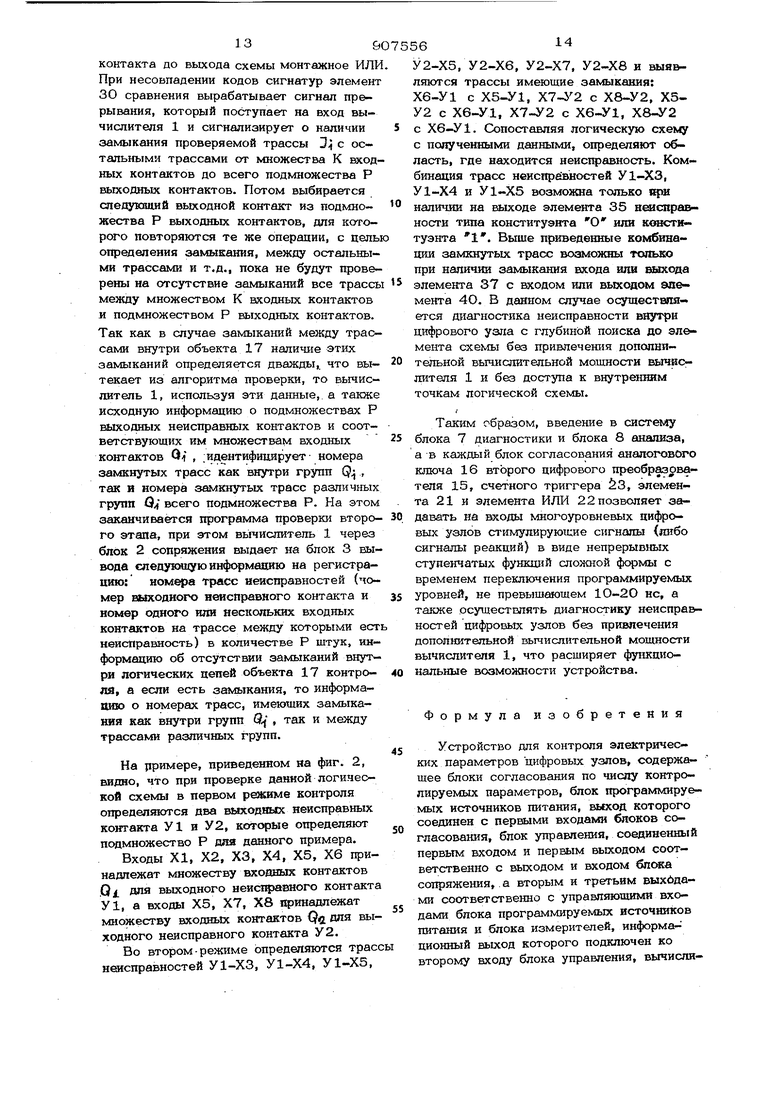

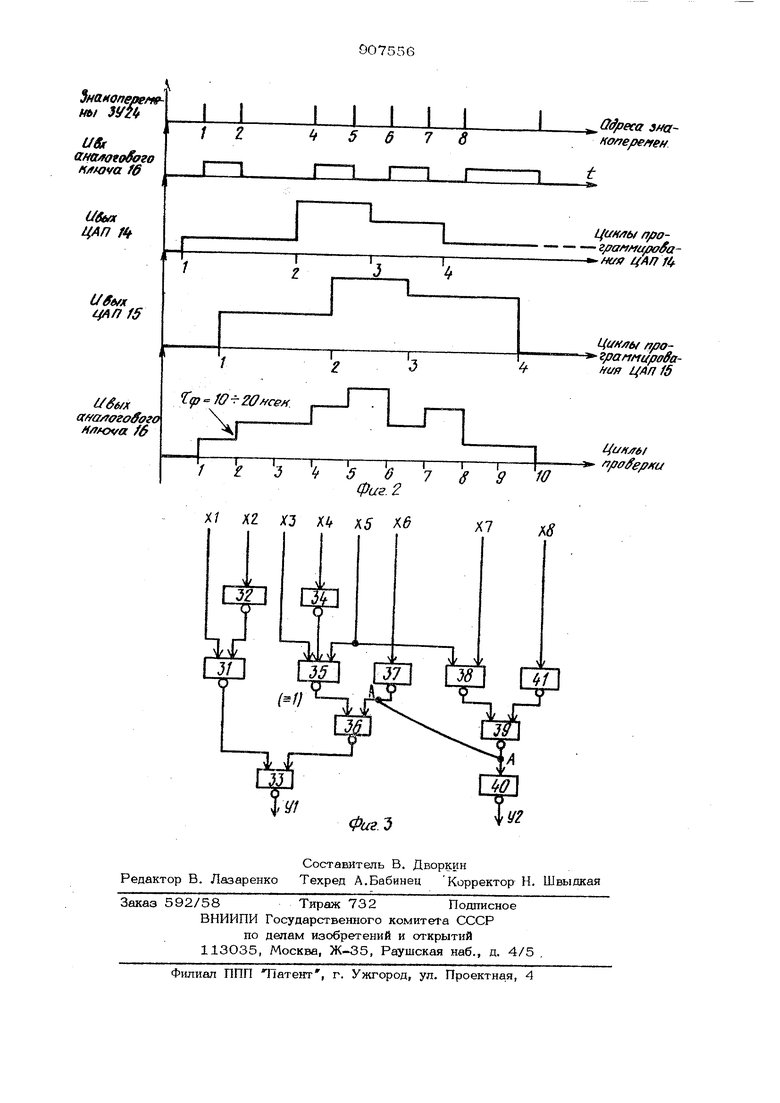

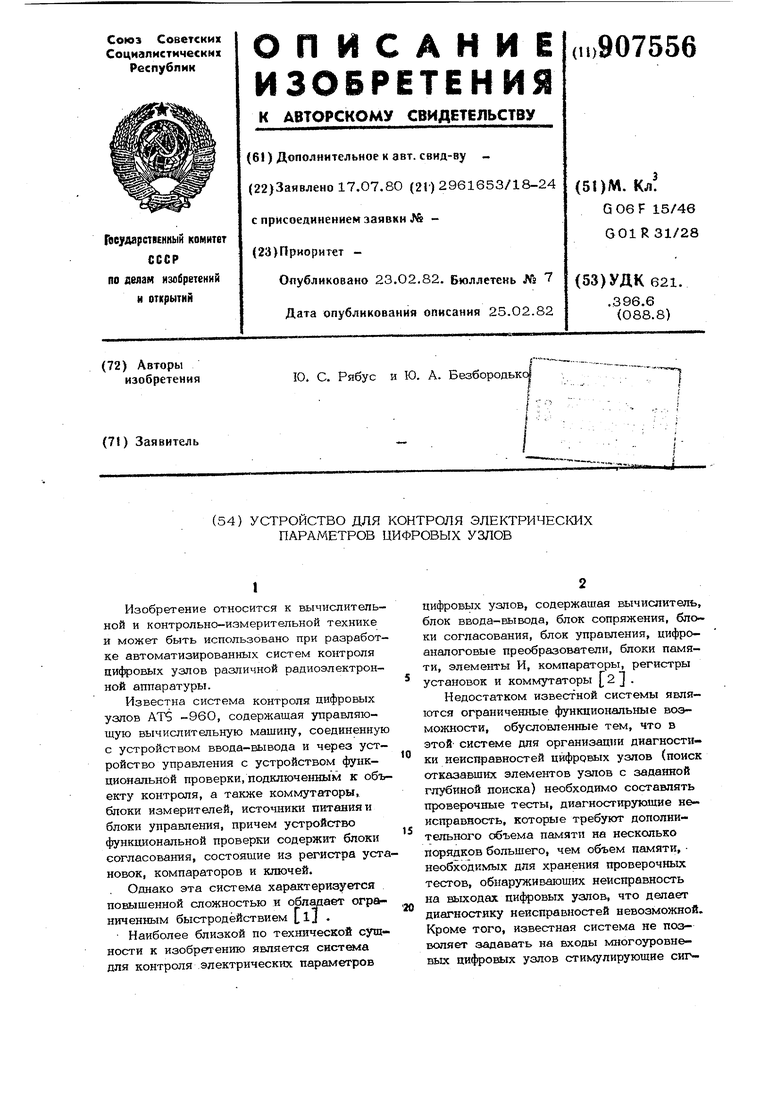

20 диагностику неисправностей невозможной.. Кроме того, известная система не позволяет задавать на входы многоуровневых цифровых узлов стимулирующие сигналы (либо сигналы реакций), которые имеют вид непрерывных ступенчатых функций сложной формы с временем переключения программируемых уровней, не превышающим 10-2О не, так как выходом системы является выход цифро-ана- лового преобразователя, при программировании которого нарушается непрерывность формируемых им сигналов и который имеет ограниченное быстродействие. Цель Изобретения - расширение функгциональных возможностей устройства. Поставленная цель достигается тем, что в устройство для контроля электрических параметров цифровых узлов, содержащее блоки согласования по числу контролируемьзх параметров, блок програм мируемых источников питания, выход которого соединен с первыми входами блоков согласования, блок управления, соединенный первым входом и выходом соответствешю с выходом и входом блока сопряжения, а вторым и третьим выходами соответственно с управляющими входами блока программируемых источников питания и блока, измерителей, информационный выход которого подключен ко второму входу блока управления, вычислитель и- блок ввода-вывода, соединенные входами и выходами с соответствующими выходами и входами блоками сопряжения второй вход каждого блока согласования соединен с четвертым выходом блока управления, первые выходы и третьи входы блоков согласования соединены с соответ ствующими выходами и входами устройст ва, причем каждый блок согласования содержит регистр уставок, подключенный первым и вторым входами соответственно к первым входам коммутатора и компара тора, второй вход которого подключен к первому Шзтходу коммутатора, второй и третий входы которого соединены соответственно с первым и третьим входами блока согласования, а второй выход - с первым выходом блока согласования, пер вый вход регистра установок соединен с первым входом блока согласования, второй вход которого соединен со вторым входом регистра уставок, с первыми входами первых элементов И и третьим входом компаратора, выход которого соединен со вторым выходом блока согласования, третий выход регистра уставок соединен со вторыми входами первых элементов И, выходы которых соединены со. входами блока памяти, выход первого цифро-аналового преобразователя соединен с четвертым входом компаратора. введены блок диагностики и блок анализа, а в каждый блок согласования введены аналоговый ключ, второй цифро-аналоговый преобразователь, счетный триггер, второй элемент И и элемент ИЛИ, причем четвертый блока управления соединен с первыми входами блока ана- . лиза и блока диагностики, первый, второй выходы и второй вход которого соединены соответственно с четвертыми, пятыми и третьими выходами блоков согласования, вход прерываний вычислителя соединен с выходом блока анализа, второй вход которого соединен с третьим выходом б -ока диагностики, четвертые и вторые выходы блоков согласования соединены соответственно с входом блока измерителей и с третьим входом блока управления, а а каждом блоке согласования четвертый вход соединен с третьими инверсными входами первых элементов И и с первым входом второго элемента И, второй вход которого соединен с пятым входом блока согласования, а выход - с первым входом элемента ИЛИ, выход блока памяти соединен со вторым входом элемента ИЛИ, выход которого соединен с управляющим входом аналогового ключа, четвертый выход регистра уставок со&- дин ей со входом пфвого цифро-аналогового преобразователя, выход которого соединен с первым информационным входом аналогового ключа, пятый выход регистра уставок соединен со входом второго цифро-аналогового преобразователя, вьтод которого соединен с пятым входом компаратора и со вторым информааиошшм вход см аналогового ключа, соешш аиого выходом с четвертым вхоаом комк татора, первый и третий аыходы которого соединены соответственно с третьим и четвертым выходами блока согпвссяаемяя, а также тем, что блок диагностики содержит регистры адресов вхсщов и выходов, дешифратор канала, триггер и мультиплексор, причем входы регистров адресов входов и выходов соединены с первым входом блока диагностики и входом триггера состояния, выход которого соединен со вторьшг входом блока диагностики, выход регистра адреса ЕЖОДОВ соединен со входом дешифратора канала, выход которого соединен с перилм выходом блсжа диагностики, выход регистра адреса, выходов соединен с первым управляющим входом Мультиплексора, второй информационный вход которого соединен со BTOfSjiM йходом блока диагностики, а выход -.с третьим выходом блока диагностики, и тем, что блок анализа содержит элемент сравнения, регистр сигнатуры неисправного контакта, регист диагностических сигнатур и сигчатурный анализатор, первый вход которого сое- динен со вторым входом блока анализа, первый выход - с первыми входами регистра сигнатуры неисправного контакта и регистра диагностических сигнатур, выходы которых соединены соответствен но с первым и вторым входами элемента сравнения, выход которого соединен с выходом блока анализа, первый вход которого соединен со вторыми входами сигнатурного анализатора, регистра сигнатуры неисправного контакта и регистра диагностических сигнатур. На фиг. 1 приведена блок-схема устройства для контроля электрических пара метров цифровых узлов; на фиг. 2 - временная диаграмма работы устройства в режиме формирования стимулирующих сиг налов (либо сигналов реакции контролируемого объекта) в виде ступенчатых функций сложной формы с временем переключения программируемых уровней, не превышающим 10-2О не; на фиг, 3 - логическая схема цифрового узла. Устройство содержит вычислитель 1, блок-2 сопряжения, блок 3 ввода-вывода блок 4 управления, блок 5 измерителей, блок 6 программируемых источников питания, блок 7 диагностики, блок 8 анализа и блоки 9 согласования, регистр 1О уставок, первые элементы И 11, ком- паратор 12, коммутатор 13, первый 14 и второй 15 цифро-аналоговые преобразо ватели, аналоговый ключ 16, объект 17 контроля, регистр 18 адреса входов, регистр 19 адреса выходов, триггер 20, второй элемент И 21, элемент ИЛИ 22, счетный триггер 23, блок 24 памяти, дешифратор 25 канала, мультиплексор 26 сигнатурный анализатор 27, регистр 28 сигнатуры неисправного контакта, регист 29диагностических сигнатур, элемент 30сравнения. Логическая схема цифрового узла (фиг. 3) содержит, например, элементы 31-41 и имеющего восемь входов XI... Х8 и два выхода У1, У2. На выходе элемента 35 данной схемы имеется не исправность типа конституэнта , а выходы элементов 37 и 39 закорочены в точке А, образуя искусственную схему монтажное ИЛИ. Устройство.работает следующим образом. Работа устройства осуществляется в двух режимах. В первом режиме осуществляется проверка объекта 17 контроля на правильность функционирования по методу Годен/ Негоден, при этом применяются проверочные тесты, обнаруживающие неисправность на выходных контактах объекта контроля. Во втором режиме осуществляется автоматический поиск множеств трасс неисправностей от неисправных выходных контактов объекта контроля к входным контактам, при этом используется программа проверки, в которой применяются те же тестовые наборы, что и В программе проверки первого этапа. При этом обнаруживают неисправности типа замыкание логически с цепей с корпусом (конституэнта О), обрыв логических цепей или замыкание с щиной питания (конституэнта 1) и замыкание логических цепей между собой. В первом режиме по команде оператора осуществляется автоматический поиск программы проверки объекта 17 контроля, подключенного к устройству. Программа проверки выбранного объекта 17 контроля, хранящаяся на внещнем носителе, вводится в вычислитель 1 через блок 3 ввода-вывода и блок 2 сопряжения. После этого по команде оператора вьнислитель 1 (в соответствии с введенной в него программой контроля) осуществляет программирование блока 5 измерителей, при этом вычислитель 1 выдает команды управления, которые через блок 2 сопряжения и блок 4 управления поступают в блок 5 -измерителей, входы которого (в соответствии с командами управления) подключаются к выходам соответствующих коммутаторов 13, выбранных программно вычислителем 1 из множества блоков 9 согласования. С помощью вычислителя 1 осуществляется перебор и последовательное подключение входов и выходов объекта 1 контроля к измерителю входных токов в блоке 5, коммутация входных, выходных и питающих цепей при контроле токов потребления. Вычислитель 1 организует с помощью блока 5 измерителей цикл измерения токов потребления и сравнегше их с заранее заданной величиной. При несовпадении измеряемой и заданной величины тока блок 5 измерителей вырабатывает сигнал Негоден, который поступает через блок 4 управления в вычислитель 1, а из него на блок 3 вывода и далее на регистрацию. Если все измеряемые токи в норме, то разрещается далънеШиее прохождение команд программы. Далее вычислитель 1 осуществляет программирование блоков 9 согласования и блока 6. Программирование блоков 9 согласования осуществля ется следующим образом: вычислитель 1 через блок 2 сопряжения и блок 4 управ ления по ии(|юрмашюнной магистрали вы дает коды управления, которые фиксиру- ет регистр 10 уставок, определяя состояние элементов блоков 9 согласования а именно, комму1атора 13, компаратора 12, двух цифро-аналоговых преобразователей 14 и 15, которые преобразуют коды, поступающие с регистра 10 уставок в аналоговые уровни. Для двухуровневых цифровых узлов программирование преобразователей 14 и 15 вычислитель осуществляет один раз перед началом проверки объекта 17 контроля, при этом аналоговые уровни преобразователей 14 и 15 устанавливаются равзлз1ми соответственно уровням логической 1 и О для данного объекта 17 контроля и не иа.лёняются до конца проверки. Для многоуровневых цифровых узлов, стимулирую щие сигналы (либо сигналы реакций) которых должны быть заданы в виде непрерывных ступенчатых функций сложной формы (фиг. 2), нрохраммирование преоб разователей 14 и 15 во время проверки объекта контроля происходит несколько раз в зависимости от формы требуемой ступенчатой функции. В зависимости от управляющих сигналов, поступающих с ре гистра 10 уставок, коммутатор 13 подключает к объекту 17 контроля либо сигнальный вход компаратора 12, либо 1 выход аналогового ключа 16. Соответствен- но данный блок согласования в дальнейщем (до перепрограммирования) осущест- впяет либо контроль сигнала, либо его генерирование. После этого вычислитель 1 через блок 2 сопряжения и блок 4 управления и через элементы И 11 соответствующих блоков 9 согласования, выбираемых из их Кшожества для данной проверки, осуществляет последовательную запись информации, соответствующей испытательной программе контроля, в бпок 24 памяти всех выбранных блоков 9 согласования. Блок 24 памяти представляет собой, например, ОЗУ с произвольной выборкой. Вследствие того, что выход блока 24 памяти соединен со входом счетного триггера 23, информация в ячейки блока 24 памяти записывается в впде знакоперемеп, т.е. в ячейки памяти с адресами, соответствующими номерам тестовых наборов, на которых догок™ S8 но произойти изменение состояния, записываются единицы, остальные ячейки находятся в нулевом состоянии. Для двухуровневых цифровых узлов 17 изменение состояния это переход из состояния в О или О в I, а для многоуровневых узлов со ступенчатой формой входных (выходных) сигналов это переход на новый уровень (фиг. 2). Программирование и нод1слючение источников блока 6 к соответствующим контактам объекта 17 контроля происходит в следующем порядке. Вычислитель 1 выдает команды управления, которые через блок 2 сопряжения и б-ок 4 отправления поступают на информационный вход блока 6, где в соответствии с этими командами осуществляется подключение входов коммутаторов 13,соответствующих блоков 9 согласования к щинам питания блока б, потенциал на которых также программируется по командам от вычислителя 1. После этого на первые входы регистров Ю уставок выбранных блоков 9 согласования поступает от вычислителя 1 команда, которая формирует на первых выходах регистра Ю уставок потенциалы, поступаю- ище на первые входы коммутаторов 13 и разрещающие подачу питания на входы объекта 17 контроля. Проверка объекта 17 контроля осуществляется путем циклического формирования стимулирующих воздействий и оценки его реакций. В течение каждого цикла контроля вычислитель 1 через блок 2 сопряжения, блек 4 управления и элементы И 11 полает параллельно на все блоки 24 памяти выбранных блоков 9 согласования управляющие команды (адреса), в результате чего коды знакоперемен, записанные в определенном поле блока 24 памяти, поступают на вход счетного триггера 23. Счетный триггер 23 преобразует последовательность знакоперемен в реальный тестовый сигнал, который через схему ИЛИ 22 поступает на управляющий вход аналового ключа 16 (фиг. 2). В зависимости от входного сигнала (логического О или логичеог кой 1) на управляющем входе аналогового ключа 16 он пропускает на выход или аналоговый уровень от преобразователя 14,или аналоговый уровень от преобразователя 15. Эти уровни с выхода аналогового ключа 16 через коммутатор 13 поступают на входы объекта 17 контроля. Фронты уровней сигналов, поступающих на входы объ екта 17 кситр.ля, . .11)едсляк)тся бькпро действием аналогоиого ключа 16 и при использовании для его изготовления сотфемешюй элементной базы имеют величину порядка 10-20 не. Ранее запрограммнрованные блоки 9 согласования, ocyuieствляют контроль реакций. Уровни с пре образователей 14 и 15-сравниваются посредством компараторов 12 с сигналом реакции, поступающим через комму- татор 13 с объекта 17 контроля. Резул тат сравнения поступает с выходов компараторов 12 выбранных блоков 9 согласования на вход блока 4 управления. При наличии хотя бы в одном из выбранных блоков согласования несовпадения требуемой реакции с реальным вы ходным сигналом блок 4 управления останавливает программу проверки, определяет номера неисправных контактов и вы дает данные о них через блок 2 сопряже ния в вьиислитель 1, который по мере необходимости выдает эти данные на блок 3 вывода для регистрации. Если на следующем цикле проверки необходимо перейти на новый уровень по входу или выходу объекта 17 контроля для цифровы узлов со ступенчатой формой входных (выходных) сигналов, fb вычислитель 1 перепрограммирует информационнъгй преобразователь, который и данный момент отключен от входов объекта 17 контроля или который не использовался в предыду щем цикле для задания требуемой реакции (фиг. 2). После этого вычислитель организует следующий цикл проверки. Ан логично осуществляются последующие W циклов контроля. В результате проверки объекта 17 контроля в первом режиме определяются номера неисправных контактов как на каждом тестовом наборе, так и на всем множестве N( тестовых наборов. Информация о номерах неисправных выходных контактов записывается в определенную зону оперативной памяти вычислителя 1 и в дальнейшем используется (как исходнъю данные) в программе проверки второ режима. В этой же зоне оперативной памяти вычислителя 1 находится инс}юрмация о группах входных контактов, имеющих логическую связь с выходными контактами, которая заносится в эту област блоком 3 с внешнего носителя в момент ввода программ проверки данного объект 17 контроля. Множество входных ко тактов, имеющих логическую связь с 1 ым выходным контактом, зависит от деГ)Г рева логического графа объекта контроля, а М1 ожество М грутш определяется количеством выходных контактов ОК. Таким образом, в результате проверки объекта контроля в первом режиме определяется подмножестЕо Р групп из полного множества М групп. Подмножество Р определяется количеством неисправны выходных контактов. Во втором режиме, если есть хотя бы один неисправный контакт (результат проверки объекта контроля на первом этапе Негоден), по команде от вычислителя 1 запускается программа поиска трасс неиспр)авностей. Вычислитель 1 выдает адрес 1 -го неисправного контакта из подмножества Р, который поступает по информационной магистрали в блок 7 диагностик11 на вход регистра 19 адреса выходов, с выхода которого код адреса поступает на управляющий вход мультиплексора 26, который подключает выбранный 1 -ый въкодной контакт объекта контроля ко входу сигнатурного анализатора. Далее вычислитапь 1 запускает программу проверки первого режима без остановки после каждого тестового набора для анализа результатов контроля. На вход объекта 17 котроля аналогично псрво {у режиму поступают пходиые тесто 1Ь е наборы, которые генерируют иа выход1Ш1х контактах объекта 17 контроля конечную последовательность сягналоп (ответных. реакш й), которые сигнатурный анализатор 27 преобразует в код сигнатур. После выдачи всех тестовых поборов иа вход объекта 17 контроля вычислитель 1 выдает команду па регистр 28, при этом в него с выхода сигнатурного анализатора 27 записывается значение кода сигнатуры для выбранного i -го неисправного выходного контакта объекта 17 контроля. Значение кода сигнатуры для -го контакта может быть любым и зависит от типа и места неисправности внутри объ екта 17 контроля. После этого вычислитель выдает код адреса первого О -го входного контакта из множества , который поступает по информационной магистрали в блок 7 диагностики на вход регистра 18 адреса входов, с выхода которого код адреса поступает на вход дешифратора канала 25, который формирует па своем выходе сигнал, поступаю1Щ1Й иа вход .;леме1ггов И 11 и И 21 Э -го блока 9 согласования, при этом запрещается прохождение команд управления от вычислителя 1 па вход блока 24 памяти и разрешается прохождение

на управляющий вход аналогового ключа 16 уровней сигналов с Шагхода блока 7 диагностики от триггера 20, который в данный момент находится в любом СОСТО51НИИ. Далее вытюлнтепь 1 снова запускает программу проверки первого релдама. В этом случае бурут генерироваться по всем входам, кроме выбранного J -го, те же входные последоватапьности, что и в предыдущем случае. При этом, если на трассе от входного D-ro до выходного 1 -го контакта нет неис правностей, то в сигнатурном анализаторе 27 будет зафиксирован код сигнатуры отличный от предыдущего, так как на -ом входном контакте присутствует постоянный уровень сигнала, вместо ранее подаваемой на него последовательности сигналов, а если на этой трассе имеется одна зшн несколько логических неисправностей типа конституэнта О или конституэнта I, то в сигнатурном анализаторе 27 будет зафиксирован код сигнатуры, рйвный предыдущем , так как отключение З-го схода объекта 17 в случае отсутствия сходягцихся разветвлений п дереве логического графа множества Q не приведет к изменению выходной последовательности на выходе - -го неисправного контакта. После этого вычисл тель 1 выдает команду на регистр 29, при этом в него с выхода сигнатурного анализатора 27 заносится значение кода диагност1-гческой сигнатуры Э -го входного контакта. сигнатура -го неисиравного контакта н диагкостическая сигнатура -( го входного 1сонтакта равны, то срабатывает элемент 30 сравнения и с его выхода на вычислитель 1 поступает сигнал прерывания, который сиг-наота1зиру ет вычислиташо 1 о наличии неисправности на проверяемой трассе. После перебора всех входных контактов множества Q для выходного -f -го неисправного контакта вычислитель 1 заносит в регистр 28 адрес следуюиГёго неисправного контакта, для которого проводятся те же операции, что и для i го неисправного контакта, с целью выявления трасс неисправностей и т.д., пока не .будут обработаны все под шюжества Р выходных неисправных контактов, noaiie этого вычислитель 1 запус кает программу, определяющую отсутстви замыканий между собой логических цепей внутри объекта 17 контроля. При этом определяется отсутствие замыкаю й межд трассами как внутри самих групп , теа и между трассами различных групп Q. всего подмножества Р.

Алгоритм работы устройства в этом случае будет следующим.

По команде от вычислителя 1 (аналогично описанному выше) выбирается iый выходной контакт, который через мультиплексор 26 подключается ко входу сигнатурного анализатора 27, а потом выбирается один из входных контакюв который принадлежит объединению множеств входных контактов Q всех подмножеств Р, т.е. йгКПо команде от

-Р

вычислителя 1, поступающей по информационной магистрали на вход блока 7 диагностики, триггер 20 устанавливается в состояние О. Далее вычислитель 1 запускает программу проверки первого этапа и по окончании цикла выдачи всех тесговых наборов на входы объекта 17 организует запись значения кода сигнатуры сигнатурного анализатора 27 в регистр 28, при этом код сигнатуры может быть любым и зависит от типа и места неисправности внутри объекта 17 контрол После этого вычислитель 1 устанавливает триггер 2О в состояние 1 и снова запускает программу проверки первого релшма, после чего организует запись значения вновь полученного кода сигнатуры в регистр 29. Если коды сигнатур совпали, то нет замыканий трассы от выходного 1 -го контакта до 3 -го входного контакта (трасса ) с остальными трассами от выходных -i -ых контактов до всего мнол-;ества К входных контактов если коды сигнатур различны, то замыкание имеет MeCiO. Это объясняется тем, что при замыкании двух различных внутренних точек на дереве логического графа (фиг. 3, точка А) образуется схема монтажное ИЛИ, при этом, если подавать на вход одной из перемкщтых трасс последовательность сигналов, opi анизуемой программой проверки первого этапа, а на вход другой поочередно подавать сначала уровень логического О, потом уровень логической 1, то в одном случае эта последовательность будет проходить на выход схемы, а в другом случае будет запрещаться поса оянным уровнем логического С на выходе, искусственно созданной схемы монтажное ИЛИ. Уровень сигнала (логический О или 1) на входе 1 -го входного контакта, при котором искусственно созданная схема монтажное ИЛИ запрещает сигналы с других входов, имеющих логическую связь с выходом схек-ш ИЛИ, зависит от количества инвертирующих элементов ОК, находящихся на трассе от входного D-го 139 контакта до выхода схемы монтажное ИЛИ При несовпадении кодов сигнатур элемент 30 сравнения вырабатывает сигнал прерывания, который поступает на вход вычислителя 1 и сигнализирует о наличии замыкания проверяемой трассы 3 с остальными трассами от множества К ЕЗСОД ных контактов до всего подмножества Р выходаплх контактов. Потом выбирается спедуккций вькодной контакт из подмножества Р выходных контактов, для которого повторяются те же операдии, с цель определения замыкания, между остальными трассами и т.д., пока не будут проверены на отсутствие замыканий все трассы между множеством К нходных контактов и подмножеством Р выходных контактов. Так как в случае замыканий между трассами внутри объекта 17 наличие этих замыканий определяется дважды,, что вытекает из алгоритма проверки, то вычислитель 1, используя эти данные, а также исходную информацию о подмножествах Р выходных неисправных контактов и соответствующих им множествам входных контактов Oi , ;и)Е1еятифицирует номера замкнутых трасс как внутри групп Q , так и номера замкнутых, трасс различных групп Q всего подмножества Р. На этом заканчивается программа проверки второго этапа, при этом вьгчислитель 1 через блок 2 сопряжения выдает на блок 3 вывода следующую информаоню на регистрацшо: номера трасс неисправностей (чомер выходного неисправного контакта и номер одного или нескольких входных контактов на трассе между которыми ест неисИравность) в количестве Р штук, информацию об отсутствии замыканий внутри логических цепей объекта 17 контроля, а если есть замыкания, то информашпо о номерах трасс, имеющих замыкания как внутри групп Q , так и между трассами различных групп. На рримере, приведенном на фиг. 2, видно, что при проверке данной логической схемы в первом режиме контроля определяются два выходных неисправных контакта У1 и У2, которые определяют подмножество Р для данного примера. Входы XI, Х2, ХЗ, Х4, Х5, Х6 принадлежат множеству входных контактов Q для выходного неистфавного контакта У1, а входы Х5, Х7, Х8 нринадлежат множеству входных контактов QU для выходного неисправного контакта У2. Во втором режиме определяются трасс неисправностей У1-ХЗ, У1-Х4, У1-Х5, 56 У2-Х5, У2-Х6, У2-Х7. У2-Х8 и выявляются трассы имеющие замыкания: Х6-У1 с Х5-У1, X7-J2 с Х8-У2, Х5У2 с Х6-У1, Х7-У2 с Х6-У1, Х8-У2 с Х6-У1. Сопоставляя логическую схему с полученными данными, определяют область, где находится неисправность. Комбинация трасс неиспре вностей У1-ХЗ, У1-Х4 и У1-Х5 возможна только яри наличии на выходе элемента 35 неисправности типа конституэнта О или конституэнта 1. Выше приведенные комбинации замкнутых трасс возможны только при наличии замыкания входа или выхода элемента 37 с входом или выходом ааемента 4О. В данном случае осущестиш- ется диагностика неисправности внутри цифрового узла с глубиной поиска до эл&мента схемы без привлечения дополнительной вычислительной мощности вычислителя 1 и без доступа к внутренним точкам логической схемы. Таким образом, введение в систему блока 7 диагностики и блока 8 анализа, а в каждый блок согласования аналогового ключа 16 второго цифрового преобразователя 15, счетного триггера S3, элемента 21 и элемента ИЛИ 2 2 позволяет задавать на вкоды многоуровневых цифровых узлов стит лирующие сигналы (либо сигналы реакций) в виде непрерывных ступенчатых фушщ11й слолоюй формы с временем переключения программируемых уровней, не превышшощем 1О-20 не, а также осуществпйть диагностику неисправностей цифровых УЗЛОВ без привлечения допалкительной вычислительной мощности вычислителя 1, что расширяет функциональные возможности устройства. Формула изобретения Устройство для контроля электрических параметров цифровых узлов, содержащее блоки согласования по числу контролируемых параметров, блок программируемых источников питания, выход которого соединен с первыми входами блоков согласования, блок управления, соединенный первым входом и первым выходом соответственно с выходом и входом блсжа сопряжения,. а вторым и третьим выхбдами соответственно с управляющими входами блока программируемых источников питания и блока измерителей, информа-: ционный выход которого подключен ко второму входу блока управления, вычисли159тепь и блок ввода-вы вода, соединешгые входами и выходами с соответствующими выходами и входами блока сопряже1шя, второй вход каждого блока согласовашга соединен с четвертым выходом блока управления, первые выходы и третьи входы блоков согласования соединены с соответствующими выходами и входами устройства, причем каждый блок согласовазш содержит регистр уставок, подключенный первым и вторым выходами соответственно к первым входам коммутатора и компаратора, второй вход которого подключе к первому выходу комгиутатора, второй и третий входы которого соединены соотвегг ствепно с первым и третьим входами блока согласования, а второй выход - с пер вым выходом блока согласования, первый вход регистра уставок соединен с первым входом блока согласования, второй вход которого соединен со вторым входом регистра уставок, с первыми входами первых элементов И и с третьим входом кокшаратора, выход которого соединен со вторым выходом блока согласования, тре тий выход регистра уставок соединен со вторыми входами первых элементов И, выходы которых соединет.1 со входами блока памяти, выход первого цифро-аналогового преобразователя соединен с четвертым входом компаратора, о т л и чающееся тем, что, с целью расширения функциональных возможностей, в него введены блок диагностики и блок анализа, а в каждый блок согласования дополт1тельно введены аналоговый ключ, второй цифро-аналоговый преобразователь счетный триггер, второй элемент И и элемент ИЛИ, причем четвертый выход блока управления соединен с иерв1лми входами блока анализа к блока диагностики, первый, второй вькоды и второй вход которого соединены соответственно с четвертыми, пятыми входами и третьими выходами блоков согласования, вход прерываний вь числителя соединен с выходом блока анализа, второй вход которого соединен с третьим выходом блока диагностики, четвертые и вторые выходы блоков согласования соединены соответ-ственно с входом блока измерите;тей и с третьим 1ЖОДОМ блока у-правлепия, а в каждом блоке согласования четвертый вход соединен с третьими инверсными входами первых элементов И и с первым входом второго элемента И, второй вход, которого соединен с пятым входом блока согласования, а -выход - с первым входом элемента ИЛИ, выход блока памяти 56 соединен со входом счетного триггера, выход которого соединен со вторым входом элемента ИЛИ, выход- которого соедш1ен с управлтощим входом аналогового ключа, четвертый выход регистра уставок соединен со входом первого цифроаналогового преобразователя, выход которого соединен с первым информац онным входом аналогового югюча, пятый выход регистра уставок соединен со входом второго цифро-аналогового преобразователя, выход которого соединен с пятым входом компаратора и со вторым информационным входом аналогового ключа, соединенного выходом с четвертым входом комк-гутатора, первый и третий выходы которого соединены соответственно с третьим и четвертым выходами блока согласования, причем блок диагностики содержит регистры адресов входов и выходов, дешифратор канала, триггер и мультиплексор, причем входы регисгров адресов входов и выходов соединены с первым входом блока диагностигети входом триггера, выход которого соединен со вторым входом блока диагностики, выход регистра адресов входов соединен со входом дешифратора канала, выход ко- торого соединен с первым выходом блока диагностики, выход регистра адресов выходов соединен с первым управляющим входом мультиплексора, второй информацион1СЬ Й вход которого соединен со вторым входом блока диагностики, а выход - с третьим выходом блока диагностики, а блок анализа содерлотт элемент сравнения, регистр сигнатуры неисправного контакта, регистр диагностических сигнатур и сигнатурный анализатор, первый вход которого соединен со вторым входом блока анализа, первый выход - с первыми входами регистра сигнатуры неисправного контакта и :)егистра диагностических сигнатур, выходы которых соедтшены, соответственно с первым и вторым входами элемента сравнения, выход которого соединен с выходом блока анализа, первый вход которого соединен со вторыми входами сигнатурного анализатора, регистра сигнатуры неисправного контакта и регистра диагностических сигнатур. Источники информашш, приняты.е во внимание при эксперт изе 1.Электроника. 1972, № 21, с. 45-54. 2.Авторское свидетельство СССР ПО заявке № 28459О9, кл. G06 F 15/46, 1919 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля электрических параметров цифровых узлов | 1984 |

|

SU1260974A1 |

| Устройство для контроля функционирования логических блоков | 1987 |

|

SU1432528A2 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ И ВОССТАНОВЛЕНИЯ ТЕХНИЧЕСКИХ СРЕДСТВ МЕДИЦИНСКОГО НАЗНАЧЕНИЯ | 1992 |

|

RU2072788C1 |

| Система для контроля и диагностики цифровых узлов | 1988 |

|

SU1594544A1 |

| Устройство для диагностики неисправностей логических блоков | 1987 |

|

SU1520548A1 |

| Система для контроля электрических параметров цифровых узлов | 1979 |

|

SU873247A2 |

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU960825A1 |

| Устройство для контроля аналоговых объектов | 1985 |

|

SU1288702A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1539782A2 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

Авторы

Даты

1982-02-23—Публикация

1980-07-17—Подача