Изобретение относится к автоматике и вычислительной технике и может быть использовано при о.бработке бинарных сигналов, например, в устройствах программного и логического управления технологическими агрегатами и установками.

Цель изобретения - повЕЛпение быстродействия.

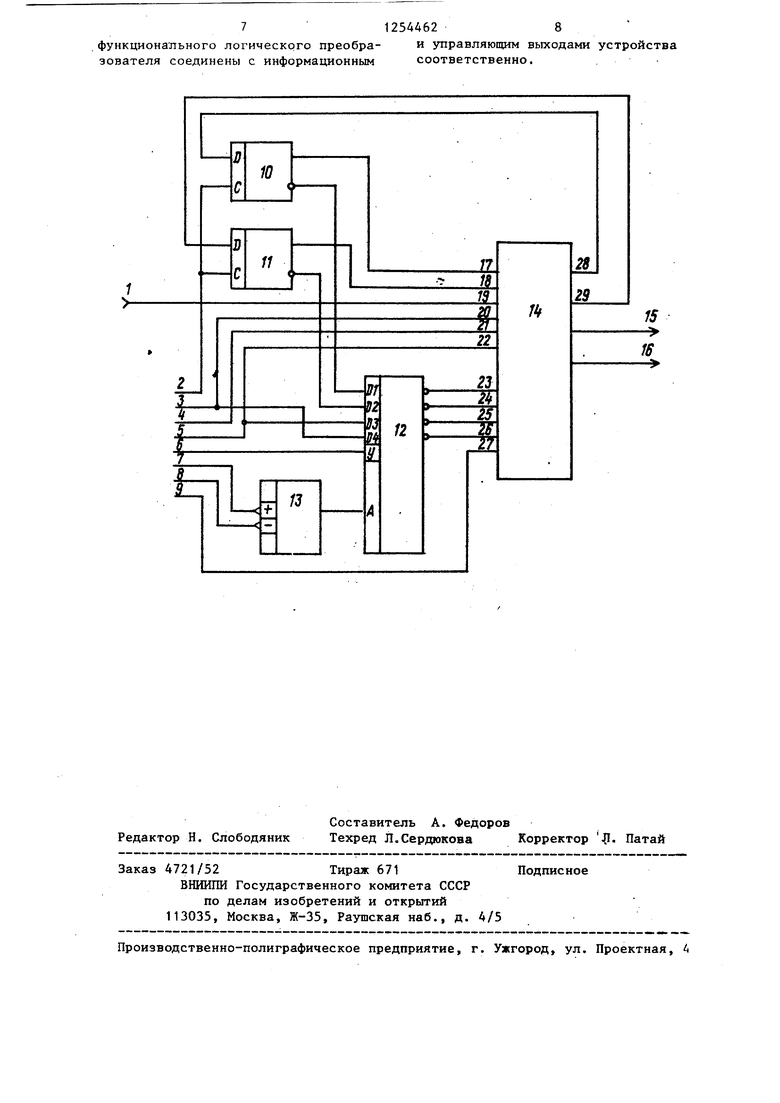

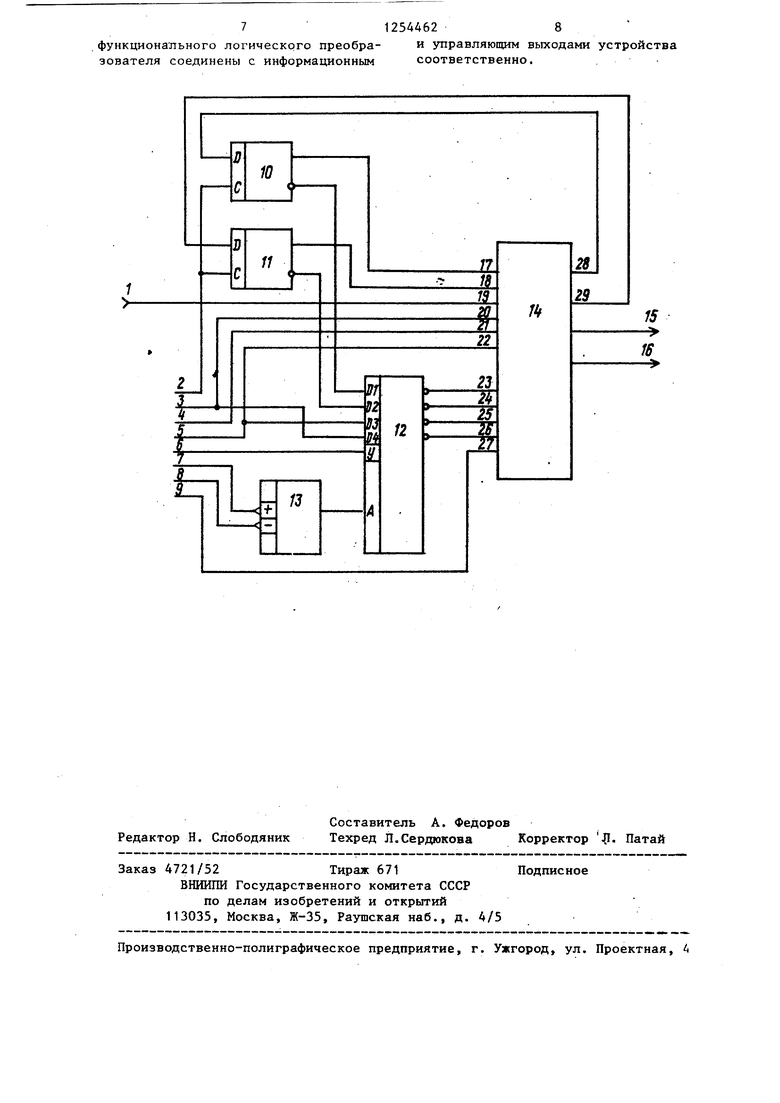

На чертеже представлена функцио- нальнай схема устройства.

Устройство содержит информационный вход 1, синхровход 2, входы 3 и 4 кода операции, вход 5 Инверсия, вход 6 Открывающая скобка, вход 7 Инкремент вход 8 Декремент, вход 9 Закрывающая скобка, триггеры 10 и 11, блок 12 памяти, счетчик .13, функциональный логический преобразователь 14, управляющий выход 15, информационный выход 16.

Функциональный логический преобразователь 14 содержит входы 17 и 18 промежуточных результатов, информационный вход 19, входы 20 и 21 кода операции, входы 22 Инверсия, входы 23 и 24 промежуточных результатов, вход 25 Инверсия, вход 26 кода операции, вход 27 Закрывающая скобка, выходы 28 и 29 промежуточных результатов.

На входы 2,7,8 поступают тактовые сигналы соответственно Строб триггеров 10 и 11, Инкремент и.. Декремент счетчика 13 скобок.

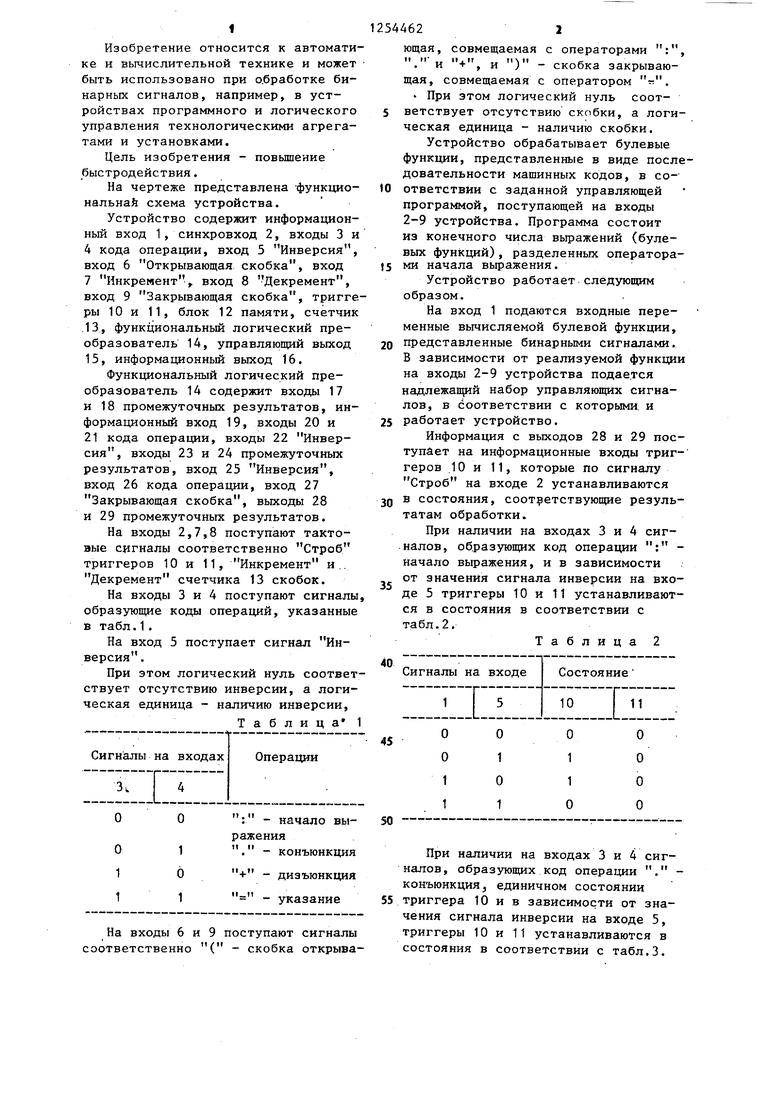

На входы 3 и 4 поступают сигналы образующие коды операций, указанные в табл.1.

На вход 5 поступает сигнал Инверсия .

При этом логический нуль соответствует отсутствию инверсии, а логическая единица - наличию инверсии.

Таблица

начало выражения

На входы 6 и 9 поступают сигналы соответственно ( - скобка открывающая,

II П ,,

rt . II

5

0

5

0

5

совмещаемая с операторами и +, и ) - скобка закрывающая, совмещаемая с оператором т. При этом логический нуль соответствует отсутствию скобки, а логическая единица - наличию скобки.

Устройство обрабатывает булевые функции, представленные в виде последовательности машинных кодов, в со- ответствии с заданной управляющей программой, поступающей на входы 2-9 устройства. Программа состоит из конечного числа вьфажений (булевых функций), разделенных операторами начала вьфажения.

Устройство работает следующим образом.

На вход 1 подаются входные переменные вычисляемой булевой функции, представленные бинарными сигналами. В зависимости от реализуемой функции на входы 2-9 устройства подается надлежащий набор управляющих сигналов, в соответствии с которыми, и работает устройство.

Информация с выходов 28 и 29 пос- тупйет на информационные входы триг- геров 10 и 11, которые по сигналу Строб на входе 2 устанавливаются в состояния, соответствующие результатам обработки.

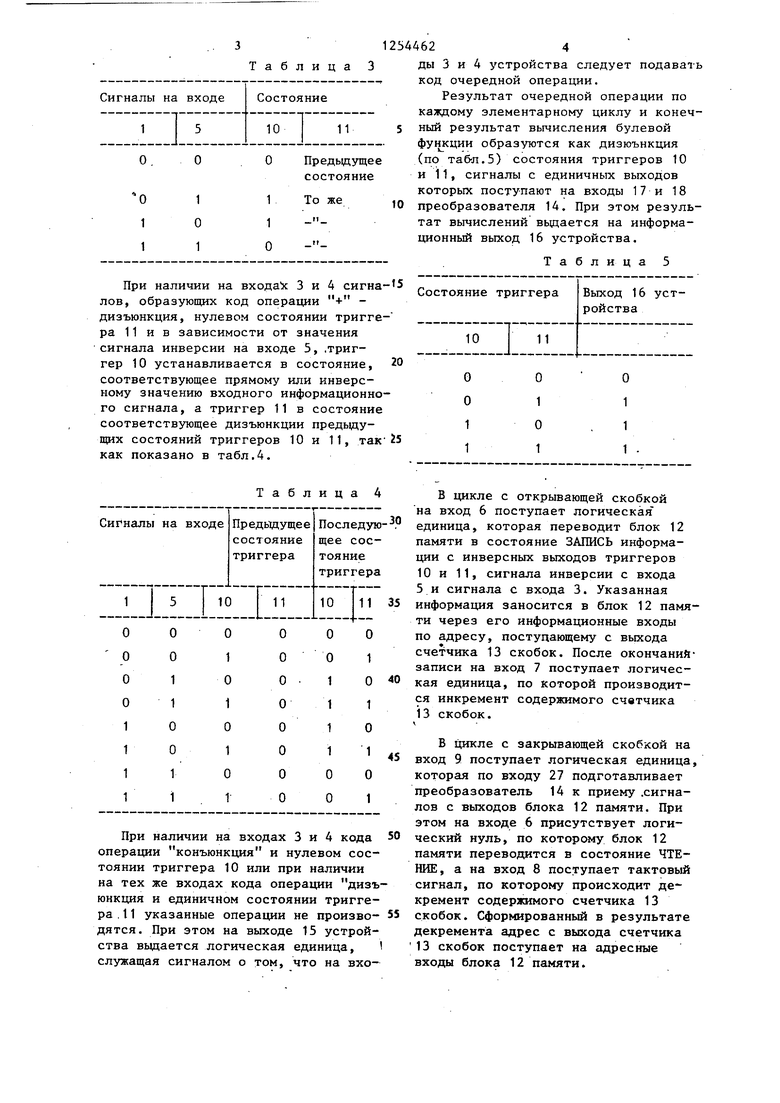

При наличии на входах 3 и 4 сигналов, образующих код операции : - начало выражения, и в зависимости от значения сигнала инверсии на входе 5 триггеры 10 и 11 устанавливаются в состояния в соответствии с табл.2.

Таблица2

При наличии на входах 3 и 4 сигналов, образующих код операции . - конъюнкция, единичном состоянии 55 триггера 10 и в зависимости от значения сигнала инверсии на входе 5, триггеры 10 и 11 устанавливаются в состояния в соответствии с табл.3.

Таблица 3

Предыдущее состояние

При наличии на входа х 3 и 4 сигна- 5 лов, образуюпщх код операции + - дизъюнкция, нулевом состоянии тригге- ра 11 ив зависимости от значения сигнала инверсии на входе 5, .триггер 10 устанавливается в состояние, 20 соответствующее прямому или инверсному значению входного информационного сигнала, а триггер 11 в состояние соответствующее дизъюнкции предьщу- щих состояний триггеров 10 и 11, как показано в табл.4.

Таблица 4

При наличии на входах 3 и 4 кода 50 операции конъюнкция и нулевом состоянии триггера 10 или при наличии на тех же входах кода операции дизъюнкция и единичном состоянии триггера . 1 1 указанные операции не произво- 55 дятся. При этом на выходе 15 устройства выдается логическая единица, служащая сигналом о том, что на вхо

ды 3 и 4 устройства следует подавать код очередной операции.

Результат очередной операции по каждому элементарному циклу и конечный результат вычисления булевой функции образуются как дизюънкция (по таб-л.5) состояния триггеров 10 и 11, сигналы с единичных выходов которых поступают на входы 17 и 18 преобразователя 14. При этом результат вычислений выдается на информационный выход 16 устройства.

Таблица 5

В цикле с открывающей скобкой на вход 6 поступает логическая единица, которая переводит блок 12 памяти в состояние ЗАПИСЬ информации с инверсных выходов триггеров 10 и 11, сигнала инверсии с входа 5 и сигнала с входа 3. Указанная информация заносится в блок 12 памяти через его информационные входы по адресу, поступающему с выхода счетчика 13 скобок. После окончаний записи на вход 7 поступает логическая единица, по которой производится инкремент содержимого счетчика

13 скобок.

В цикле с закрывающей скобкой на вход 9 поступает логическая единица которая по входу 27 подготавливает преобразователь 14 к приему .сигналов с выходов блока 12 памяти. При этом на входе 6 присутствует логический нуль, по которому блок 12 памяти переводится в состояние ЧТЕНИЕ, а на вход 8 поступает тактовый сигнал, по которому происходит декремент содержимого счетчика 13 скобок. Сформированный в результате декремента адрес с выхода счетчика 13 скобок поступает на адресные входы блока 12 памяти.

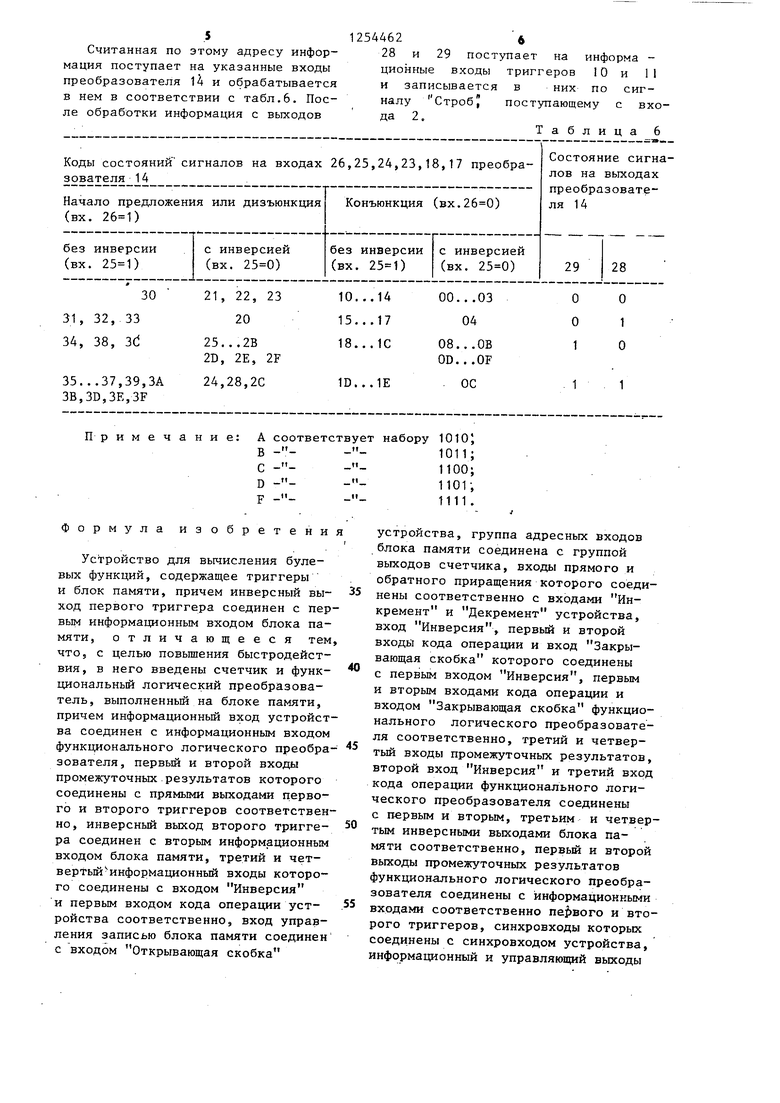

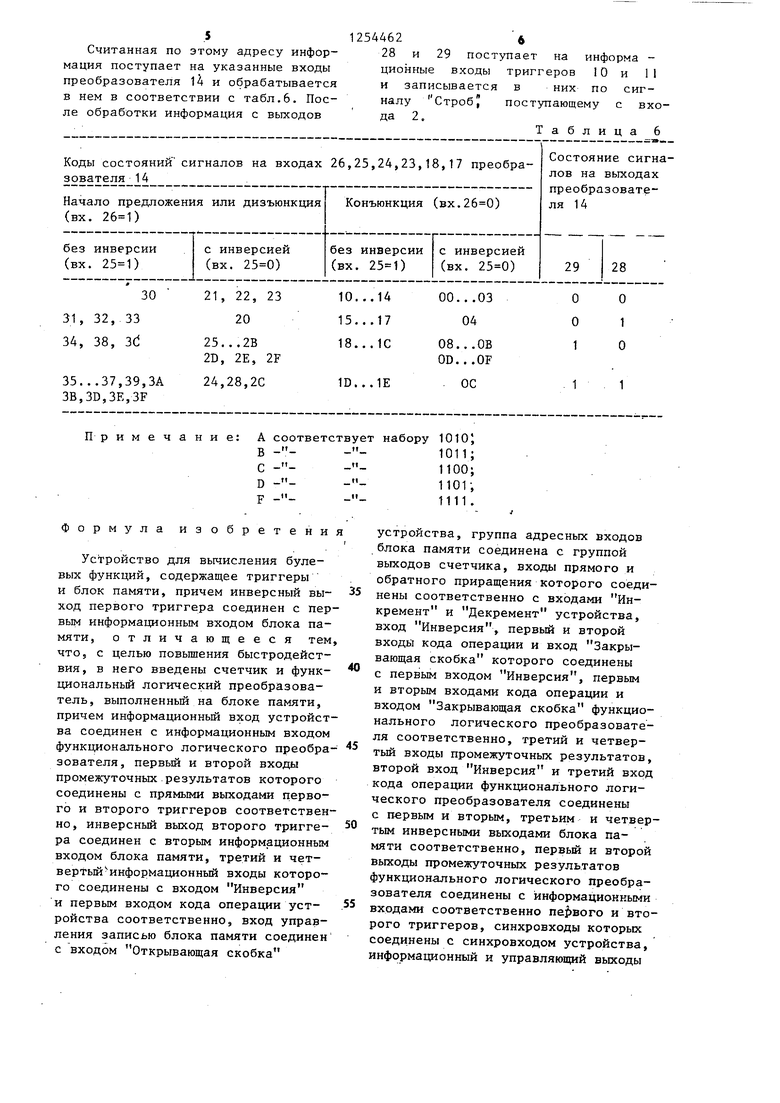

Считанная по этому адресу информация поступает на указанные входы преобразователя 1Д и обрабатывается в нем в соответствии с табл.6. После обработки информация с выходов

Коды состояний сигналов на входах 26,25,24,23,18,17 преобразователя 14

Формула иэобретени

Устройство для вычисления булевых функций, содержащее триггеры и блок памяти, причем инверсный выход первого триггера соединен с первым информационным входом блока памяти, отличающееся тем что, с целью повьшения быстродействия , в него введены счетчик и функ- циональньй логический преобразователь, выполненный на блоке памяти, причем информационный вход устройства соединен с информационным входом функционального логического преобра эователя, первый и второй входы промежуточных результатов которого соединены с прямыми выходами первого и второго триггеров соответственно, инверсный выход второго триггера соединен с вторым информационным входом блока памяти, третий и чет- вертый информационный входы которого соединены с входом Инверсия и первым входом кода операции устройства соответственно, вход управления записью блока памяти соединен с входом Открывающая скобка

28 и 29 поступает на информа - ционные входы триггеров 10 и 11 и записывается в них по сигналу СтробJ поступающему с входа 2.

Таблица 6

Состояние сигналов на выходах

5

0

5

устройства, группа адресных входов блока памяти соединена с группой выходов счетчика, входы прямого и обратного приращения которого соединены соответственно с входами Инкремент и Декремент устройства, вход Инверсия, первый и второй входы кода операции и вход Закрывающая скобка которого соединены с первым входом Инверсия, первым и вторым входами кода операции и входом Закрывающая скобка функционального логического преобразователя соответственно, третий и четвертый входы промежуточных результатов, второй вход Инверсия и третий вход кода операции функционального логического преобразователя соединены с первым и вторым, третьим и четвертым инверсными выходами блока памяти соответственно, первый и второй выходы промежуточных результатов функционального логического преобразователя соединены с информационными входами соответственно n&jtBoro и второго триггеров, синхровходы которых соединены с синхровходом устройства, информационный и управляющий выходы

712544628

функционального логического преобра- и управляющим выходами устройства эователя соединены с информационным соответственно.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления булевых функций | 1986 |

|

SU1372319A1 |

| Устройство для вычисления булевых функций | 1984 |

|

SU1242928A1 |

| Устройство для вычисления булевых функций | 1984 |

|

SU1218376A2 |

| Устройство для определения значений булевых функций | 1990 |

|

SU1805462A1 |

| Устройство для вычисления булевыхфуНКций | 1978 |

|

SU807272A1 |

| Устройство для вычисления булевых функций | 1982 |

|

SU1049898A1 |

| Устройство для вычисления булевых функций | 1986 |

|

SU1332310A1 |

| Устройство для определения значений булевых функций | 1987 |

|

SU1508204A1 |

| Устройство для вычисления булевых функций | 1980 |

|

SU955027A1 |

| Устройство для моделирования конечных автоматов | 1980 |

|

SU955080A1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано при обработке бинарных сигналов в устройствах программного и логического управления технологическими агрегатами и установками. Цель изобретения - повышение быстродействия. Устройство обрабатывает булевые функции, представленные в виде последовательности машинных кодов, в соответствии с заданной управляющей программой.- Про .J грамма состоит из конечного числа выражений, разделенных операторами начала выражения. Устройство содержит функциональный логический преобразователь, счетчик, блок памяти и два триггера. На информационный вход устройства последовательно подаются двоичные значения переменных вычисляемой булевой функции. В зависимости от реализуемой функции на управляющие входы устройства подается соответствующий набор управляющих сигналов, определяющий логику работы устройства. Промежуточные результаты вычислений с выходов функционального логического преобразователя записываются в триггеры и, при наличии скобок в вычисляемом выражении, в блок памяти. С выходов триггеров и блока памяти информация поступает на входы преобразователя для дальнейшей обработки. Окончательный ре зультат вычислений выдается на информационный выход устройства при поступлении сигналов окончания вычисления или выявлении определенных .логических признаков. 1 ил., 6 табл. i (Л to СП N 4ib CD ГО

| Устройство для вычисления булевыхфуНКций | 1978 |

|

SU798805A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для вычисления булевыхфуНКций | 1978 |

|

SU807272A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-08-30—Публикация

1984-01-25—Подача