Изобретение относится к автоматике и вычислительной технике и предназначено для вычисления булевых функций- при последовательном считывании и обработке операндов и операторов, из которых состоит логическое выражение.

Известно логическое устройство, .предназначенное для решения задач логического управления, алгоритм . функционирования которых представляет собой последовательную реализацию каждого из набора булевых уравнений, содержащее программный блок, реле времени, индикаторы несовпадений, формирователь признака опроса и блок анаши за функций 1 .

Недостатками этого устройства являются его сложность и ограниченные функциональные возможности, так как это устройство позволяет вычислять булевы функции, представленные только в дизъюнктивной или конъюнктивной нормальных, формах..

Наиболее близким к предлагаемому является устройство, содержаццее логический блок, подключенный к генератору функциональных импульсов, блоку памяти данных и через дешифраторы

операции и адреса к блоку памяти проrpat/мы 2 .

Известное устройство позволяет вычислять булевы функции, представленные в конъюнктивной форме, без предварительйого преобразования их в дизъюнктивную , если операндаичи для , конъюнкций являются дизъюнкции переменных. Однако его

10 функциональные возможности также ограничены вследствие отсутствия возможности реализации булевых уравнений, записанных в скобочной форме, если выражение в скобках представляет собой набор конъюнкций нескольких

15 переменных, соединенных дизъюнктивно.

Цель изобретения - расширений функциональных возможностей устрой,ства, в результате чего последнее 20 обеспечит вычисление булевых функций, представленных в скобочной форме при условии, что выражения в скобках представляют собой наборы конъюнкций произвольного числа переменных, соединенных дизъюнктивно.

25

Поставленная цель достигается тем, что в устройство, содержащее блок памяти данных, адресный вход которого подключен к первому выходу блока памяти программ, второй выход которого

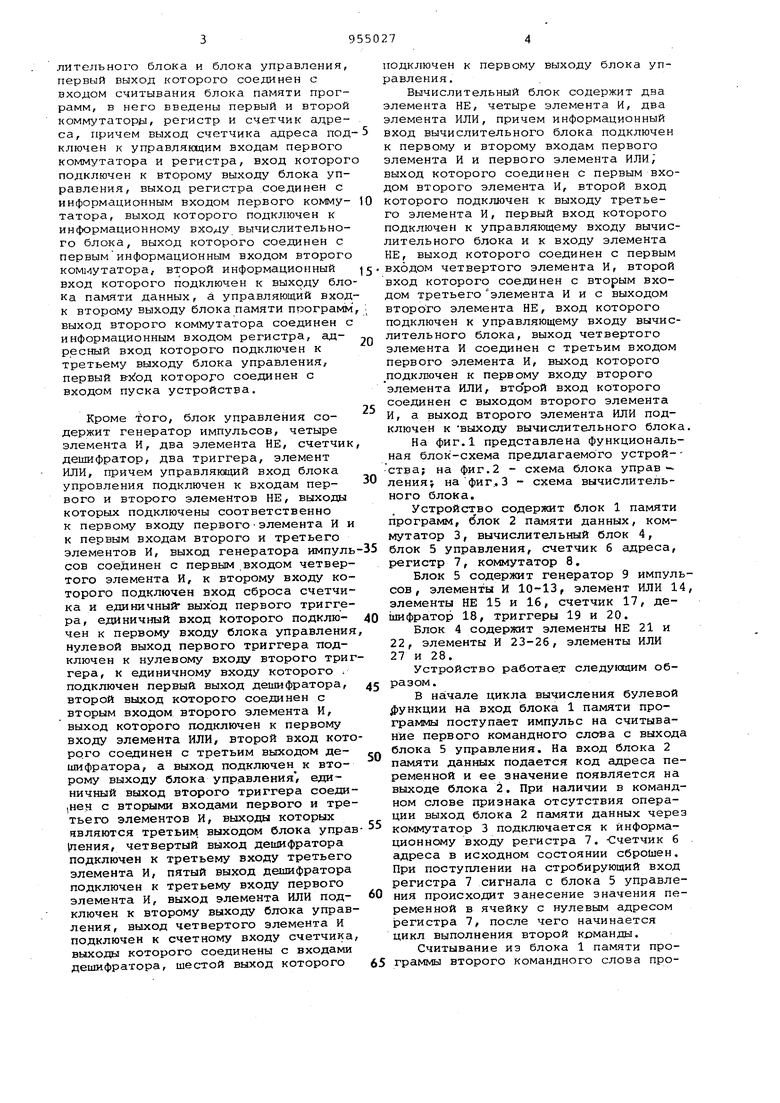

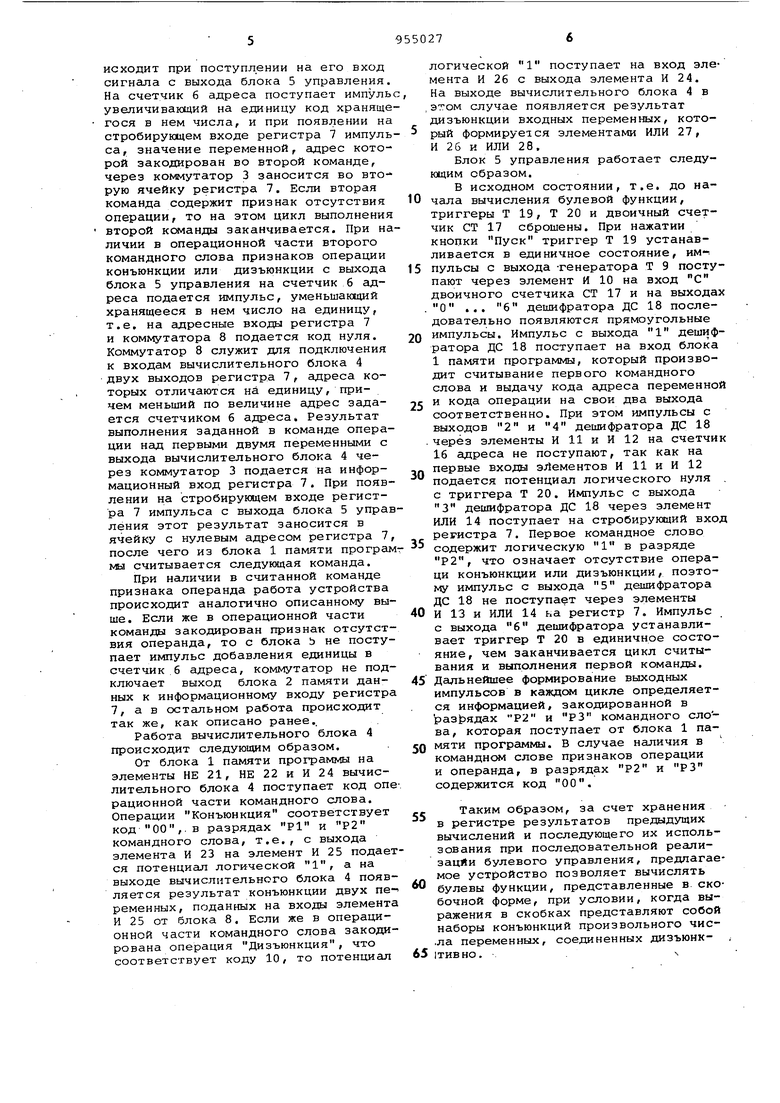

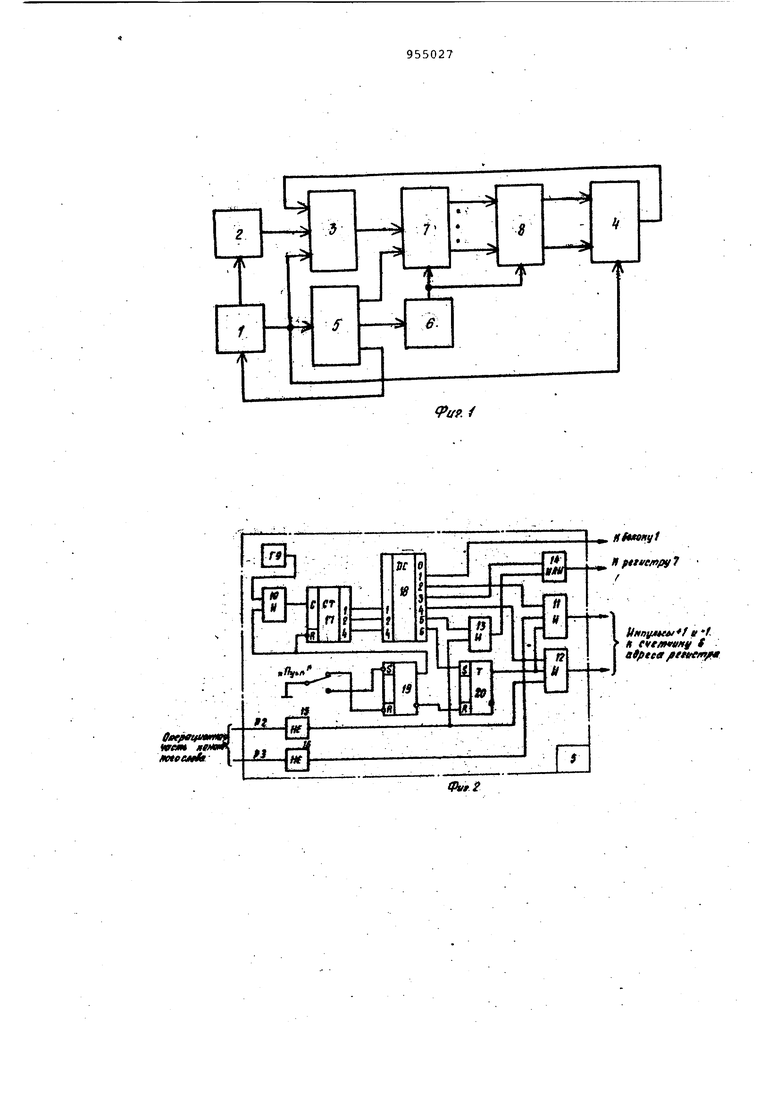

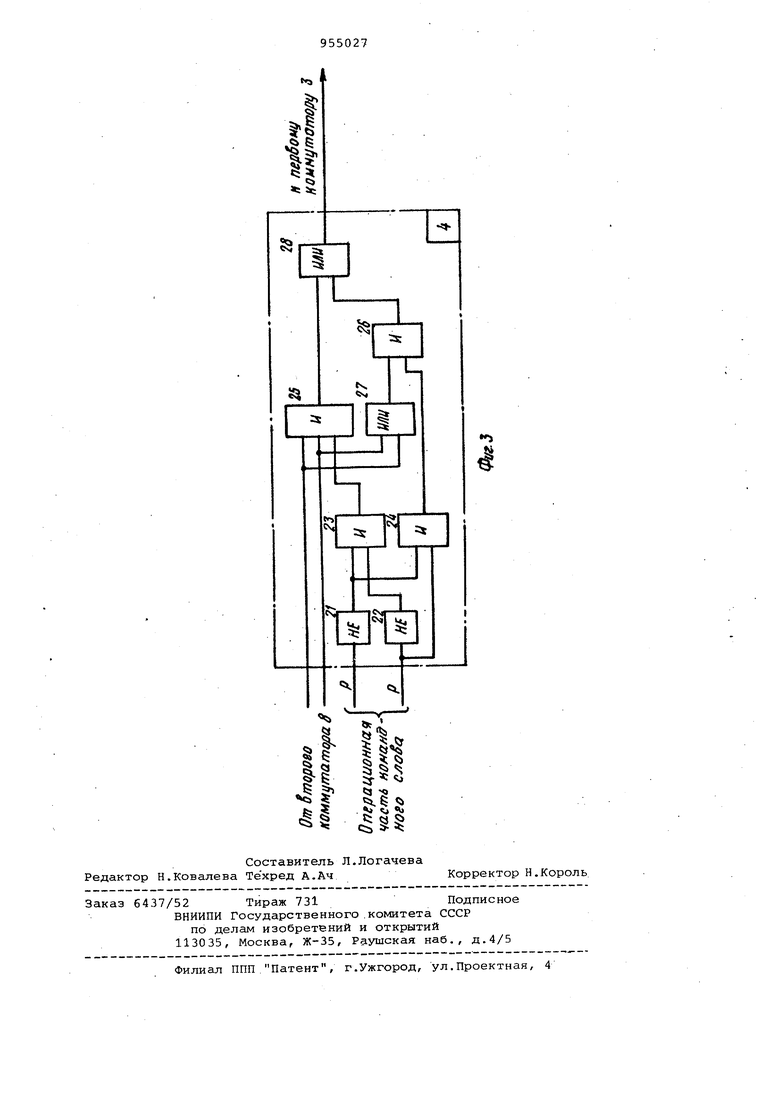

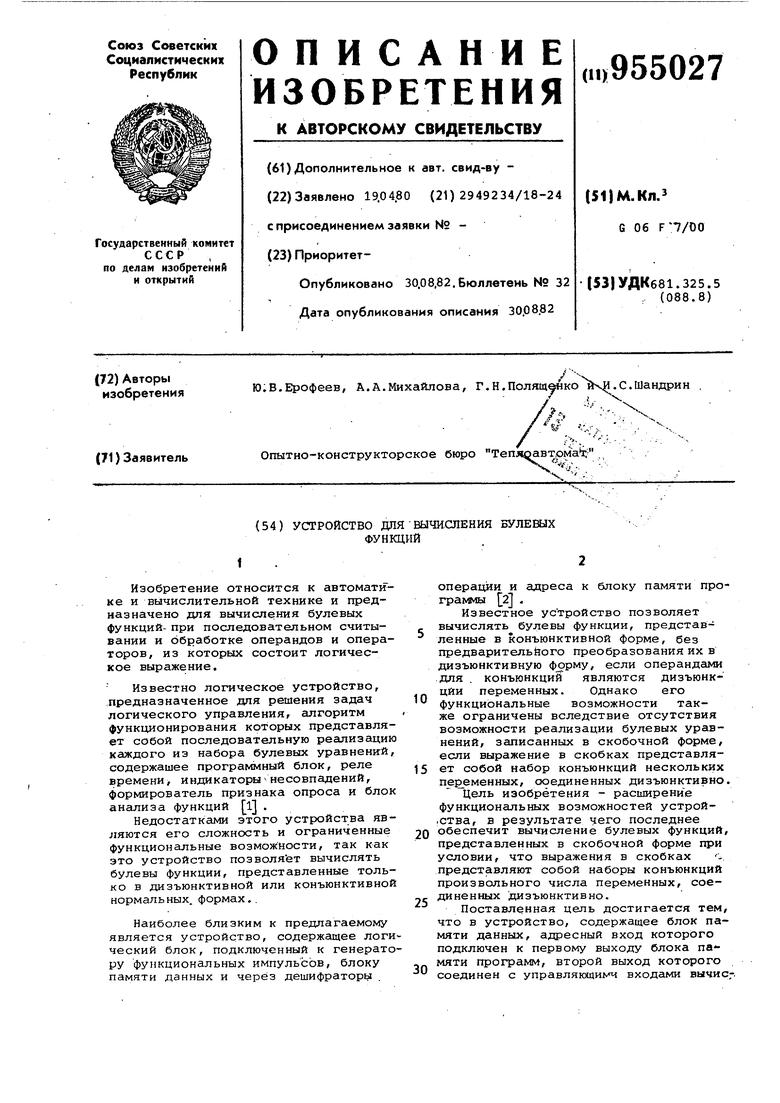

30 соединен с управляющими входами вычис,-лителъного блока и блока управления первый выход которого соединен с входом считывания блока памяти программ, в него введены первый и второй коммутаторы, регистр и счетчик адреса, причем выход счетчика адреса под ключен к управляющим входам первого коммутатора и регистра, вход которог подключен к второму выходу блока управления, выход регистра соединен с информационным входом первого коммутатора, выход которого подключен к информационному входу вычислительного блока, выход которого соединен с первым информационным входом второго коммутатора, второй информационный вход которого подключен к выходу бло ка памяти данных, а управляющий вход к второму выходу блока памяти nporpaNW выход второго коммутатора соединен информационным входом регистра, адресный вход которого подключен к третьему выходу блока управления, первый в-л;од которого соединен с входом пуска устройства. Кроме того, блок управления содержит генератор импульсов, четыре элемента И, два элемента НЕ, счетчик дешифратор, два триггера, элемент ИЛИ, причем управляющий вход блока упровления подключен к входам первого и второго элементов НЕ, выходы которых подключены соответственно к первому входу первогоэлемента И и к первым входам второго и третьего элементов И, выход генератора импул сов соединен с первым входом четвер того элемента И, к второму входу ко торого подключен вход сброса счетчи ка и единичный- выход первого тригге ра, единичный вход Которого подключен к первому входу блока управлени нулевой выход первого триггера подключен к нулевому входу второго три гера, к единичному входу которого подключен первый выход дешифратора, второй выход которого соединен с вторым входом второго элемента И, выход которого подключен к первому входу элемента ИЛИ, второй вход кот рого соединен с третьим выходом дешифратора, а выход подключен к второму выходу блока управления, единичный выход второго триггера соеди ,нен с вторыми входами первого и тре тьего элементов И, выходы которьах являются третьим выходом блока упра 1пения, четвертый выход дешифратора подключен к третьему входу третьего элемента И, пятый выход дешифратора подключен к третьему входу первого элемента И, выход элемента ИЛИ подключен к второму выходу блока управ ления, выход четвертого элемента И подключен к счетному входу счетчика выходы которого соединены с входами дешифратора, шестой выход которого подключен к первому выходу блока управления. Вычислительный блок содержит два элемента НЕ, четыре элемента И, два элемента ИЛИ, причем информационный вход вычислительного блока подключен к первому и второму входам первого элемента И и первого элемента ИЛИ, выход которого соединен с первым входом второго элемента И, второй вход которого подключен к выходу третьего элемента И, первый вход которого подключен к управляющему входу вычислительного блока и к входу элемента НЕ, выход которого соединен с первым входом четвертого элемента И, второй вход которого соединен с вторым входом третьего элемента И и с выходом второго элемента НЕ, вход которого подключен к управляющему входу вычислительного блока, выход четвертого элемента И соединен с третьим входом первого элемента И, выход которого подключен к первому входу второго элемента ИЛИ/ второй вход которого соединен с выходом второго элемента И, а выход второго элемента ИЛИ подключен к ВЫХОДУ вычислительного блока. На фиг.1 представлена функциональная блок-схема предлагаемого устрой-ства; на фиг.2 - схема блока управ - лeния нафиг,3 - схема вычислительного блока. Устройство содержит блок 1 памяти программ, блок 2 паиляти данных, коммутатор 3, вычислительный блок 4, блок 5 управления, счетчик 6 адреса, регистр 7, коммутатор 8, Блок 5 содержит генератор 9 импульсов, элементы И 10-13, элемент ИЛИ 14, элементы НЕ 15 и 16, счетчик 17, дешифратор 18, триггеры 19 и 20. Блок 4 содержит элементы НЕ 21 и 22, элементы И 23-26, элементы ИЛИ 27 и 28. Устройство работае.т следующим образом. В начале цикла вычисления булевой функции на вход блока 1 памяти программы поступает импульс на считывание первого командного слова с выхода блока 5 управления. На вход блока 2 памяти данных подается код адреса переменной и ее значение появляется на выходе блока 2. При наличии в командном слове признака отсутствия операции выход блока 2 памяти данных через коммутатор 3 подключается к информационному входу регистра 7. -Счетчик б адреса в исходном состоянии сброшен. При поступлении на стробирующий вход регистра 7 сигнала с блока 5 управления происходит занесение значения переменной в ячейку с нулевЬ|1М адресом регистра 7, после чего начинается цикл выполнения второй крманды. Считывание из блока 1 памяти программы второго командного слова происходит при поступлении на его вход сигнала с выхода блока 5 управления. На счетчик 6 адреса поступает импуль увеличивающий на единицу код хранящегося в нем числа, и при появлении на стробирукщем входе регистра 7 импульса, значение переменной, адрес которой закодирован во второй команде, через коммутатор 3 заносится во вто- рую ячейку регистра 7. Если вторая команда содержит признак отсутствия операции, то на этом цикл выполнения второй команды заканчивается. При наличии в операционной части второго командного слова признаков операции конъюнкции или дизъюнкции с выхода блока 5 управления на счетчик 6 адреса подается импульс, уменьшакщий хранящееся в нем число на единицу, т.е. на адресные входы регистра 7 и коммутатора 8 подается код нуля. Коммутатор 8 служит для подключения к входам вычислительного блока 4 двух выходов регистра 7, адреса которых отличаются на единицу, причем меньший по величине адрес задается счетчиком 6 адреса. Результат выполнения заданной в команде операции над первыми двумя переменными с выхода вычислительного блока 4 через коммутатор 3 подается на информационный вход регистра 7. При появлении на стробирующем входе регистра 7 импульса с выхода блока 5 управления этот результат заносится в ячейку с нулевым адресом регистра 7, после чего из блока 1 памяти програм мы считывается следующая команда.

При наличии в считанной команде признака операнда работа устройства происходит аналогично описанному выше. Если же в операционной части команды закодирован признак отсутствия операнда, то с блока Ь не поступает импульс добавления единицы в счетчик б адреса, коммутатор не подключает выход блока 2 памяти данных к информационному входу регистра 7, а в остальном работа происходит так же, как описано ранее.

Работа вычислительного блока 4 происходит следующим образом.

От блока 1 памяти программы на элементы НЕ 21, НЕ 22 и И 24 вычислительного блока 4 поступает код операционной части командного слова. Операции Конъюнкция соответствует код 00,.в разрядах Р1 и Р2 командного слова, т.е., с выхода элемента И 23 на элемент И 25 подается потенцисШ логической 1, а на выходе вычислительного блока 4 появляется результат конъюнкции двух ne-i ременных, поданных на входы элемента И 25 от блока 8. Если же в операционной части командного слова закодирована операция Дизъюнкция, что соответствует коду 10, то потенциал

логической 1 поступает на вход элемента И 26 с выхода элемента И 24. На выходе вычислительного блока 4 в , этом случае появляется результат дизъюнкции входных переменных, который формируется элементами ИЛИ 27, И 2G и ИЛИ 28.

Блок 5 управления работает следующим образом.

В исходном состоянии, т.е. до на0чала вычисления булевой функции, триггеры Т 19, Т 20 и двоичный счетчик СТ 17 сброшены. При нажатии кнопки Пуск триггер Т 19 устанавливается в единичное состояние, им5пульсы с выхода -генератора Т 9 поступают через элемент И 10 на вход С двоичного счетчика СТ 17 и на выходах .О ... 6 дешифратора ДС 18 последовательно появляются прямоугольные импульсы. Импульс с выхода 1 дешиф0ратора ДС 18 поступает на вход блока 1 памяти программы, который производит считывание первого командного слова и выдачу кода адреса переменной и кода операции на свои два выхода

5 соответственно. При этом импульсы с выходов 2 и 4 дешифратора ДС 18 через элементы И 11 и И 12 на счетчик 16 адреса не поступают, так как на первые входы элементов И 11 и И 12

0 подается потенцисШ логического нуля . с триггера Т 20. Импульс с выхода 3 дешифратора ДС 18 через элемент ИЛИ 14 поступает на стробирующий вход регистра 7. Первое командное слово

5 содержит логическую 1 в разряде Р2, что означает отсутствие операци конъюнкции или ДИЗЪЮНКЦИИ; поэтому импульс с выхода 5 дешифратора ДС 18 не поступает через элементы

0 И 13 и ИЛИ 14 ьа регистр 7. Импульс с выхода 6 дешифратора устанавливает триггер Т 20 в единичное состояние, чем заканчивается цикл считывания и выполнения первой команды.

5 Дальнейшее формирование выходных импульсов в каждс 4 цикле определяется информацией, закодированной в Р2 и РЗ командного слова, которая поступает от блока 1 памяти программы. В случае наличия в

0 командном слове признаков операции и операнда, в разрядах Р2 и РЗ содержит ся код 00.

Таким образом, за счет хранения

5 в регистре результатов предыдущих вычислений и последующего их использования при последовательной реализации булевого управления, предлагаемое устройство позволяет вычислять

0 булевы функции, представленные в. скобочной форме, при условии, когда выражения в скобках представляют собой наборы конъюнкций произвольного чис,ла переменных, соединенных дизъюнк5тивно..ч Формула изобретения

1.Устройство для вычисления булевых функций, содержащее блок памяти данных, адресный вход которого подключен к первому выходу блока памяти программ, второй выход которого соединен с управляющими входами вычислительного блока и блока управления, первый выход которого соединен с входом считывания блока памяти программ, отличающееся тем, что,

с целью расширения функциональных возможностей за счет решения булевых уравнений в скобочной форме, в него введены первый и второй коммутаторы, регистр и счетчик адреса, причем вы-, ,ход счетчика адреса подключен к управляющим входам первого коммутатора и регистра, вход которого подключен к второму выходу блока управления, выход регистра соединен с информационным входом первого коммутатора, выход которого подключен к информационному входу вычислительного блока выход которого соединен с первым информационным входом второго коммутатора, второй информационный вход которого подключен к выходу блока памяти данных, а управляющий вход - к второму выходу блока памяти программ выход второго коммутатора соединен с информационным входомрегистра, адресный вход которого подключай к третьему выходу блока управлени-я, первый вход которого соединен с входом пуска устройства,

2.Устройство по п,1, отличающее с я тем, что блок управления содержит генератор импульсов, четыре элемента И, два элемента НЕ, счетчик дешифратор, два триггера, элемент ИЛИ причем управляющий вход блока управлений подключен к входам первого и второго элементов НЕ, выходы которых подключены соответственно к первому входу первого элемента И и к первым входам второго и третьего элементов И, выход генератора импульсов соединен с первым входом четвертого элемента И, к второму входу которого подключен вход сброса счетчика и единичный выход первого триггера, едини4ный вход которого подключен к первому входу блока управления, нулевой выход первого триггера подключен к нулевому входу второго триггера, к единичному входу которого подключен

первый выход дешифратора, второй выход которого соединен с вторым входом второго элемента И, выход которого подключен к первому входу элемента ИЛИ, второй вход которого соединен с третьим выходом дешифратора, а выход t подключен к второму выходу блока управления, единичный выход второго триггера соединен с вторыми входами первого и третьего элементов И, выходы которых являются третьим выходом блока управления, четвертый выход дешифратора подключен к третьему входу третьего элемента И, пятый выход дешифратора подключен к третьему входу первого элемента И, выход элемента ИЛИ подключен к второму выходу блока управления, выход четвер:того элемента И подключен к счетному входу счетчика, выходы которого соединены с входами дешифратора, шестой выходкоторого подключен к первому, выходу блока управления.

3. Устройство по П.1, отличающееся тем, что вычислительный блок содержит два элемента НЕ, четыре элемента И, два элемента ИЛИ, примем информационный вход вычислительного блока подключен к-первому и второму входам первого элемента И и первого элемента ИЛИ, выход которого соединен с первым входом второго элемента И, второй вход которого подключен к выходу третьего элемента И, первый вход которого подключен к управляющему входу вычислительного блока и к входу элемента НЕ, выход которого соединен с первым входом четвертого элемента И, второй вход которого соединен с вторым входом третьего элемента И.и с выходом второго элемента НЕ, вход которого подключен к управляющему входу вы числительного блока, выход четвертого элемента И соединен с третьим входом первого элемента И, выход которого подключен к первому входу второго элемента ИЛИ, второй вход которого соединен с выходом второго элемента И, а выход второго элемента ИЛИ подключен к выходу вычислительного блока.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР 371580, кл. G Об F 15/00, 1970.

2.Измерения, ко.нтроль, автомати-. зация. 1979, т.20, № 4, с.25-33 (прототип) . ..

fPu. /

| название | год | авторы | номер документа |

|---|---|---|---|

| Система программного управления технологическими процессами | 1989 |

|

SU1688229A1 |

| Устройство для реализации булевых функций | 1982 |

|

SU1032451A1 |

| Устройство для моделирования конечных автоматов | 1980 |

|

SU955080A1 |

| Вычислительное устройство для реализации логических функций | 1983 |

|

SU1269130A1 |

| Устройство для ввода в микроЭВМ дискретных сигналов | 1988 |

|

SU1608679A1 |

| Система программного управления технологическими процессами | 1989 |

|

SU1681297A1 |

| Устройство для последовательного программного управления | 1983 |

|

SU1126928A1 |

| УСТРОЙСТВО ДЛЯ ПРОГРАММНОГО ЛОГИЧЕСКОГО УПРАВЛЕНИЯ ЭЛЕКТРОПРИВОДАМИ, ЭЛЕКТРОННЫМИ КЛЮЧАМИ И СИГНАЛИЗАЦИЕЙ | 1996 |

|

RU2106676C1 |

| Устройство для программного управления | 1985 |

|

SU1348772A1 |

| Устройство для ввода в микроЭВМ дискретных сигналов | 1990 |

|

SU1751772A1 |

м муммм

IWWW itfffe ft

netoenit .

lH fOHyi It pttveinpy

IfHaifMf / Iff.

Л fVfAHWMf f

etfitea fetieem/л

2Г|

ч| 1

:

Авторы

Даты

1982-08-30—Публикация

1980-04-19—Подача