Изобретение относится к электроизмерительной технике и может использоваться в системах релейной защиты и автоматики, использующих составляющие прямой и обратной последовательности.

.Цель изобретения - повышение точности и помехоустойчивости измерения симметричных составляюпцгх путем применения дискретного преобразования Фурье с постоянным шагом дискретизации для осуществления селективной фильтрации основной гармоники, что позволяет полностью ликвидировать влияние гармоник, частоты которых кратны частоте основной гармоники, а погрешность, вносимая другими видами помех и щумом, может быть сведена до произвольной малой величины увеличением времени анализа.

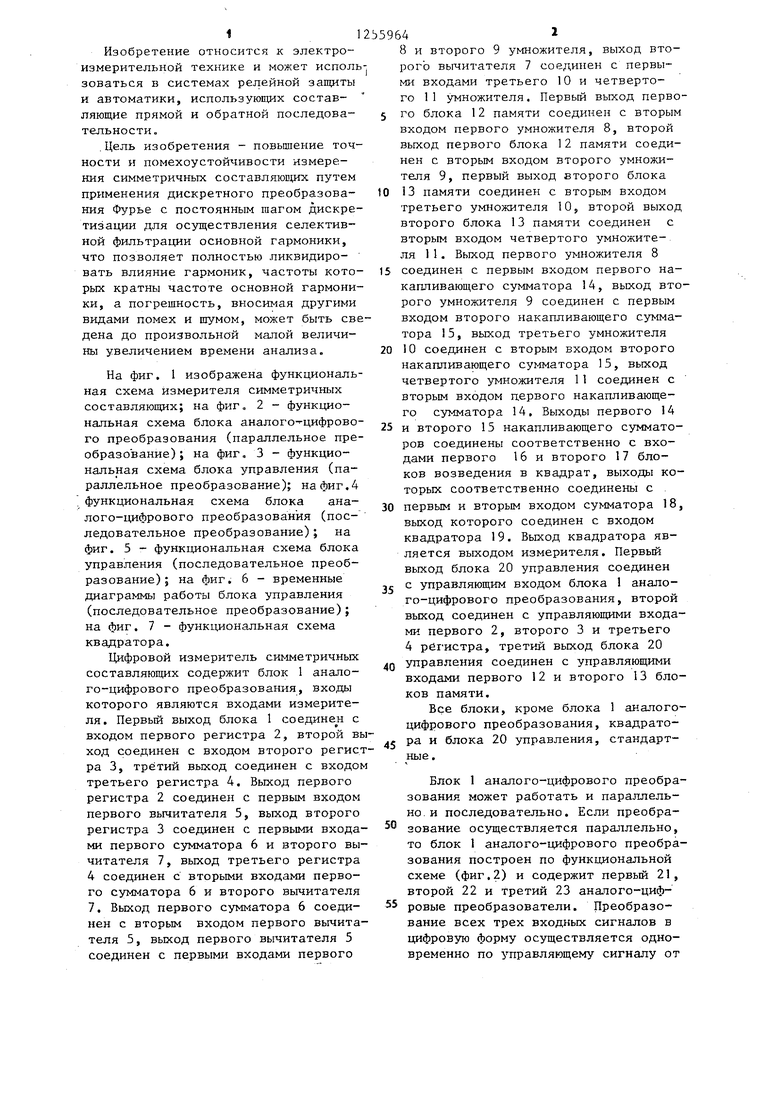

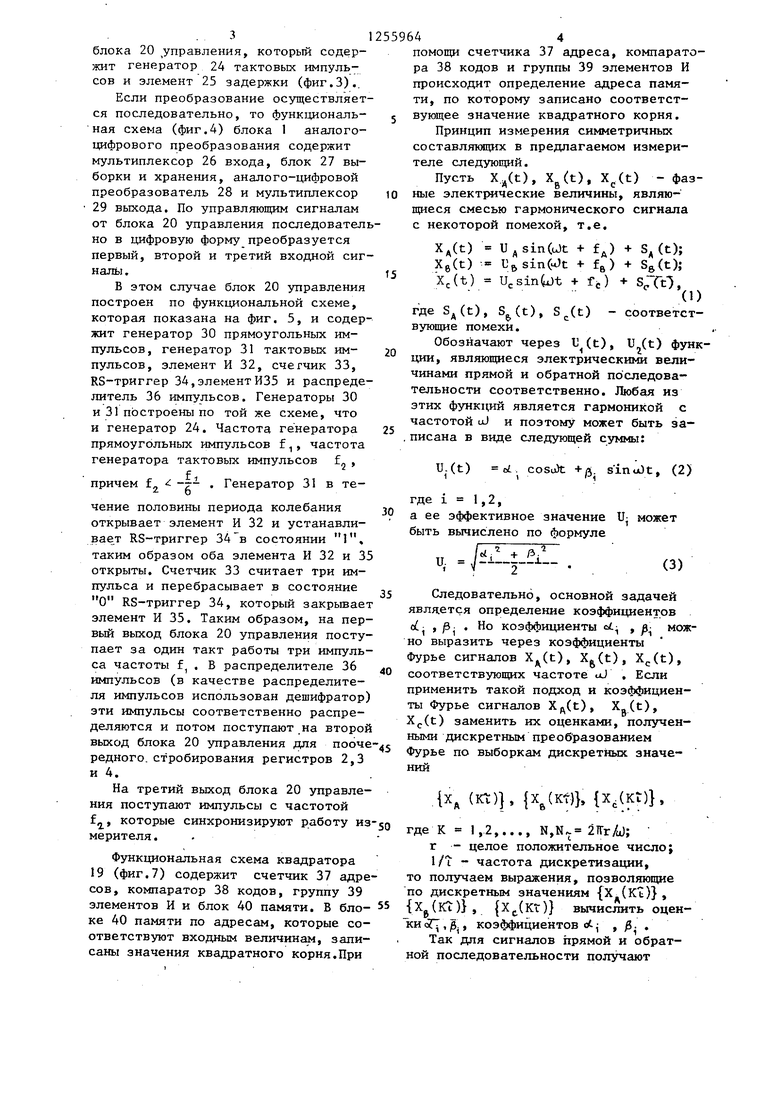

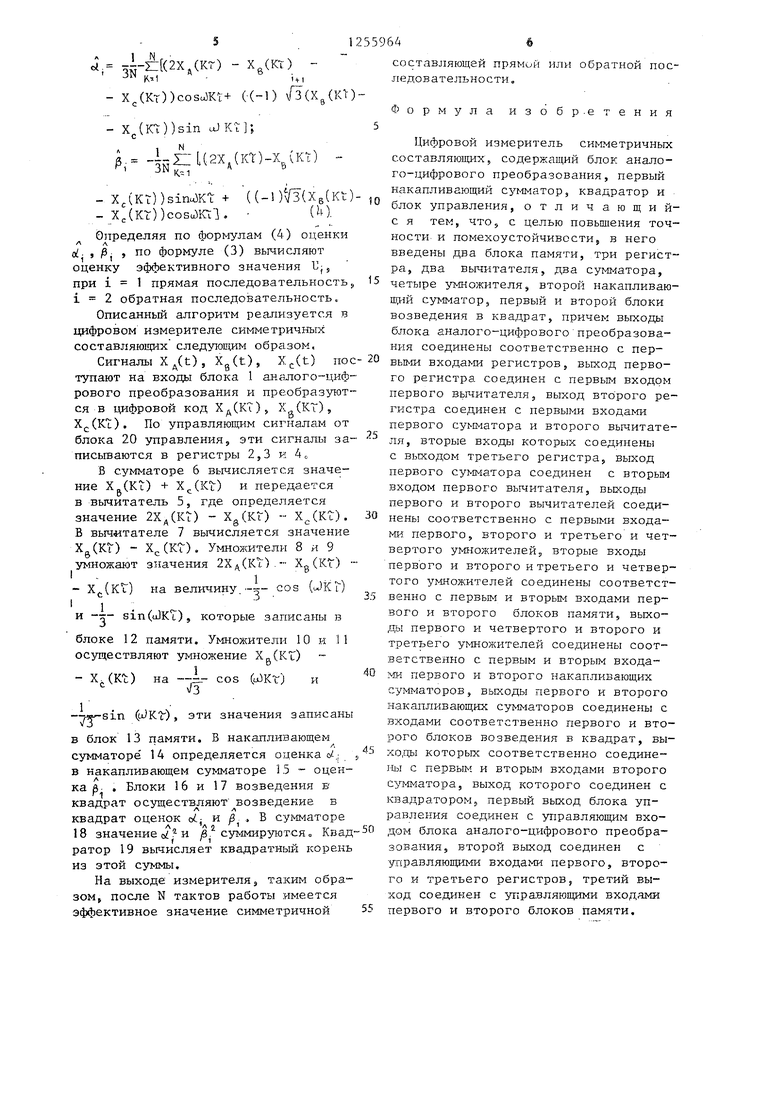

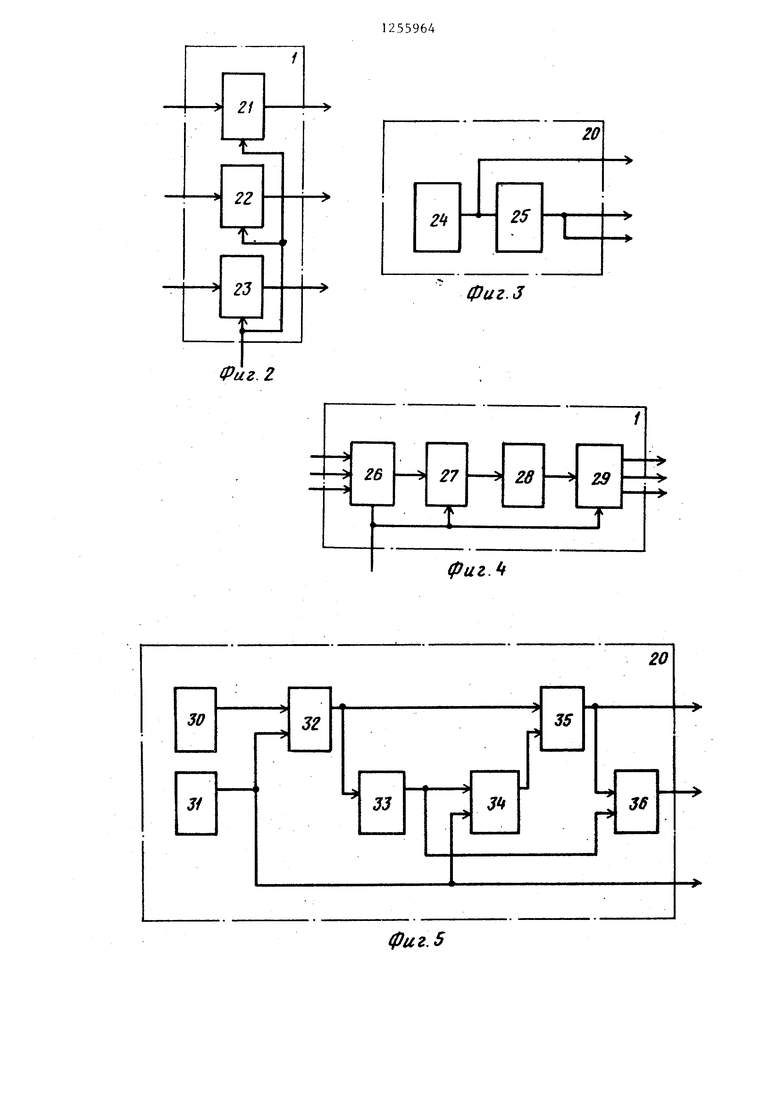

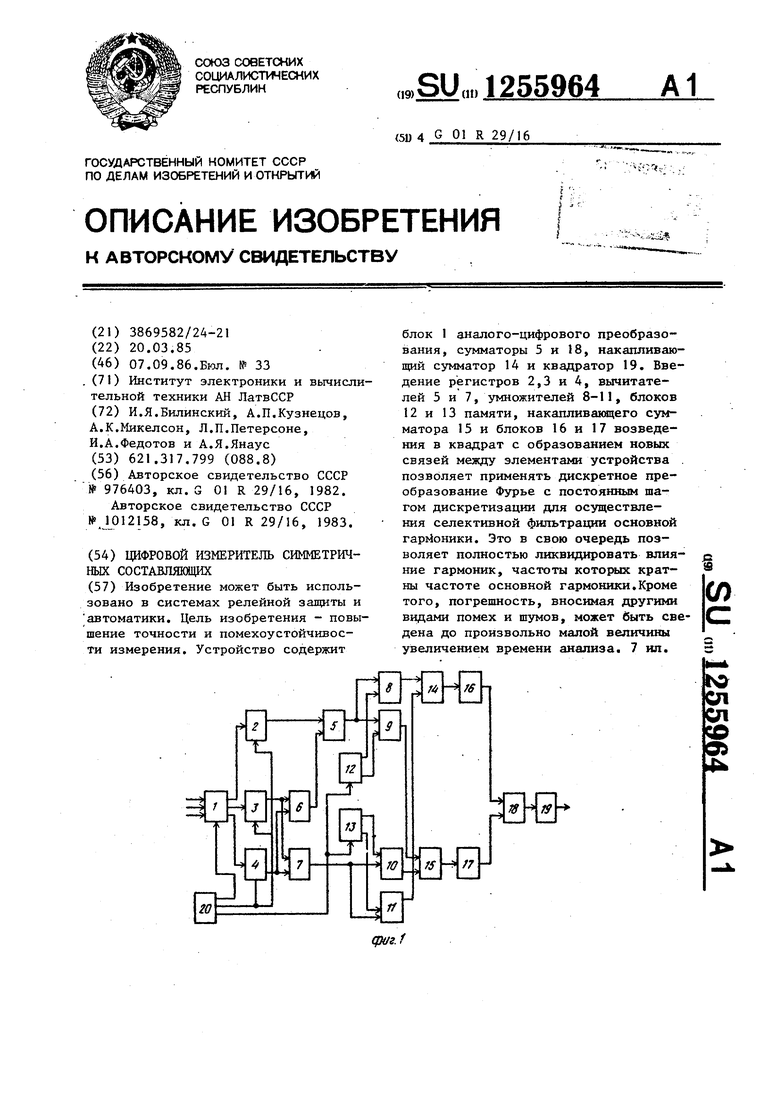

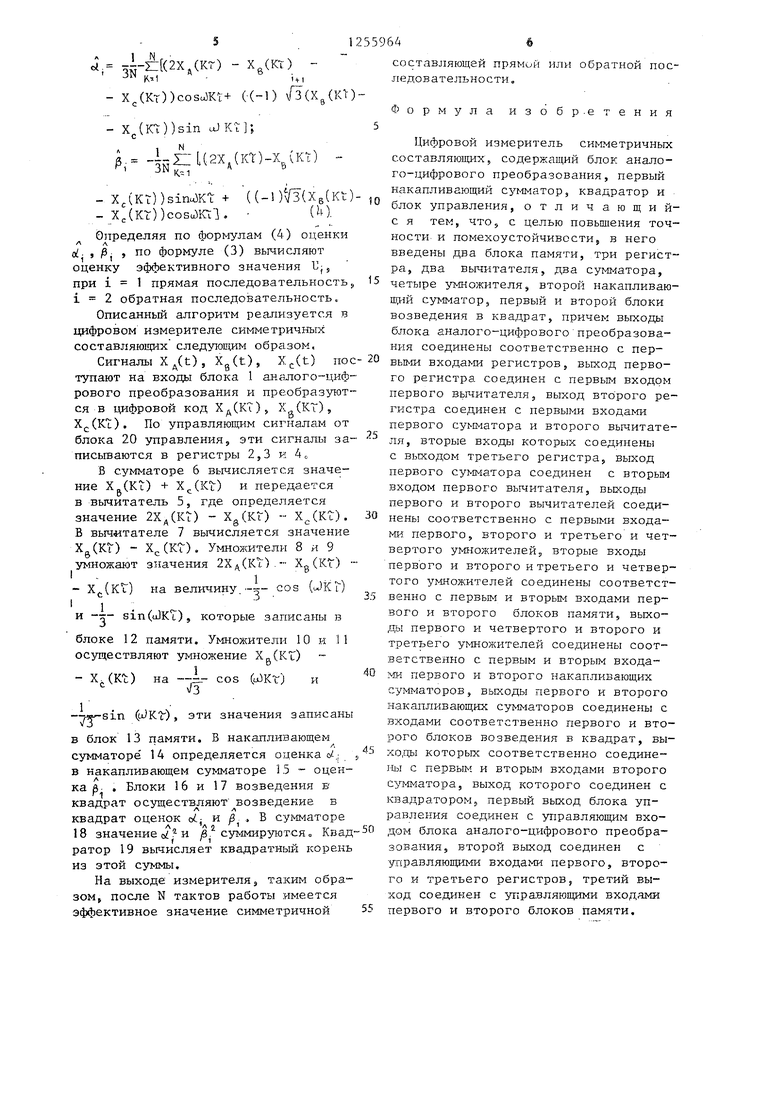

На фиг, 1 изображена функциональная схема измерителя симметричных составляющих; на фиг. 2 - функциональная схема блока аналого- цифрово- го преобразования (параллельное преобразование) ; на фиг. 3 - функциональная схема блока управления (параллельное преобразование); на фиг.4 функциональная схема блока аналого-цифрового преобразования (последовательное преобразование); на фиг. 5 - функциональная схема блока управления (последовательное преобразование) ; на фиг, 6 - временные диаграммы работы блока управления (последовательное преобразование); на фиг, 7 - функциональная схема квадратора.

Цифровой измеритель симметричных составляющих содержит блок 1 аналого-цифрового преобразования, входы которого являются входами измерителя. Первый выход блока 1 соедине с входом первого регистра 2, второй выход соединен с входом второго регистра 3, третий выход соединен с входом третьего регистра 4, Выход первого регистра 2 соединен с первым входом первого вьгчитателя 5, выход второго регистра 3 соединен с первыми входами первого сумматора 6 и второго вы- читателя 7, выход третьего регистра 4 соединен с вторыми входами первого сумматора 6 и второго вьтитателя 7, Выход первого сумматора 6 соединен с вторым входом первого вычита- теля 5, выход первого вычитателя 5 соединен с первыми входами первого

8 и второго 9 умножителя, выход второго вьгчитателя 7 соединен с первыми входами третьего 10 и четвертого 11 умножителя. Первый выход первого блока 12 памяти соединен с вторым входом первого умножителя 8, второй выход первого блока 12 памяти соединен с вторым входом второго умножителя 9, первый выход второго блока

13 памяти соединен с вторым входом третьего умножителя 10, второй выход второго блока 13 памяти соединен с вторым входом четвертого умножите-, ля 11, Выход первого умножителя 8

соединен с первым входом первого накапливающего сумматора 14, выход второго умножителя 9 соединен с первым входом второго накапливающего сумматора 15, выход третьего умножителя

10 соединен с вторым входом второго накапливающего сумматора 15, выход четвертого умножителя 11 соединен с вторым входом первого накапливающего сумматора 14, Выходы первого 14

и второго 15 накапливающего сумматоров соединены соответственно с входами первого 16 и второго 17 блоков возведения в квадрат, выходы которых соответственно соединены с

первым и вторым входом сумматора 18, выход которого соединен с входом квадратора 19, Выход квадратора является выходом измерителя. Первый выход блока 20 управления соединен

с управляющим входом блока 1 аналого-цифрового преобразования, второй выход соединен с управляющими входами первого 2, второго 3 и третьего 4 регистра, третий выход блока 20

управления соединен с управляющими входами первого 12 и второго 13 блоков памяти.

Все блоки, кроме блока 1 аналого- цифрового преобразования, квадратора и блока 20 управления, стандарт- mie,

Блок 1 аналого-цифрового преобразования может работать и параллельно, и последовательно. Если преобра

зование осуществляется параллельно.

то блок 1 аналого-цифрового преобразования построен по функциональной схеме (фиг,2) и содержит первый 21, второй 22 и третий 23 аналого-циф- ровые преобразователи. Преобразование всех трех входных сигналов в цифровую форму осуществляется одновременно по управляющему сигналу от

блока 20 управления, который содержит генератор 24 тактовых импульсов и элемент 25 задержки (фиг.З)..

Если преобразование осуществляется последовательно, то функциональ- ная схема (фиг.4) блока 1 аналого- цифрового преобразования содержит мультиплексор 26 входа, блок 27 выборки и хранения, аналого-цифровой преобразователь 28 и мультиплексор 29 выхода. По управляющим сигналам от блока 20 управления последовательно в цифровую форму преобразуется первый, второй и третий входной сигналы.

В этом случае блок 20 управления построен по функциональной схеме, которая показана на фиг. 5, и содержит генератор 30 прямоугольных импульсов, генератор 31 тактовых им- пульсов, элемент И 32, счегчик 33, RS-триггер 34,элементИЗЗ и распределитель 36 импульсов. Генераторы 30 и 31 построены по той же схеме, что и генератор 24. Частота генератора прямоугольных импульсов f,, частота генератора тактовых импульсов f,

причем „ - -т- . Генератор 31 в те2 D

чение половины периода колебания открывает элемент И 32 и устанавливает RS-триггер 34 в состоянии 1. таким образом оба элемента И 32 и 35 открыты. Счетчик 33 считает три импульса и перебрасывает в состояние О RS-триггер 34, который закрьшает элемент И 35. Таким образом, на первый выход блока 20 управления поступает за один такт работы три импульса частоты f, . В распределителе 36 импульсов (в качестве распределителя импульсов использован дешифратор) эти импульсы соответственно распределяются и потом поступают на второй выход блока 20 управления для пооче редного. стробирования регистров 2,3 и 4.

На третий выход блока 20 управления поступают импульсы с частотой f, которые синхронизируют работу из мерителя. .

Функциональная схема квадратора 19 (фиг.7) содержит счетчик 37 адресов, компаратор 38 кодов, группу 39 элементов И и блок 40 памяти. В бло- ке 40 памяти по адресам, которые соответствуют входным величинш, записаны значения квадратного корня.При

jю Т5

2025

зо о

помощи счетчика 37 адреса, компаратора 38 кодов и группы 39 элементов И происходит определение адреса памяти, по которому записано соответствующее значение квадратного корня.

Принцип измерения симметричных составлякяцих в предлагаемом измерителе следующий.

Пусть X,,(t), Xg(t), Xj,(t) - фазные элект1жческие величины, являющиеся смесью гармонического сигнала с некоторой помехой, т.е.

Хд(с) (u)t + д) + S(t); Xe(t) UE,sin( Jt + fe) Se,(t);

X,(t) + fc) + ,

где S(t), S(t), S(t) - соответст- вукнцие помехи.

Обозначают через I (t), U (t) Фзшк- ции, являющиеся электрическими величинами прямой и обратной по следова- тельности соответственно. Любая из этих функций является гармоникой с частотой oJ и поэтому может быть записана в виде следующей суммы:

и. (t) ot. coso)t +|5. s inoOt, (2)

где i 1,2,

а ее эффективное значение U- может

быть вычислено по формуле

,./5тц:21.

(3)

Следовательно, основной задачей является определение коэффициентов 0 , . Но коэффициенты bt , можно выразить через коэффициенты Фурье сигналов X(t), X(t), Xj.(t), соответствующих частоте oJ . Если применить такой подход и коэффициенты Фурье сигналов X((t), X-(t), Xp(t) заменить их оценками, полученными дискретным преобразованием Фурье по выборкам дискрет иых значений

.{X, (Kt), {X(Kt)}, {X,(Kt)}.

где к 1,2,..., N,N.. 21ГгА); г - целое положительное число; 1/1 частота дискретизации, то получаем выражения, позволяющие по дискретным значениям {Х.(Ки)} , {Х (Кл)}, |X(.(Kt)} вычислить оцеи- киог,Д., коэффициентов otj , - .

Так для сигналов прямой и обратной последовательности получают

Ы, (2Х,(КГ) - Х(КТ) - Кт1 HI

-X(KT))cosa)Kt+ С(1) ГЗ(Х/КП

-xjKi;))sin cJKtJ;

.- -т(.-

-х,(кг))з1пцжг + ((-O VKXglKt)

))cosa)iai, (0.

Определяя по формулам (4) оценки d- , - ) по формуле (3) вычисляют оценку эффективного значения L j, при 1 1 прямая последовательность,, обратная последовательность.

Описанный алгоритм реализуется в цифровом измерителе симметричных составляющих следующим образом,

Сигналы Xд(t), Xg(t), Xj.(t) нос тупают на входы блока 1 аналого-цифрового преобразования и преобразуются в цифровой код ХдСКТ), 7vg(KT), X(Kt). По управляющим сигналам от блока 20 управления, эти сигналы за- письгааются в регистры 2,3 и 4„

В сумматоре 6 вычисляется значение XjjCKt) + X() и передается в вычитатель 5, где определяется значение 2Хд(КГ) - Хд(КГ) - Х(кг). В выч«тателе 7 вычисляется значение Х(КГ) - Х(КГ). Умножители 8 и 9 умножают значения 2Хд(К 1).- X(Kt) - X,.(Kt) на величину, о- cos (JKt)

1 . ,- и -г- sinCiJKT), которые записаны в

блоке 12 памяти. Умножители 10 и П осуществляют умножение )

- ХЛкг) на --1- cos (u)Kt) и

--fv-sin (cJKt), эти значения записаны- в блок 13 памяти. В накапливающем

Лсумматоре 14 определяется оценка с/,; в накапливающем сумматоре 15 - оценка р. . Блоки 16 и 17 возведения в квадрат осущестБ яют возведение в квадрат оценок oL к . В сумматоре 18 значение of : и суммируются, Квад ратор 19 вычисляет квадратный корень из этой суммы.

На выходе измерителя, таким образом , после N тактов работы имеется эффективное значение симметричной

составляющей прямой или обратной последовательности.

1)ормула изобр.етения

Цифровой измеритель симметричных составляющих, содержащий блок аналого-цифрового преобразования, первый накапливающий сумматор, квадратор и блок управления, отличающий- с я тем, что, с целью повьщ1ения точности и помехоустойчивости в него введены два блока памяти, три регистра, два вычитателя, два сумматора, четыре умножителя, второй накапливающий сумматор, первый и второй блоки возведения в квадрат, причем выходы блока аналого-цифрового преобразования соединены соответственно с первыми входами регистров, выход первого регистра, соединен с первым входом первого вьгчитателя, выход второго регистра соединен с первыми входами первого сумматора и второго вычитателя, вторые входы которых соединены с выходом третьего регистра, выход первого сумматора соединен с вторым входом первого вычитателя, выходы первого и второго вычитателей соединены соответственно с первыми входами первого, второго и третьего и четвертого умножителей, вторые входы первого и второго и третьего и четвертого умножителей соединены соответственно с первым и вторым входами первого и второго блоков памяти, выходы первого и четвертого и второго и третьего умножителей соединены соответственно с первым и вторым входа- 1ЧИ первого и второго накапливающих сумматоров, выходы первого и второго накапливающих сумматоров соединены с входами соответственно первого и второго блоков возведения в квадрат, выходам которых соответственно соединены с первым и вторым входами второго сумматора, выход которого соединен с квадратором, первый выход блока управления соединен с управляющим входом блока аналого-цифрового преобразования, второй выход соединен с управляющими входами первого, второго и третьего регистров, третий выход соединен с управляюищми входами первого и второго блоков памяти.

го

Zft

25

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для фильтрации симметричных составляющих | 1985 |

|

SU1343362A1 |

| Цифровой измеритель коэффициента гармоник | 1988 |

|

SU1580276A1 |

| Устройство для измерения фазовых сдвигов | 1984 |

|

SU1226341A1 |

| СЧЕТЧИК ПОТЕРЬ АКТИВНОЙ ЭЛЕКТРОЭНЕРГИИ В ТРАНСФОРМАТОРЕ | 2015 |

|

RU2589498C1 |

| Устройство для сжатия и передачи информации | 1988 |

|

SU1515183A1 |

| Анализатор спектра с линейным предсказанием | 1985 |

|

SU1275315A1 |

| Цифровой измеритель коэффициента гар-МОНиК | 1979 |

|

SU805195A1 |

| Анализатор гармоник | 1988 |

|

SU1663571A1 |

| Устройство для выбора частотных диапазонов передачи группового радиосигнала | 1982 |

|

SU1072277A1 |

| Устройство для вычисления коэффициентов Фурье | 1983 |

|

SU1096655A1 |

Изобретение может быть использовано в системах релейной залщты и автоматики. Цель изобретения - повышение точности и помехоустойчивости измерения. Устройство содержит блок 1 аналого-цифрового преобразования, сумматоры 5 и 18, накапливающий сумматор 14 и квадратор 19. Введение регистров 2,3 и 4, вычитате- лей 5 и 7, умножителей 8-11, блоков 12 и 13 памяти, накапливакщего сумматора 15 и блоков 16 и 17 возведения в квадрат с образованием новых связей между элементами устройства . позволяет применять дискретное преобразование Фурье с постоянным шагом дискретизации для осуществления селективной фильтрации основной гармоники. Это в свою очередь позволяет полностью ликвидировать влияние гармоник, частоты которых кратны частоте основной гармоники,Кроме того, погрешность, вносимая другими видами помех и шумов, может быть сведена до произвольно малой величины увеличением времени анализа. 7 ил. § (Л сл ел ;о Од

23

iPuz.Z

30

зг

J/

фиг.З

rt

J5

JJ

J«

л

J

фиг. 5

фаг 5

39

ЦО

Редактор Н.Данкулич

Составитель Н,Михалев Техред М.Ходанич

Заказ 4818/45Тираж 728Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

фиг.7

Корректор А.Обручар

| Цифровой измеритель симметричных составляющих трехфазной сети | 1981 |

|

SU976403A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Цифровой измеритель симметричных составляющих трехфазной сети | 1981 |

|

SU1012158A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1986-09-07—Публикация

1985-03-20—Подача