Изобретение относится к вычислительной технике и может быть использовано в системах управления автоматизированными электроприводами.

Цель изобретения - повышение точности при интегрировании медленно меняющихся сигналов.

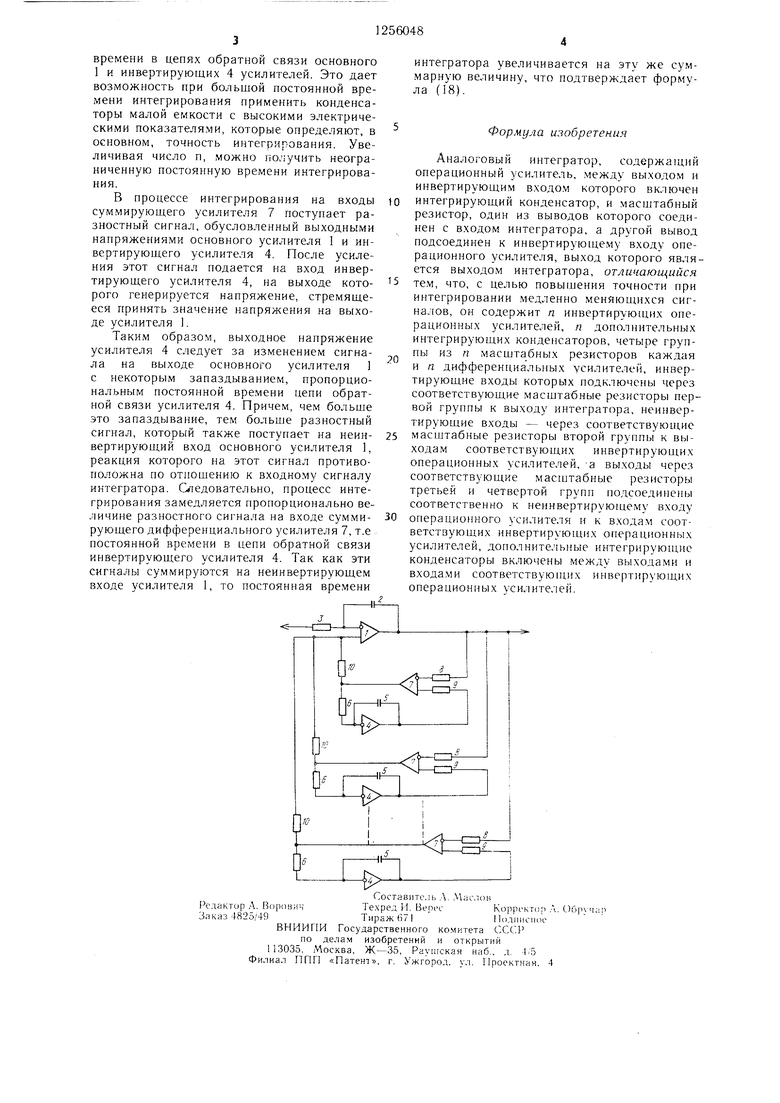

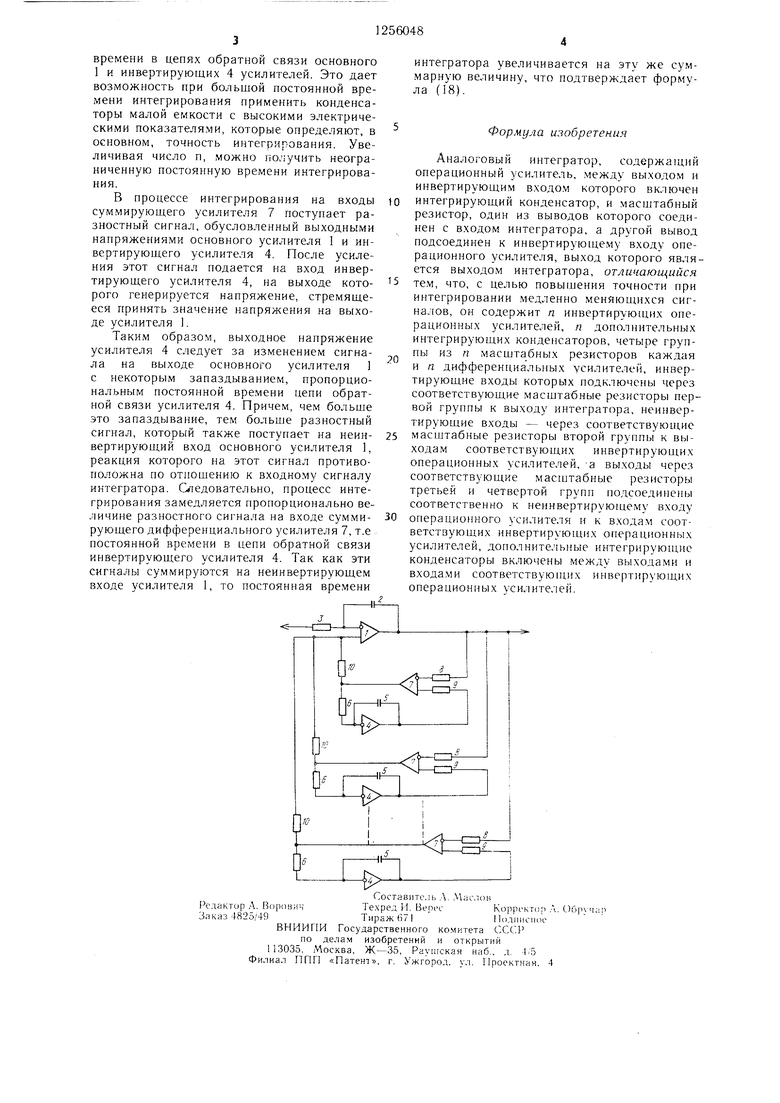

На чертеже представлена схема аналогового интегратора.

Интегратор содержит основной операционный усилитель 1 с интегрирующим конденсатором 2 в цепи обратной связи и входным масштабным резистором 3, п инвертирующих операционных усилителей 4 с дополнительными интегрирующими конденсаторами 5 в цепях обратных связей и группой (третьей) входных и масщтабныд резисторов 6, п дифференциальных усилителей 7, инвертирующие входы которых подключены через первую группу масщтабных резисторов 8 к выходу интегратора. Неинвертирующие входы дифференциальных усилителей 7 через вторую группу масщтабных резисторов 9 соединены с выходами соответствующих инвертирующих усилителей 4. Выходы дифференциальных усилителей 7 соединены через четвертую группу масщтабных резисторов 10 с неинвертирующим входом основного операционного усилителя 1 и с соответствующими резисторами 6.

Интегратор работает следующим образом.

Для упрощения анализа работы аналогового интегратора примем, что схема содержит один инвертирующий операционный усилитель 4 и соответственно один суммирующий дифференциальный усилитель 7, т.е. п 1. Составим уравнения для контурных токов рассматриваемой .схемы согласно закону Кирхгофа:

UBX UBX.I 1Гз ,

.- ивых. - S i2dt; UBUX.- Usx.7 зГв;

ивых.4UBX.7 14Г9;

Usi-i -UBIU.Y is Гад ;

UBX.4- ивых.7 1бГб;

UBX.4ивых.4 J iydt,

(1)

(2); (3) (4) (5) (6)

(7)

е UBX. - входное напряжение интегратора; UBUX. - выходное напряжение интегратора;

-напряжение на инвертирующем входе основного усилителя;

-напряжение на неинвертирующем входе основного усилителя;

-напряжение на инвертирующем входе дифференциального усилителя 7;

-напряжение на неинвертирующем входе дифференциального усилителя 7;

UBUX.,, - выходное напряжение дифференциального усилителя 7;

UBX.4 - входное напряжение инвертирующего усилителя 4;

UB.,

Uti .7

Utx.7

ивых.4-выходное напряжение инвертирующего усилителя 4; ii -входной ток интегратора; 2 - ток через интегрирующий кондентор 2;

1з - ток через масштабный резистор 8; 4 -ТОК через масштабный резистор 9; is - ток через масщтабный резистор 10;

ie -ток через масштабный резистор 6; i7 - ток через интегрирующий конденсатор 5;

гз, Гб, Г8, - сопротивления соответственно. гэ, гю масщтабных резисторов 3, 6, 8,

9, 10.

Уравнение можно дополнить условиями, вытекающими из свойств включения идеального операционного усилителя

ii i2;(8)

i6 (9)

(10)

UB X. UBX.,;(11)

UB X.| ивых.у;(12)

Выражения (1) - (12) можно упростить и

привести к виду

UBX.Iивых. -f J

UBX.UBX. I

dt;

;i3)

I

Решая совместно уравнения получим;

UBX.dt

ивых.

LjEblX- :

1

С2ГЗ+ СбГб

i

j Uex.dt,

(14)

;i3) и (14),

(15) (16)

TO+T

где TO С2ГЗ - постоянная времени цепи обратной связи основного усилителя 1;

TI СбГб - постоянная времени цепи обратной связи первого инвер- ртирующего усилителя 4. 0 Повторяя анализ схемы для л инвертирующих усилителей 4 и п дифференциальных усилителей 7, придем к конечной фор муле

45

(jBbJX. TfT

0)

1о+ 1+ i2-t----+ 1л J

т„

где Т2 - постоянная времени цепи обратной связи второго инвертирующего усилителя 4;

постоянная времени цепи обратной связи п-го инвертирующего усилителя 4.

Приняв Т| Т2 .... Тп, ние (17) перепишется

i (18)

выражеUBUX.: -

To-f пТ

j UBX.dt.

Таким образом, постоянная времени интегратора определяется суммой постоянной

времени в цепях обратной связи основного 1 к инвертирующих 4 усилителей. Это дает возможность при большой постоянной времени интегрирования применить конденсаторы малой емкости с высокими электрическими показателями, которые определяют, в основном, точность интегрирования. Увеличивая число п, можно гю.чучить неограниченную постоянную времени интегрирования.

В процессе интегрирования на входы суммируюш,его усилителя 7 поступает разностный сигнал, обусловленный выходными напряжениями основного усилителя 1 и инвертирующего усилителя 4. После усиления этот сигнал подается на вход инвертирующего уси.тителя 4, на выходе которого генерируется напряжение, стремящееся принять значение напряжения на выходе усилителя 1.

Таким образом, выходное напряжение усилителя 4 следует за изменением сигнала на выходе основного усилителя 1 с некоторым запаздыванием, пропорциональным постоянной времени цепи обратной связи усилителя 4. Причем, чем больще это запаздывание, тем больше разностный сигнал, которьгй также поступает на неин- вертирующ.ий вход основного усилителя 1, реакция которого на этот сигнал противоположна по отношению к входному сигналу интегратора. Следовательно, процесс интегрирования замедляется пропорционально величине разностного сигнала на входе суммирующего дифференциального усилителя 7, т.е постоянной времени в цепи обратной связи инвертирующего усилителя 4. Так как эти сигналы суммируются на неинвертирующем входе усилителя 1, то постоянная времени

интегратора увеличивается на эту же суммарную величину, что подтверждает формула (8).

Формула изобретения

Аналоговый интегратор, содержащий операционный усилитель, между выходом и инвертирующим входом которого включен

интегрирующий конденсатор, и масштабный резистор, один из выводов которого соединен с входом интегратора, а другой вывод подсоединен к инвертируюп 1,ему входу операционного усилителя, выход которого является выходом интегратора, отличающийся

тем, что, с целью повышения точности при интегрировании медленно меняющихся сигналов, он содержит п инвертирующих операционных усилителей, п дополнительных интегрирующих конденсаторов, четыре группы из п масштабных резисторов каждая и п дифференциальных усилителей, инвертирующие входы которых подключены через соответствующие масшта-бные резисторы первой группы к выходу интегратора, неинвертирующие входы - через соответствующие

масштабные резисторы второй группы к выходам соответствующих инвертируюпшх операционных усилителей, а выходы через соответствующие MacnjTa6Hbie резисторы третьей и четвертой групп подсоединены соответственно к неинвертируюгцему входу

операционного усилителя и к входам соответствующих инвертирующих операционн1 1х усилителей, дополните, интегрирующие конденсаторы включены между выходами и входами соответствующих инвертирующих операционных усилителей.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналоговый интегратор | 1979 |

|

SU834714A1 |

| Интегратор | 1979 |

|

SU834715A1 |

| Интегратор | 1980 |

|

SU928369A1 |

| Интегратор | 1983 |

|

SU1198546A1 |

| Интегратор со сбросом | 1984 |

|

SU1260977A1 |

| Операционный усилитель с периодической компенсацией смещения нуля | 1982 |

|

SU1024938A1 |

| Устройство для интегрирования сигнала | 1984 |

|

SU1201853A1 |

| ИНТЕГРАТОР С БОЛЬШИМ ВРЕМЕНЕМ ИНТЕГРИРОВАНИЯ | 1992 |

|

RU2034331C1 |

| Устройство для интегрирования сигнала | 1981 |

|

SU960853A1 |

| Интегратор | 1978 |

|

SU748439A1 |

Изобретение относится к вычислительной технике и может быть использовано в системах управления автоматизированными электроприводами. Цель изобретения - повышение точности при интегрировании медленно меняющихся сигналов. Интегратор содержит основной операционный усилитель с интегрирующим конденсатором в цепи обратной связи и входным масштабным резистором, п инвертирующих операционных усилителей с дополнительными интегрирующими конденсаторами в цепях обратных связей и группой входных масштабных резисторов, п дифференциальных усилителей и еще три группы из п масштабных резисторов. Достижение поставленной цели обеспечено благодаря введению в интегратор п инвертирующих операционных усилителей, дополнительных интегрирующих конденсаторов, четырех групп из п масштабных резисторов каждая, п дифференциальных усилителей и благодаря новым связям между элементами интегратора. 1 ил. (Л N: СП О) о 1 00

Составите.1ь Л. ,1ов

i e. UiKTop .. В()р 1в;1ЧТехред И. ВересКорректор Л. Обручар

Заказ 4825/49Тираж 671Подписное

ВНИИГ1И Государственного ко.митета ССС}

по дела.ч изобретений и открытий

113035, Москва. Ж-35, Раушская наб.. л, 4/5

Филиал ППП «Патент, г. Ужгород, ул. Проектная. 4

| ИНТЕГРАТОР | 0 |

|

SU363988A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Справочник по аналоговой вычислительной технике./Под ред | |||

| акад | |||

| Г | |||

| Е | |||

| Пухова | |||

| Киев: Техника, 1975, с | |||

| Нефтяной конвертер | 1922 |

|

SU64A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1986-09-07—Публикация

1985-01-03—Подача