1

Изобретение относится к полупроводниковой электронике и может использоваться для преобразования уровней электрических сигналов, в частности для преобразования уровней сигналов транзисторно-транзисторной логики (ТТЛ) в уровни сигналов логики на комплементарных полевых транзисторах с изолированным затвором (км ДП) или в уровни питания приборов с зарядовой связью (ПЗС).

Цель изобретения - повышение быстродействия преобразователя уровней На фиг. 1 и 2 изображены соответственно преобразователи уровней по первому и второму вариантам, предназначенные для преобразования положительного входного в положительное выходное напряжение.

Преобразователь уровня по первому варианту содержит восемь МОП-транзисторов 1-8, из которых 1, 4 образуют первую комплементарную пару, а 2, 5 и 3, 6 вторую и третью, из которых первая включена между первой 9 и второй 10 шинами питания, а вторая и третья - между первой 9 и третьей 11 шинами питания, затворы транзисторов 1, 4,3 и 7 соединены с входной шиной 12, затворы транзисторов 2 и 8 - с выходом первой пары (сток транзистора 1), а затворы транзисторов 5 и 6 с выходами соответственно третьей .(сток транзистора 3) и второй (сток транзисто- 5 2) пар, причем транзисторы 7 и 8 включены между второй шинЬй 10 питания и стоками транзисторов 2 и 3, соединенных соответственно с выходными шинами 13 и 14.

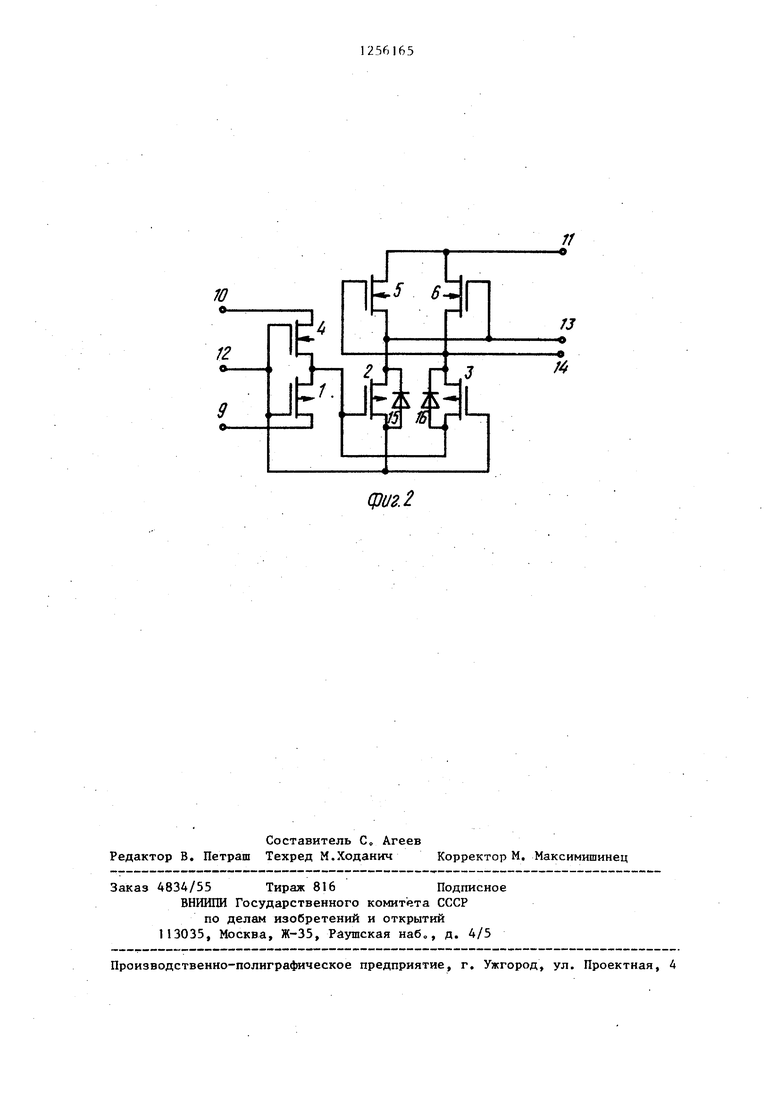

Преобразователь уровня по в гором варианту содержит шесть транзисторов 1-6, образующих три комплементарные пары, из которых 1, 4 образуют первую комплементарную пару, включенную между первой и второй шинами 9 и 10 питания, 2, 5 - вторую, включенную между входной шиной 12 и третьей шиной 11 питания, 3, 6 .- третью, включенную между выходом первой пары (сток транзистора 9) и третьей шиной П питания, и два диода 15 и 16, включенные встречно- параллельно транзисторам 2 и 3 соот

ветственно, причем затворы транзисторов 1, 3 и 4 соединены с входной шиной 12, затвор транзистора 2 - со стоком транзистора 1, а затворы

5

2

транзисторов. 5 и 6 - с выходами соответственно третьей (сток транзистора 3) и второй (сток транзистора 2) пар.

Преобразователь уровней по первому варианту работает следующим образом.

Транзисторы 1 и 4 образуют инвертор входного сигнала и служат для формирования на двух входах триггера, образованного транзисторами 2, 3, 5 и 6, взаимоинверсных сигналов управления.

Пусть в исходном состоянии на входной шине 12 присутствует нуле- . вой потенциал (потенциал шины 9). Транзисторы 4, 2 и 6 открыты, а ос

тальные закрыты. На шине 13 присутствует потенциал шины 9, на шине 14- потенциал шины 11.

При изменении уровня сигнала на входной шине 12 на единичный потенциал (потенциал шины 10) транзистор 7 открывается и фо: сированно перезаряжает область стока трензистора 5. Это изменение, воздействуя на затвор транзистора 6, вызьшает его подзапи- рание. Одновременно единичный потен- циал входной шины отпирает транзистор 3. Таким образом, отпирание транзистрра 3 и запирание транзистора 6 происходят одновременно и регенеративный процесс опрокидывания триггера на транзисторах 2, 3, 5 и 6 происходит быстрее, причем в данном случае пороговые свойства транзистора 5 не влияют на этот процесс, г После окончания переходных процессов транзисторы 4, 3 и 5 оказываются открытыми, на шине 13 присутствует потенциал шины 11, а на шине 14 - потенциал шины 9,

Преобразователь уровней по второму варианту работает следующим образом.

Пусть в исходном состоянии на входной шине 12 присутствует нуле-. вой потенциал (потенциал шины 9). Транзисторы 4, 2 и 6 открыты, а остальные закрыты На шине 13 присутствует потенциал шины 9, а на шине 14 - потенциал шины П.

При изменении уровня сигнала на входной шине 12 на единичный потен- циал (потенциал шины 10) транзисторы 1 и 3 открываются. Одновременно входной сигнал через открытый ди- од 15 перезаряжает область стока

31

транзистора 5, подзапирая транзистор 6. Таким образом, как и в первом варианте, отпирание транзистора 3 и запирание транзистора 6 происходят одновременно и регенеративный процес опрокидывания схемы осуществляется быстрее, причем пороговые свойства транзистора 5 не влияют на этот процесс. После окончания опрокидывания схемы транзисторы 1, 3 и 5 оказыва- ются открытыми, а остальные закрытыми. На шине 13 присутствует потенциал шины II, а на шине 14 - потенциал шины 9.

Для преобразования положительного входного напряжения в биполярное выходное тип проводимости всех транзисторов изменяется на противоположный, вторая шина питания соединяется с общим проводом, к первой шине под- ключ ается положительная ЭДС, к третьей - отрицательная.

По сравнению с известным быстродействие предлагаемого преобразователя уровней повьш1ается за счет разре- шения технического противоречия между необходимостью сохранения ключевого режима схемы для обеспечения ее экономичности и необходимостью ее перевода в линейный режим для повы- шения быстродействия. В начальные моменты переключения в качестве активных элементов выступают введенные транзисторы или диоды, которые закрываются после начала регенеративно- го процесса перебрасывания триггера.

Ф о р м ула изобретения

1. Преобразователь уровней, со- держащий шесть МОП-транзисторов, образующих три комплементарные пары, из которых первая включена между первой и второй шинами питания, а вторая и третья - между первой и третьей шинами питания, затворы

654

транзисторов первой пары и МОП-транзистора первого типа третьей пары соединены с входной шиной, затвор транзистора первого типа второй пары - с выходом первой пары, а затворы МОП транзисторов второго типа второй и третьей пар - с выходами третьей и второй пары соответственно, соединенными также с соответствующими выходными шинами, отличающийся тем, что, с целью повышения быстродействия, в него введены седьмой и восьмой МОП-тран- зиcтJOpы первого типа, включенные между выходами соответственно второй и третьей пары и второй шиной питания, причем их затворы соединены соответственно с входной шиной и выходом первой пары.

2. Преобразователь уровней, содержащий шесть МОП-транзисторов, образующих три комплементарные пары, из которых первая включена между первой и второй шинагог питания, а вторая и третья истоками МОП-транзисторов второго типа соединены с третьей шиной питания, затворы транзисторов первой пары и транзистора первого типа третьей пары соединены с входной шиной, затвор транзистора первого типа второй пары - с выходом первой пары, а затворы транзисторов второго типа второй и третьей пар - с выходами третьей и второй пары соответственно, соединенными также с выходными шинами, отличающийся тем, что, с целью повышения быстродействия, в него ведены первый и второй диоды, вклюенные встречно-параллельно транисторам первого типа второй и треьей пары, причем истоки транзистоов первого типа второй и третьей ары соединены соответственно с ходной шиной и выходом первой пары.

70

ПР

Ц

JrlfifiL

/J

/

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналоговое запоминающее устройство | 1980 |

|

SU890440A1 |

| Преобразователь уровней сигналов на МДП-транзисторах | 1988 |

|

SU1538246A1 |

| ВЫХОДНОЙ ФОРМИРОВАТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ С УСТРОЙСТВОМ ЗАЩИТЫ ОТ ЭЛЕКТРОСТАТИЧЕСКИХ РАЗРЯДОВ ДЛЯ КМОП МИКРОСХЕМ | 2013 |

|

RU2540813C1 |

| ЛОГИЧЕСКИЙ ВЕНТИЛЬ | 2014 |

|

RU2546302C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ КОМПАРАТОР С ВЫБОРКОЙ ВХОДНОГО СИГНАЛА | 2008 |

|

RU2352061C1 |

| КОМПАРАТОР ДВОИЧНЫХ ЧИСЕЛ | 2021 |

|

RU2762061C1 |

| БАЗОВЫЙ УСИЛИТЕЛЬНЫЙ ЭЛЕМЕНТ ДИФФЕРЕНЦИАЛЬНОЙ ДИНАМИЧЕСКОЙ ЛОГИКИ (ВАРИАНТЫ) | 1999 |

|

RU2154338C1 |

| ЭЛЕМЕНТ ВХОДНОГО РЕГИСТРА | 2022 |

|

RU2787930C1 |

| Логическая матрица на основе мемристорной коммутационной ячейки | 2017 |

|

RU2643650C1 |

| ЯЧЕЙКА ПАМЯТИ СТАТИЧЕСКОГО ОПЕРАТИВНОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 2012 |

|

RU2507611C1 |

Изобретение относится к полупроводниковой электронике. Может использоваться для преобразования уровней электрических сигналов, в частности для преобразования уровней сигналов транзисторно-транзисторной логики в уровни сигналов логики на 7ff 12 ПЕ 9 комплементарных полевых транзисторах с изолированным затвором или в уровни сигналов приборов с зарядовой связью. Цель изобретения - повышение быстродействия - достигается за счет того, что в преобразователь уровней, выполненный на шести МОП-транзисторах, дополнительно введены седьмой и восьмой МОП-транзисторы первого типа. Преобразователь уровня (выпол- . ненный по первому варианту) содержит МОП-транзисторы 1-8, из которых 1, 4 образуют первую комплементарную пару, а 2, 5 и 3, 6 вторую и третью пары, шины 9, 10 и 11 питания, входную шину 12, выходные шины 13 и 14. Схема преобразователя уровня по второму варианту приводится в описании изобретения. 2 с,п. ф-лы, 2 ил о с s (Л // п р1 п щ /J Staofii tc ел О5 О СП iLJh 74 . фиг.1

| Мкртчян С | |||

| О | |||

| Преобразователи уровней логических элементов | |||

| - М.: Радио и связь, 1982, с„ 35, рис, 25. |

Авторы

Даты

1986-09-07—Публикация

1985-03-20—Подача