Изобретение относится к импульсной техникe, в частности к устройствам цифровой вычислительной техники, и может быть использовано при разработке быстродействующих микропроцессоров с малым потреблением мощности.

Уменьшение размеров транзисторов и улучшение их параметров позволяет создавать все более быстрые и производительные микропроцессоры, однако время и мощность, затрачиваемые на перезаряд линий связи внутри кристалла становятся основным фактором, сдерживающим рост их производительности.

Импеданс линий связи - более консервативный параметр, чем характеристики транзисторов, поэтому поиск новых схемотехнических решений направлен на уменьшение потерь в линиях связи. Одним из разрабатываемых ныне логических стилей является Small-Swing Differential Logic (SSDL) [M. Matsui et al. "200 MHz Video Compression Macrocell Using Low-Swing Differential Logic" in ISSCC Dig. Tech. Papers p. 76-77, Feb. 1994], в котором логические функции реализуются с помощью проходных N-канальных транзисторов (pass-transistors), включенных в парафазные линии с последующим защелкиванием результата на триггерном усилителе (sense amplifier), стробируемом синхросигналом CLK. Информация передается дифференциальным сигналом 100-200 mV, предзаряжаемым к уровню "земли". За счет этого достигается значительная экономия мощности и площади, занимаемой на кристалле, и как следствие увеличение быстродействия.

Однако этот логический стиль не нашел пока широкого применения главным образом из-за отсутствия быстрого, надежного и малопотребляющего триггерного усилителя, предназначенного для работы с малыми сигналами, предзаряд которых осуществляется к уровню "земли".

Известен базовый усилительный элемент дифференциальной динамической логики, содержащий триггер на двух инверторах, выполненных на КМОП транзисторах, с перекрестными связями, подключенных одноименными выводами пары транзисторов одного типа проводимости к первой шине источника питания, одноименными выводами пары транзисторов другого типа проводимости, соединенных с соответствующими первым и вторым входами узла активизации триггера, выход которого подключен ко второй шине источника питания, узел восстановления исходного состояния триггера на двух транзисторах, выводы сток-исток которых объединены с одноименными выводами соответствующих транзисторов того же типа проводимости инверторов триггера, подключенных к первой шине источника питания, парафазные информационные шины, подключенные к одноименным входам узла активизации триггера, шину синхронизации, подключенную к управляющим входам узлов активизации триггера и восстановления исходного состояния триггера, выходы инверторов триггера являются парафазными выходами устройства [M. Matsui and J.В.Burr "A Low-Voltage 32•32-Bit Multiplier in Dynamic Differential Logic" 1995 IEEE Symposium on Low Power Electronics, v. 1].

Недостатками известного устройства являются малая скорость нарастания выходного сигнала, так как цепь заряда каждого из выходов триггера выполнена на трех последовательно соединенных Р-канальных МОП транзисторах, которые имеют худшие характеристики, чем N-канальные МОП транзисторы.

Кроме того, относительно высока потребляемая мощность, обусловленная необходимостью использования относительно мощных Р-канальных МОП транзисторов.

По технической сущности наиболее близким к предлагаемому изобретению является базовый усилительный элемент дифференциальной динамической логики - триггерный усилитель, содержащий триггер на двух инверторах, выполненных на КМОП транзисторах, с перекрестными связями, подключенных одноименными выводами пары транзисторов одного типа проводимости к первой шине источника питания, одноименными выводами пары транзисторов другого типа проводимости соединенных с соответствующими первым и вторым входами узла активизации триггера, выход которого подключен ко второй шине источника питания, узел восстановления исходного состояния триггера на двух транзисторах, выводы сток-исток которых объединены с одноименными выводами соответствующих транзисторов того же типа проводимости инверторов триггера, подключенных к первой шине источника питания, парафазные информационные шины, подключенные к одноименным входам узла активизации триггера, шину синхронизации, подключенную к управляющим входам узла восстановления исходного состояния триггера, выходы инверторов триггера являются парафазными выходами устройства (пат. США N 4843264, кл. G 01 R 19/00 от 1989 г.).

Однако и у этого известного устройства скорость нарастания выходного сигнала невысока, так как цепь заряда каждого из выходов триггера содержит три последовательно соединенных МОП транзисторa.

Техническим результатом является увеличение быстродействия и снижение потребляемой мощности.

Достигается это тем, что базовый усилительный элемент дифференциальной динамической логики, содержащий триггер на двух инверторах, выполненных на КМОП транзисторах, с перекрестными связями, подключенных одноименными выводами пары транзисторов одного типа проводимости к первой шине источника питания, одноименными выводами пары транзисторов другого типа проводимости, соединенных с соответствующими первым и вторым входами узла активизации триггера, выход которого подключен ко второй шине источника питания, узел восстановления исходного состояния триггера на двух транзисторах, выводы сток-исток которых объединены с одноименными выводами соответствующих транзисторов того же типа проводимости инверторов триггера, подключенных к первой шине источника питания, парафазные информационные шины, подключенные к одноименным входам узла активизации триггера, шину синхронизации, подключенную к управляющим входам узлов активизации триггера и восстановления исходного состояния триггера, выходы инверторов триггера являются парафазными выходами устройства, согласно изобретению введен дополнительный N-канальный МОП транзистор, а узел активизации триггера выполнен на двух парах последовательно соединенных N-канальных МОП транзисторов, образующих первую и вторую разрядные цепи, входные выводы которых являются соответствующими входами узла активизации триггера, а их выходы подключены к выходу узла активизации триггера, выводы сток-исток дополнительного N-канального МОП транзистора подключены к входам узла активизации триггера, а его затвор подключен к первой шине источника питания, общие выводы последовательно соединенных транзисторов узла активизации триггера подключены к соответствующим парафазным информационным шинам, а затворы N-канальных МОП транзисторов разрядных цепей соединены с управляющим входом узла активизации триггера.

Кроме того, во втором варианте изобретения базовый усилительный элемент дифференциальной динамической логики, содержащий триггер на двух инверторах, выполненных на КМОП транзисторах с перекрестными связями, подключенных одноименными выводами пары транзисторов одного типа проводимости к первой шине источника питания, одноименными выводами пары транзисторов другого типа проводимости соединенных с соответствующими первым и вторым входами узла активизации триггера, выход которого подключен ко второй шине источника питания, узел восстановления исходного состояния триггера на двух транзисторах, выводы сток-исток которых объединены с одноименными выводами соответствующих транзисторов того же типа проводимости инверторов триггера, подключенных к первой шине источника питания, парафазные информационные шины, подключенные к одноименным входам узла активизации триггера, шину синхронизации, подключенную к управляющим входам узла восстановления исходного состояния триггера, выходы инверторов триггера являются парафазными выходами устройства, согласно изобретению введены дополнительный N-канальный МОП транзистор и N дополнительных шин логической синхронизации, а узел активизации триггера выполнен на 2N (где N - целое число) парах последовательно соединенных N-канальных МОП транзисторов, образующих 2N-1 и 2N разрядные цепи, входные выводы которых являются соответствующими первым и вторым входами узла активизации триггера, а их выходы подключены к выходу узла активизации триггера, выводы сток-исток дополнительного N-канального МОП транзистора подключены к входам узла активизации триггера, а его затвор подключен к первой шине источника питания, общие выводы последовательно соединенных транзисторов узла активизации триггера подключены к соответствующим 2N парафазным информационным шинам, а затворы N-канальных МОП транзисторов 2N-1 и 2N разрядных цепей подключены к N-й шине логической синхронизации.

Сущность изобретения заключается в том, что введение дополнительного N-канального МОП транзистора и соответствующее выполнение узла активизации триггера позволило увеличить проводимость разрядных цепей без увеличения мощности транзисторов.

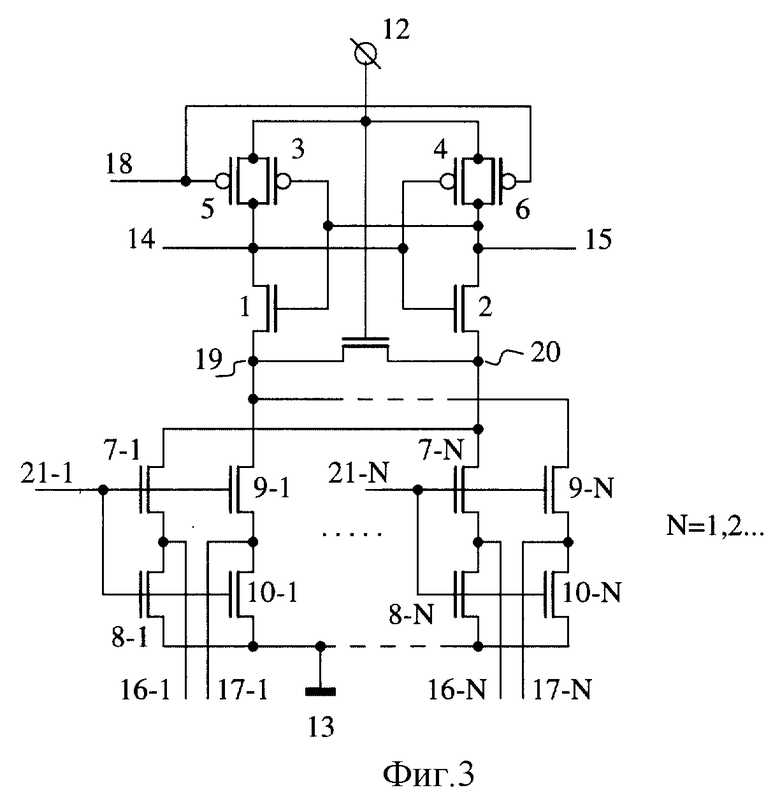

На фиг.1 представлена принципиальная электрическая схема одного варианта предлагаемого устройства; на фиг.2 - временные диаграммы его работы; на фиг. 3 - принципиальная электрическая схема второго варианта предлагаемого устройства; на фиг.4 - временные диаграммы его работы.

Базовый усилительный элемент дифференциальной динамической логики (фиг 1) содержит триггер на двух инверторах, выполненных на КМОП транзисторах 1, 2 и 3, 4 (соответственно N-канальных и Р-канальных), узел восстановления исходного состояния триггера на двух Р-канальных МОП транзисторах 5 и 6, узел активизации триггера, выполненный на двух парах последовательно соединенных N-канальных МОП транзисторов 7, 8 и 9, 10 соответственно, дополнительный N-канальный МОП транзистор 11, первую и вторую шины 12 и 13 питания соответственно.

Выходы инверторов триггера являются парафазными выходами 14 и 15 устройства.

Общие выводы последовательно соединенных N-канальных МОП транзисторов 7, 8 и 9, 10 узла активизации триггера подключены к соответствующим парафазным информационным шинам 16 и 17, а затворы N-канальных МОП транзисторов разрядных цепей соединены с управляющим входом узла активизации триггера, подключенного к шине 18 синхронизации.

Выводы сток-исток дополнительного N-канального МОП транзистора 11 подключены к входам 19, 20 узла активизации триггера.

Второй вариант базового усилительного элемента дифференциальной динамической логики (фиг. 3) содержит МОП транзисторы 1 - 6, 7-1...7-N - 10-1... 10-N и 11, две шины 12 и 13 питания, парафазные выходы 14 и 15, парафазные информационные шины 16-1...16-N и 17-1...17-N, шину 18 синхронизации, подключенную к управляющим входам узла восстановления исходного состояния триггера.

Кроме того, устройство содержит N дополнительных шин 21-1...21-N логической синхронизации, а узел активизации триггера выполнен на 2N (где N - целое число) парах последовательно соединенных транзисторов 7-1...7-N, 8-1.. . 8-N и 9-1. . .9-N, 10-1...10-N, образующих 2N-1-ю и 2N-ю разрядные цепи, входные выводы которых являются соответствующими первым и вторым входами узла активизации триггера, а их выходы подключены к выходу узла активизации триггера, то есть кo второй шине 13 источника питания.

Выводы сток-исток дополнительного N-канального МОП транзистора 11 подключены к входам 19, 20, узла активизации триггера, а его затвор подключен к первой шине 12 источника питания. Общие выводы последовательно соединенных транзисторов 7-1...7-N, 8-1...8-N и 9-1...9-N, 10-1...10-N подключены к соответствующим 2N парафазным информационным шинам 16-1...16-N и 17- 1...17-N, а затворы N-канальных МОП транзисторов 2N-1 и 2N (где N - целое число) разрядных цепей подключены к N-й шине 21-N логической синхронизации.

Работа устройства.

В исходном состоянии при наличии положительного напряжения на шине 12 относительно потенциала земли на шине 13 и при присутствии на шине 18 синхронизации и информационных шинах 16, 17 потенциала земли (логический "0"), на парафазных выходах 14, 15 устанавливается положительный потенциал - логическая "1", а на входах 19, 20 узла активизации устанавливаются потенциалы Udd - Utn, где Udd - напряжение питания, a Utn - пороговое напряжение N-канального МОП транзистора.

При подаче парафазного сигнала на шины 16 и 17 согласно временной диаграмме (фиг. 2) до прихода положительного фронта стробирующего сигнала на шину 18 синхронизации потенциалы на выходах 14, 15 триггера не изменяются. При поступлении положительного фронта стробирующего сигнала на шину 18 синхронизации транзисторы 7, 9 узла активизации открываются, что вызывает быстрое уменьшение потенциалов на входах 19, 20 узла активизации триггера.

Вследствие конечной длительности положительного фронта стробирующего сигнала на шине 18 синхронизации потенциал на входе 20, подключенного через транзистор 9 к информационной шине 17, начинает уменьшаться позже, чем потенциал на входе 19 на время tф•Uin/Udd, где tф - длительность положительного фронта стробирующего сигнала, a Uin - разность потенциалов на информационных шинах 16 и 17.

Одновременно начинается уменьшение потенциалов на выходах 14, 15 триггера с такой же разницей во времени.

За счет положительной обратной связи триггер устанавливается в одно из устойчивых состояний.

Одновременно с этим происходит "притягивание" шин 16 и 17 к потенциалу земли через транзисторы 8 и 10 соответственно.

При окончании стробирующего сигнала на шине 18 синхронизации Р-канальные МОП транзисторы 5, 6 узла восстановления триггера открываются и подключают выходы 14, 15 триггера к шине 12 питания, восстанавливая его в исходное состояние.

N-канальный транзистор 11 способствует ускорению переходных процессов в момент включения и выключения триггера, выравнивая потенциалы на входах 19, 20 узла активизации.

Аналогично работает и второй вариант устройства (фиг. 3).

Особенностью его работы является наличие сигналов логической синхронизации на дополнительных шинах 21-1...21-N.

Одновременно с появлением сигнала на шине 18 синхронизации появляется только один положительный сигнал логической синхронизации на одной из шин 21-1...21-N в соответствии с временной диаграммой (фиг. 4).

Второй вариант устройства имеет расширенные функциональные возможности, в частности может быть использован в качестве N-входного мультиплексора.

Таким образом, в предлагаемых вариантах заявляемого устройства по сравнению с аналогами применен иной принцип передачи входного дифференциального сигнала на выходы триггера, при котором в разрядных цепях используются два последовательно соединенных N-канальных МОП транзистора, что позволяет повысить скорость переключения устройства, увеличить его нагрузочную способность и устойчивость к разбросу параметров.

Для оценки характеристик предлагаемого устройства проведено его сравнение с характеристиками прототипа. При Spice-моделировании использовались модели транзисторов, соответствующих технологии 0,35 мкм.

Основными характеристиками аналогичных устройств являются:

- задержка выходного сигнала от стробирующего сигнала в зависимости от размаха парафазного входного сигнала и от емкостной нагрузки на выходы усилительного элемента,

- чувствительность Vin min (минимальная величина парафазного входного сигнала, не вызывающая сбой работы усилителя при введении максимально возможных разбросов технологических параметров транзисторов триггера),

- потребляемая мощность,

- занимаемая площадь (суммарная ширина каналов транзисторов).

Результаты сравнения приведены в таблице.

Предлагаемое устройство имеет более высокую нагрузочную способность и быстродействие по сравнению с известными, а также меньшие размеры и более низкое потребление мощности. Это обусловлено оптимальной совокупностью существенных признаков, изложенных в формуле изобретения.

Устройство имеет значительный запас по быстродействию, что позволяет без особого ущерба уменьшать его размеры (при сохранении нагрузки на выходы), а значит, уменьшать потребляемую мощность. Так, при уменьшении размеров всех транзисторов вдвое задержка td увеличивается всего на 0,01 ns при той же нагрузке на выходы.

| название | год | авторы | номер документа |

|---|---|---|---|

| КАСКАДНЫЙ ИНТЕГРАЛЬНЫЙ МОДУЛЬ ДИНАМИЧЕСКОЙ ПАМЯТИ "СИБЛ" | 2001 |

|

RU2218611C2 |

| УСТРОЙСТВО КОРРЕКЦИИ СКВАЖНОСТИ ВХОДНОГО СИГНАЛА | 2011 |

|

RU2467473C1 |

| УСТРОЙСТВО ЭЛЕКТРОННОГО ГИСТЕРЕЗИСА | 2012 |

|

RU2486668C1 |

| ЛОГИЧЕСКИЙ ВЕНТИЛЬ | 2014 |

|

RU2546302C1 |

| ИНТЕГРАЛЬНЫЙ N-РАЗРЯДНЫЙ ЦИФРОАНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ (ЦАП) (ВАРИАНТЫ) | 1995 |

|

RU2113055C1 |

| КОМПАРАТОР ДВОИЧНЫХ ЧИСЕЛ | 2021 |

|

RU2762061C1 |

| ДИНАМИЧЕСКИЙ D-ТРИГГЕР | 2018 |

|

RU2679220C1 |

| СТАТИЧЕСКАЯ ЗАПОМИНАЮЩАЯ ЯЧЕЙКА С ДВУМЯ АДРЕСНЫМИ ВХОДАМИ | 2011 |

|

RU2470390C1 |

| РАДИАЦИОННО-СТОЙКАЯ ЭНЕРГОНЕЗАВИСИМАЯ ПРОГРАММИРУЕМАЯ ЛОГИЧЕСКАЯ ИНТЕГРАЛЬНАЯ СХЕМА | 2014 |

|

RU2563548C2 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2017 |

|

RU2653301C1 |

Изобретение относится к устройствам цифровой вычислительной техники. В базовый усилительный элемент дифференциальной динамической логики, содержащий триггер на двух инверторах, выполненный на КМОП транзисторах с перекрестными связями, с узлом активизации триггера и восстановления его исходного состояния, введен дополнительный N-канальный МОП транзистор, а узел активизации триггера выполнен на двух парах последовательно соединенных N-канальных МОП транзисторов, образующих две разрядные цепи. Технический результат: повышение быстродействия и снижение потребляемой мощности. 2 з.п. ф-лы, 1 табл., 4 ил.

| US 4843264 A, 07.06.1989 | |||

| КАСКАДНОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО НА КМДП ТРАНЗИСТОРАХ | 1998 |

|

RU2132591C1 |

| СПОСОБ ПОЛУЧЕНИЯ СРЕДНИХ ДИСТИЛЛАТОВ И БАЗОВЫХ МАСЕЛ | 1994 |

|

RU2135549C1 |

| US 5886541 A, 23.03.1999 | |||

| US 5903169 A, 11.05.1999 | |||

| US 5859548 A, 12.01.1999. | |||

Авторы

Даты

2000-08-10—Публикация

1999-11-17—Подача