Изобретение относится к полупроводниковой промышленности, в частности к интегральным микросхемам, и может быть использовано для защиты выходов высокочастотных КМОП микросхем от электростатических разрядов.

Тенденции развития полупроводниковой промышленности непосредственно связаны с уменьшением минимальных топологических размеров интегральных микросхем, что приводит к повышению чувствительности устройств к воздействию электростатических разрядов. Для субмикронных технологий особенно важно обеспечить равномерное распределение стрессового тока в момент разряда, своевременное включение защитного элемента и быстрый отвод тока с наименьшим рассеиванием тепла. Один из путей защиты состоит в использовании устройств защиты для входных и выходных выводов (а также шин питания) интегральной микросхемы. Устройство защиты должно иметь минимальные паразитное сопротивление и емкость, чтобы минимизировать падение напряжения на этом элементе и уменьшить дополнительную нагрузочную емкость защищаемого устройства.

Известно устройство защиты выводов КМОП микросхем, содержащее два ключевых транзистора, два управляющих усилителя, шину питания, шину «земли», входную или выходную шину. При электростатическом разряде ток протекает через один ключевой транзистор /1/.

Основным недостатком этого решения по отношению к заявленному изобретению является то, что при электростатическом разряде открывается только один из ключевых транзисторов, что приводит к необходимости увеличивать размеры ключевых транзисторов, ведет к увеличению паразитной емкости выводов и снижает быстродействие микросхемы.

Наиболее близким по техническому решению является устройство защиты выводов микросхем, содержащее два ключевых МОП транзистора, два нагрузочных резистора и два управляющих транзистора /2/. При электростатическом разряде ток протекает через один управляющий и два ключевых транзистора. Недостатком технического решения является то, что при защите выходных каскадов ток электростатического разряда протекает только через элемент защиты, а мощные выходные транзисторы формирователя фактически не участвуют в процессе защиты микросхемы и совместно с ключевыми транзисторами элемента защиты определяют площадь формирователя на кристалле микросхемы.

Задачей предлагаемого изобретения является уменьшение суммарной площади, занятой на кристалле микросхемы мощными транзисторами, а также уменьшение паразитной емкости этих транзисторов.

Поставленная задача достигается тем, что выходной каскад формирователя построен на основе комплементарной пары мощных МОП транзисторов, подключенных истоками к шинам питания и «земли», а стоками к выходной шине. Затворы выходных транзисторов соединены с выходами логических элементов 3ИЛИ/НЕ, 3И/НЕ. Устройство защиты от электростатических разрядов содержит два ключевых транзистора, два управляющих транзистора и два нагрузочных резистора. Истоки ключевых транзисторов соединены с выходной шиной, а стоки - с шиной питания (для РМОП) и шиной «земли» (для NМОП). Затвор ключевого РМОП транзистора и сток управляющего NМОП транзистора соединены и подключены к шине питания через первый нагрузочный резистор. Затвор ключевого NМОП транзистора и сток управляющего РМОП транзистора подключены к шине «земли» через второй нагрузочный резистор. Затвор управляющего NМОП транзистора соединен с шиной «земли», а его исток - с выходной шиной. Затвор и исток РМОП управляющего транзистора соединены с шиной питания и выходной шиной соответственно. Первый вход логического элемента 3ИЛИ/НЕ соединен с затвором NМОП ключевого транзистора. Второй вход соединен с выходом логического инвертора, вход которого подключен к затвору РМОП ключевого транзистора. Третий вход подключен к логическому входу формирователя. Первый вход логического элемента 3И/НЕ соединен с затвором РМОП ключевого транзистора, второй вход - с выходом второго логического инвертора, вход которого подключен к затвору NМОП ключевого транзистора. Третий вход подключен к логическому входу формирователя.

Управляющие сигналы подаются на затворы выходных МОП транзисторов через логические элементы 3ИЛИ/НЕ и 3И/НЕ. В нормальном режиме работы выходное напряжение формирователя ограничено напряжением в шинах питания. Все транзисторы в элементе защиты закрыты, а на первые входы логических элементов подаются напряжения с управляющих каскадов элемента защиты, соответствующие напряжениям питания. В этом режиме элементы 3ИЛИ/НЕ, 3И/НЕ выполняют функцию инвертора входного управляющего сигнала (D). Напряжения на выходах обоих логических элементов одинаково и равно напряжению питания или «земли».

В режиме электростатического разряда напряжение на выходной шине выходит за пределы диапазона между шинами питания. При этом открываются один из управляющих транзисторов элемента защиты, оба ключевых транзистора элемента защиты и оба выходных транзистора. Уменьшение сопротивления в цепи электростатического разряда соответствует увеличению суммарной ширины МОП транзисторов, открытых в режиме электростатического разряда.

Новизна предложенного технического решения заключается в том, что устройство защиты выхода формирователя импульсных сигналов не только переключает ток электростатического разряда в шины питания с использованием ключевых транзисторов, но и управляет выходными транзисторами формирователя, уменьшая сопротивление в цепи разряда.

По данным научно-технической и патентной литературы авторам неизвестна заявляемая совокупность признаков, направленная на достижение поставленной задачи, и это решение не вытекает с очевидностью из известного уровня техники, что позволяет сделать вывод о соответствии решения уровню изобретения.

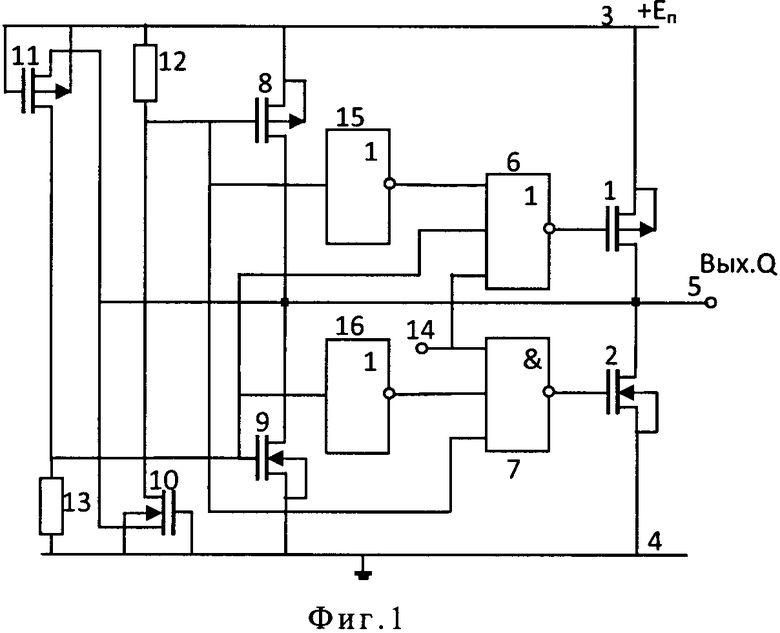

Сущность изобретения поясняется чертежом, где на фиг.1 приведена электрическая схема формирователя импульсных сигналов с устройством защиты от электростатических разрядов, где:

1) первый выходной транзистор (РМОП);

2) второй выходной транзистор (NМОП);

3) шина питания;

4) шина «земли»;

5) выходная шина;

6) логический элемент 3ИЛИ/НЕ;

7) логический элемент 3И/НЕ;

8) первый ключевой транзистор в устройстве защиты (РМОП);

9) второй ключевой транзистор в устройстве защиты (NМОП);

10) первый управляющий транзистор в устройстве защиты (NМОП);

11) второй управляющий транзистор в устройстве защиты (РМОП);

12) первый нагрузочный резистор;

13) второй нагрузочный резистор;

14) логический вход формирователя;

15) первый логический инвертор;

16) второй логический инвертор.

Выходной формирователь импульсных сигналов содержит устройство защиты от электростатических разрядов схемотехнически идентичное прототипу. Отличие состоит в том, что сигналы (x1 и x2), поступающие на затворы ключевых МОП транзисторов (8, 9) в устройстве защиты, передаются и на входы логических элементов в выходном каскаде. Логика управления выходными транзисторами отражена в таблице.

Устройство защиты работает следующим образом. Электростатический разряд (ЭСР) возникает между контактной площадкой выходного сигнала (5) и контактной площадкой одной из шин (3, 4). Есть вероятность возникновения ЭСР между площадками входных и выходных сигналов. ЭСР может иметь как положительную, так и отрицательную полярность относительно шин питания. Функция устройства защиты состоит в ограничении напряжения на затворах МОП транзисторов путем переключения разрядного тока из выходной цепи в шины питания. При вытекающем разрядном токе на выходе формируется отрицательный потенциал. При этом открываются первый управляющий транзистор (10), первый и второй ключевые транзисторы (8, 9). На входах инверторов (15, 16) формируется низкий логический уровень, что приводит к открытию обоих выходных транзисторов (1, 2). При вытекающем разрядном токе на выходе (5) формируется положительный потенциал. При этом открывается второй управляющий транзистор (11), первый и второй ключевые транзисторы (8, 9). На входах инверторов (15, 16) формируется высокий логический уровень, что также приводит к открытию выходных транзисторов в соответствии с логикой, отраженной в таблице.

X1 - логический уровень на затворе первого ключевого транзистора;

Х2 - логический уровень на затворе второго ключевого транзистора;

У1 - логический уровень на затворе первого выходного транзистора;

У2 - логический уровень на затворе второго выходного транзистора;

КЗ - короткое замыкание между шинами питания;

1 - высокий уровень напряжения;

0 - низкий уровень напряжения;

X - любой логический уровень;

КЗ - короткое замыкание шин питания.

В модели электростатического разряда через тело человека эквивалентная емкость источника тока - 100 пФ, а эквивалентное сопротивление 1500 Ом. Разряд с напряжением 2000В создает максимальный ток 1.33 А. При этом напряжение на выводе микросхемы не должно превышать напряжение питания более чем в 1.5 раза. Для типового напряжения питания 3.3В максимально допустимое напряжение составит 5В. Максимальное сопротивление элементов защиты для входного тока 1.33 А не должно превышать 3.7 Ом. Группы открытых РМОП и NМОП транзисторов должны иметь сопротивление не более 7.4 Ом каждая. Сопротивление открытого NМОП транзистора около 5 Ом/мм. Следовательно, суммарная ширина открытых NМОП транзисторов не менее 660 мкм. Удельное сопротивление РМОП транзисторов примерно вдвое больше и их суммарная ширина - 1330 мкм.

При нагрузочной способности выходного формирователя 30 мА и допустимом остаточном напряжении выходных транзисторов не более 0.3 В необходимо сопротивление открытых выходных транзисторов не более 10 Ом. Это соответствует ширине выходных транзисторов: 500 мкм (NМОП) и 1000 мкм (РМОП). При этих ограничениях минимальная ширина ключевых транзисторов в устройстве защиты составит только 160 мкм для NМОП и 330 мкм для РМОП, а суммарная ширина мощных транзисторов в формирователе будет около 2 мм. Если выходные транзисторы не использовать для защиты от электростатических разрядов, то суммарная ширина транзисторов возрастет на 1.5 мм, то есть на 75%. Соответственно увеличатся площадь и паразитная емкость мощных транзисторов.

Источники информации

1. Патент США № US 5910847, 1999 г.

2. Патент РФ №2308146, 2007 г.

Изобретение относится к области формирования выходных сигналов высокочастотных КМОП микросхем и защиты выходов от электростатических разрядов. Техническим результатом является повышение быстродействия формирователя импульсов. Формирователь содержит выходной каскад на основе комплементарных выходных транзисторов и логических элементов 3ИЛИ/НЕ, 3И/НЕ. Устройство защиты содержит два комплементарных ключевых транзистора, два комплементарных управляющих транзистора и два нагрузочных резистора. В рабочем режиме ключевые транзисторы закрыты, а выходные транзисторы включаются поочередно в соответствии с уровнем входного сигнала. В режиме возникновения электростатического разряда оба ключевых транзистора и оба выходных транзистора открыты. Это позволяет уменьшить размеры ключевых транзисторов и паразитную электрическую емкость выходной шины. 1 ил.

Выходной формирователь импульсных сигналов с устройством защиты от электростатических разрядов для КМОП микросхем, содержащий выходной каскад на основе комплементарной пары МОП транзисторов, подключенных истоками к шинам питания и «земли», а стоками - к выходной шине, а также логические элементы 3ИЛИ/НЕ, 3И/НЕ, выходы которых соединены с затворами РМОП и NМОП выходных транзисторов соответственно, а также устройство защиты от электростатических разрядов, содержащее два ключевых транзистора, два управляющих транзистора и два нагрузочных резистора; стоки первого и второго ключевых транзисторов соединены с выходной шиной, а истоки - с шинами питания и «земли» соответственно; затвор первого ключевого транзистора и сток первого управляющего транзистора подключены к шине питания через первый нагрузочный резистор, а затвор второго ключевого транзистора и сток второго управляющего транзистора подключены к шине «земли» через второй нагрузочный резистор, при этом затвор первого управляющего транзистора соединен с шиной «земли», а его исток - с выходной шиной; затвор второго управляющего транзистора соединен с шиной питания, а исток - с выходной шиной, отличающийся тем, что первый вход логического элемента 3ИЛИ/НЕ соединен с затвором второго ключевого транзистора, второй вход соединен с выходом первого логического инвертора, вход которого подключен к затвору первого ключевого транзистора, а третий вход подключен к управляющему логическому входу формирователя, также первый вход логического элемента 3И/НЕ соединен с затвором первого ключевого транзистора, второй вход соединен с выходом второго логического инвертора, вход которого подключен к затвору второго ключевого транзистора, а третий вход - к управляющему логическому входу формирователя импульсных сигналов.

| УСТРОЙСТВО ЗАЩИТЫ ВЫВОДОВ ИНТЕГРАЛЬНЫХ СХЕМ СО СТРУКТУРОЙ МДП ОТ ЭЛЕКТРОСТАТИЧЕСКИХ РАЗРЯДОВ | 2005 |

|

RU2308146C2 |

| ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ НАПРЯЖЕНИЯ С УСТРОЙСТВОМ ЗАЩИТЫ ОТ ОТРИЦАТЕЛЬНЫХ ВЫБРОСОВ ПРИ ПОДКЛЮЧЕНИИ ИНДУКТИВНОЙ НАГРУЗКИ | 2011 |

|

RU2483437C1 |

| Формирователь импульсов | 1974 |

|

SU509994A1 |

| Формирователь импульсов | 1975 |

|

SU675600A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Способ приготовления лака | 1924 |

|

SU2011A1 |

| Приспособление для суммирования отрезков прямых линий | 1923 |

|

SU2010A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

2015-02-10—Публикация

2013-11-26—Подача