Предлагаемое изобретение относится к цифровой вычислительной технике и может быть использовано при построении адресных регистров запоминающих устройств и входных регистров микропроцессорных систем.

Известно электронное устройство - Элемент входного регистра [1]. Указанное устройство предназначено для преобразования по команде управляющего сигнала ВК  входного сигнала D в выходные дополняющие сигналы F1 и F2, необходимые для работы дешифраторов тактируемых запоминающих устройств. Кроме того, Элемент входного регистра и может быть использован в качестве разряда входных регистров микропроцессорных систем для управления многоразрядными шинами данных

входного сигнала D в выходные дополняющие сигналы F1 и F2, необходимые для работы дешифраторов тактируемых запоминающих устройств. Кроме того, Элемент входного регистра и может быть использован в качестве разряда входных регистров микропроцессорных систем для управления многоразрядными шинами данных

Данный Элемент входного регистра содержит входы D, ВК и  выходы F1 и F2 шину источника питания высокого уровня напряжения Uип, шину источника питания низкого уровня напряжения «земля», МОП транзисторы Р-типа с первого по пятый и N-типа с шестого по десятый и четыре инвертора [1].

выходы F1 и F2 шину источника питания высокого уровня напряжения Uип, шину источника питания низкого уровня напряжения «земля», МОП транзисторы Р-типа с первого по пятый и N-типа с шестого по десятый и четыре инвертора [1].

Недостатком известного устройства Элемента входного регистра [1] является низкое быстродействие, вызванное большим количеством элементов подсоединенных к входам выходных инверторов первому и второму, в результате чего, узловые емкости, подсоединенные к входам этих инверторов, имеют большое значение и увеличивают время переходного процесса перезаряда этих узлов.

Наличие четвертого инвертора требует физического соединения стоков комплементарной пары МОП транзисторов этого инвертора с истоками ключевых транзисторов, что увеличивает емкость данного узла и снижает быстродействие Элемента входного регистра. Кроме того, входные сигналы ВК и  подсоединены каждый к затворам трех МОП транзисторов, суммарная величина емкости которых снижает нагрузочную способность входных сигналов и замедляет переходный процесс источников входных сигналов, что в свою очередь дополнительно снижает быстродействие схемы.

подсоединены каждый к затворам трех МОП транзисторов, суммарная величина емкости которых снижает нагрузочную способность входных сигналов и замедляет переходный процесс источников входных сигналов, что в свою очередь дополнительно снижает быстродействие схемы.

Задачей предлагаемого изобретения является повышение быстродействия Элемента входного регистра.

Поставленная задача достигается тем, что в схему Элемента входного регистра [1], содержащую МОП транзисторы Р-типа с первого по пятый и N-типа с шестого по десятый, вход сигнала D, вход сигнала СЕ, соединенный с затворами транзисторов пятого и восьмого, вход сигнала  соединенный с затворами третьего и десятого транзисторов, шину источника питания высокого уровня напряжения VDD, соединенную с истоками транзисторов второго, третьего и четвертого, шину источника питания низкого уровня напряжения GND, соединенную с истоками транзисторов седьмого, восьмого и девятого, первый инвертор, вход которого соединен со стоками транзисторов пятого, восьмого и девятого и затвором седьмого транзистора, а выход является выходом OUT, второй инвертор, вход которого соединен со стоками транзисторов третьего, четвертого и десятого и затвором второго транзистора, а выход соединен с входом третьего инвертора, выход которого является выходом

соединенный с затворами третьего и десятого транзисторов, шину источника питания высокого уровня напряжения VDD, соединенную с истоками транзисторов второго, третьего и четвертого, шину источника питания низкого уровня напряжения GND, соединенную с истоками транзисторов седьмого, восьмого и девятого, первый инвертор, вход которого соединен со стоками транзисторов пятого, восьмого и девятого и затвором седьмого транзистора, а выход является выходом OUT, второй инвертор, вход которого соединен со стоками транзисторов третьего, четвертого и десятого и затвором второго транзистора, а выход соединен с входом третьего инвертора, выход которого является выходом  причем стоки транзисторов первого, второго, шестого и седьмого соединены с затворами транзисторов четвертого и девятого, введены одиннадцатый МОП транзистор Р-типа и двенадцатый МОП транзистор N-типа, затворы которых соединены с затворами транзисторов четвертого и девятого, и сток одиннадцатого транзистора соединен с истоком пятого, сток двенадцатого - с истоком десятого, а исток одиннадцатого транзистора - с шиной источника питания высокого уровня напряжения VDD, а двенадцатого - с шиной источника питания низкого уровня напряжения GND, и исток первого транзистора соединен с затвором второго, исток шестого транзистора - с затвором седьмого, а затворы транзисторов первого и шестого с входом D.

причем стоки транзисторов первого, второго, шестого и седьмого соединены с затворами транзисторов четвертого и девятого, введены одиннадцатый МОП транзистор Р-типа и двенадцатый МОП транзистор N-типа, затворы которых соединены с затворами транзисторов четвертого и девятого, и сток одиннадцатого транзистора соединен с истоком пятого, сток двенадцатого - с истоком десятого, а исток одиннадцатого транзистора - с шиной источника питания высокого уровня напряжения VDD, а двенадцатого - с шиной источника питания низкого уровня напряжения GND, и исток первого транзистора соединен с затвором второго, исток шестого транзистора - с затвором седьмого, а затворы транзисторов первого и шестого с входом D.

В предлагаемом Элементе входного регистра, вместо четвертого инвертора введены два МОП транзистора, что уменьшает суммарные узловые емкости, подсоединенные к входам выходных инверторов, и емкости узлов стоков, введенных МОП транзисторов, подсоединенных к соответствующим истокам ключевых МОП транзисторов. Поэтому за счет уменьшения времени переходного процесса во время переключения напряжений узлов схемы быстродействие Элемента входного регистра повышается.

Кроме того, в отличие от известного Элемента входного регистра, входные сигналы ВК и  подсоединены каждый к затворам только двух МОП транзисторов (а не трех, как в известном устройстве), что в свою очередь дополнительно повышает быстродействие схемы.

подсоединены каждый к затворам только двух МОП транзисторов (а не трех, как в известном устройстве), что в свою очередь дополнительно повышает быстродействие схемы.

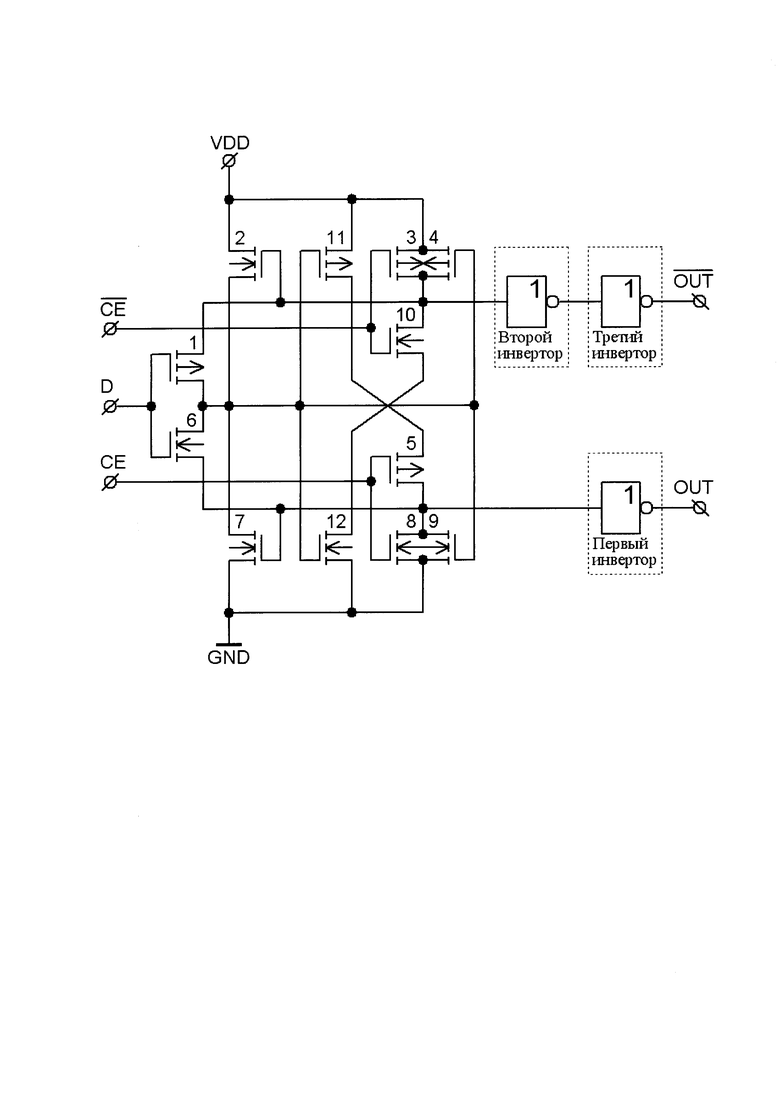

На Рисунке приведена схема предлагаемого Элемента входного регистра.

Предлагаемый Элемент входного регистра содержит транзисторы Р-типа с первого по пятый 1-5 и одиннадцатый 11 и N-типа с шестого по десятый 6-10 и двенадцатый 12, вход сигнала D, соединенный с затворами транзисторов первого 1 и шестого 6, вход сигнала СЕ, соединенный с затворами пятого 5 и восьмого 8 транзисторов, вход сигнала  соединенный с затворами третьего 3 и десятого 10 транзисторов, шину источника питания высокого уровня напряжения VDD, соединенную с истоками транзисторов второго 2, третьего 3, четвертого 4 и одиннадцатого 11, шину источника питания низкого уровня напряжения GND, соединенную с истоками транзисторов седьмого 7, восьмого 8 девятого 9 и двенадцатого 12, первый инвертор, вход которого соединен со стоками пятого 5, восьмого 8 и девятого 9 транзисторов, истоком шестого 6 и затвором седьмого 7 транзисторов, а выход является выходом OUT Элемента входного регистра, второй инвертор, вход которого соединен со стоками третьего 3, четвертого 4 и десятого 10 транзисторов, истоком 1 и затвором второго 2 транзисторов, а выход соединен с входом третьего инвертора, выход которого является выходом

соединенный с затворами третьего 3 и десятого 10 транзисторов, шину источника питания высокого уровня напряжения VDD, соединенную с истоками транзисторов второго 2, третьего 3, четвертого 4 и одиннадцатого 11, шину источника питания низкого уровня напряжения GND, соединенную с истоками транзисторов седьмого 7, восьмого 8 девятого 9 и двенадцатого 12, первый инвертор, вход которого соединен со стоками пятого 5, восьмого 8 и девятого 9 транзисторов, истоком шестого 6 и затвором седьмого 7 транзисторов, а выход является выходом OUT Элемента входного регистра, второй инвертор, вход которого соединен со стоками третьего 3, четвертого 4 и десятого 10 транзисторов, истоком 1 и затвором второго 2 транзисторов, а выход соединен с входом третьего инвертора, выход которого является выходом  Элемента входного регистра. Причем стоки первого 1, второго 2, шестого 6 и седьмого 7 транзисторов соединены с затворами транзисторов четвертого 4, девятого 9, одиннадцатого 11 и двенадцатого 12, сток одиннадцатого транзистора 11 соединен с истоком пятого 5, а сток двенадцатого 12 - с истоком десятого 10.

Элемента входного регистра. Причем стоки первого 1, второго 2, шестого 6 и седьмого 7 транзисторов соединены с затворами транзисторов четвертого 4, девятого 9, одиннадцатого 11 и двенадцатого 12, сток одиннадцатого транзистора 11 соединен с истоком пятого 5, а сток двенадцатого 12 - с истоком десятого 10.

Предлагаемая схема Элемента входного регистра предназначена для формирования прямого OUT и инверсного  сигналов по установленному сигналу данных D и по положительному СЕ и отрицательному

сигналов по установленному сигналу данных D и по положительному СЕ и отрицательному  фронту управляющих сигналов и работает следующим образом.

фронту управляющих сигналов и работает следующим образом.

В исходном состоянии на вход СЕ поступает напряжение высокого уровня (VDD) и, следовательно, на вход  - низкого (GND). Поэтому транзисторы третий 3 и восьмой 8 открыты, а пятый 5 и десятый 10 - закрыты. Через открытый транзистор 3 на исток транзистора 1, на сток транзистора 10, на затвор транзистора 2 и на вход второго инвертора поступает напряжение высокого уровня VDD. Одновременно через открытый транзистор 8 на исток транзистора 6, сток транзистора 5, на затвор транзистора 7 и на вход первого инвертора поступает напряжение низкого уровня GND. Если на входе D напряжение высокого уровня VDD, то транзистор 1 закрыт, а транзистор 6 - открыт.Поэтому через открытые транзисторы 8 и 6 напряжение низкого уровня GND передается на стоки транзисторов 2 и 7 и затворы транзисторов 4, 9, 11 и 12, в результате чего транзисторы 4 и 11 открываются, а 9 и 12 - закрываются. Так как на входе первого инвертора напряжение низкого уровня GND, то на его выходе и, следовательно, на выходе OUT напряжение высокого уровня VDD. И, поскольку на входе второго инвертора напряжение высокого уровня VDD, то на его выходе и, следовательно, на входе третьего инвертора - напряжение низкого уровня GND, а на выходе третьего инвертора и на выходе

- низкого (GND). Поэтому транзисторы третий 3 и восьмой 8 открыты, а пятый 5 и десятый 10 - закрыты. Через открытый транзистор 3 на исток транзистора 1, на сток транзистора 10, на затвор транзистора 2 и на вход второго инвертора поступает напряжение высокого уровня VDD. Одновременно через открытый транзистор 8 на исток транзистора 6, сток транзистора 5, на затвор транзистора 7 и на вход первого инвертора поступает напряжение низкого уровня GND. Если на входе D напряжение высокого уровня VDD, то транзистор 1 закрыт, а транзистор 6 - открыт.Поэтому через открытые транзисторы 8 и 6 напряжение низкого уровня GND передается на стоки транзисторов 2 и 7 и затворы транзисторов 4, 9, 11 и 12, в результате чего транзисторы 4 и 11 открываются, а 9 и 12 - закрываются. Так как на входе первого инвертора напряжение низкого уровня GND, то на его выходе и, следовательно, на выходе OUT напряжение высокого уровня VDD. И, поскольку на входе второго инвертора напряжение высокого уровня VDD, то на его выходе и, следовательно, на входе третьего инвертора - напряжение низкого уровня GND, а на выходе третьего инвертора и на выходе  - высокого (VDD). Если на входе D напряжение низкого уровня GND, то транзистор 1 открыт, а транзистор 6 - закрыт. И через открытые транзисторы 3 и 1 на стоки транзисторов 2 и 7 и затворы транзисторов 4, 9, 11 и 12 поступает напряжение высокого уровня VDD. В результате чего транзисторы 4 и 11 закрываются, а 9 и 12 - открываются. Так как на входе первого инвертора напряжение низкого уровня GND, то на его выходе и, следовательно, на выходе OUT напряжение высокого уровня VDD. И, поскольку на входе второго инвертора напряжение высокого уровня VDD, то на его выходе и, следовательно, на входе третьего инвертора - напряжение низкого уровня GND, а на выходе третьего инвертора и на выходе

- высокого (VDD). Если на входе D напряжение низкого уровня GND, то транзистор 1 открыт, а транзистор 6 - закрыт. И через открытые транзисторы 3 и 1 на стоки транзисторов 2 и 7 и затворы транзисторов 4, 9, 11 и 12 поступает напряжение высокого уровня VDD. В результате чего транзисторы 4 и 11 закрываются, а 9 и 12 - открываются. Так как на входе первого инвертора напряжение низкого уровня GND, то на его выходе и, следовательно, на выходе OUT напряжение высокого уровня VDD. И, поскольку на входе второго инвертора напряжение высокого уровня VDD, то на его выходе и, следовательно, на входе третьего инвертора - напряжение низкого уровня GND, а на выходе третьего инвертора и на выходе  - высокого (VDD).

- высокого (VDD).

Если на входе D установлено напряжение высокого уровня VDD, а на вход СЕ поступает напряжение низкого уровня GND и, соответственно, на вход  напряжение высокого уровня VDD, то транзисторы первый 1, третий 3 и восьмой 8 закрываются, а пятый 5, шестой 6 и десятый 10 - открываются. Так как одиннадцатый транзистор 11 открыт ранее установленным на его затворе напряжением низкого уровня GND, то напряжение высокого уровня VDD через открытые транзисторы одиннадцатый 11 и пятый 5 поступает на исток шестого 6 транзистора, затвор седьмого 7, стоки восьмого 8 и девятого 9 транзисторов и на вход первого инвертора. Поэтому седьмой 7 транзистор открывается, а на выходе первого инвертора и выходе OUT Элемента входного регистра формируется напряжение низкого уровня GND. Через открытый седьмой 7 транзистор на затворах транзисторов четвертого 4, девятого 9, одиннадцатого 11 и двенадцатого 12 удерживается напряжение низкого уровня GND, в результате чего транзисторы четвертый 4 и одиннадцатый 11 сохраняются в открытом состоянии, а девятый 9 и двенадцатый 12 - в закрытом. Так как через открытый транзистор 4 на истоке первого 1 транзистора, затворе второго 2, стоках третьего 3 и 4 транзисторов и на входе второго инвертора сохраняется напряжение высокого уровня VDD, то на его выходе и, следовательно, на входе третьего инвертора - напряжение низкого уровня напряжения GND. Поэтому на выходе третьего инвертора, который является выходом

напряжение высокого уровня VDD, то транзисторы первый 1, третий 3 и восьмой 8 закрываются, а пятый 5, шестой 6 и десятый 10 - открываются. Так как одиннадцатый транзистор 11 открыт ранее установленным на его затворе напряжением низкого уровня GND, то напряжение высокого уровня VDD через открытые транзисторы одиннадцатый 11 и пятый 5 поступает на исток шестого 6 транзистора, затвор седьмого 7, стоки восьмого 8 и девятого 9 транзисторов и на вход первого инвертора. Поэтому седьмой 7 транзистор открывается, а на выходе первого инвертора и выходе OUT Элемента входного регистра формируется напряжение низкого уровня GND. Через открытый седьмой 7 транзистор на затворах транзисторов четвертого 4, девятого 9, одиннадцатого 11 и двенадцатого 12 удерживается напряжение низкого уровня GND, в результате чего транзисторы четвертый 4 и одиннадцатый 11 сохраняются в открытом состоянии, а девятый 9 и двенадцатый 12 - в закрытом. Так как через открытый транзистор 4 на истоке первого 1 транзистора, затворе второго 2, стоках третьего 3 и 4 транзисторов и на входе второго инвертора сохраняется напряжение высокого уровня VDD, то на его выходе и, следовательно, на входе третьего инвертора - напряжение низкого уровня напряжения GND. Поэтому на выходе третьего инвертора, который является выходом  , сохраняется напряжение высокого уровня VDD.

, сохраняется напряжение высокого уровня VDD.

Если на вход СЕ поступает напряжение низкого уровня GND и, соответственно, на вход  напряжение высокого уровня VDD, а на входе D перед этим было установлено напряжение низкого уровня GND, то транзисторы первый 1, пятый 5 и десятый 10 открываются, а транзисторы третий 3, шестой 6, и восьмой 8 - закрываются. Так как двенадцатый транзистор 12 открыт ранее установленным на его затворе напряжением высокого уровня VDD, то напряжение низкого уровня GND через открытые транзисторы двенадцатый 12 и десятый 10 поступает на исток первого 1 транзистора, затвор второго 2, стоки третьего 3 и 4 транзисторов и на вход второго инвертора. Поэтому второй 2 транзистор открывается, а на выходе второго инвертора и, следовательно, на входе третьего инвертора появляется напряжение высокого уровня VDD. Так как на входе третьего инвертора напряжение высокого уровня VDD, то на его выходе и выходе

напряжение высокого уровня VDD, а на входе D перед этим было установлено напряжение низкого уровня GND, то транзисторы первый 1, пятый 5 и десятый 10 открываются, а транзисторы третий 3, шестой 6, и восьмой 8 - закрываются. Так как двенадцатый транзистор 12 открыт ранее установленным на его затворе напряжением высокого уровня VDD, то напряжение низкого уровня GND через открытые транзисторы двенадцатый 12 и десятый 10 поступает на исток первого 1 транзистора, затвор второго 2, стоки третьего 3 и 4 транзисторов и на вход второго инвертора. Поэтому второй 2 транзистор открывается, а на выходе второго инвертора и, следовательно, на входе третьего инвертора появляется напряжение высокого уровня VDD. Так как на входе третьего инвертора напряжение высокого уровня VDD, то на его выходе и выходе формируется напряжение низкого уровня GND. При этом через открытый второй 2 транзистор на затворах транзисторов четвертого 4, девятого 9, одиннадцатого 11 и двенадцатого 12 сохраняется напряжение высокого уровня VDD.

формируется напряжение низкого уровня GND. При этом через открытый второй 2 транзистор на затворах транзисторов четвертого 4, девятого 9, одиннадцатого 11 и двенадцатого 12 сохраняется напряжение высокого уровня VDD.

При переходе схемы Элемента входного регистра в режим исходного состояния на управляющие входы прямой СЕ и инверсный  поступают напряжения, соответственно, высокого VDD и низкого GND уровней. Поэтому транзисторы третий 3 и восьмой 8 открываются, а транзисторы пятый 5 и десятый 10 - закрываются и вход D готов к приему и(или) изменению входного сигнала. Через открытый транзистор 3 на исток транзистора 1, на сток транзистора 10, на затвор транзистора 2 и на вход второго инвертора поступает напряжение высокого уровня VDD. Поэтому транзистор 2 закрывается, а на выходе второго и на входе третьего инверторов формируется напряжение низкого уровня GND. Так как на входе третьего инвертора напряжение низкого уровня GND, то на его выходе и выходе

поступают напряжения, соответственно, высокого VDD и низкого GND уровней. Поэтому транзисторы третий 3 и восьмой 8 открываются, а транзисторы пятый 5 и десятый 10 - закрываются и вход D готов к приему и(или) изменению входного сигнала. Через открытый транзистор 3 на исток транзистора 1, на сток транзистора 10, на затвор транзистора 2 и на вход второго инвертора поступает напряжение высокого уровня VDD. Поэтому транзистор 2 закрывается, а на выходе второго и на входе третьего инверторов формируется напряжение низкого уровня GND. Так как на входе третьего инвертора напряжение низкого уровня GND, то на его выходе и выходе  Элемента входного регистра устанавливается напряжение высокого уровня VDD. Одновременно через открытый транзистор 8 на исток транзистора 6, сток транзистора 5, на затвор транзистора 7 и на вход первого инвертора поступает напряжение низкого уровня GND. Поэтому седьмой 7 транзистор тоже закрывается. Так как на выходе первого инвертора и выходе OUT Элемента входного регистра устанавливается напряжение высокого уровня VDD, то схема Элемента входного регистра переходит в режим ожидания (Standby), соответствующий исходному состоянию, а именно, на обоих выходах OUT и

Элемента входного регистра устанавливается напряжение высокого уровня VDD. Одновременно через открытый транзистор 8 на исток транзистора 6, сток транзистора 5, на затвор транзистора 7 и на вход первого инвертора поступает напряжение низкого уровня GND. Поэтому седьмой 7 транзистор тоже закрывается. Так как на выходе первого инвертора и выходе OUT Элемента входного регистра устанавливается напряжение высокого уровня VDD, то схема Элемента входного регистра переходит в режим ожидания (Standby), соответствующий исходному состоянию, а именно, на обоих выходах OUT и  установлено напряжение высокого уровня VDD, независимо от состояния входа данных D.

установлено напряжение высокого уровня VDD, независимо от состояния входа данных D.

Так как в предлагаемом Элементе входного регистра, вместо четвертого инвертора введены два МОП транзистора, то суммарные паразитные узловые емкости, образованные подсоединенными к входам выходных инверторов, и емкости узлов стоков, введенных МОП транзисторов, подсоединенных к соответствующим истокам ключевых МОП транзисторов уменьшены, что позволяет повысить быстродействие Элемента входного регистра за счет уменьшения времени переходного процесса переключения перечисленных узлов.

Отсутствие четвертого инвертора устраняет необходимость физического соединения стоков комплементарной пары МОП транзисторов этого инвертора с истоками ключевых транзисторов, что уменьшает емкость критичных узлов и повышает быстродействие Элемента входного регистра. Кроме того, входные сигналы ВК и  , подсоединены каждый к затворам двух МОП транзисторов, в результате чего нагрузочная способность входных сигналов увеличивается и ускорят переходный процесс источников входных сигналов, что в свою очередь дополнительно повышает быстродействие схемы.

, подсоединены каждый к затворам двух МОП транзисторов, в результате чего нагрузочная способность входных сигналов увеличивается и ускорят переходный процесс источников входных сигналов, что в свою очередь дополнительно повышает быстродействие схемы.

Таким образом, в предлагаемом Элементе входного регистра быстродействие повышено.

Литература

1. Кармазинский А.М. Синтез принципиальных схем цифровых элементов на МДП-транзисторах. - М.: Радио и связь, 1983. Рис. 3.22, стр. 142.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЭЛЕМЕНТ ВХОДНОГО РЕГИСТРА | 2021 |

|

RU2771447C1 |

| ПРЕОБРАЗОВАТЕЛЬ УРОВНЯ НАПРЯЖЕНИЯ | 2018 |

|

RU2679186C1 |

| ПРЕОБРАЗОВАТЕЛЬ УРОВНЯ НАПРЯЖЕНИЯ | 2017 |

|

RU2667798C1 |

| ПРЕОБРАЗОВАТЕЛЬ УРОВНЯ НАПРЯЖЕНИЯ | 2016 |

|

RU2604054C1 |

| ПРЕОБРАЗОВАТЕЛЬ УРОВНЯ НАПРЯЖЕНИЯ | 2016 |

|

RU2632567C1 |

| ПРЕОБРАЗОВАТЕЛЬ ЛОГИЧЕСКОГО УРОВНЯ НАПРЯЖЕНИЯ | 2016 |

|

RU2642416C1 |

| ВЫСОКОВОЛЬТНЫЙ ПРЕОБРАЗОВАТЕЛЬ УРОВНЯ НАПРЯЖЕНИЯ | 2019 |

|

RU2702979C1 |

| КМОП ЛОГИЧЕСКИЙ ВЕНТИЛЬ ИСКЛЮЧАЮЩЕЕ-ИЛИ | 2023 |

|

RU2814896C1 |

| ЛОГИЧЕСКИЙ ВЕНТИЛЬ ИСКЛЮЧАЮЩЕЕ-ИЛИ | 2023 |

|

RU2802665C1 |

| ТРЁХВХОДОВОЙ КМОП ЛОГИЧЕСКИЙ ВЕНТИЛЬ ИСКЛЮЧАЮЩЕЕ ИЛИ/ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ | 2020 |

|

RU2761172C1 |

Настоящее изобретение относится к области вычислительной техники. Технический результат заключается в повышении быстродействия элемента входного регистра. Технический результат достигается за счёт того, что схема элемента входного регистра содержит шину питания высокого уровня напряжения VDD, шину питания низкого уровня напряжения GND, шесть МОП-транзисторов Р-типа и шесть МОП-транзисторов N-типа, первый, второй и третий инверторы, управляющие входы СЕ и  , вход данных D и выходы OUT и

, вход данных D и выходы OUT и  . 1 ил.

. 1 ил.

Элемент входного регистра, содержащий МОП-транзисторы Р-типа с первого по пятый и N-типа с шестого по десятый, вход сигнала D, вход сигнала СЕ, соединенный с затворами транзисторов пятого и восьмого, вход сигнала  , соединенный с затворами третьего и десятого транзисторов, шину источника питания высокого уровня напряжения VDD, соединенную с истоками транзисторов второго, третьего и четвертого, шину источника питания низкого уровня напряжения GND, соединенную с истоками транзисторов седьмого, восьмого и девятого, первый инвертор, вход которого соединен со стоками транзисторов пятого, восьмого и девятого и затвором седьмого транзистора, а выход является выходом OUT, второй инвертор, вход которого соединен со стоками транзисторов третьего, четвертого и десятого и затвором второго транзистора, а выход соединен с входом третьего инвертора, выход которого является выходом

, соединенный с затворами третьего и десятого транзисторов, шину источника питания высокого уровня напряжения VDD, соединенную с истоками транзисторов второго, третьего и четвертого, шину источника питания низкого уровня напряжения GND, соединенную с истоками транзисторов седьмого, восьмого и девятого, первый инвертор, вход которого соединен со стоками транзисторов пятого, восьмого и девятого и затвором седьмого транзистора, а выход является выходом OUT, второй инвертор, вход которого соединен со стоками транзисторов третьего, четвертого и десятого и затвором второго транзистора, а выход соединен с входом третьего инвертора, выход которого является выходом  причем стоки транзисторов первого, второго, шестого и седьмого соединены с затворами транзисторов четвертого и девятого, отличающийся тем, что в него введены одиннадцатый МОП-транзистор Р-типа и двенадцатый МОП-транзистор N-типа, затворы которых соединены с затворами транзисторов четвертого и девятого, и сток одиннадцатого транзистора соединен с истоком пятого, сток двенадцатого - с истоком десятого, а исток одиннадцатого транзистора - с шиной источника питания высокого уровня напряжения VDD, а двенадцатого - с шиной источника питания низкого уровня напряжения GND, и исток первого транзистора соединен с затвором второго, исток шестого транзистора - с затвором седьмого, а затворы транзисторов первого и шестого с входом D.

причем стоки транзисторов первого, второго, шестого и седьмого соединены с затворами транзисторов четвертого и девятого, отличающийся тем, что в него введены одиннадцатый МОП-транзистор Р-типа и двенадцатый МОП-транзистор N-типа, затворы которых соединены с затворами транзисторов четвертого и девятого, и сток одиннадцатого транзистора соединен с истоком пятого, сток двенадцатого - с истоком десятого, а исток одиннадцатого транзистора - с шиной источника питания высокого уровня напряжения VDD, а двенадцатого - с шиной источника питания низкого уровня напряжения GND, и исток первого транзистора соединен с затвором второго, исток шестого транзистора - с затвором седьмого, а затворы транзисторов первого и шестого с входом D.

| ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ | 2007 |

|

RU2374745C2 |

| ПРЕОБРАЗОВАТЕЛЬ УРОВНЯ НАПРЯЖЕНИЯ | 2018 |

|

RU2679186C1 |

| US 6169391 B1, 02.01.2001 | |||

| US 6777981 B2, 17.08.2004 | |||

| US 6580258 B2, 17.06.2003 | |||

| KR 102122304 B1, 12.06.2020. | |||

Авторы

Даты

2023-01-13—Публикация

2022-04-21—Подача