пряжениям UqH U:,. в результате на выходах С 4 и 7 появляются сигналы,, в которых компенсируется воздействие

Изобретение относится к электросвй ;зи и может использоваться в системах передачи, данных и телемеханики.

Цель изобретения - повышение помехоустойчивости в условиях действия импульсных помех.

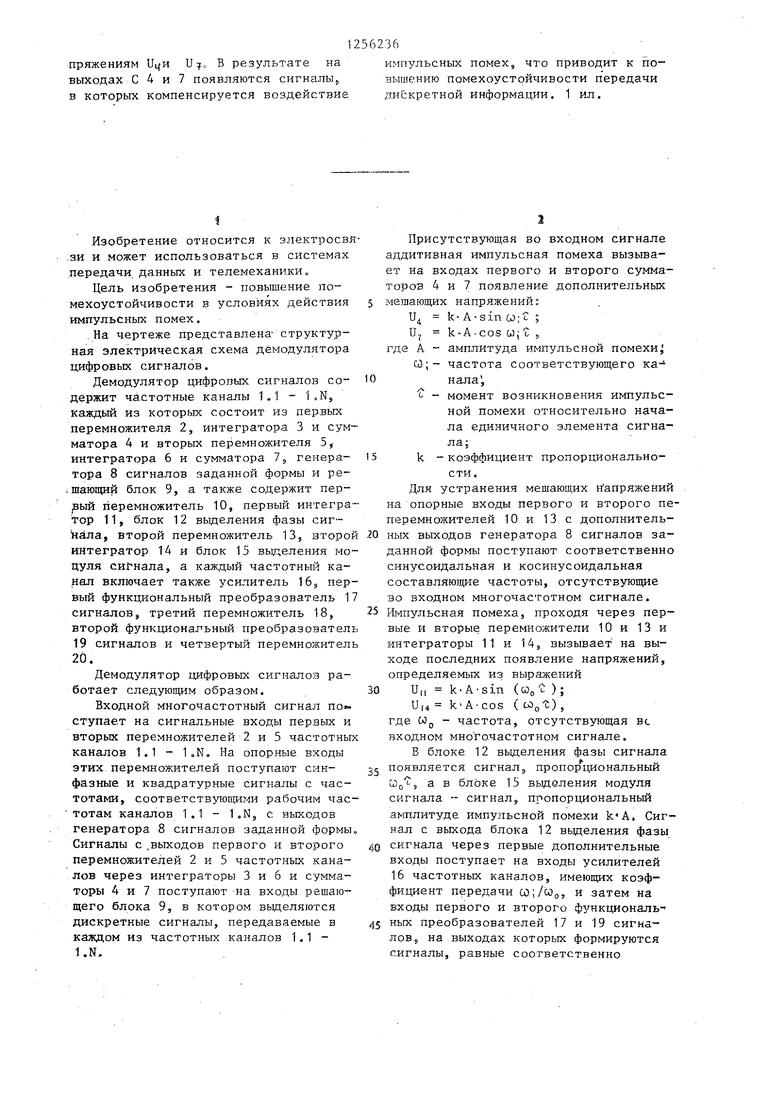

.На чертеже представлена- структурная электрическая схема демодулятора цифровых сигналов.

Демодулятор цифровых сигналов содержит частотные каналы 1.1 1.N, каждый из которых состоит из первых перемножителя 2, интегратора 3 и сумматора 4 и вторых перемножителя 5, интегратора 6 и сумматора 7 генератора 8 сигналов заданной формы и ре- Iшающий блок 9, а также содержит пер- рый перемножитель 10, первый интегратор 11, блок 12 вьщеления фазы сиг- нала, второй перемножитель 13, второй интегратор 14 и блок 15 выделения модуля сиГ-нала, а каждый частотный ка- н:ал включает также усилитель 16 первый функциональный преобразователь 17 сигналов, третий перемножитель 18, второй функциональный преобразователь 19 сигналов и четвертый перемножитель 20.

Демодулятор цифровых сигнало:з работает следующим образом.

Входной многочастотный сигнал по. ступает на сигнальные входы первых и вторых перемножителей 2 и 5 частотных каналов 1.1 - 1.N. На опорные входы этих перемножителей поступают синфазные и квадратурные сигналы с частотами, соответствующими рабочим час- тотам каналов 1.1 - 1.N, с выходов генератора 8 сигналов заданной формы. Сигналы с ,выходов первого и второго перемножителей 2 и 5 частотных каналов через интеграторы 3 и 6 и сумматоры 4 и 7 поступают -на входы решающего блока 9, в котором выделяются дискретные сигналы, передаваемые в каждом из частотных каналов 1.1 - I.N.

импульсных помех, что приводит к повышению помехоустойчивости передачи дискретной информации, 1 ил.

Присутствующая во входном сигнале аддитивная импульсная помеха вызывает на входах первого и второго сумматоров 4 и 7 появление дополнительных мешающих напряжений: U, k- А sin GJ;c ; U k-A-cos u; t 5

где A амплитуда импульсной помехиj Q;- частота соответствующего ка- нала ,

момент возникновения импульсной помехи относительно начала единичного элемента сигнала;

k -коэффициент пропорциональности.

Для устранения мешающих Напряжений на опорные входы первого и второго пе- перемножителей 10 и 13 с дополнительных выходов генератора 8 сигналов заданной формы поступают соответственно синусоидальная и косинусоидальная составляющие частоты, отсутствующие во входном многочастотном сигнале. Импульсная помеха, проходя через первые и вторые перемножители 10 и 13 и интеграторы 11 и 14, вызывает на выходе последних появление напряжений, определяемых из выражений и,| k-A sin (Uo ); U(4 k A-cos ( Wot), где WQ - частота, отсутствующая вс входном мно го.частотном сигнале.

В блоке 12 вьщеления фазы сигнала появляется сигнал, пропор циональный u3(j i, а в блоке 15 выделения модуля сигнала - сигнал, пропорциональный амплитуде импульсной помехи k A. Сигнал с выхода блока 12 выделения фазы сигнала через первые дополнительные входы поступает на входы усилителей 16 частотных каналов, имеющих коэффициент передачи со;/сОо, и затем на входы первого и второго функциональ ных преобразователей 17 и 19 сигналов j на выходах которых формируются сигналы, равные соответственно

sin (U; D) и cos (u;t). Эти сигналы поступают на первые входы третьего и четвертого перемножителей 18 и 20 частотных каналов, на вторые входы которых через вторые дополнительные входы частотных каналов поступают сигналы с блока 15 вьщеления модуля сигнала.

Таким образом в каждом частотном канале на выходах третьего и четвертого перемножителей 18 и 20 образуются сигналы, равные и противофазные упоминавшимся вьше мешающим напряжениям U4 и и В результате этого на выходах сумматоров 4 и 7 появляются сигналы, в которых компенсируется воздействие импульсных помех, что приводит к повьшению помехоустойчивости передачи дискретной информации.

Формула изобретения

Демодулятор цифровых сигналов, содержащий частотные каналы, каждый из которых состоит из последовательно соединенных первых перемножителя, интегратора и сумматора и последовательно соединенных вторых перемножителя, интегратора и сумматора, причем объе- диненные сигнальные входы первых и вторых перемножителей частотных каналов являются входом демодулятора, а опорные входы первых и вторых перемножителей частотных каналов подклю- чены к соответствующим выходам генератора сигналов заданной формы, при .этом выходы первого и второго сумматоров частотных каналов соединены с

Редактор Н. Данкулич Заказ 4838/59

Составитель В. Зенкин

Техред М.Ходанич Корректор Т.Колб

Тираж 624Подписное

ВНИИПЙ Государственного комитета СССР

по делам изобретений и от-крытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

1256236

входами решающего блока, выходы которого являются выходами демодулятора, отличающийся тем, что, с целью повьшения помехоустойчивости, в условиях действия импульсных помех, в него введены последовательно соединенные первый перемножитель, первый интегратор и блок вьщеления фазы сигнала, последовательно соединенные второй перемножитель, второй интегратор и блок вьщеления модуля сигнала, а в каждый частотный канал введены последовательно соединенные усилитель первый-функциональный преобразователь сигналов и третий перемножитель и последовательно соединенные второй функциональный преобразователь сигналов и четвертый перемножитель, причем выходы третьего и четвертого перемножителей соединены с вторыми входами первого и второго сумматоров соответственно, вход второго функционального преобразователя сигналов подключен к выходу усилителя, при этом опорные входы первого и второго перемножите- лей соединены с дополнительными выходами генератора сигналов заданной формы, вторые входы блока выделения модуля сигнала и блока вьщеления фазы сигнала подключены к выходам первого и второго интеграторов срответс твен- но, сигнальные входы первого и второго перемножителей объединены с входом демодулятора, а вход усилителя и объединенные опорные входы третьего и четвертого перемножителей соединены соответственно с выходом блока вьщеления фазы сигнала и выходом блока вьщеления модуля сигнала.

| название | год | авторы | номер документа |

|---|---|---|---|

| Приемник цифровых сигналов | 1985 |

|

SU1406813A2 |

| ЦИФРОВОЙ МОДЕМ КОМАНДНОЙ РАДИОЛИНИИ ЦМ КРЛ | 2013 |

|

RU2548173C2 |

| Устройство для приема сигналов с частотно-фазовой модуляцией | 1988 |

|

SU1518915A2 |

| Устройство для импульсно-фазового управления преобразователем | 1983 |

|

SU1094127A1 |

| СИСТЕМА ВЫСОКОСКОРОСТНОЙ ДЕКАМЕТРОВОЙ РАДИОСВЯЗИ | 2014 |

|

RU2608554C2 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА ДИСКРЕТНЫХ СООБЩЕНИЙ С ИСПОЛЬЗОВАНИЕМ СИГНАЛОВ С ПРЯМЫМ РАСШИРЕНИЕМ И АВТОКОРРЕЛЯЦИОННЫМ СЖАТИЕМ СПЕКТРА | 2008 |

|

RU2358401C1 |

| СИСТЕМА ДЕКАМЕТРОВОЙ РАДИОСВЯЗИ С ВЫСОКОСКОРОСТНОЙ ПЕРЕДАЧЕЙ ДАННЫХ | 2015 |

|

RU2608569C2 |

| ДЕМОДУЛЯТОР ДВУХПОЗИЦИОННЫХ ФАЗОМАНИПУЛИРОВАННЫХ СИГНАЛОВ | 2018 |

|

RU2699066C1 |

| Автокорреляционный демодулятор псевдослучайных сигналов с относительной фазовой модуляцией второго порядка | 2017 |

|

RU2660594C1 |

| СПОСОБ ПОМЕХОУСТОЙЧИВОЙ ДЕКАМЕТРОВОЙ РАДИОСВЯЗИ С ВЫСОКОСКОРОСТНОЙ ПЕРЕДАЧЕЙ ДАННЫХ | 2023 |

|

RU2825314C1 |

Изобретение относится к электросвязи и может быть использовано в системах передачи данных и телемеханики. Целью изобретения является по- вьшение помехоустойчивости в условиях /f/ iдействия импульсных помех. Демодулятор содержит частотные каналы -1.1- 1.N, каждый из которых состоит из первых перемножителя (П) 2, интегратора 3, сумматора (С) 4 и вторых П 5, интегратора 6, С 7, генератор 8 сигналов заданной формы, решающий блок 9, П 10 и 13, интеграторы 11 и 14, блок 12 выделения фазы сигнала и блок 15 выделения модуля сигнала. Каждый частотный канал включает также усилитель 16, функциональные преобразователи 17 и 19, П 18 и 20. Присутствующая во входном сигнале аддитивная импульсная помеха вызывает на входах С 4 и 7 появление метающих напряжений и и U-J. В каждом частотном канале на вьпсодах П 18 и 20 образуются сигналы, равные и противофазные на- (П yi /. k

| Устройство для приема двух псевдослучайных фазоманипулированных сигналов | 1982 |

|

SU1104680A1 |

| кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Вяжущее | 1988 |

|

SU1537664A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1986-09-07—Публикация

1984-12-25—Подача