Изобретение относится к регистрирующей технике и может быть исполь зойано в автоматических регистрирующих приборах для вывода информации из электронных вычислительных машин

Цель изобретения - повьштение быстродействия и точности устройства.

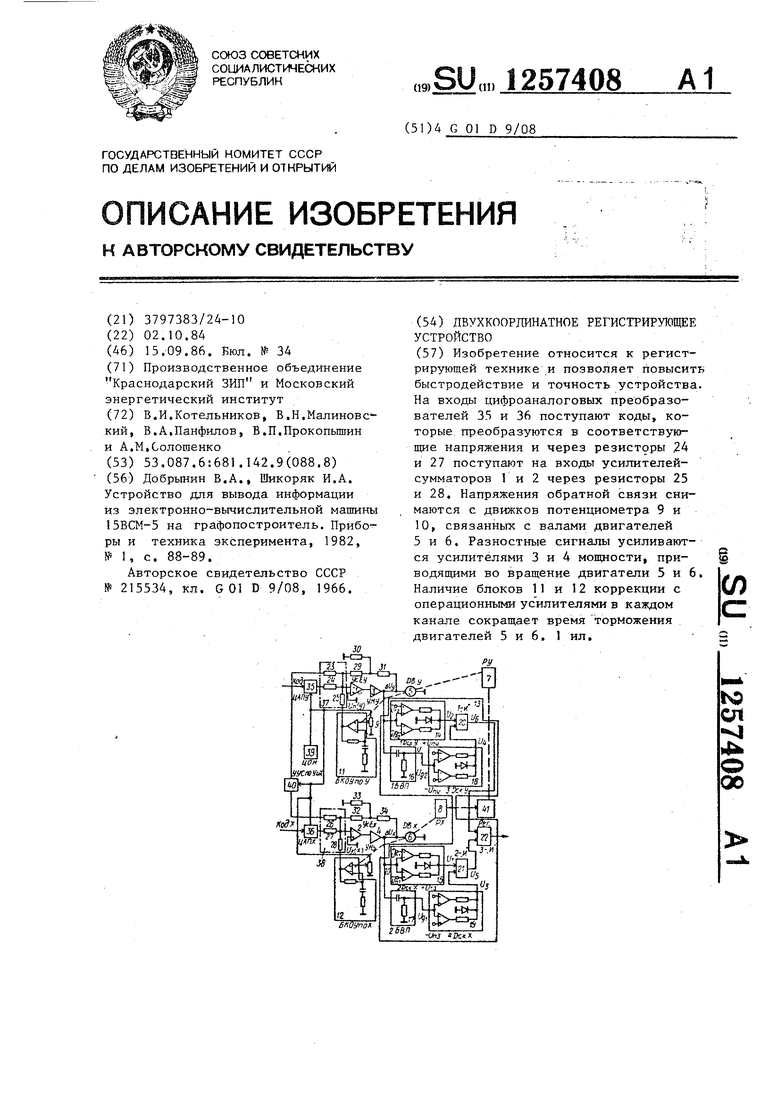

На чертеже схематически показано устройство.

Устройство содержит усилители- сумматоры и 2 , по Y и X (У, i: по У и X)J усилители 3 и 4 мощности по каналам У и X (УМ по У и X), двигатели 5 и 6 в каналах У и X (ДвУ,, ДВХ редукторы 7 и 8 в каналах У и X (РУ, РХ), потенциометры 9 и 10 обратной связи по положению по У и X (ПОС yj ПОС X)5 блоки 11 и 12 коррекции с операционным усилителем по каналам У и X (БКОУ по У Бкру по X), блок 13 выдачи сигнала Готовность первый и второй дискриминаторы 14 и 15,. по У и X (1-2 Дек У и X) , первый и второй блоки 16 и 17 выделения производной (1 и 2 ВВП), третий и четвертый дискриминаторы I 8 и 19 по У и X (3-4 Дек У и Х), первую, вторую и третью схемы 20-22 И (l-H, 2-11, 3-Й), резисторы 23-28 усилителей- сумматоров 1 и 2 по У и Х, резисторы 29-34 обратной связи усилителей-сумматоров 1 и 2 и усилителей мощности 3 и 4, цифроаналоговые преобразователи 35 и 36 по У и X (ЦАП У и X)5 сравнивающие устройства 37 и 38 по У и Xj источник 39 опорного напряжения- (ИОН) , блок 40 управления смещения по У и X (УУС по У н X), регистрирующий блок 41 (Per).

Выход усилителей-сумматоров и 2 по У и X через усилители 3 и 4 мощности по каналам У и X соединены с двигателями 5 и 6 каналов У и X, которые через редукторы 7 и 8 каналов У и X соединены с регистрирующим блоком 4 и одновременно с ками потенциометров 9 и 10 обратной связи по положению по У и Х.

Инвертирующие входы усилителей- сумматоров через резисторы 25 и 26 соответственно соединены с блоками II и 12 коррекции с операционными усилителями, в которые входят операционные усилители, инвертирующие входы которых через соответствующие резисторы coeдинeIiы с их входами н через последовательно соединенные конденсатор и резистор - с общей точкой, неинвертирзпощие входы - с

5

0

5

0

5

0

5

0

5

движком потенциометров 9 и 10 обратной связи, соответственно через резисторы 24 и 27 - с цифроаналого- выми преобразователями, через резисторы 23 и 26 - с блоком 40 управления смещением,

Инвертируюпхие входы усилителей- сумматоров соответственно через резисторы 29, 30 и 32, 33 соединены с общей точкой, а через резисторы 29, 31 и 32, 34 - с вьг/содами усилителей 3 и 4 мощности, соединенных с соответствующими двигателями 5 и. 6 каналов, входами первого и второго дискриминаторов 14 и 15 и первым и вторым блокат-да 6 и 17 выделения производной.

Выход источника 39 опорного напряжения соединен с входами цифро- аналоговых преобразователей 35 и

о

36 и одними концами выводов потенциометров обратной связи по У и X, вторые концы которых подключены к общей точке.

Выходы первого и второго блоков 16 и 17 вьщеления производной соответственно соединены с входами третьих и четвертых дискриминаторов 18 и 19, выходы которых и выходы первых и второго диcкpи инaтopoв 14 и 15 соединены соответственно с входами первой и второй схем И 20 и 21, выходы последних соединены с входами третьей схемы И 22, на выходе которой формируется сигнал Готовность,

Устройство работает следующим образом.

,На первые входы цифроаналоговых преобразователей 35 и 36 поступают коды, которые преобразутотся в соответствующие напряжения Ug(y) и Ug)((X) и через резисторы 24 и 27 поступают соответственно на инвертирующие- входы усилителей-сумматоров через резисторы 25 и 28. К этим же инвертирующим входам усилителей-сумматоров 1 и 2 поступают напряжения отрицательных обратньп связей блоков П и 12 коррекции с операционны- 1-га усилителями. Напряжения обратной связи U|(y) и Пц (X) снимаются с движков потенциометров 9 и 10 обратной связи по положению, жестко связан-, ньгх с соответствую11гими валами реверсивных двигателей 5 и 6 каналов. Выходные напряжения U (У) и U. (X) содержат составляюгцие, пропорционшть- Hijie положениям носителя и пишущего

10

пера соответственно, а также аксиальным скоростям их движения, и соответственно вычитаются из входных напряжений и(У) и и,(Х) в сравнивающих устройствах 37 и 38 каналов. Полученные разностные сигналы усиливаются усилителями 3 и 4 мощности, которые приводят во вращение двигатели 5 и 6.

Наличие блоков 11 и 12 коррекции с операционными усилителями в каждом канале У и X приводит к тому, что при подходе пера к точке с требуемыми координатами на выходах усилителей рассогласования появляются усиленные разностные напряжения uU,j и л Ujj противоположной полярности. Это значительно сокращает время торможения двигателей 5 и 6j следовательно повьшается быстродействие уст-2о ройства. Остановка носителя и пера происходит после уменьшения н апряже- ний на д ll,j ийЬ до напряжения трога- ния соответствующих двигателей 5 и 6.

Напряжения AlL и. &U поступают также на входы блока 13 выдачи сиг- нала Готовность. Пороги срабатьгоа- ния дискриминаторов 14 и 15 (±tJn,

15

+lIfiJ 5 например, вьтолненных на операционных усилителях, выходы которых через резисторы соединены между собоЙ5 а точка соединения резисторов через диод или стабилитрон соединена с общей точкой, устанавливаются из значений tUons которые выбираются равными напряжению тро- гания соответствующих электродвигателей, nosTONTV высокие уровни выходных напряжений этих дискриминаторов и и Uj имеют место не только при равновесии следящих систем, но и на участках торг ожения электродвигателей 5 и 6. Низкие уровни напряжений Uj и и. на выходах третьего и четвертого дискриминаторов 18 и 19 появляются при изменениях входных напряжений следящих систем и на участках . торможения электродвигателей 5 и 6, так как на входы третьего и четвертого дискриминаторов I8 и 19 соответственно поступают выходные напряжения Ug и U первого и второго блоков 16 и 17 выделения производной. Поэтому при соответствующем выборе постоянных времени этих блоков и порогов срабатывания третьего и четвертого дискриминаторов 18 и 19 (±и„ и tU) высокие уровни на3D

35

40

45

50

55

25

10

-2о

257Д084.

пряжений и J и Ug на выходах схем И 20 и 21 появляются только в моменты равновесия, соответствующие следующей точке выводимой графической или текстовой информации, формируя на выходе третьей схемы И 12 сигнал Готовность. В частностиS сигнал Готовность может воздействовать на систему прерываний электронной вычислительной машины.

Формула изобретения

Двухкоординатное регистрирующее устройство, содержащее регистрирующий блок, два канала астатической следящей системы по координатам X и У, каждая из которых,содержит сравнивающее устройство 5 выход которого через усилитель, двигатель и .редуктор связан с регистрирующим блоком и движком потенциометра-обратной связи, а также блок выдачи сигнала Го- TOBHOCTb s подключенный двумя входами к выходам усилителей, отличающееся тем, что, с-целью . повьшения быстродействия и точности устройства, в него введены источник опорного напряжения, блок управления смещением, каждый канал содержит цифроаналоговый преобразователь, блок коррекции и цепь обратной связи усилителя, причем в каждом канале блок коррекции включен между движком потенциометра обратной связи и пер- вьш входом сравнивающего устройства, выход источника опорного напряжения соединен с клеммой питания потенциометра обратной связи, с входом блока управления смещением и с вторым входом циЛроаналогового преобразователя, первьш вкод которого является входом устройства по соответствующей координате,, выход соединен с вторым входом сравнивающего устройства, третий и четвертый входы которого подключены к выходу блока упоавлент-.л смещением и цепи обратной связи усилителя, а блок выдачи сигнала Готовность СОСТОИТ из двух каналов по осям X и У, каждый из которых содержит два дискриминатора, блок вьоделе- ния производной и схему И, и общей для обоих каналов схемы И, при этом входная клемь{а блока выдачи сигнала Готовность для каждого канала подключена через первый дискриминатор к первому входу схемы И, через послея1257408®

допате гько соединенные блок пьщеле- мы И, а выходы схем И по каждоьгу ка- ния нрочявпдчой м отор ОЙ ,1 кс сркк ИН;1-- налу подключены к первому и второму тпЬ - к второму 1злодз указанной схе- входам обпгей схемы И,

Наказ 44 l5/3b Тираж 705Подписное

ВНИЖШ Государственного комитета СССР

по делам изобретений н открытий 13035., Москва, Ж-ЗЗ, Раушская наб,, д., 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная. 4

Корректор Л.Патай

| название | год | авторы | номер документа |

|---|---|---|---|

| Функциональный преобразователь | 1979 |

|

SU849241A1 |

| Функциональный преобразователь | 1981 |

|

SU993285A1 |

| Устройство для измерения разности температур | 1980 |

|

SU909588A1 |

| Система для программного управления правильной машиной | 1986 |

|

SU1327065A1 |

| Устройство для моделирования тиристора | 1983 |

|

SU1091190A1 |

| Интегрирующее устройство | 1979 |

|

SU824227A1 |

| Формирователь многофазного синусоидального напряжения для частотно-управляемого электропривода | 1988 |

|

SU1598096A1 |

| Многодвигательный электропривод | 1991 |

|

SU1774457A1 |

| Система биоадаптивного регулирования | 1983 |

|

SU1110441A1 |

| Устройство для двухкоординатного позиционирования | 1982 |

|

SU1070512A1 |

Изобретение относится к регистрирующей технике и позволяет повысить быстродействие и точность устройства. На входы цифроаналоговых преобразователей 35 и 36 поступают коды, которые преобразуются в соответствующие напряжения и через резисторы 24 и 27 поступают на входы усилителей- сумматоров 1 и 2 через резисторы 25 и 28. Напряжения обратной связи снимаются с движков потенциометра 9 и 10, связанных с валами двигателей 5 и 6. Разностные сигналы усиливаются усилителями 3 и 4 мощности, приводящими во вращение двигатели 5 и 6. Наличие блоков 11 и 12 коррекции с операционными усилителями в каждом канале сокращает время торможения двигателей 5 и 6. 1 ил. (Л ьо О1 Ч 4 О 00

| Добрынин В.А., Шикоряк И.А | |||

| Прибор для нагревания перетягиваемых бандажей подвижного состава | 1917 |

|

SU15A1 |

| Приборы и техника эксперимента, 1982, № 1, с | |||

| Шланговое соединение | 0 |

|

SU88A1 |

| ДВУХКООРДИНАТНЫЙ РЕГИСТРИРУЮЩИЙ ПРИБОР | 1966 |

|

SU215534A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1986-09-15—Публикация

1984-10-02—Подача