10

5

25

Изобретение относится к измериельной технике, в частности к измеителям амплитуды однократных имульсов сложной формы.

Целью изобретения является расшиение функциональных возможностей нализатора путем измерения всех кстремальных (максимальных) значений мпульсов сложной формы.

Эта цель достигается тем, что в стройство дополнительно введены р ополнительных параллельных ветвейо

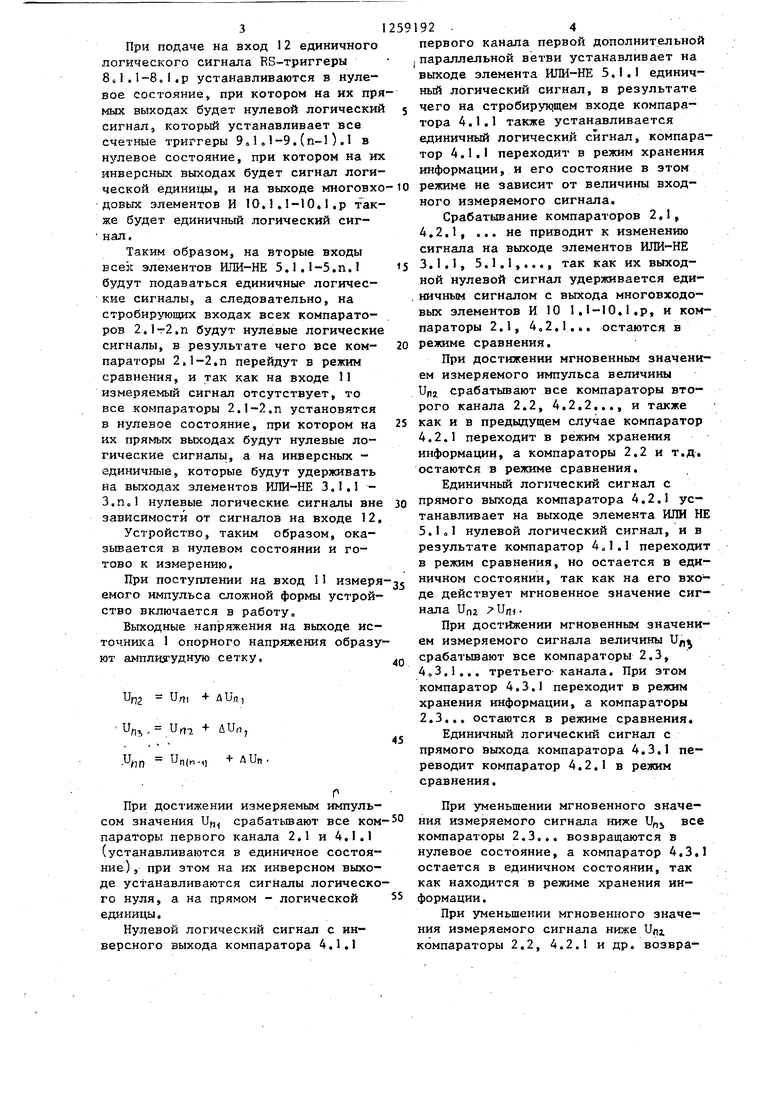

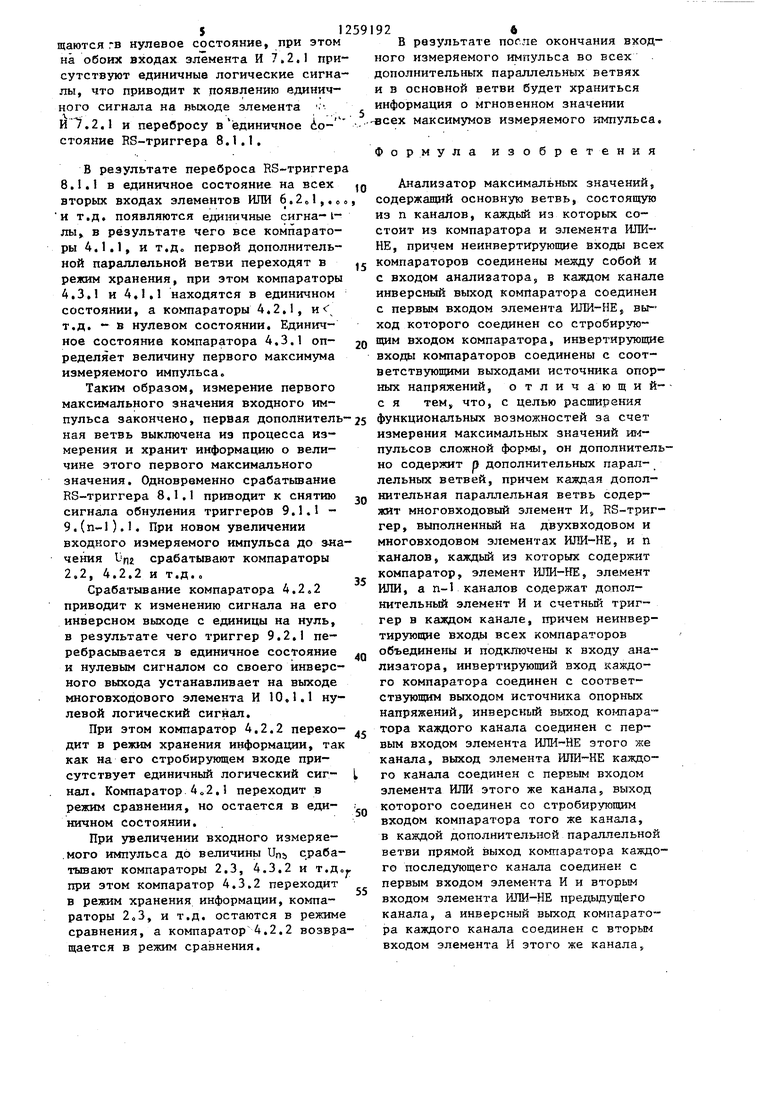

.На фиг. 1 представлена структурная схема устройства; на фиг. 2 - импульс сложной формы. .

Устройство содержит основную ветвь.. р дополнительных параллельных ветвей и источник 1 опорных напряжений. На фиг. 1 показаны тдлько две первые из р дополнительных параллельных вет- , вей.

Каждая из ветвей (основная и дополнительные ) содержит п каналов. Каждый канал основной ветви состоит из компаратора 2.1..2.п и элемента ИЛИ-НЕ 3.1.1...3.П.1. Каждьй канал дополнительных параллельных ветвей состоит из компаратора 4.1.1...А.П.1, элемента 5.1.1...5.п.1, зле- мента ИЛИ 6.1.1...б.п.1. Каждый из (п-1) каналов дополнительных параллельных ветвей содержит элемент И 7.1.1...7.(п-1).1.

Кроме того, каждая дополнительная паралпельная ветвь содержит RS-триг- гер 8.1.1...8в1.р, на многовходовом и двухвходовом элементах ИЛИ-НЕ,(п-1) счетных триггеров 9.1.1...9.(п-1).1 и многовходовый элемент И 10.1.1.... 10.1.р.

Измеряемый импульс подается на вход 11 устройства, сигнал Сброс - на вход 12 Сброс устройства.

Неинвертирующие входы всех ком- раторов 2.1-2.П подключены к входу 11 устройства.

Инвертирующие входы всех компа- , раторов подключены к соответствующим выходам источника 1 опорных напряжений (на фиг. 1 указаны только адреса связей).

В каждой ветви инверсный выход компаратора 2.1 каждого канала соединен с первым входом элемента ИЛИ- НЕ 3.1.1...З.П.1 этого же канала. В основной ветви выход элемента ИПИ-НЕ 3.1 о 1...З.п.1 каждого канала соединен со стробирующим входом компаратора 2.1.. ..2.П этого же канала.

ib

35

40

45

50

55

10

5

25

я с

ь.. ,

,

)

, 2591922

В каждой дополнительно} параллельной ветви соответственно соединены . прямой выход компаратора 4,2.1... 4.П.П последующего канала с nepabtM входом элементов И 7 .2.1-7 . (f1-1 ) ./ и вторым входом элемента ИЛИ-НЕ 5.1.1...5.П.1 предьщущего канала, инверсный выход компараторов 4.1.1 4.Л.1 каждого канала соединен с вторым входом элементов И 7.1.1.-7.(п- 1).1 этого же канала, выход элементов ИЛИ-НЕ 5.1.1-5.п.I каждого канала соединен с первым входом элемента ИЛИ 6.1 .1 .. .б. п. 1 этого же канала, а выход элемента ИЛИ 6.1.1.... 6.П.1 каждого канала соединен со стробирующим входом компараторов 4.1.1-4.п.1 этого же канала,

В первой дополнительной параллельной ветви третьи входы всех элементов Ш1И-НЕ 5.1.1...5.Г1.1 соединены с входом 12 Сброс устройства.

В каждой дополнительной параллельной ветви выходы элементов И 7.1.1-7,(п-1).1 соединены с S-входа- ми RS-триггеров 8;1.1-8.1,р. R-входы RS-триггеров 8.1.1-8.1.р всех дополнительных параллельных ветвей подключены к входу 12 Сброс.

Прямой выход RS-триггера 8.1.1... 8.1.p каждой дополнительной параллельной ветви соединен с вторыми входами элементов ИЛИ 6.1.1-6,п.1 и R-входами счетных триггеров 9.1.1- 9.(п-0.1 этой же ветви. Инверсные выходы всех счетных триггеров 9.1,1- 9.(п-1).1 в каждой дополнительной параллельной ветви соединены с входами многовходовых элементов И 10.1.1- 10.1,р.

Выход элементов И 10.1,1-10,1,п каждой предыдущей дополнительной параллельной ветви соединен с третьими входами элементов ИЛИ-НЕ 5.1 ,1-5.П.г последующей дополнительной параллельной вотви.

Выход элемента И 10. Up р-й до- полнительйой параллельной ветви соединен с вторыми входами элементов ИЛИ-НЕ 3.1.1-З.по 1 основной ветви.

В каждой предыдущей дополнительной параллельной ветви счетный вход счетного триггера 9.1,1.,.9.(п-1).1 каждого канала соединен с инверсным выходом компаратора 4,2.1.,,4.п.2 этого же канала, но последующей ветви.

Устройство работает следующим образом.

ib

35

40

45

50

55

31

При подаче на вход 12 единичного логического сигнала RS-триггеры 8«1.1-8.,р устанавливаются в нулевое состояние при котором на их прямых вькодах будет нулевой логический сигнал, который устанавливает все счетные триггеры 9.1.1-9.(п-1).1 в нулевое состояние, при котором на их инверсных выходах будет сигнал логической единицы, и на выходе миоговхо довых элементов И 10.1.1-10.I,р также будет единичный логический сиг- нал.

Таким образом, на вторые входы всех элементов ИЛИ-НЕ 5.1,1-5,п. 1 будут подаваться единичные логические сигналы, а следовательно, на стробирующих входах всех компараторов 2,1-2.п будут нулевые логические сигналы, Б результате чего все ком- параторы 2.1-2.П перейдут в режим сравнения, и так как на входе 11 измеряемый сигнал отсутствует, то все компараторы 2.1-2.П установятся в нулевое состояние, при котором на их прямых выходах будут нулевые логические сигналы, а на инверсных - единичные, которые будут удерживать на выходах элементов ИЛИ-НЕ 3.1.1 - З.П.1 нулевые логические сигналы вне зависимости от сигналов на входе 12,

Устройство, таким образом, ока- зьшается в нулевом состоянии и готово к измерению.

При поступлении на вход 11 измеряеного импульса сложной формы устройство включается в работу.

Выходные нап ряжения на выходе источника 1 опорного напряжения образуют амплиуудную сетку.

Un2 Urji + лЪ п, .UrJi + uUrt, ПП П(-1) + ЛУп

При достижении измеряемым импульсом значения Uf, срабатьшают все компараторы первого канала 2,1 и 4,1,1 (устанавливаются в единичное состоя- ние), при этом на их инверсном выходе устанавливаются сигналы логического нуля, а на прямом - логической единицы.

Нулевой логический сигнал с инверсного выхода компаратора 4,1,1

$Ю

5 20 25 зо

дс

0

5

0 5

192 .4

первого канала первой дополнительной I параллельной ветви устанавливает на выходе элемента ИЛИ-НЕ 5,1,1 единичный логический сигнал, в результате чего на стробирук щем входе компаратора 4,1,1 также устанавливается единичный логический сигнал, компаратор 4,1,1 переходит в режим хранения информации, и его состояние в этом режиме не зависит от величины входного измеряемого сигнала.

Срабатывание компараторов 2,1, 4,2,1, ,,, не приводит к изменению сигнала на выходе элементов ИЛИ-НЕ 3,1,1, 5,1,1,,,,, так как их выходной нулевой сигнал удерживается еди- , иичным сигналом с выхода многовходо- вых элементов И 10 1,1-10,1,р, и компараторы 2,1, 4,2,1,,, остаются в режиме сравнения.

При достижении мгновенным значением измеряемого импульса величины Up2 срабатывают все компараторы второго канала 2,2, 4,2,2,,,, и также как и в предыдущем случае компаратор 4,2,1 переходит в режим хранения информации, а компараторы 2,2 и т,д, остаются в режиме сравнения.

Единичный логический сигнал с прямого выхода компаратора 4,2,1 устанавливает на выходе элемента ИЛИ НЕ 5,1„1 нулевой логический сигнал, и в результате компаратор ,1 переходит в режим сравнения, но остается в единичном состоянии, так как на его входе действует мгновенное значение сигнала Una 7Uni.

При достижении мгновенным значением измеряемого сигнала величины U срабатывают все компараторы 2,3, .1,., третьего канала. При этом компаратор 4,3,1 переходит в режим хранения информации, а компараторы 2,3,,, остаются в режиме сравнения.

Единичный логический сигнал с прямого выхода компаратора 4,3,1 переводит компаратор 4,2,1 в режим сравнения.

При уменьшении мгновенного значения измеряемого сигнала ниже все компараторы 2,3.,, возвращаются в нулевое состояние, а компаратор 4,3,1 остается в единичном состоянии, так как находится в режиме хранения информации.

При уменьшении мгновенного значения измеряемого сигнала ниже Un компараторы 2,2, 4.2.1 и др. возвраS1259

щаются гв нулевое состояние, при этом

на обоих входах элемента И 7,2.1 присутствуют единичные логические сигналы, что приводит к появлению единичного сигнала на вьгходе элемента И 7.2.1 и перебросу в единичное io- стояние RS-триггера 8.1.1.

В результате переброса RS-триггера 8.1.1 в единичное состояние на всех торых входах элементов ИЛИ 6.2 о 1,.в т.д. появляются еди1шчные сигна-I- ы, в результате чего все компараторы 4.1.1, и т.До первой дополнительной параллельной ветви переходят в режим хранения, при этом компараторы 4.3,1 и 4,1.1 находятся в единичном состоянии, а компараторы 4.2.1, и т.д. в нулевом состоянии. Единичное состояние компаратора 4.3.1 определяет величину первого максимума измеряемого импульса.

Таким образом, измерение первого максимального значения входного импульса закончено, первая дополнительная ветвь выключена из процесса измерения и хранит информацию о величине этого первого максимального значения. Одновременно срабатывание RS-триггера 8.1.1 приводит к снятию сигнала обнуления триггеров 9.1.1 - 9.(п-1).1, При новом увеличении входного измеряемого импульса до значения 1 п2 срабатывают компараторы 2,2, 4.2.2 и т.д..

Срабатывание компаратора 4.2,2 приводит к изменению сигнала на его инверсном выходе с единицы на нуль, в результате чего триггер 9.2.1 перебрасывается в единичное состояние и нулевым сигналом со своего инверсного выхода устанавливает на выходе многовходового элемента И 10,1.1 нулевой логический сигнал.

При этом компаратор 4.2.2 переходит в режим хранения информации, так как на его стробирующем входе присутствует единичный логический сигнал. Компаратор 4 о2.1 переходит в режим сравнения, но остается в единичном состоянии.

При увеличении входного измсряе- мого импульса до величины Un срабатывают компараторы 2.3, 4.3.2 и т.До при этом компаратор 4.3,2 переходит в режим хранения информации, компараторы 2оЗ, и т.д. остаются в режиме сравнения, а компаратор 4.2.2 возвращается в режим сравнения.

o

5

0

5

0

5

Q

5

0

5

192«

В результате после окончания входного измеряемого импульса во всех дополнительных параллельных ветвях и в основной ветви будет храниться информация о мгновенном значении -всех максимумов измеряемого импульса.

Формула изобретения

Анализатор максимальных значений, содержащий основную ветвь, состоящую из п каналов, каждый из которых состоит из компаратора и элемента ИЖ- НЕ, причем неинвертирующие входы всех компараторов соединены между собой и с входом анализатора, в каждом канале инверсный выход компаратора соединен с первым входом элемента ИЛИ-НЕ, выход которого соединен со стробирую- щим входом компаратора, инвертирующие входы компараторов соединены с соответствующими выходами источника опорных напряжений, о тлич ающий- с я тем, что, с целью расширения функциональных возможностей за счет измерения максимальных значений импульсов сложной формы, он дополнительно содержит о дополнительных параллельных ветвей, причем каждая дополнительная параллельная ветвь содержит многовходовый элемент И, RS-триг- гер, выполненный на двухвходовом и многовходовом элементах ИЛИ-НЕ, и п каналов, каждый из которых содержит компаратор, элемент ИЛИ-НЕ, элемент ИЛИ, а п-1 каналов содержат дополнительный элемент И и счетный триггер в каждом канале, причем неинвертирующие входы всех компараторов объединены и подключены к входу анализатора, инвертирующий вход каждого компаратора соединен с соответствующим выходом источника опорных напряжений, инверсный выход компара™ тора каждого канала соединен с первым входом элемента ИЛИ-НЕ этого же канала, выход элемента ИЖ-НЕ каждого канала соединен с первым входом элемента ИЖ этого же канала, выход которого соединен со стробирующим входом компаратора того же канала, в каждой дополнительной параллельной ветви прямой выход компаратора каждого последующего канала соединен с первым входом элемента И и вторым входом элемента ИЛИ-НЕ предьщуп его канала, а инверсный выход компаратора каждого канала соединен с вторым входом элемента И этого же канала.

7I 259 I

выход элемента И каждого канала подключен к .S-входу RS-триггера, R-вход которого подключен к входу Сброс, инверсный выход RS-трнггера соединен с вторыми входами элементов ИЛИ всех п каналов и R-входами счетных триггеров, счетный вход каждого из которых соединен с инверсным выходом компаратора этого же канала на последующей параллельной ветви, а инверсный ю выход каждого счетного триггера в каждой дополнительной параллельной

92 .8

ветви соединен с входом многовходово- го элемента И этой же ветви, выход которого соединен с третьими входами всех элементов ИЛИ-НЕ последующей дополнительной параллельной ветви, выход многовходоного элемента И р-й дополнительной параллельной ветви соединен с вторыми входами элементов ИЛИ-НЕ основной ветви, а третьи входы элементов ИЛИ-НЕ первой дополнительной параллельной ветви подключены к входу Сброс анализатора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для цифрового анализа формы однократных электрических сигналов | 1982 |

|

SU1049832A1 |

| Устройство для измерения скорости перемещения | 1987 |

|

SU1571509A1 |

| Устройство для проверки счетчиков | 1977 |

|

SU736378A1 |

| Устройство для анализа формы однократных электрических импульсов | 1983 |

|

SU1095103A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ ПО РАДИОКАНАЛУ | 2004 |

|

RU2259017C1 |

| Матричный распределитель | 1987 |

|

SU1580377A1 |

| Измеритель коротких интервалов времени | 1980 |

|

SU920629A1 |

| Устройство для автоматического счета подвижных объектов | 1975 |

|

SU658023A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ В КАНАЛЕ МНОЖЕСТВЕННОГО ДОСТУПА | 2000 |

|

RU2179787C1 |

| Счетное устройство с предварительной уставкой кода | 1982 |

|

SU1027832A1 |

Изобретение может быть использовано в измерителях амплитуды однократных импульсов сложной формы. Цель изобретения - расширение функциональных возможностей. Устройство содержит основную и дополнительную 1 Чн1п-Ц ветви, каждая ветвь содержит П каналов 1, каждый канал которой состоит из компараторов 2 и элементов 3 ИЛИ- НЕ, а каждый канал 1 дополнительной параллельной ветви состоит иэ компаратора 4, элемента 5 ИЛИ-НЕ и элемента 6 ИЛИ; каждый из (п-1 ) каналов дополнительных параллельных ветвей содержит элемент 7 И, каждая дополнительная параллельная ветвь содержит. RS-триггер 8, счётный триггер 9 и многовходовой элемент 10 И. Расширение функциональных возможностей до- стлгается за счет введения дополнительных параллельных ветвей,позволяющих об,- еспечить измерешге всех максимальных значений импульсов сложной формы.2 ил. С Цс овчпя Stirti, l 1ч9 СП СО ю

Uni

Составитель В. Шубин Редактор В, Данко Техред А.Кравчук Корректор М. Самборская

5117/43

Тираж 728 Подписное ВНШПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Фиг. 2

| ИМПУЛЬСНЫЙ ВОЛЬТМЕТР | 1972 |

|

SU416620A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для измерения амплитуды одиночных импульсов | 1972 |

|

SU447625A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1986-09-23—Публикация

1984-07-02—Подача