Изобретение относится к электронной коммутационной технике, в частности к матричным распределителям с запоминанием программы настройки, и может быть использовано в автоматике, вычислительной технике при создании интеллектуальных ЭВМ и электронных автоматических телефонных станциях нового поколения.

Цель изобретения - упрощение и повышение производительности в результате уменьшения времени поиска для произвольного числа каналов и расширение функциональных возможностей за счет одновременной фиксации этих каналов в свободном режиме искания.

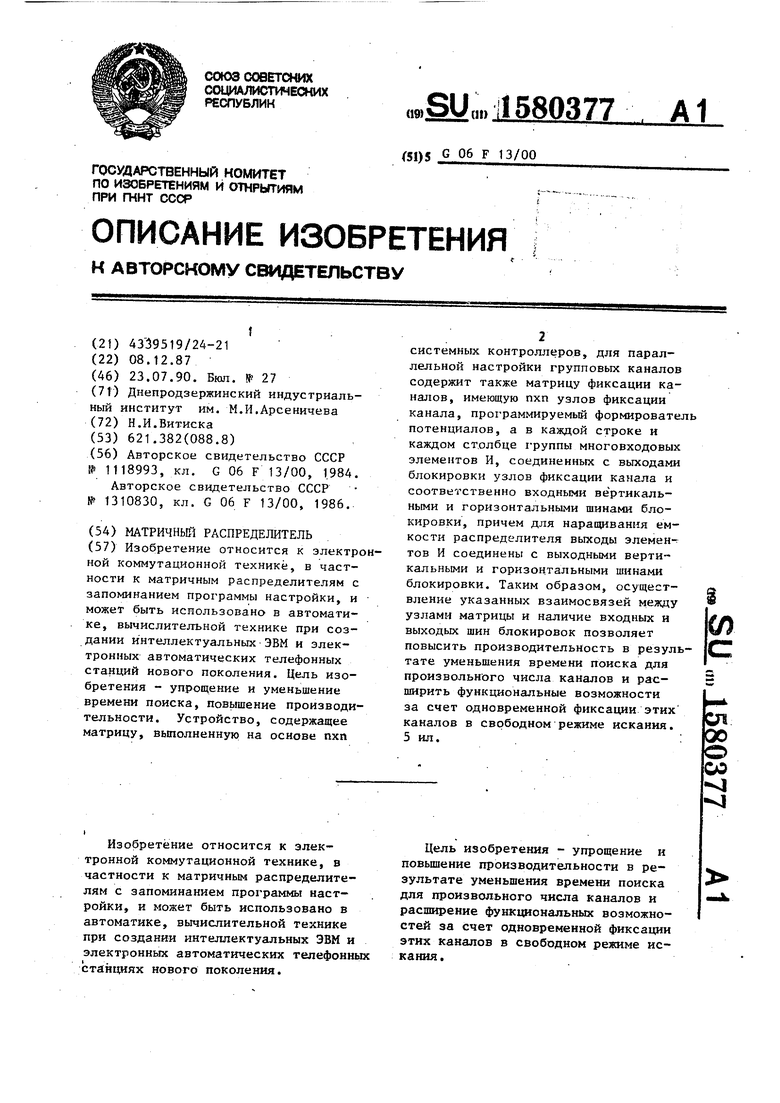

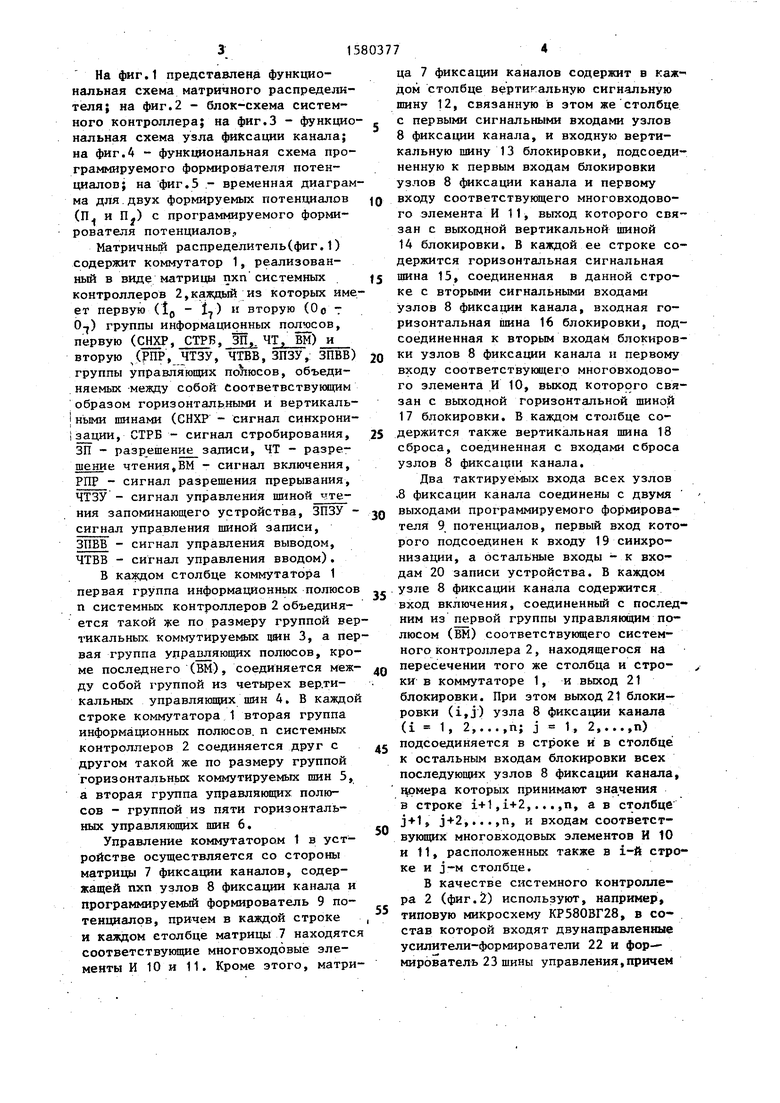

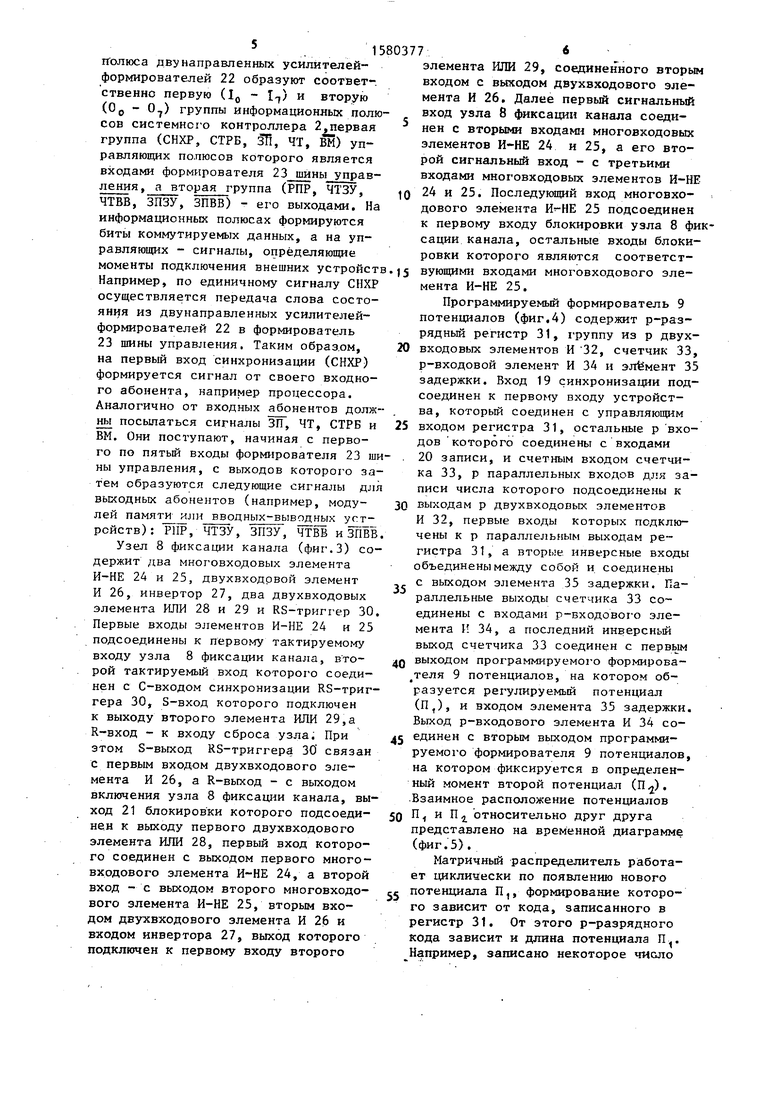

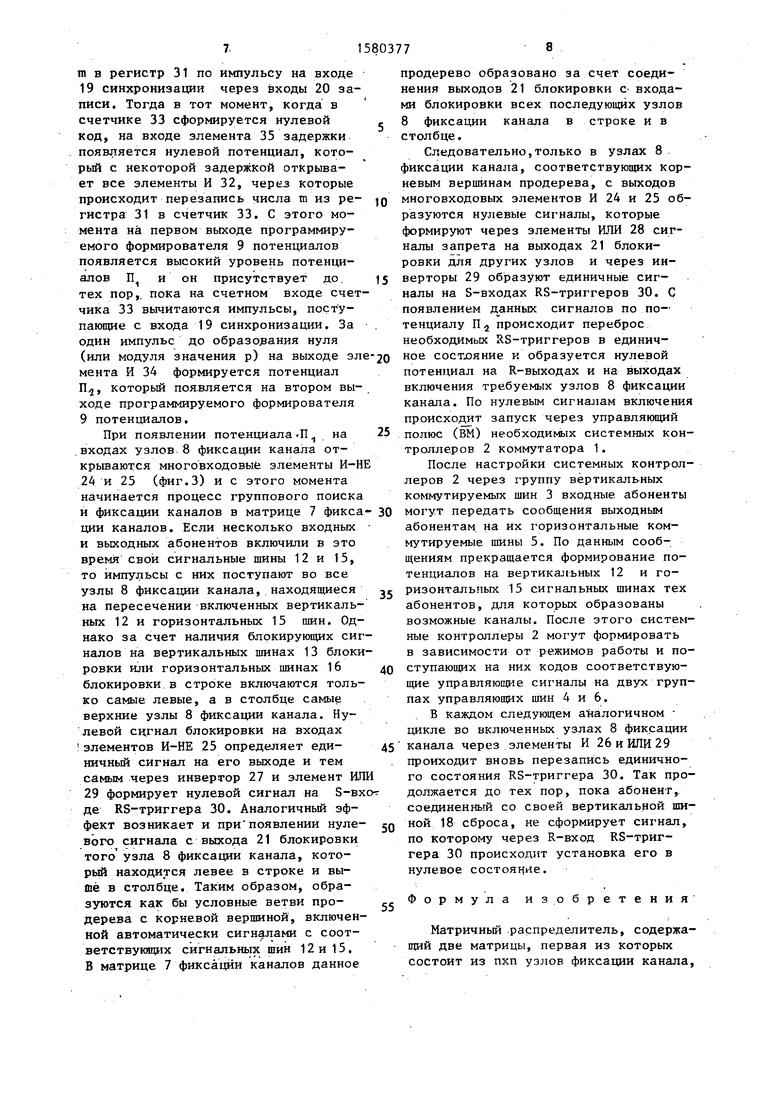

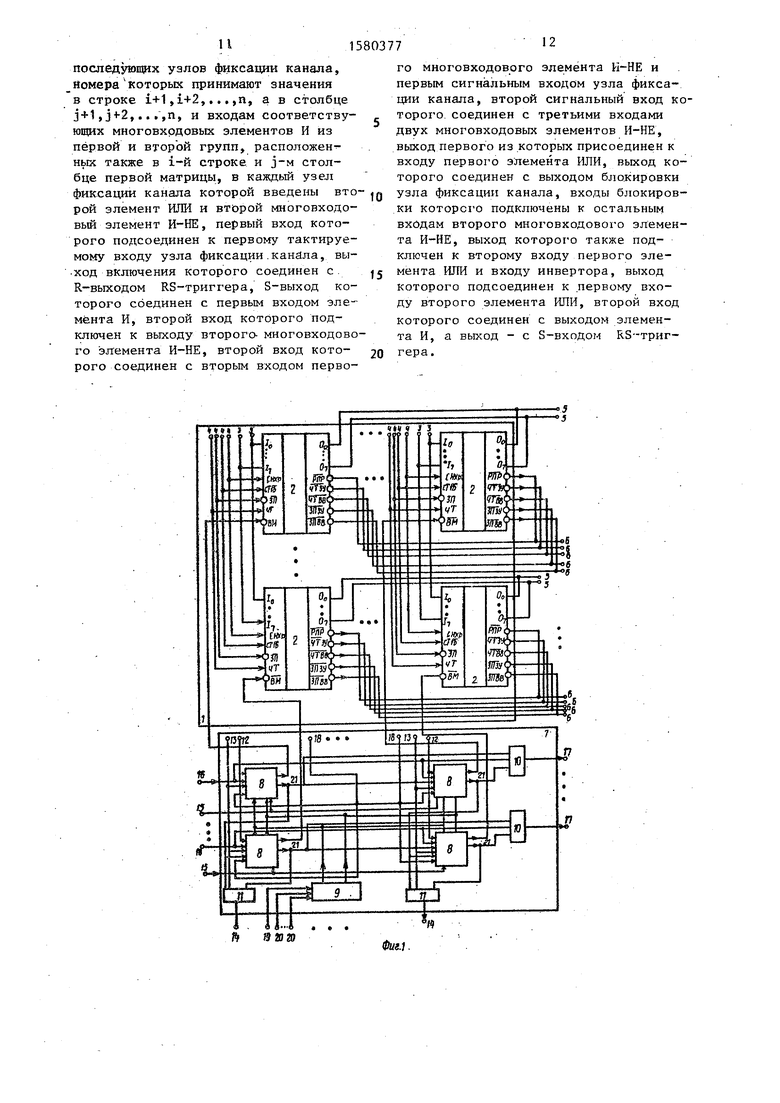

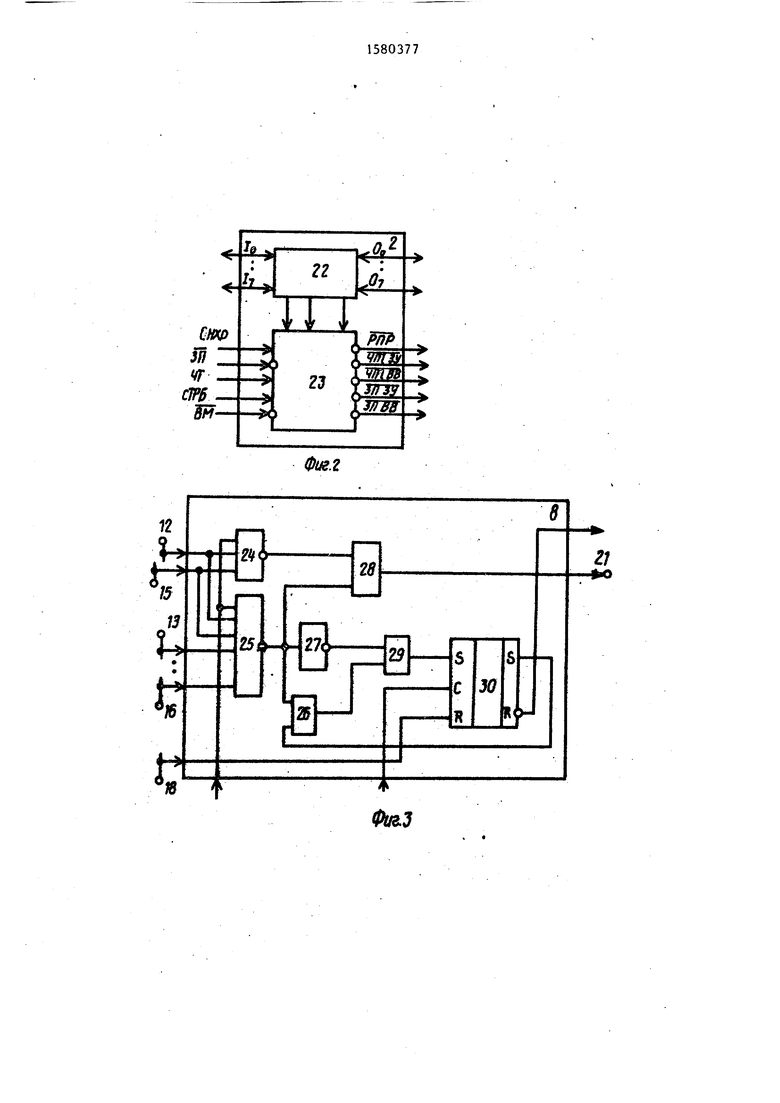

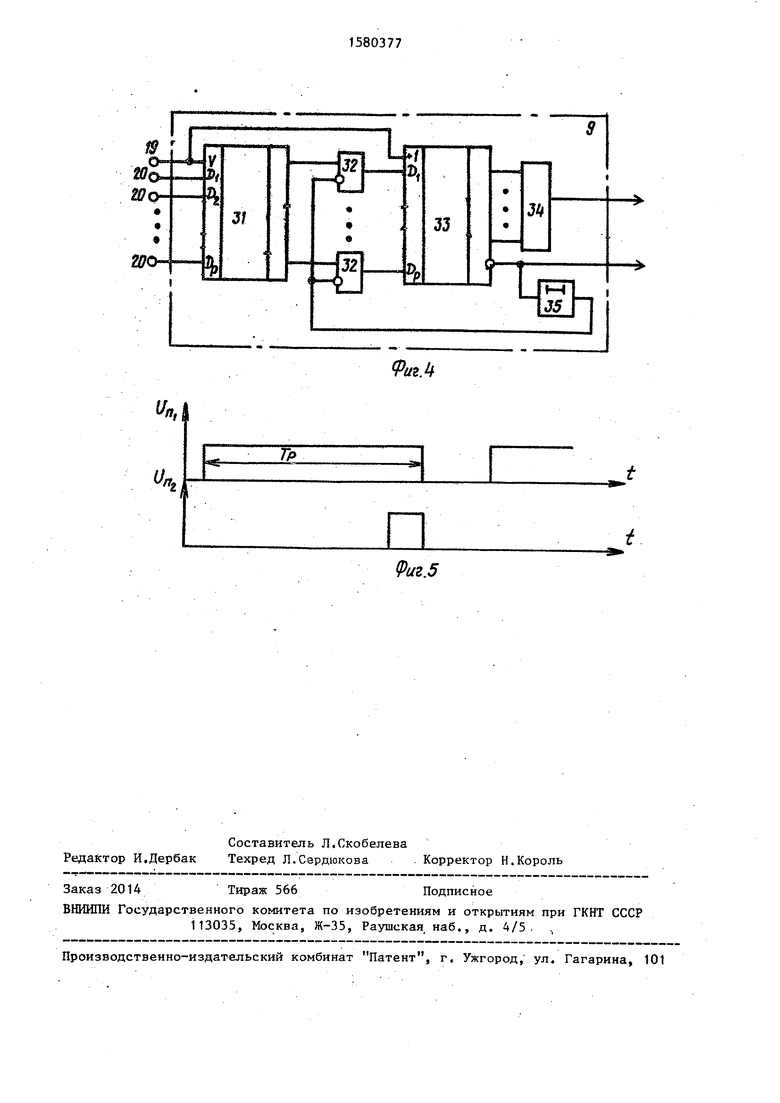

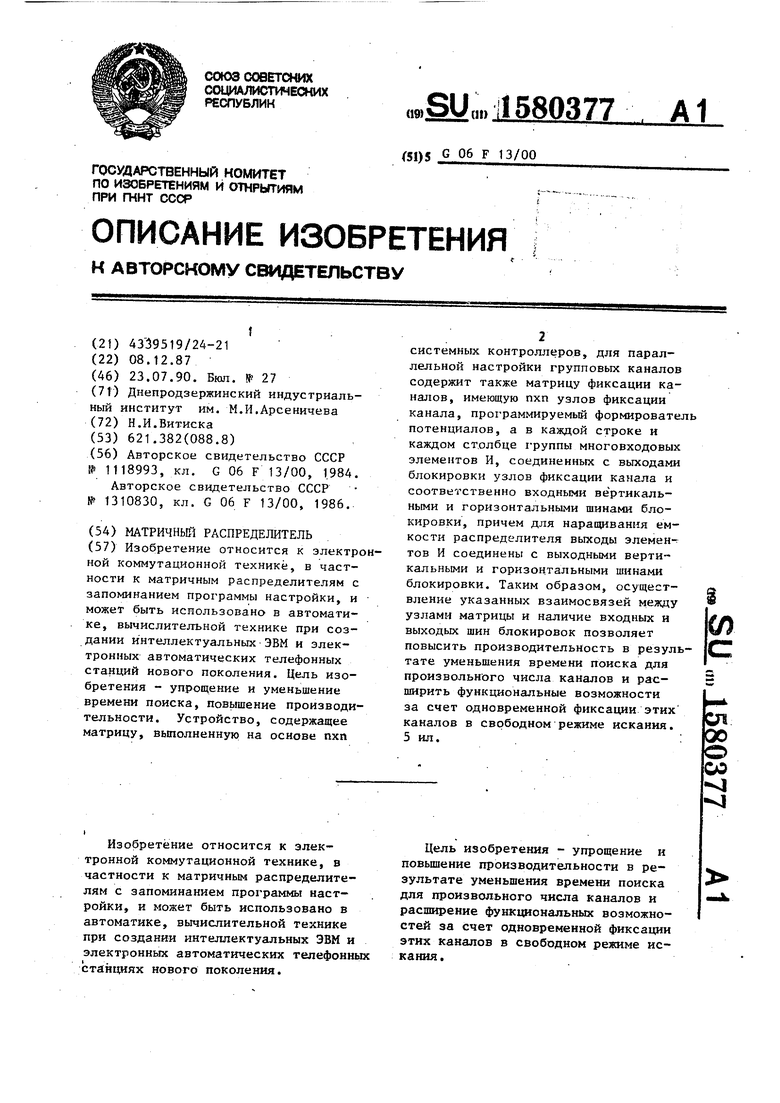

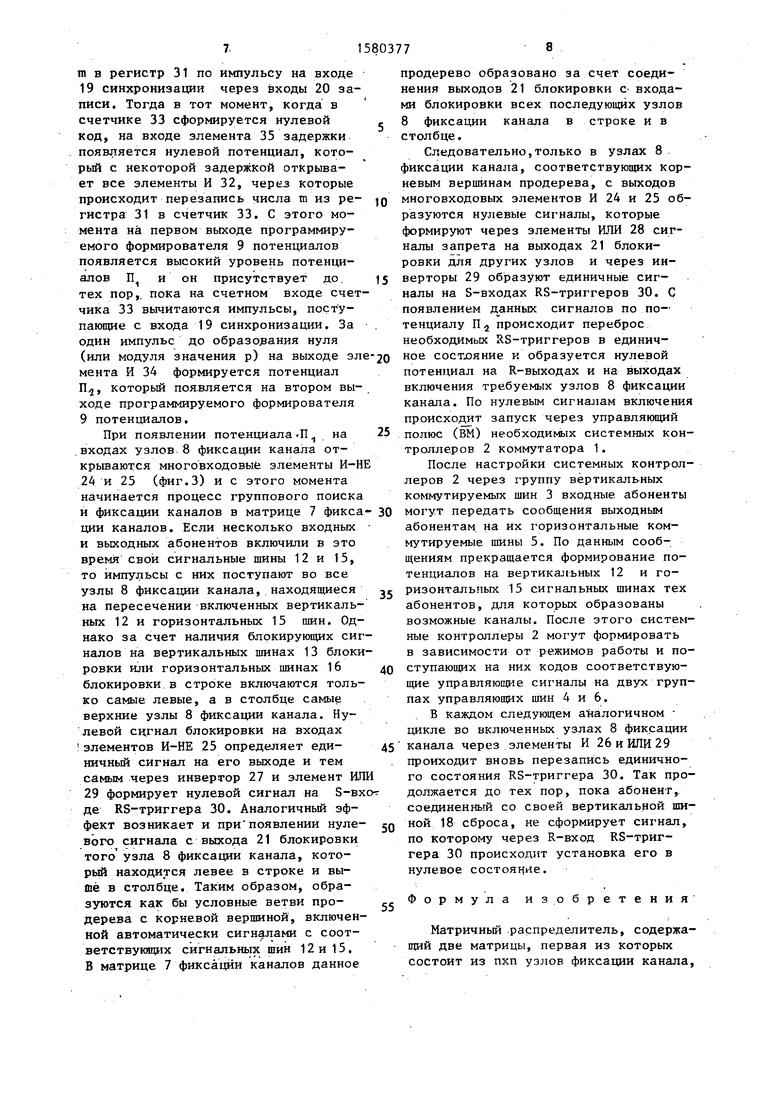

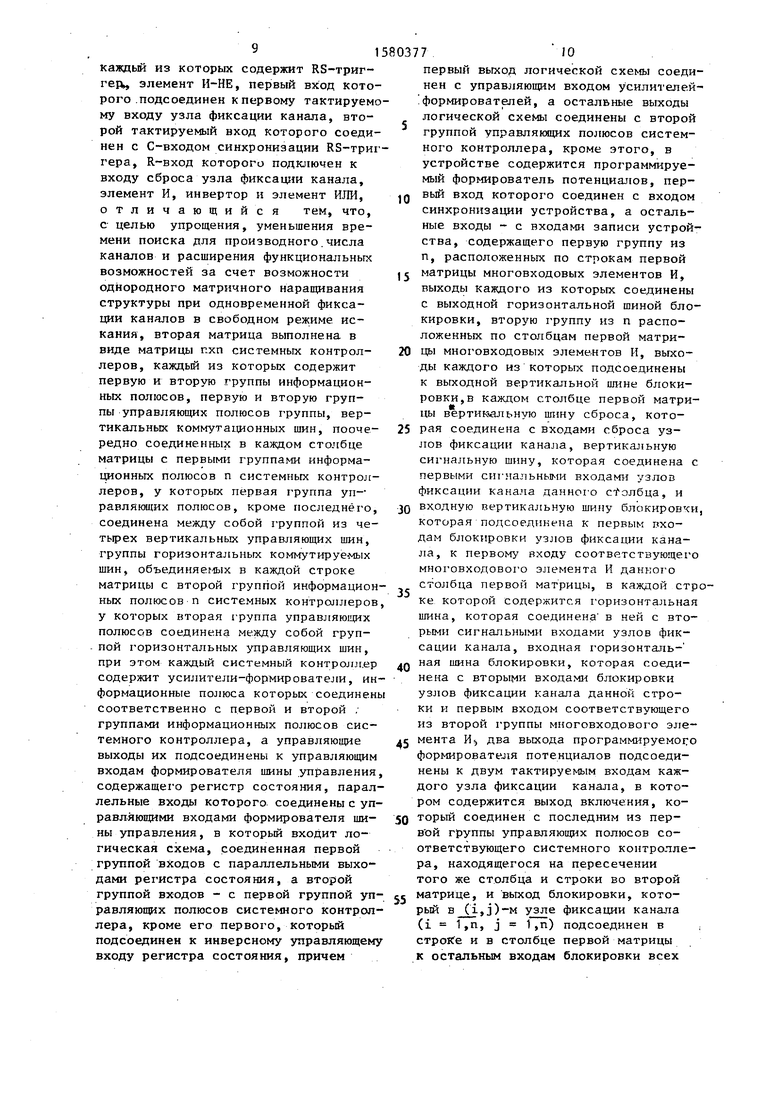

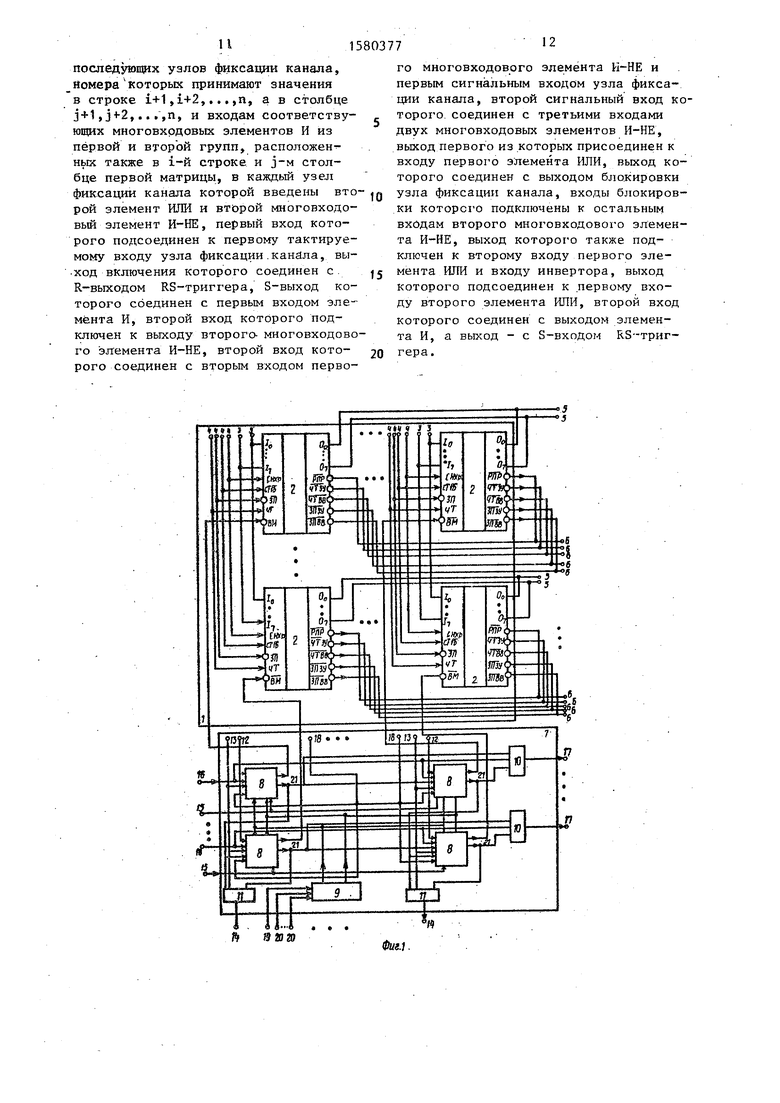

На фиг.1 представлена функциональная схема матричного распределителя; на фиг.2 - блок-схема системного контроллера; на фиг.З - функциональная схема узла фиксации канала; на фиг.4 - функциональная схема программируемого формирователя потенциалов; на фиг.З - временная диаграмма для двух формируемых потенциалов (П и Пг) с программируемого формирователя потенциалов.,

Матричный распределитель(фиг.1) содержит коммутатор 1, реализованный в виде матрицы пхп системных контроллеров 2,каждый из которых имеет первую (10 - 17) и вторую (00 т О-j) группы информационных полюсов,

первую (СНХР, СТРБ, ЗП,. ЧТ, ВМ) и

вторую л(РПР, ЧТЗУ, ЧТВВ, ЗПЗУ, ЗПВВ) группы управляющих полюсов, объединяемых между собой Соответвствующим образом горизонтальными и вертикаль- Iными шинами (СНХР - сигнал синхрони- , СТРБ - сигнал стробирования, ЗП - разрешение записи, ЧТ - разрешение чтения,ВМ - сигнал включения, РПР - сигнал разрешения прерывания, ЧТЗУ - сигнал управления шиной те- ния запоминающего устройства, ЗПЗУ - сигнал управления шиной записи, ЗПВВ - сигнал управления выводом, ЧТВВ - сигнал управления вводом).

В каждом столбце коммутатора 1 первая группа информационных полюсов п системных контроллеров 2 объединяется такой же по размеру группой вертикальных коммутируемых шин 3, а первая группа управляющих полюсов, кроме последнего (ВМ), соединяется между собой группой из четырех вер.ти- кальных управляющих шин А. В каждой строке коммутатора 1 вторая группа информационных полюсов п системных контроллеров 2 соединяется друг с другом такой же по размеру группой горизонтальных коммутируемых шин 5, а вторая группа управляющих полюсов - группой из пяти горизонтальных управляющих шин 6.

Управление коммутатором 1 в устройстве осуществляется со стороны матрицы 7 фиксации каналов, содержащей пхп узлов 8 фиксации канала и программируемый формирователь 9 потенциалов, причем в каждой строке и каждом столбце матрицы 7 находятся соответствующие многовходовые элементы И 10 и 11. Кроме этого, матри0

5

0

5

0

5

0

5

0

5

ца 7 фиксации каналов содержит в каждом столбце вертикальную сигнальную шину 12, связанную в этом же столбце с первыми сигнальными входами узлов 8 фиксации канала, и входную вертикальную шину 13 блокировки, подсоединенную к первым входам блокировки узлов 8 фиксации канала и первому входу соответствующего многовходово- го элемента И 11, выход которого связан с выходной вертикальной шиной 14 блокировки. В каждой ее строке содержится горизонтальная сигнальная шина 15, соединенная в данной строке с вторыми сигнальными входами узлов 8 фиксации канала, входная горизонтальная шина 16 блокировки, подсоединенная к вторым входам блокировки узлов 8 фиксации канала и первому входу соответствующего многовходово- го элемента И 10, выход которого связан с выходной горизонтальной шиной 17 блокировки. В каждом столбце содержится также вертикальная шина 18 сброса, соединенная с входами сброса узлов 8 фиксации канала.

Два тактируемых входа всех узлов .8 фиксации канала соединены с двумя выходами программируемого формирователя 9 потенциалов, первый вход которого подсоединен к входу 19 синхронизации, а остальные входы - к входам 20 записи устройства. В каждом узле 8 фиксации канала содержится вход включения, соединенный с последним из первой группы управляющим полюсом (ВМ) соответствующего системного контроллера 2, находящегося на пересечении того же столбца и строки в коммутаторе 1, и выход 21 блокировки. При этом выход 21 блокировки (i,j) узла 8 фиксации канала

(i 1, 2n; j 1, 2,...,п)

подсоединяется в строке и в столбце к остальным входам блокировки всех последующих узлов 8 фиксации канала, номера которых принимают значения

в строке i+1,i+2п, а в столбце

j-M, j+2,...,n, и входам соответствующих многовходовых элементов И 10 и 11, расположенных также в i-й строке и j-м столбце.

В качестве системного контроллера 2 (фиг.2) используют, например, типовую микросхему КР580ВГ28, в состав которой входят двунаправленные усилители-формирователи 22 и фор- мирователь 23 шины управления,причем

гголюса двунаправленных усилителей- формирователей 22 образуют соответственно первую (10 - 17) и вторую (00 - 07) группы информационных полюсов системного контроллера 2,первая группа (СНХР, СТРБ, ЗП, ЧТ, ВМ) управляющих попюсов которого является входами формирователя 23 шины управления, а вторая группа (РПР, ЧТЗУ, ЧТВВ, ЗПЗУ, ЗПВВ) - его выходами. На информационных полюсах формируются биты коммутируемых данных, а на управляющих - сигналы, определяющие моменты подключения внешних устройст Например, по единичному сигналу СНХР осуществляется передача слова состояния из двунаправленных усилителей- формирователей 22 в формирователь 23 шины управления. Таким образом, на первый вход синхронизации (СНХР) формируется сигнал от своего входного абонента, например процессора. Аналогично от входных абонентов должны посылаться сигналы ЗТГ, ЧТ, СТРБ и ВМ. Они поступают, начиная с первого по пятый входы формирователя 23 шны управления, с выходов которого затем образуются следующие сигналы дл выходных абонентов (например, модулей памяти или вводных-выводных устройств): Flip, ЧТЗУ, ЗПЗУ, чтвв изпвв

Узел 8 фиксации канала (фиг.З) содержит два многовходовых элемента И-НЕ 24 и 25, двухвходовой элемент И 26, инвертор 27, два двухвходовых элемента ИЛИ 28 и 29 и RS-триггер 30 Первые входы элементов И-НЕ 24 и 25 подсоединены к первому тактируемому входу узла 8 фиксации канала, второй тактируемый вход которого соединен с С-входом синхронизации RS-триг- гера 30, S-вход которого подключен к выходу второго элемента ИЛИ 29,а R-вход - к входу сброса узла. При этом S-выход RS-триггера 30 связан с первым входом двухвходового элемента И 26, а R-выход - с выходом включения узла 8 фиксации канала, выход 21 блокировки которого подсоединен к выходу первого двухвходового элемента ИЛИ 28, первый вход которого соединен с выходом первого много- входового элемента И-НЕ 24, а второй вход - с выходом второго многовходо- вого элемента И-НЕ 25, вторым входом двухвходового элемента И 26 и входом инвертора 27, выход которого подключен к первому входу второго

0

5

элемента ИЛИ 29, соединенного вторым входом с выходом двухвходового элемента И 26. Далее первый сигнальный вход узла 8 фиксации канала соединен с вторыми входами многовходовых элементов И-НЕ 24 и 25, а его второй сигнальный вход - с третьими входами многовходовых элементов И-НЕ 24 и 25. Последующий вход многовхо- дового элемента И-НЕ 25 подсоединен к первому входу блокировки узла 8 фиксации канала, остальные входы блокировки которого являются соответствующими входами многовходового элемента И-НЕ 25.

Программируемый формирователь 9 потенциалов (фиг.4) содержит р-раз- рядный регистр 31, группу из р двух0 входовых элементов И 32, счетчик 33, р-входовой элемент И 34 и элемент 35 задержки. Вход 19 синхронизации подсоединен к первому входу устройства, который соединен с управляющим входом регистра 31, остальные р входов которого соединены с входами 20 записи, и счетным входом счетчика 33, р параллельных входов для записи числа которого подсоединены к выходам р двухвходовых элементов И 32, первые входы которых подключены к р параллельным выходам регистра 31, а вторые инверсные входы объединены между собой и соединены с выходом элемента 35 задержки. Параллельные выходы счетчика 33 соединены с входами р-входового элемента И 34, а последний инверсный выход счетчика 33 соединен с первым выходом программируемого формирова- еля 9 потенциалов, на котором образуется регулируемый потенциал (П,), и входом элемента 35 задержки. Выход р-входового элемента И 34 соединен с вторым выходом программируемого формирователя 9 потенциалов, на котором фиксируется в определенный момент второй потенциал (П). Взаимное расположение потенциалов П, и П4 относительно друг друга представлено на временной диаграмме (фиг.5).

Матричный распределитель работает циклически по появлению нового

е потенциала П,, формирование которого зависит от кода, записанного в регистр 31. От этого р-разрядного кода зависит и длина потенциала П1. Например, записано некоторое число

0

5

0

5

0

m в регистр 31 по импульсу на входе 19 синхронизации через входы 20 записи. Тогда в тот момент, когда в счетчике 33 сформируется нулевой код, на входе элемента 35 задержки появляется нулевой потенциал, который с некоторой задержкой открывает все элементы И 32, через которые происходит перезапись числа m из ре- гистра 31 в счетчик 33. С этого момента на первом выходе программируемого формирователя 9 потенциалов появляется высокий уровень потенциалов П1 и он присутствует до тех пор, пока на счетном входе счетчика 33 вычитаются импульсы, поступающие с входа 19 синхронизации. За один импульс до образования нуля (или модуля значения р) на выходе эл мента И 34 формируется потенциал n.j, который появляется на втором выходе программируемого формирователя 9 потенциалов.

При появлении потенциала П1 на входах узлов 8 фиксации канала открываются многовходовые элементы И-Н 24 и 25 (фиг.З) и с этого момента начинается процесс группового поиска и фиксации каналов в матрице 7 фикса ции каналов. Если несколько входных и выходных абонентов включили в это время свои сигнальные шины 12 и 15, то импульсы с них поступают во все узлы 8 фиксации канала, находящиеся на пересечении включенных вертикальных 12 и горизонтальных 15 шин. Однако за счет наличия блокирующих сигналов на вертикальных шинах 13 блокировки или горизонтальных шинах 16 блокировки в строке включаются только самые левые, а в столбце самые верхние узлы 8 фиксации канала. Нулевой сигнал блокировки на входах 1 элементов И-НЕ 25 определяет еди- ничный сигнал на его выходе и тем самым через инвертор 27 и элемент ИЛ 29 формирует нулевой сигнал на S-вх де RS-триггера 30. Аналогичньй эффект возникает и при появлении нуле- вого сигнала с выхода 21 блокировки того узла 8 фиксации канала, который находится левее в строке и выше в столбце. Таким образом, образуются как бы условные ветви про- дерева с корневой вершиной, включенной автоматически сигналами с соответствующих сигнальных шин 12 и 15. В матрице 7 фиксации каналов данное

продерево образовано за счет соединения выходов 21 блокировки с входами блокировки всех последующих узлов 8 фиксации канала в строке и в столбце.

Следовательно,только в узлах 8 фиксации канала, соответствующих корневым вершинам продерева, с выходов многовходовых элементов И 24 и 25 образуются нулевые сигналы, которые формируют через элементы ИЛИ 28 сигналы запрета на выходах 21 блокировки для других узлов и через инверторы 29 образуют единичные сигналы на S-входах RS-триггеров 30. С появлением данных сигналов по потенциалу П происходит переброс необходимых RS-триггеров в единичное состояние и образуется нулевой потенциал на R-выходах и на выходах включения требуемых узлов 8 фиксации канала. По нулевым сигналам включения происходит запуск через управляющий полюс (ВМ) необходимых системных контроллеров 2 коммутатора 1.

После настройки системных контроллеров 2 через группу вертикальных коммутируемых шин 3 входные абоненты могут передать сообщения выходным абонентам на их горизонтальные коммутируемые шины 5. По данным сообщениям прекращается формирование потенциалов на вертикальных 12 и горизонтальных 15 сигнальных шинах тех абонентов, для которых образованы возможные каналы. После этого системные контроллеры 2 могут формировать в зависимости от режимов работы и поступающих на них кодов соответствующие управляющие сигналы на двух группах управляющих шин 4 и 6.

В каждом следующем аналогичном цикле во включенных узлах 8 фиксации канала через элементы И 26 и ИЛИ 29 проиходит вновь перезапись единичного состояния RS-триггера 30. Так продолжается до тех пор, пока абонент, соединенный со своей вертикальной шиной 18 сброса, не сформирует сигнал, по которому через R-вход RS-триггера 30 происходит установка его в нулевое состояние.

Формула изобретения

Матричный распределитель, содержащий две матрицы, первая из которых состоит из пхп узлов фиксации канала,

каждый из которых содержит RS-триг- гер, элемент И-НЕ, первый вход которого подсоединен к первому тактируемому входу узла фиксации канала, второй тактируемый вход которого соединен с С-входом синхронизации RS-триг- гера, R-вход которого подключен к входу сброса узла фиксации канала, элемент И, инвертор и элемент ИЛИ, отличающийся тем, что, с целью упрощения, уменьшения времени поиска для производного числа каналов и расширения функциональных возможностей за счет возможности однородного матричного наращивания структуры при одновременной фиксации каналов в свободном режиме искания, вторая матрица выполнена в виде матрицы пхп системных контроллеров, каждый из которых содержит первую и вторую группы информационных полюсов, первую и вторую группы управляющих полюсов группы, вертикальных коммутационных шин, поочередно соединенных в каждом столбце матрицы с первыми группами информационных полюсов п системных контроллеров, у которых первая группа уп-- равляющих полюсов, кроме последнего, соединена между собой группой из четырех вертикальных управляющих шин, группы горизонтальных коммутируемых шин, объединяемых в каждой строке матрицы с второй группой информационных полюсов п системных контроллеров, у которых вторая группа управляющих полюсов соединена между собой группой горизонтальных управляющих шин, при этом каждый системный контроллер содержит усилители-формирователи, информационные полюса которых соединены соответственно с первой и второй . группами информационных полюсов системного контроллера, а управляющие выходы их подсоединены к управляющим входам формирователя шины управления, содержащего регистр состояния, параллельные входы которого соединены с управляющими входами формирователя шины управления, в который входит логическая схема, соединенная первой группой входов с параллельными выходами регистра состояния, а второй группой входов - с первой группой управляющих полюсов системного контроллера, кроме его первого, который подсоединен к инверсному управляющему входу регистра состояния, причем

5

0

5

первый выход логической схемы соединен с управляющим входом усилителей- формирователей, а остальные выходы логической схемы соединены с второй группой управляющих полюсов системного контроллера, кроме этого, в устройстве содержится программируемый формирователь потенциалов, первый вход которого соединен с входом синхронизации устройства, а остальные входы - с входами записи устройства, содержащего первую группу из п, расположенных по строкам первой матрицы многовходовых элементов И, выходы каждого из которых соединены с выходной горизонтальной шиной блокировки, вторую группу из п расположенных по столбцам первой матрицы многовходовых элементов И, выходы каждого из которых подсоединены к выходной вертикальной шине блокировки, в каждом столбце первой матрицы вертикальную шину сброса, которая соединена с входами сброса узлов фиксации канала, вертикальную сигнальную шину, которая соединена с первыми cm нальными входами узлов фиксации канача даннсч о столбца, и Q входную вертикальную шину блокировки, которая подсоединена к первым лхо- дам блокировки узлов фиксации канала, к первому входу соответствующего многовходового элемента И данного столбца первой матрицы, в каждой строке которой содержится горизонтальная шина, которая соединена в ней с вторыми сигнальными входами узлов фиксации канала, входная горизонталь- ная шина блокировки, которая соединена с вторыми входами блокировки узлов фиксации канала данной строки и первым входом соответствующего из второй группы многовходового элемента И два выхода программируемого формирователя потенциалов подсоединены к двум тактируемым входам каждого узла фиксации канала, в котором содержится выход включения, который соединен с последним из первой группы управляющих полюсов соответствующего системного контроллера, находящегося на пересечении того же столбца и строки во второй матрице, и выход блокировки, который в (i,j)-M узле фиксации канала (i 1,n, j 1,п) подсоединен в строке и в столбце первой матрицы к остальным входам блокировки всех

5

0

5

0

5

последующих узлов фиксации канала, номера которых принимают значения в строке i+1, i+2,...,п, а в столбце j+1,j+2,...,n, и входам соответствующих многовходовых элементов И из первой и второй групп, расположенных также в 1-й строке и j-м столбце первой матрицы, в каждый узел фиксации канала которой введены второй элемент ИЛИ и второй многовходо- вый элемент И-НЕ, первый вход которого подсоединен к первому тактируемому входу узла фиксации канала, выход включения которого соединен с R-выходом КЗ-триггера, S-выход которого соединен с первым входом элемента И, второй вход которого подключен к выходу второго- многовходово го элемента И-НЕ, второй вход кото- рого соединен с вторым входом перво

0

5

го многовходоврго элемента И-НЕ и первым сигнальным входом узла фиксации канала, второй сигнальный вход которого соединен с третьими входами двух многовходовых элементов И-НЕ, выход первого из которых присоединен к входу первого элемента ИЛИ, выход которого соединен с выходом блокировки узла фиксации канала, входы блокировки которого подключены к остальным входам второго многовходового элемента И-НЕ, выход которого также подключен к второму входу первого элемента ИЛИ и входу инвертора, выход которого подсоединен к первому входу второго элемента ИЛИ, второй вход которого соединен с выходом элемента И, а выход - с S-входом RS-триг- гера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Модуль многокаскадной коммутационной системы | 1990 |

|

SU1793443A1 |

| Матричный коммутатор | 1987 |

|

SU1499364A1 |

| Устройство для исследования путей в графах | 1981 |

|

SU1005066A2 |

| Устройство для формирования и анализа семантических сетей | 1989 |

|

SU1619289A1 |

| АВТОМАТИЗИРОВАННАЯ РЕЗЕРВИРОВАННАЯ СИСТЕМА УПРАВЛЕНИЯ ЗАПРАВКОЙ КРИОГЕННОГО РАЗГОННОГО БЛОКА | 1995 |

|

RU2084011C1 |

| Устройство для управления динамической памятью | 1987 |

|

SU1524089A1 |

| УСТРОЙСТВО СЧИТЫВАНИЯ НА ПРИБОРАХ С ЗАРЯДОВОЙ СВЯЗЬЮ ДЛЯ ДВУХМЕРНЫХ ПРИЕМНИКОВ ИЗОБРАЖЕНИЯ | 2002 |

|

RU2239915C2 |

| Устройство поиска степени оптимальности размещения в кластерных многопроцессорных системах | 2022 |

|

RU2791419C1 |

| Устройство для ввода дискретных сигналов в электронную вычислительную машину | 1990 |

|

SU1791808A1 |

| Устройство для контроля состояния объектов | 1986 |

|

SU1368902A1 |

Изобретение относится к электронной коммутационной технике, в частности к матричным распределителям с запоминанием программы настройки, и может быть использовано в автоматике, вычислительной технике при создании интеллектуальных ЭВМ и электронных автоматических телефонных станций нового поколения. Цель изобретения - упрощение и уменьшение времени поиска, повышение производительности. Устройство, содержащее матрицу, выполненную на основе NXN системных контроллеров, для параллельной настройки групповых каналов содержит также матрицу фиксации каналов, имеющую NXN узлов фиксации канала, программируемый формирователь потенциалов,а в каждой строке и каждом столбце группы многовходовых элементов И, соединенных с выходами блокировки узлов фиксации канала и соответственно входными вертикальными и горизонтальными шинами блокировки, причем для наращивания емкости распределителя выходы элементов И соединены с выходными вертикальными и гозиронтальными шинами блокировки. Таким образом, осуществление указанных взаимосвязей между узлами матрицы и наличие входных и выходных шин блокировок позволяет повысить производительность в результате уменьшения времени поиска для произвольного числа каналов и расширить функциональные возможности за счет одновременной фиксации этих каналов в свободном режиме искания. 5 ил.

ft

Фиг,;

Фи&З

Редактор И.Дербак

Составитель Л.Скобелева

Техред Л.Сердюкова Корректор Н.Король

Заказ 2014

Тираж 566

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5 ,

Производственно-издательский комбинат Патент, г. Ужгород, ул. Гагарина, 101

Фиг Л

Фиг.5

Подписное

| Устройство для сопряжения | 1983 |

|

SU1118993A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения группы из М вычислительных машин с группой из К абонентов | 1986 |

|

SU1310830A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-07-23—Публикация

1987-12-08—Подача