Изобретение относится к автоматике и вычислительной технике и предназначено для использования в системах экспресс-обработки измерителей информации.

Целью изобретения является расширение функциональных возможностей путем определения автокорреляционной функции порядковых статистик.

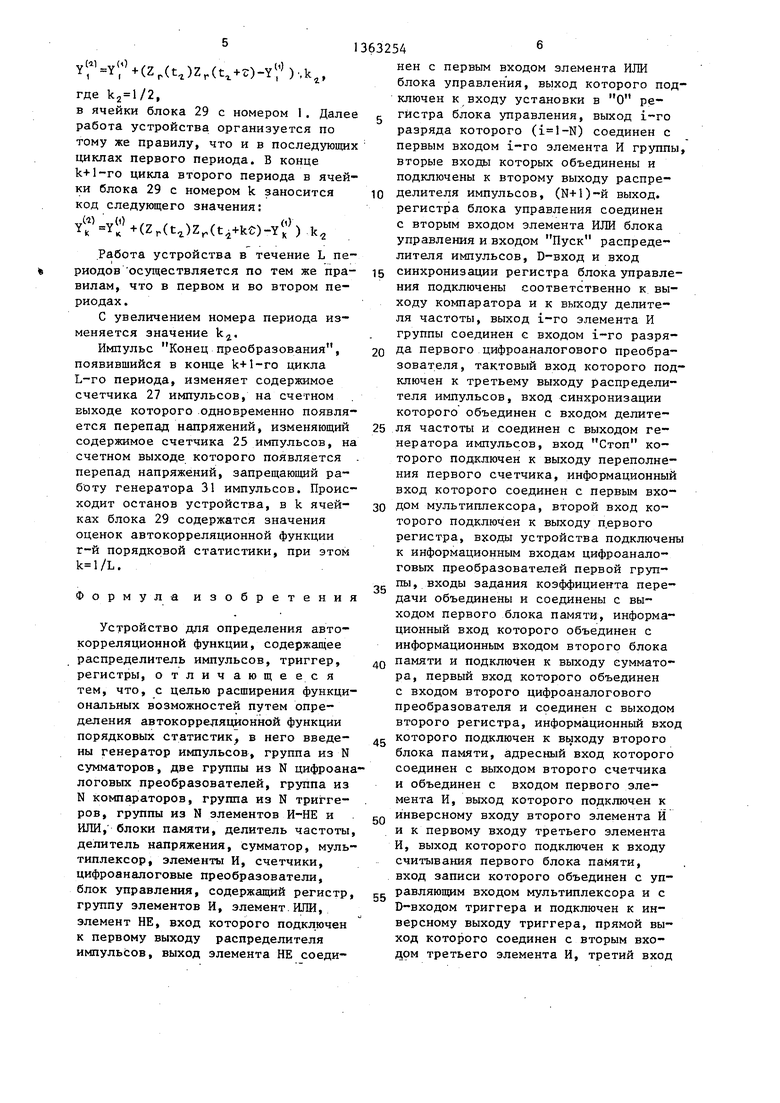

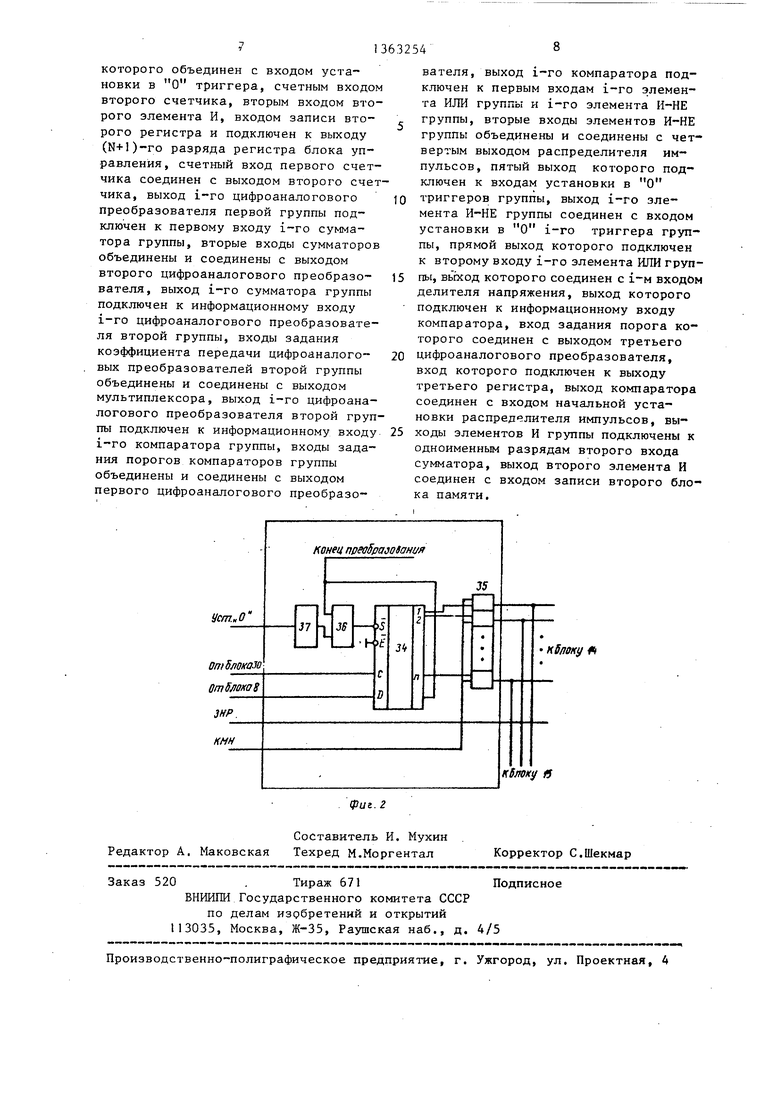

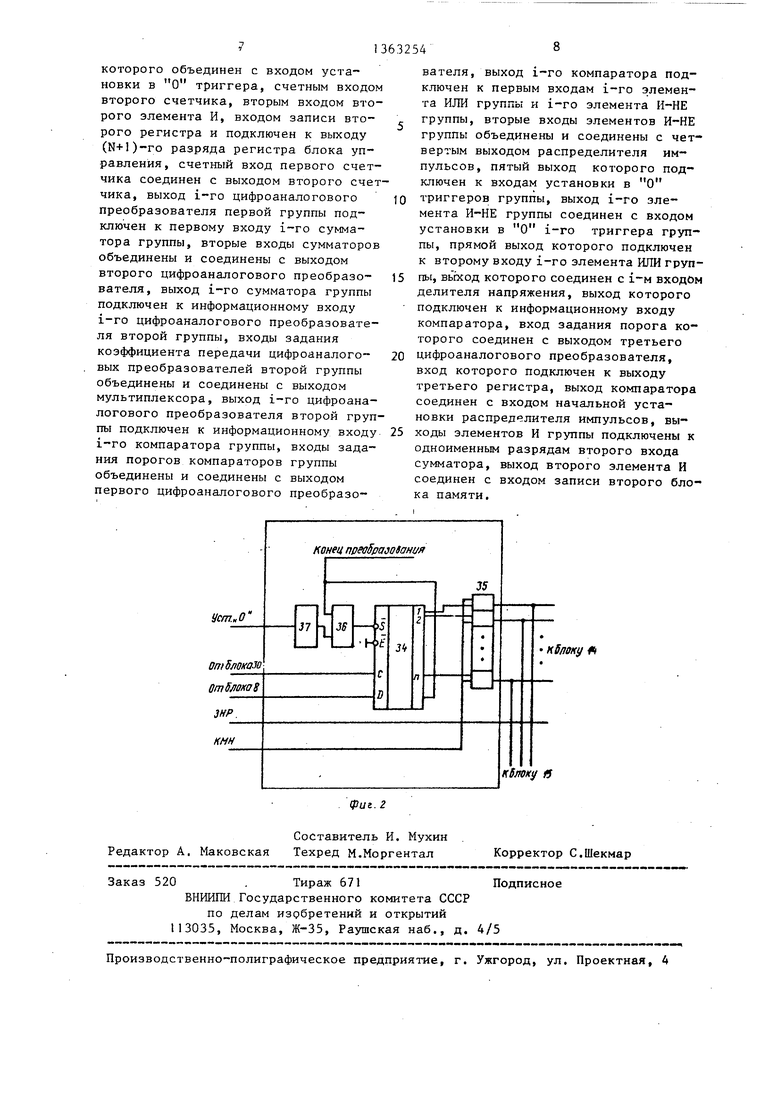

На фиг. 1 представлена блок-схема предлагаемого устройства; на фиг, 2 - блок-схема блока управления.

Устройство (фиг. 1) содержит группу цифроаналоговых преобразователей 1, группу сумматоров 2, группу цифро- аналоговых преобразователей 3, группу компараторов 4, группу элементов управления и входом Пуск распреде- элементов ИЛИ 7, блок 8 сравнения, содержащий делитель 9 напряжения, цифроаналоговый преобразователь 10 и компаратор 11; блок 12 уравновешивания, содержащий блок 13 управления и цифроаналоговый преобразователь 14, Кроме того, устройство содержит сумматор 15, цифроаналоговый преобразователь 16, регистры 17-19, триггер 20, мультиплексор 21, элементы 22-25, счетчик 25, распределитель 26 импульсов, счетчик 27, блоки 28,29 памяти, делитель 30 частоты, генератор 31 импульсов, выходы 32,33 устройства.

выходные коды счетчика 25 импульсов и регистра 17 одинаковы;

счетчик 27 импульсов обнулен; на выходе логического элемента ,И 24 установлен уровень логического нуля;

на цифровом выходе устройства и выходе регистра 18 установлен код, JO соответствующий нулевому напряжению на аналоговом выходе 32 устройства. Устройство начинает свою работу с запуска генератора 31 импульсов. I период. В первом цикле этого 15 периода измеряется текущее значение г-й порядковой статистики Zf,(t). В конце первого цикла импульс Конец преобразования устанавливает на Q-вьгходе D-триггера 20 потенциал 20 логической единицы. При этом на выходе мультиплексора 21 устанавливается выходной код счетчика 25 импульсов, соответствующий единичному коэффициенту передачи цифроаналоговых 25 преобразователей 3; блок 28 памяти переводится в режим записи информации с выхода сумматора 15 iiо адресу, определяемому потенциалом Q-выхода D-триггера 20 (например, в ячейки с 30 номером адреса 2).

По заднему фронту импульса Конец преобразования изменяется на единицу содержимое счетчика 27 импульсов. После этого изменяется потенциал

Блок 12 управления (фиг. 2) содер-35 выходе логического элемента И 24,

жит регистр 34, группу элементов

И 35, элемент ИЛИ 36, элемент НЕ 37.

Устройство работает следукяцим образом.

запрещающий прохождение импульсов с выхода логического элемента И, 22 на вход установки режима блока 28 памяти. Блок памяти устанавливается в 40 режим считывания информации. На

Перед началом работы блоки устройства находятся в следующем состоянии

распределитель 26 содержит программу своей работы в течение одного цикла;

на Q-выходе D-триггера 20 - потенциал логической единицы;

ячейки блока 29 памяти обнулены;

блоки 28 и 29 находятся в режиме считывания информации; .

на выходе блока 28 - код, соответствующий единичному коэффициенту передачи умножающих цифроаналоговых преобразователей 1;

выходной код регистра 17, определяющий единичный коэффициент передачи умножающих цифроаналоговых преобразователей 3, установлен на выходе мультиплексора 21;

выходные коды счетчика 25 импульсов и регистра 17 одинаковы;

счетчик 27 импульсов обнулен; на выходе логического элемента ,И 24 установлен уровень логического нуля;

на цифровом выходе устройства и выходе регистра 18 установлен код, соответствующий нулевому напряжению на аналоговом выходе 32 устройства. Устройство начинает свою работу с запуска генератора 31 импульсов. I период. В первом цикле этого периода измеряется текущее значение г-й порядковой статистики Zf,(t). В конце первого цикла импульс Конец преобразования устанавливает на Q-вьгходе D-триггера 20 потенциал логической единицы. При этом на выходе мультиплексора 21 устанавливается выходной код счетчика 25 импульсов, соответствующий единичному коэффициенту передачи цифроаналоговых преобразователей 3; блок 28 памяти переводится в режим записи информации с выхода сумматора 15 iiо адресу, определяемому потенциалом Q-выхода D-триггера 20 (например, в ячейки с номером адреса 2).

По заднему фронту импульса Конец преобразования изменяется на единицу содержимое счетчика 27 импульсов. После этого изменяется потенциал

выходе логического элемента И 24,

запрещающий прохождение импульсов с выхода логического элемента И, 22 на вход установки режима блока 28 памяти. Блок памяти устанавливается в режим считывания информации. На

цифровых входах цифроаналоговых преобразователей 1 установлен код значения г-й порядковой статистики Z(t), По заднему фронту импульса Конец преобразования с некоторой задержкой осуществляется запись данных () из блока 29 в регистр 18 (например, из ячеек с адресом 1). Напряжение на выходе цифроаналого- вого преобразователя 16 равно нулю. На Q-выходе D-триггера 20 потенциал логической единицы сохраняется в течение k циклов первого периода. Блок 28 находится в режиме считывания информации в течение этих циклов.

После прекращения действия импульса Конец преобразования начинается второй цикл.

В конце второго цикла по переднему фронту импульса Конец преобразования осуществляется запись выходного кода сумматора 15:

.( 1

г (о)

YV Y7+ Z,(t,)Z(t,+0),

где Zp(t), Zp(t;+ o) - значения r-й

порядковой статистики в моменты времени t и t, +t, в ячейки блока 29 памяти с номером 1

По заднему фронту импульса Конец преобразования изменяется на единицу содержимое счетчика 27 импульсов; блок 29 устанавливается в режим считывания информации из ячеек с номером 2; с некоторой задержкой производится запись данных ( 0) в регистр 18 из блока 29. Далее на 1ина- ется третий цикл.

Работа устройства в третьим и в течение последующих k-2 циклов происходит так же, как и во втором . В конце k+1-го цикла работы устройства в момент появления импульса Конец преобразования выходной код сумматора 15 соответствует значению

.W

(о

., Z,(t,)Z(t,+k)+Y ° .

Этот код по переднему фронту импульса Конец преобразования заносится в блок 29 в ячейки с адресом k

В этом же цикле по заднему фронту импульса Конец преобразования изменяется на единицу содержимое счетчика 27 импульсов, на счетном выходе которого появляется перепад напряжений, изменяющий на единицу содержимое счетчика 25 импульсов. На выходе логического элемента И 24 появляется потенциал логического нуля, запрещающий изменение режима работы блока 29 (блок 29 переводится в режим считывания информации- из ячеек с адресным номером 0), но раз- решающий изменение режима работы блок 28 памяти. Под воздействием перепада выходного напряжения логического элемента на Q-выходе D-триг- гера 20 устанавливается потенциал логического нуля. По заднему фронту импульса Конец преобразования с некоторой временной задержкой происходит запись данньпс из ячеек блока 29 памяти с адресом О в регистр 18. В это время на выходе мультиплексо

10

15

20

25

30

35

40

45

50

5

ра 21 устанавливается код регистра 17, соответствующий единичному коэффициенту передачи умножающих цифро- аналоговых преобразователей 3 (). Такой же код устанавливается на выходе блока 28, работающего в режиме считывания информации из ячеек с адресом 1. Напряжение на выходе 32 устройства равно нулю. На цифровом выходе 33 устройства устанавливается выходной код регистра 18. Указанная выше ситуация k+1-го цикла имеет место в конце первого периода.

it период. Так как на цифровых входах цифроаналоговых преобразователей 3 и 1 установлены коды, соответствующие единичному коэффициенту передачи, то в первом цикле второго (а также любого из L периодов работы системы) периода измеряется значение г-й порядковой статистики ). При появлении импульса Конец преобразования на Q-выходе D-тригге- ра 20 устанавливается потенциал логической единицы. Блок 28 переводится в режим записи информации с выхода сумматора 15 в ячейки с адресом 2. На выходе мультиплексора 21 устанавливается код, соответствующий состоянию счетчика 25, соответствующий коэффициенту передачи цифроана- логовых преобразователей 3 (). Это значение поддерживается, как и код значения Zp(t), неизменным в течение периода.

По заднему фронту импульса Конец преобразования изменяется на единицу содержимое счётчика 27 импульсов. После этого изменяется потенциал на выходе логического элемента И 24, запрещающий прохождение импульсов с выхода логического элемента И 22 на вход установки режима блока 28. Блок 28 устанавливается в режим считывания информации из ячеек-с адресом 2. По заднему фронту импульса Конец преобр азования с некоторой временной задержкой осуществляется запись данных (Y ) из ячеек блока 29 с номером адреса I в регистр 18. На выходе цифроаналогового преобразователя 16 устанавливается выходное напряжение, значение которого соответствует Y, . В конце второго цикла по переднему фронту импульса Конец преобразования осуществляется запись выходного кода сумматора 15, соответствующего значению

с)

+(z,(t)z()-Y; ).k

4

где ,

в ячейки блока 29 с номером 1. Далее работа устройства организуется по тому же правилу, что и в последующих циклах первого периода. В конце k+1-го цикла второго периода в ячейки блока 29 с номером k заносится код следующего значения:

k

yi;4(ZXt),+kC)-Yf)

k к Vt-гЧ -7. к

Работа устройства в течение L периодов осуществляется по тем же правилам, что в первом и во втором периодах .

С увеличением номера периода изменяется значение k.

Импульс Конец преобразования, появившийся в конце k+1-го цикла L-ro периода, изменяет содержимое счетчика 27 импульсов, на счетном выходе которого .одновременно появляется перепад напряжений, изменяющий содержимое счетчика 25 импульсов, на счетном выходе которого появляется перепад напряжений, запрещающий работу генератора 31 импульсов. Происходит останов устройства, в k ячейках блока 29 содержатся значения оценок автокорреляционной функции г-й порядковой статистики, при этом .

Формула изобретения

Устройство для определения автокорреляционной функции, содержащее распределитель импульсов, триггер, регистры, отличающееся тем, что, с целью расщирения функциональных возможностей путем определения автокорреля1щонной функции порядковых статистик, в него введены генератор импульсов, группа из N сумматоров, две группы из N цифроана логовых преобразователей, группа из N компараторов, группа из N триггеров, группы из N злементов И-НЕ и ИЛИ, блоки памяти, делитель частоты, делитель напряжения, сумматор, мультиплексор, элементы И, счетчики, цифроаналоговые преобразователи, блок управления, содержащий регистр, группу злементов И, элемент.ИЛИ, элемент НЕ, вход которого подключен к первому выходу распределителя импульсов, выход элемента НЕ соеди .

10

15

20

25

-

363254

йен с первым входом элемента ИЛИ блока управления, выход которого подключен к входу установки в О регистра блока управления, выход i-ro разряда которого () соединен с первым входом i-ro элемента И группы, вторые входы которых объединены и подключены к второму выходу распределителя импульсов, (Н+1)-й выход, регистра блока управления соединен с вторым входом элемента ИЛИ блока управления и входом Пуск распределителя импульсов, D-вход и вход синхронизации регистра блока управления подключены соответственно к выходу компаратора и к выходу делителя частоты, выход i-ro элемента И группы соединен с входом i-ro разряда первого цифроаналогового преобразователя, тактовый вход которого подключен к третьему выходу распределителя импульсов, вход синхронизации которого объединен с входом делителя частоты и соединен с выходом генератора импульсов, вход Стоп которого подключен к выходу переполнения первого счетчика, информационный вход которого соединен с первым входом мультиплексора, второй вход которого подключен к выходу первого регистра, входы устройства подключены к информационным входам цифроанало- говых преобразователей первой группы, входы задания коэффициента передачи объединены и соединены с выходом первого блока памяти, информационный вход которого объединен с информационным входом второго блока памяти и подключен к выходу сумматора, первый вход которого объединен с входом второго цифроаналогового преобразователя и соединен с выходом второго регистра, информационный вход которого подключен к выходу второго блока памяти, адресный вход которого соединен с выходом второго счетчика и объединен с входом первого элемента И, выход которого подключен к инверсному входу второго элемента И и к первому входу третьего элемента И, выход которого подключен к входу считывания первого блока памяти, вход записи которого объединен с управляющим входом мультиплексора и с D-входом триггера и подключен к инверсному выходу триггера, прямой выход которого соединен с вторым входом третьего элемента И, третий вход

30

35

40

45

50

55

которого объединен с входом установки в О триггера, счетным входом второго счетчика, вторым входом второго элемента И, входом записи второго регистра и подключен к выходу (N+1)-го разряда регистра блока управления, счетный вход первого счетчика соединен с выходом второго счетчика, выход i-ro цифроаналогового преобразователя первой группы подключен к первому входу i-ro сумматора группы, вторые входы сумматоров объединены и соединены с выходом второго цифроаналогового преобразователя, выход i-ro сумматора группы подключен к информационному входу i-ro цифроаналогового преобразователя второй группы, входы задания коэффициента передачи цифроаналого- вых преобразователей второй группы объединены и соединены с выходом мультиплексора, выход i-ro цифроаналогового преобразователя второй группы подключен к информационному входу i-ro компаратора группы, входы задания порогов компараторов группы объединены и соединены с выходом первого цифроаналогового преобразоконец прго5ра о1ания

Уст.,0

37

JS

ОтЬлоках

QmSjiaxoS

(риг. г

Составитель И. Мухин Редактор А, Маковская Техред М.Моргентал

Заказ 520 . Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

вателя, выход i-ro компаратора подключен к первым входам i-ro элемента ИЖ группы и i-ro элемента И-НЕ группы, вторые входы элементов И-НЕ группы объединены и соединены с четвертым выходом распределителя импульсов, пятый выход которого подключен к входам установки в О

0 триггеров группы, выход i-ro элемента И-НЕ группы соединен с входом установки в О i-ro триггера группы, прямой выход которого подключен к второму входу i-ro элемента ИЛИ груп5 пы, вьгкод которого соединен с i-м входом делителя напряжения, выход которого подключен к информационному входу компаратора, вход задания порога которого соединен с выходом третьего

0 цифроаналогового преобразователя, вход которого подключен к выходу третьего регистра, выход компаратора соединен с входом начальной установки распределителя импульсов, вы-

5 ходы элементов И группы подключены к одноименным разрядам второго входа сумматора, выход второго элемента И соединен с входом записи второго блока памяти.

J

кВлоку л

к бшу б

Корректор С.Шекмар

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения корреляционной функции | 1984 |

|

SU1363255A1 |

| Устройство для определения среднего значения выборочного размаха | 1984 |

|

SU1363252A1 |

| Устройство кодирования и декодирования сигналов звукового вещания | 1987 |

|

SU1711331A1 |

| Устройство для регистрации информации | 1985 |

|

SU1304170A1 |

| Цифроаналоговый генератор телевизионного сигнала | 1989 |

|

SU1654978A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Устройство для определения функций плотности вероятностей | 1984 |

|

SU1363253A1 |

| Цифроаналоговый преобразователь с автокалибровкой | 1989 |

|

SU1683176A1 |

| Устройство для регистрации информации | 1989 |

|

SU1698895A1 |

| СТЕНД ДЛЯ ИЗУЧЕНИЯ ЭЛЕКТРОННЫХ СРЕДСТВ АВТОМАТИЗАЦИИ | 2005 |

|

RU2279718C1 |

Изобретение относится к системам экспресс-обработки измерительной информации. Целью изобретения является расширение функциональных возможностей путем определения автокорреляционной функции для порядковых статистик. Цель достигается за счет упорядочивания ансамбля входных величин и реализации рекурсивньпс алгоритмов. Для зтого в устройство введены группа цифроаналоговых преобразователей 13, две группы компараторов 2,4, элементы И-НЕ 5, триггеры 6, элементы ИЛИ .7, блок сравнения 8, блок уравновешивания 12, сумматор 15, цифроаналоговый преобразователь -16, регистры 17-19, счетчики 25 27, делитель частоты 30, генератор импульсов 31, распределитель импульсов 26, элементы И 22-24, блоки памяти 28,29. 2 ил. с fB ел со о оо ю СП 4;

| 0 |

|

SU326557A1 | |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| МНОГОКАНАЛЬНЫЙ ЦИФРОВОЙ КОРРЕЛЯТОР | 0 |

|

SU337784A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-12-30—Публикация

1984-10-29—Подача