(З) УСТРОЙСТВО ДЛЯ ЦИФРОВОГО

ФУНКЦИОНАЛЬНОГО ПРЕОБРАЗОВАНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Функциональный преобразователь | 1981 |

|

SU960836A1 |

| Функциональный преобразователь | 1983 |

|

SU1115069A1 |

| Цифровой функциональный преобразователь | 1981 |

|

SU960837A1 |

| Цифровой функциональный преобразователь | 1983 |

|

SU1098006A1 |

| Устройство для цифрового функционального преобразования | 1981 |

|

SU993271A1 |

| Функциональный преобразователь | 1981 |

|

SU1018127A1 |

| Функциональный преобразователь | 1985 |

|

SU1249547A1 |

| Функциональный преобразователь | 1982 |

|

SU1037272A1 |

| Функциональный преобразователь двух переменных | 1984 |

|

SU1168964A1 |

| Функциональный преобразователь | 1984 |

|

SU1211756A1 |

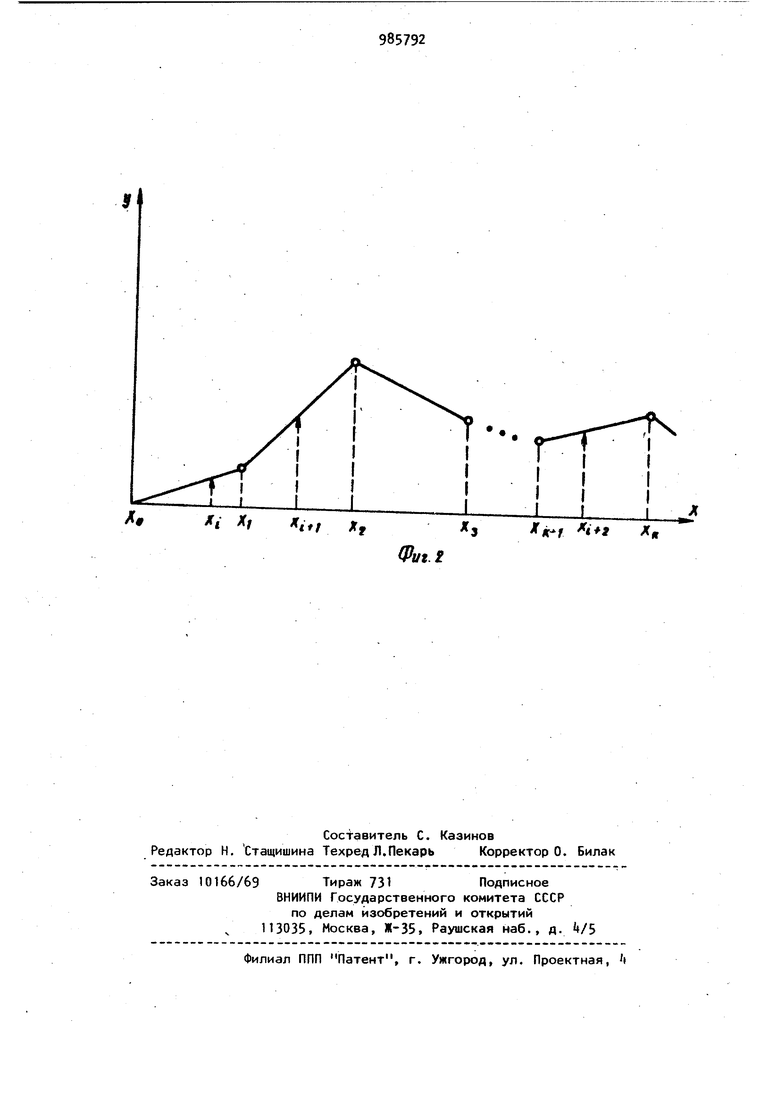

Изобретение относится к автомати-, ке и вычислительной технике и может найти применение для кусочно-линейного функционального преобразования циф ровых сигналов. Известен цифровой функциональный преобразователь, содержащий формирователь кода аргумента, блок сравнения кодов, блок вычитания кодов, множительный блок, блоки памяти, коммутаторы и выходной сумматор С1 . Известен также цифровой функциональный преобразователь, содержащий блок формирования кода номера отрезка, дешифратор, блоки памяти, генератор импульсов, элемент запрета, группу элементов И, счетчики, блоки сравнения кодов и выходной реверсивный счетчик С2 . Общим недостатком известных преобpaзoвateлeй является ограниченный диапазон скорости изменения аргумента. Наиболее близким к предлагаемому является устройство для цифрового функционального преобразования, содержащее входной регистр, подключенный информационными входами к шинам ввода агрумента, первый реверсивный счетчик, выходы которого соединены с выходами устройства и с первой группой входов первого блока вычитания кодов, подключенного старшим разрядом второй группы входов к выходу старшего разряда блока памяти, выходом знака разности - к входу управления реверсом первого реверсивного счетчика, выходами кода разности - к управляющим входам управляемого делителя час тоты, а выходом обнуления - к входу стробирования управляемого деления частоты и к первому входу первого элемента И, соединенного вторым входом с выходом генератора импульсов, а выходом - с сигнальным входом управляемого делителя частоты, выход которого подключен к счетному входу первого реверсивного счетчика, причем выходы входного регистра через дешифратор адреса соединены с входами блока памяти, подключенного выходами младших разрядов к младшим разрядам второй группы входов первого блока вычитания кодов, соединенного выходом обнуления с управляющим входом входного регистра 3 . Недостатками прототипа являются ограниченный диапазон скорости изменения аргумента и пониженная динамическая точность преобразования, так как для нормальной работы устройства необходимо ограничивать крутизну изменения аргумента функции для исключения пропусков участков аппроксимации при воспроизведении функции. Цель изобретения - расширение диапазона скорости изменения аргумента и повышение динамической точности пре образования. Поставленная цель достигается тем что в устройство для цифрового функционального преобразования, содержащее входной регистр, подключенный информационными входами к шинам ввода аргумента, первый реверсивный счетчик выходы которого соединены с выходами устройства и с первой группой входов первого блока вычитания кодов, подключенного старшим разрядом второй группы входов к выходу старшего разряда блока памяти, выходом знака разности - к входу управления реверсом первого реверсивного счетчика, выходами кода разности - к управляющим входам управляемого делителя частоты а выходом обнуления - к входу стробирования управляемого делителя частоты и к первому входу первого элемента И соединенного вторым входом с выходом генератора импульсов, а выходом - с сигнальным входом управляемого делите ля частоты, выход которого подключен к счетному входу первого реверсивного счетчика, дополнительно введены второй блок вычитания кодов, второй реверсивный счетчик, группа компараторов, группа регистров опорных кодов второй элемент И, триггер, элемент за держки, группа элементов И и сумматор соединенный первой группой входов с выходами входного регистра, младшим разрядом второй группы входов - с выходом триггера, а выходами - с первой группой входов второго блока вычитаНИИ кодов, подключенного второй группой входов к выходам второго реверсив ного счетчика и к адресным входам бло ка памяти, выходами кода разности - к первым группам входов компараторов группы, выходом обнуления - к первому входу второго элемента И и к стробирующим входам компараторов, а выходом знака разности - к входу управления реверсом второго реверсивного счетчика и к установочному входу триггера, соединенного входом обнуления с управляющим входом входного регистра и с выходом второго элемента И, подключенного вторым входом к выходу обнуления первого блока вычитания кодов и через элемент задержки к счетному входу второго реверсивного счетчика, причем выходы регистров опорных кодов соединег ны соответственно с вторыми группами входов компараторов группы, подключенных выходами к входам управления коэффициентом пересчета первого реверсивного счетчика и к первым входам элементов И группы, соединенных вторыми входами с выходами младших разрядов блока памяти, а выходами с младшими разрядами второй группы входов первого блока вычитания кодов. На фиг. 1 изображена блок-схема устройства для цифрового функционального преобразования; на фиг. 2 - график воспроизводимой функции, поясняющий работу устройства. Устройство (фиг. 1) содержит первый реверсивный счетчик 1, выходы которого соединены с выходами устройства и с первой группой входов первого блока 2 вычитания кодов. Блок 2 подключен старшим разрядом второй группы входов к выходу старшего разряда блока 3 памяти, выходом А кода разности - к управляющим входам управляемого делителя 5 частоты, выходом 6 знака разности - к входу управления реверсом реверсивного счетчика 1, а выходом 7 обнуления - к входу стробирования делителя 5 частоты и к первому входу первого элемента И 8. Элемент И 8 соединен вторым входом с выходом генератора 9 импульсов, а выходом - с сигнальным входом делителя 5, выход которого подключен к счетному входу счетчика 1. Входной регистр 10 соединен информационными входами с шинами 11 ввода аргумента, а выходамис первой группой входов сумматора 12. Сумматор 12 соединен младшим разрядом второй группы входов с выходом триггера 13, а выходами - с первой группой входов второго блока Н вычитания кодов. Блок k подключен второи группой входов к выходам второго реверсивного счетчика 15 и к адресным входам блока 3 памяти, выходами 16 ко да разности - к первым группам входов компараторов 17, выходом 18 обнуления - к первому входу второго элемента И 19 и к стробирующим входам компараторов, а выходом 20 знака разности - к входу управления реверсом счет чика 15 и к установочному входу триггера 13. Триггер 13 соединен входом обнуления с управляющим входом входного регистра 10: и с выходом элемента И 19 подключенного вторым входом к выходу 7 обнуления блока 2 вычитания кодов и через элемент 21 задержки к счетному входу счетчика 15. Выходы регистров 22 опорных кодов соединены соответственно с вторыми группами вхо дов компараторов 7, подключенных выходами к входам управления коэ(|н})ициентом пересчета счетчика 1 и к первым входам эле;ментов И 23 группы, соединенных вторыми входами с выходами младших разрядов блока 3 памяти, а выходами - с младшими разрядами второй группы входов блока 2 вычитания кодов. Устройство работает следующим образом.. В блок 3 памяти заносятся ординаты узловых точек функции преобразоваIния f(хц),где , 1, 2,..., причем в первую ячейку заносится нулевой код По выходному коду реверсивного счетчика 15, разрядность которого определяется количеством узловых точек, хра нимых в блоке 3, находится код узловой точки соответствующего значения функции преобразования. G помощьюбло ка 2 вычитания кодов и управляемого делителя 5 автоматически устанавливается коэффициент наклона аппроксимирующих отрезков. В блоке 14 вычитания кодов, определяется разность между поступившим и предыдущим значениями аргумента. Полученная разность поступает на входы компараторов 17, где сравнивается с соответствующими опорными кодами регистров 22. По срабатыванию соответствующих компараторов устанавливается коэффициент пересчета разности счетчика 1 и разрядность второй группы входов блока 2 вычитания, определяющая дискретность воспроизведения функ ции в зависимости от скорости изменения (крутизны) аргумента, В случае поступления в регистр 10 аргумента х значение которого находится между узловыми, точками аппроксимации, триггер 13 выдает единицу на младший разряд второй группы входов сумматора 12 при возрастании аргумента и нуль - при убывании аргумента, что необходимо для установления в блоке 14 вычитания кодов значения аргумента, к которому осуществляется интерполяция. Элемент 21 задержки задерживает передний фронт сигнала совпадения кодов с шлхода 7 блока 2, поступающий на очередной вход счетчика 15, на время вычисления блоком 14 кода разности. В регистры 22 опорных кодов заносятся соответствующие коды, превышение которых характеризует пропуск определенного числа участков аппроксимации. В исходном состоянии счетчики 1 и 15, регистр 10 и триггер 13 обнулены и нулевой код с выходов счетчика 15 поступает на адресные входы блока 3 памяти. При этом нулевой код f(xo) из первой ячейки блока 3 поступает в блок 2 вычитания, вырабатыващий разность кодов с выходов блока 3 и счетчика 1. Передний фронт сигнала совпаде««1Я с выхода 7 блока 2 поступает на вход элемента И 8, закрывая его на время установки коэффициента деления, на вход стробирования делителя 5 частоты, разрешая установку в делителе 5 коэффициента деления, через элемент 21 задержки на вход счетчика 15, переводя его в следующее состояние, и на второй вход И 19« На -первый вход элемента.И 19 поступает передний 1|фонт сигнала совпадения с выхода 18 блока 14, в результате чего элемент И 19 открывается, разрешая передачу кода следующего значения аргумента во входной регистр 10, и переключая триггер 13 в единичное состояние Рассмотрим работу устройства при поступлении на его входы аргумента различной крутизны (фиг. 2). При поступлении на входы регистра 10 кода блоком первого значения аргумента х, 14 вычисляется разность кодов сумматора 12 и счетчика 15, которая не превышает порогов срабатывания компараторов 17 Таким образом, разрядность счетчика 1 не Изменяется и ни один из элементов И 23 не заперт. По коду счетчика 15 осуществляется выборка узловой точки соответствующего значёния функции на первом участке аппро798ксимации, которая поступает из блока 3 памяти на входы блока 2, формирующего разность кодов f(x) и fCx). Эта разность поступает с выходов 4 блока 2 на управляющие входы делителя 5 частоты, в котором устанавливается соответствующий коэффициент деления. После прихода на вторую группу входов блока 2 значения функции f(x) на выходе 7 блока 2 вырабатывается задний фронт сигнала обнуления, задержанный на время, необходимое для установки коэффициента деления делите ля 5 частоты. По заднему фронту сигнала с выхода 7 блока 2 открывается элемент И 8 и импульсы с выхода генератора 9 поступают через делитель 5 частоты на счётный вход счетчика 1. Таким образом, выполняется линейная интерполяция функции на выбранном интервале аппроксимации. Формируемый в счетчике 1 выходной код устройства при необходимости может быть преобразован в аналоговый сигнал соответствующим цифро-аналоговым преобразователем. При совпадении кода счетчика 1 и кода f(x) на выходе 7 обнуления блока 2 фоомиоуется очередной импульсный сигнал совпадения, по которому Элемент И 8 закрывается. По сигналам совпадения с выхода 18 обнуления блока k и выхода 7 обнуления блока 2 элементом И 19 выдается разрешение на считывание в регистр 10 кода следую(фиг. 2) значения аргуменщего х. та. Передний фронт сигнала совпадения с выхода 7 блока 2, задержанный элементом 21 задержки на время, необходимое для формирования на выходах 16 кода разности блока 14, переводит счетчик 13 в следующее состояние. Счетчик 15 осуществляет выборку соответствующего значения функции f(x2) из блока 3 памяти. В блоке 2 формируется разность кодов f(x2) и f(x), поступающая на управляющие входы делителя 5 частоты и устанавливающая коэффициент передачи на очередном участ ке аппроксимации. Задним фронтом импульса совпадения с выхода 7 блока 2 элемент И 8 открывается и начинается линейная интерполяция второго участка функции. По совпадению кода счетчика 1 и кода f(х„) блока 3 памяти на выходе 7 блока 2 формируется очередной импульс ный сигнал, по (оторому элемент И 8 закрывается, счетчик 15 переходит в 2 следующее состояние и через элемент И 19 Дается разрешение на считывание в регистр 10 очередного значения аргумента. При поступлении в регистр 10 кода аргумента (фиг, 2) в блоке И формируется разность кодов между значениями сумматора 12 и счетчика 15, поступающая по заднему фронту сигнала с выхода 18 обнуления блока 14 на входы компараторов 17. При этом сработают компараторы, у которых входное значение превысит пороговое (задаваемое регистрами 22 опорных кодов), устанавливают необходимую разрядность счетчика 1 и блокируют соответствующие выходы младших разрядов блока 3 памяти через элементы И 23. Таким образом, увеличивается дискретность шага интерполяции, что позволяет выполнить интерполяцию последрвательно на всех участках аппроксимации между значениями аргумента 2 и Xj, (фиг. 2) с более высокой скоростью, определяемой крутизной изменения аргумента. По коду счетчика 15 осуществляется выборка соответствующего значения функции f(xj) из блока 3 памяти. В блоке 2 формируется разность кодов f{x. и (хп) поступающая на управляющие входы делителя 5 частоты и устанавливающая коэффициент передачи на очередном участке аппроксимации. Задним фронтом импульса совпадения с выхода 7 блока 2 элемента И 8 открывается и начинается линейная интерполяция третьего участка функции. Воспроизведение участков аппроксимации продолжается до момента достижения счетчиком 15 кода, содержащегося в сумматоре 12. При совпадении кодов счетчика 15 и сумматора 12 на выходе 18 обнуления блока 14 формируется импульс и по совпадению его с импульсным сигналом с выхода 7 блока 3 через элемент И 19 выдается разрешение на считывание в регистр 10 очередного значения аргумента. На последующих участках аппроксимации, устройство работает аналогично вышеописанному, При изменении знака крутизны функЦИИ разность между сбседними значениями узловых точек функции изменяет знак и признак знака крутизны с выхода 6 блока 2 управляет реверсом счетчика 1. При изменении знака крутизны аргумента разность кодов счетчика 15 и сумматора 12 также изменяет знак и признак этого знака с выхода 20 блока управляет реверсом счетчика и состоянием триггера 13Таким образом, предлагаемое устройство по сравнению с прототипом позволяет воспроизводить функции в более широком диапазоне скоростей изменения аргумента и с меньшей динамической ошибкой преобразователя, что определяется возможностью изменения дис кретности шага применения воспроизво- го димой функции в зависимости от крутизны аргумента, приводящей к изменению времени воспроизведения участков и позволяющей воспроизводить промежуточные участки аппроксимации. Формула изобретения Устройство для цифрового функционального преобразования содержащее входной регистр, подключенный информационными входами к шинам ввода аргумента, первый реверсивный счетчик, выходы которого соединены с выходами устройства и с первой группой входов первого блока вычитания кодов, подключенного старшим разрядом второй группы входов к выходу старшего разряда блока памяти, выходом знака piL3.ности - к входу управления реверсом первого реверсивного счетчика, выходами кода разности - к управляющим входам управляемого делителя частоты. а выходом обнуления - к входу строби-з5 рования управляемого делителя частоты и к первому входу первого элемента И, соединенного вторым входом с выходом генератора импульсов, а выходом - с сигнальным входом управляемо-40 го делителя частоты, выход которого подключен к счетному входу первого реверсивного счетчика, отличающееся тем, что, с целью расширения диапазона скорости изменения ар- 45

гумента и повышения динамической точности преобразования, в устройство дведены второй блок вычитания кодов. 88 15

Авторы

Даты

1982-12-30—Публикация

1981-07-13—Подача