Изобретение относится к телемеханике и может быть использовано в автоматизированных системах контроля и управления многопараметрическими объектами, а также в средствах программного опроса каналов с автоматическим выбором порядка опроса.

Цель изобретения - упрощение и повышение быстродействия.

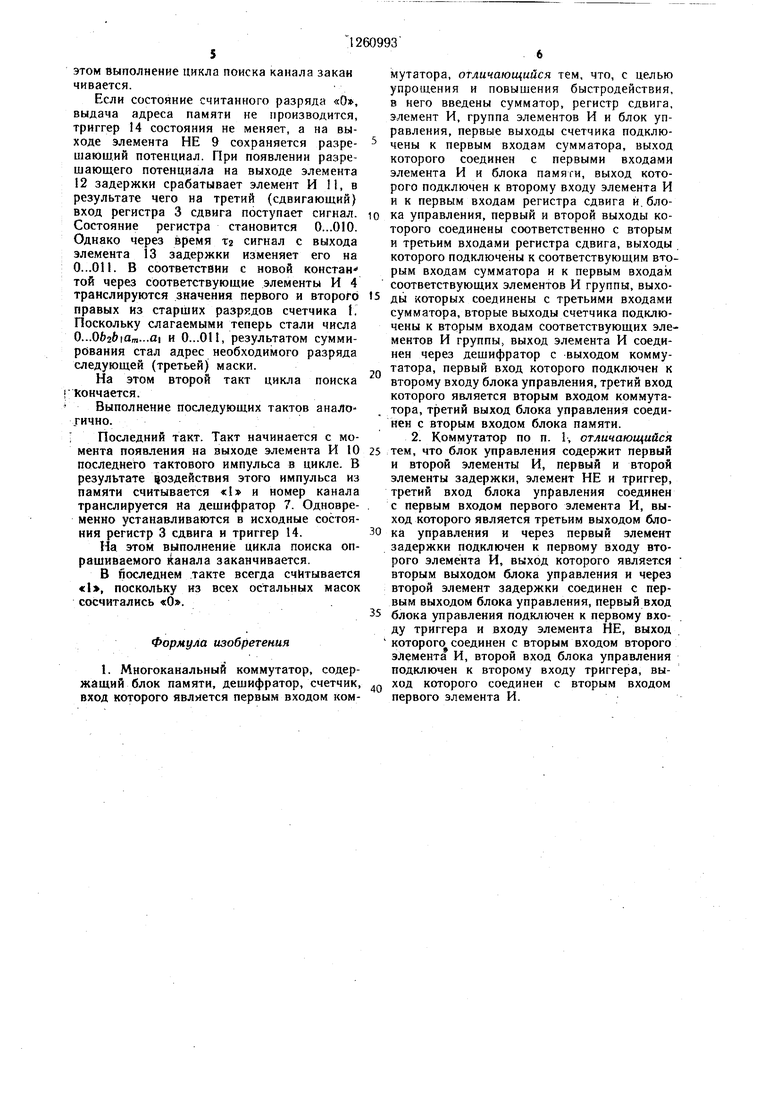

На фиг. 1 представлен полный кадр информации и подкадры с различной часгде «Ь означает наличие канала, «О - отсутствие. На фиг. 2а применительно к каналам кадра фиг. 1 представлены маски для подкадров всех частот опроса. Если маски разместить так, как показано на S фиг. 26 и спроецировать их на позиции кадра, то каждой позиции будет соответствовать только одна «1 в какой-либо одной маске. Если затем разряды всех масок пронумеровать в возрастающем порядке

тотой опроса; на фиг. 2а - коды масок JQ (фиг. 2в), а сами маски рассматривать как

для подкадров всех частей опроса; на фиг. 26 - план размещения масок в кадре; на фиг. 2в - нумерация разрядов масок; на фиг. За - таблица соответствия позиции кадра и номеров опрашиваемых каисходные данные для программного коммутатора, то поиск опрашиваемого канала для каждой позиции кадра будет заключаться в последовательном просмотре разрядов масок соответствующих этой позиции. При обнаруналов; на фиг. 36 - таблица кодирования 15 жении в какой-либо маске «1 опращива- разрядов масок; на фиг. 4 - таблица ется канал с номером, равным номеру дан- разрядов на

20

ного разряда. На фиг. За показано соотношение позиции кадра и номеров опрашиваемых каналов для исходных данных фиг. 2в. Если теперь маски зафиксировать в одноразрядной памяти (фиг. 36), то последовательный просмотр соответствующих разрядов будет осуществляться в порядке считывания по адресам согласно фиг. 4.

Счетчик 1 предназначен для фиксации

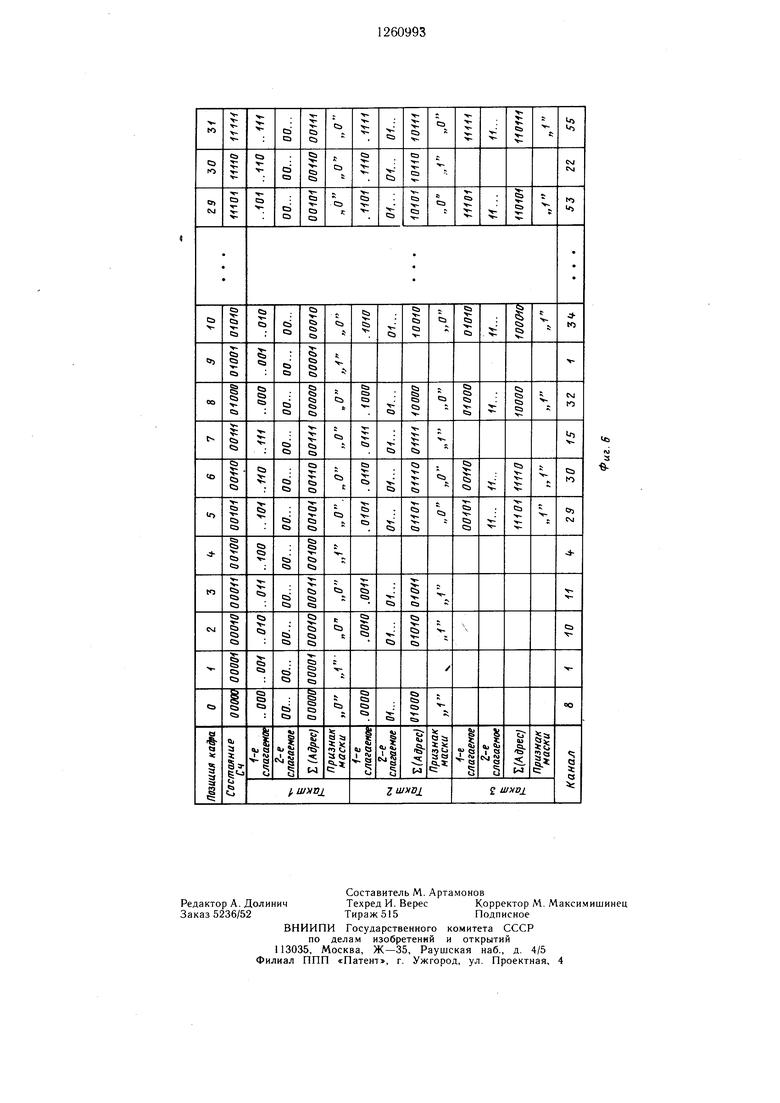

последовательного считывания масок, записанных в блок памяти; фиг. 5 - функциональная схема коммутатора; на фиг. 6 - таблица алгоритма работы коммутатора.

Коммутатор содержит счетчик 1, блок 2 памяти, регистр 3 сдвига, группу элементов И 4, сумматор 5, элемент И б, дешифратор 7, блок 8 управления.

Блок 8 управления состоит из элемен- 25 синхроимпульсов кадра. Число, формирующе- та НЕ 9, элементов И 10 и 11, элемен- еся на счетчике, является номером позиции тов 12 и 13 задержки, триггера 14.кадра. Число младших разрядов соответЦиклический кадр, формируемый комму- ствует размеру маски самых высокоопрос- таторами опроса, представляет собой совокуп- ных каналов. Младшие разряды подаются ность (набор) сообщений каналов с различ- на сумматор 5 непосредственно, старшие разной частотой опроса. Каждое сообщение кад- зо ряды - через элементы И 4. Перед на- ра является результатом опроса соответ- чалом формирования кадра состояние счетчи- ствующего канала.ка 1 - 1.

Частоты опроса каналов в кадре соот-Блок 2 памяти предназначен для храненосятся как 1:2:4 и т. д.ния масок каналов. Маски размещаются в

Для каждого сеанса опроса набор кана- памяти последовательно (в соответствии с лов и их распределение в кадре апри- 35 фиг. 36). Память одноразрядная, орно известны. На основе этого производит-Регистр 3 сдвига предназначен для обся программирование для программно- перестраиваемых коммутаторов. Различие каналов по частотам опроса позволяет интерпретировать кадр соответствующими подкад- но числу старших разрядов счетчика 1. В рами.начале каждого цикла регистр находится в

На фиг. 1 приведен кадр информа- состоянии О-0. Установка его в это состоя- тивностью сообщений. В кадре раз- ние производится сигналом с выхода блока 2 мещаются сообщения 14 каналов (Ki -Kj4)памяти при считывании «1. Образование

с частотой опроса ,5 каналов (Ki- констант производится при помощи сигна- К5 с частотой опроса и 2 каналов 45 лов сдвига и установки младщего разряразования последовательности констант О- 01, О-011, 1 - 1 в цикле работы коммутатора. Число вырабатываемых констант рав(К1 /(2) с .

Для кадра информативностью Q максимально возможное число каналов высшей опросности Q//MiKc 3 максимальное число самых низкоопросных - РДннн (гф их число равно Q).50

Размещение на любой позиции кадра канала с любой частотой опроса позволяет формировать кадры самой различной структуры.

Для любой структуры кадра распределение каналов с какой-либо частотой опро- 55 са в «своих подкадрах можно представить в виде разрядных позиционных масок.

да в «1, поступающих соответственно с второго и первого выходов блока 8 управления. Выходы регистра соединены с соответствующими входами элементов И 4 и сумматора 5.

Сумматор 5 предназначен для образования адреса обращения к блоку 2 памяти в результате суммирования двух слагаемых. Первое слагаемое представляет собой композицию младщих разрядов счетчика 1, поступающих непосредственно, и старщих разрядов счетчика, коммутируемых через элементы И 4 константой с регистра 3 сдвига. Вторым слагаемым является константа с

где «Ь означает наличие канала, «О - отсутствие. На фиг. 2а применительно к каналам кадра фиг. 1 представлены маски для подкадров всех частот опроса. Если маски разместить так, как показано на фиг. 26 и спроецировать их на позиции кадра, то каждой позиции будет соответствовать только одна «1 в какой-либо одной маске. Если затем разряды всех масок пронумеровать в возрастающем порядке

(фиг. 2в), а сами маски рассматривать как

исходные данные для программного коммутатора, то поиск опрашиваемого канала для каждой позиции кадра будет заключаться в последовательном просмотре разрядов масок соответствующих этой позиции. При обнару жении в какой-либо маске «1 опращива- ется канал с номером, равным номеру дан-

жении в какой-либо маске «1 опращива- ется канал с номером, равным номеру дан-

ного разряда. На фиг. За показано соотношение позиции кадра и номеров опрашиваемых каналов для исходных данных фиг. 2в. Если теперь маски зафиксировать в одноразрядной памяти (фиг. 36), то последовательный просмотр соответствующих разрядов будет осуществляться в порядке считывания по адресам согласно фиг. 4.

Счетчик 1 предназначен для фиксации

памяти последовательно (в соответствии с фиг. 36). Память одноразрядная, Регистр 3 сдвига предназначен для об но числу старших разрядов счетчика 1. В начале каждого цикла регистр находится в

разования последовательности констант О- 01, О-011, 1 - 1 в цикле работы коммутатора. Число вырабатываемых констант рав констант производится при помощи сигна- лов сдвига и установки младщего разряда в «1, поступающих соответственно с второго и первого выходов блока 8 управления. Выходы регистра соединены с соответствующими входами элементов И 4 и сумматора 5.

Сумматор 5 предназначен для образования адреса обращения к блоку 2 памяти в результате суммирования двух слагаемых. Первое слагаемое представляет собой композицию младщих разрядов счетчика 1, поступающих непосредственно, и старщих разрядов счетчика, коммутируемых через элементы И 4 константой с регистра 3 сдвига. Вторым слагаемым является константа с

регистра 3 сдвига. Веса разрядов константы равны весам соответствующих старших разрядов счетчика 1. Если второе слагаемое равно О-О, то старшие разряды в образовании первого слагаемого не участвуют и результатом суммирования является код младших разрядов счетчика 1.

Элемент И 6 предназначен для коммутации номера опрашиваемого канала (адреса памяти, по которому производилось

ние «О регистра 3 сдвига и восстанавливается исходное состояние триггера 14, запирающего элемент И 10. Поскольку сигнал на выходе блока 2 памяти присутствует длительное время (до следующего 5 считывания), то появление разрушающего сигнала с выхода элемента 12 задержки не приводит к срабатыванию элемента И 11, поскольку на другом входе этого элемента присутствует запрещающий потенциал с инобращение), если результатом считывания из,Q вертора НЕ 9. На этом выполнение цикла памяти является «1. Коммутируемый номер канала с выхода элемента И 6 поступает на вход дешифратора 7.

Дещифратор 7 предназначен для дешифрации номера канала и выработки управляющего сигнала, поступающего на соот-15 является разрушающий потенциал. Спустя ветствующий датчик.время TI с момента обращения к памяти

Блок 8 управления предназначен длятактовый импульс появляется на выходе выработки управляющих сигналов, поступающих на блок 2 памяти и регистр 3 сдвига.

Коммутатор работает следующим обра-, . ,.„.,..

зом.20 рающий) вход регистра 3 сдвига. Но поскольИсходной информацией для работы ком-ку состояние регистра О-О, то после деймутатора являются маски, размещаемые вствия сдвигающего сигнала его состояние не

блоке 2 памяти.меняется. Спустя время появляется сигнал на

Опрос очередного канала в кадре произ-выходе элемента 13 задержки, в результате

водится в результате выполнения коммута- 5 действия которого правый (младший) разряд

поиска канала заканчивается.

Если состояние считанного разряда маски равно «О, то выдача адреса памяти не производится, триггер 14 состояния не меняет, а на выходе элемента НЕ 9 поэлемента 12 задержки, в результате чего срабатывает элемент И 11. Сигнал с выхода этого элемента действует на третий (сдвитором очередного цикла поиска этого канала. Перед началом очередного цикла поиска регистр 3 сдвига находится в состоянии О-О, а на выходе триггера 14 имеется запрещающий потенциал, препятствующий

регистра 3 сдвига принимает состояние «1. В соответствии с новым состоянием О-01 сдвигающего регистра через соответствующий элемент И 4 транслируется состояние первого (младшего) из старших разрядов

ствующего разряда маски каналов следую- ш,ей по величине опросности, по которому следует провести обращение к памяти.

На этом первый такт цикла поиска кончается.

прохождению через элемент И 10 тактовых зосчетчика 1 на соответствующий вход сумма- импульсов, поступающих- на третий входтора 5. Поскольку первым слагаемым ста- блока 8 управления.ло число Q...bi а.-.щ, где ат...а - значе- Очередной цикл поиска начинается с по-ния младших разрядов; Ь - значение пра- ступления очередного синхроимпульса навого из старших разрядов счетчика 1, а вто- вход счечтика 1 и на второй вход блока 8рым слагаемым - константа 0-01, на выхо- управления. При этом на счетчике фикси- 35де сумматора 5 образуется адрес соответ- руется номер очередной позиции кадра, а триггер 14 взводится и на его выходе появляется разрешающий потенциал, поступающий на второй вход элемента И 10.

В дальнейшем работа коммутатора в цикле поиска происходит потактно.

Такт 1. Такт начинается с момента по-Такт 2. Такт начинается с момента появления на выходе элемента И 10 первогоявления на выходе элемента И 10 второго тактового импульса в цикле. Тактовый им-тактового импульса, в результате чего пульс воздействует на второй вход блока 2из блока 2 памяти по адресу (0п.-.0ч Ь От... памяти, в результате чего в последнем за- ...oi) (Оп...02 Ь Om...Oi) производится пускается циклограмма «Чтение. Посколькусчитывание необходимого разряда второй

маски..

Если состояние считанного разряда «1, то номер канала транслируется через элемент И 6, фиксируется и дешифрируется

является состояние младших разрядов счет- 50дешифратором 7. Одновременно считан- чика 1. По этому адресу из памятиным сигналом «1 регистр 3 сдвига сбра- считывается состояние соответствующего раз-сывается в состояние О-О, а триггер 14 ряда маски каналов с высшей частотойпринимает исходное состояние, запирая опроса. Если это состояние «1, то адресэлемент И 10. Поскольку на выходе эле- памяти (номер канала) транслируется черезмента НЕ 9 имеет мес то запрещающий элемент И 6, фиксируется и дешифрирует- 55потенциал, то при появлении разрушающе- ся дешифратором 7. Одновременно считан-го сигнала на выходе элемента 12 задерж- ным сигналом «1 подтверждается состоя-ки элемент И 11 не срабатывает. На

регистр 3 сдвига находится в состоянии О-О и на выходах всех элементов И 4 имеют место «О, то результатом суммирования, а следовательно, и адресом памяти

ние «О регистра 3 сдвига и восстанавливается исходное состояние триггера 14, запирающего элемент И 10. Поскольку сигнал на выходе блока 2 памяти присутствует длительное время (до следующего считывания), то появление разрушающего сигнала с выхода элемента 12 задержки не приводит к срабатыванию элемента И 11, поскольку на другом входе этого элемента присутствует запрещающий потенциал с инвертора НЕ 9. На этом выполнение цикла

вертора НЕ 9. На этом выполнение цикла

является разрушающий потенциал. Спустя время TI с момента обращения к памяти

поиска канала заканчивается.

Если состояние считанного разряда маски равно «О, то выдача адреса памяти не производится, триггер 14 состояния не меняет, а на выходе элемента НЕ 9 потактовый импульс появляется на выходе

, . ,.„.,..

рающий) вход регистра 3 сдвига. Но поскольэлемента 12 задержки, в результате чего срабатывает элемент И 11. Сигнал с выхода этого элемента действует на третий (сдвирегистра 3 сдвига принимает состояние «1. В соответствии с новым состоянием О-01 сдвигающего регистра через соответствующий элемент И 4 транслируется состояние первого (младшего) из старших разрядов

счетчика 1 на соответствующий вход сумма- тора 5. Поскольку первым слагаемым ста- ло число Q...bi а.-.щ, где ат...а - значе- ния младших разрядов; Ь - значение пра- вого из старших разрядов счетчика 1, а вто- рым слагаемым - константа 0-01, на выхо- де сумматора 5 образуется адрес соответ-

ствующего разряда маски каналов следую- ш,ей по величине опросности, по которому следует провести обращение к памяти.

На этом первый такт цикла поиска кончается.

счетчика 1 на соответствующий вход сумма- тора 5. Поскольку первым слагаемым ста- ло число Q...bi а.-.щ, где ат...а - значе- ния младших разрядов; Ь - значение пра- вого из старших разрядов счетчика 1, а вто- рым слагаемым - константа 0-01, на выхо- де сумматора 5 образуется адрес соответ-

этом выполнение цикла поиска канала закан чивается.

Если состояние считанного разряда «О, выдача адреса памяти не производится, триггер 14 состояния не меняет, а на выходе элемента НЕ 9 сохраняется разрешающий потенциал. При появлении разрешающего потенциала на выходе элемента 12 задержки срабатывает элемент И 11, в результате чего на третий (сдвигающий) вход регистра 3 сдвига поступает сигнал. Состояние регистра становится О...()10. Однако через время т сигнал с выхода элемента 13 задержки изменяет его на 0...011. В соответствии с новой констан той через соответствующие элементы И 4

мутатора, отличающийся тем, что, с целью упрощения и повышения быстродействия, в него введены сумматор, регистр сдвига, элемент И, группа элементов И и блок управления, первые выходы счетчика подклю5 чены к первым входам сумматора, выход которого соединен с первыми входами элемента И и блока памяти, выход которого подключен к второму входу элемента И и к первым входам регистра сдвига и. бло10 ка управления, первый и второй выходы которого соединены соответственно с вторым и третьим входами регистра сдвига, выходы которого подключены к соответствующим вторым входам сумматора и к первым входам соответствующих элементов И группы, выхотранслируются значения первого и второго 15 ды которых соединены с третьими входами

правых из старЩих разрядов счетчика 1. Поскольку слагаемыми теперь стали числа O...062fttam...ai и 0...011, результатом суммирования стал адрес необходимого разряда следующей (третьей) маски.

На этом второй такт цикла поиска Кончается.

Выполнение последующих тактов аналогично.

Последний такт. Такт начинается с мосумматора, вторые выходы счетчика подключены к вторым входам соответствующих элементов И группы, выход элемента И соединен через дешифратор с выходом комму- J- татора, первый вход которого подключен к второму входу блока управления, третий вход которого является вторым входом коммутатора, третий выход блока управления соединен с вторым входом блока памяти.

2. Коммутатор по п. 1, отличающийся

мента появления на выходе элемента И 10 25 тем, что блок управления содержит первый

последнего тактового импульса в цикле. В результате воздействия этого импульса из памяти считывается «1 и номер канала транслируется на дешифратор 7. Одновременно устанавливаются в исходные состояния регистр 3 сдвига и триггер 14.

На этом выполнение цикла поиска оп- ращиваемого «Канала заканчивается.

В йоследнем такте всегда считывается «1, поскольку из всех остальных масок сосчитались «О.

и второй элементы И, первый и второй элементы задержки, элемент НЕ и триггер, третий вход блока управления соединен с первым входом первого элемента И, выход которого является третьим выходом бло30 ка управления и через первый элемент задержки подключен к первому входу второго элемента И, выход которого является вторым выходом блока управления и через второй элемент задержки соединен с первым выходом блока управления, первый вход

Формула изобретения 1. Многоканальный коммутатор, содер35 блока управления подключен к первому входу триггера и входу элемента НЕ, выход которого соединен с вторым входом второго элемента И, второй вход блока управления

подключен к второму входу триггера, вы- жащий блок памяти, дешифратор, счетчик, ход которого соединен с вторым входом вход которого является первым входом ком- первого элемента И.

мутатора, отличающийся тем, что, с целью упрощения и повышения быстродействия, в него введены сумматор, регистр сдвига, элемент И, группа элементов И и блок управления, первые выходы счетчика подключены к первым входам сумматора, выход которого соединен с первыми входами элемента И и блока памяти, выход которого подключен к второму входу элемента И и к первым входам регистра сдвига и. блока управления, первый и второй выходы которого соединены соответственно с вторым и третьим входами регистра сдвига, выходы которого подключены к соответствующим вторым входам сумматора и к первым входам соответствующих элементов И группы, выходы которых соединены с третьими входами

сумматора, вторые выходы счетчика подключены к вторым входам соответствующих элементов И группы, выход элемента И соединен через дешифратор с выходом комму- татора, первый вход которого подключен к второму входу блока управления, третий вход которого является вторым входом коммутатора, третий выход блока управления соединен с вторым входом блока памяти.

2. Коммутатор по п. 1, отличающийся

тем, что блок управления содержит первый

тем, что блок управления содержит первый

и второй элементы И, первый и второй элементы задержки, элемент НЕ и триггер, третий вход блока управления соединен с первым входом первого элемента И, выход которого является третьим выходом блока управления и через первый элемент задержки подключен к первому входу второго элемента И, выход которого является вторым выходом блока управления и через второй элемент задержки соединен с первым выходом блока управления, первый вход

блока управления подключен к первому входу триггера и входу элемента НЕ, выход которого соединен с вторым входом второго элемента И, второй вход блока управления

о 2 3 S S 7 8 3 10 И 12 )3 1 IS S П IS IS 20 21 22 23 Z ZS IS 27 2S 23 3031 . Кадр :.

f . Kj «1 .1

v2

f

1 f f f«

5 S

10 11 13 « Ладкавр (Kaipj

Фаг.1

Маска каналов с/j«« |f|Ol flOlOlOl g|OlOig|glPT Tgl Паска каналов с IOlOlg|OlOlfNlglfig|fl lgNloHlg|g{g|g|oNUIOl |g|f }2|gif|g|rl t fiCKa каналов .l

loн g g f gTШШlf i |gTfTgTgTgTgT7rg gT-fTgTgfg| gFi gi giT{gTgTgi

i a i o o o no ff o o o o im i miTimo STiTo o o}o oTo o (o|g|g g g|flf|g|f|g|Яf|g|floJf g|g|g|g|glллg|frglflлg f gln

ffy i/g// 2/3/V/5/ff/7«y 24fZ2232 2524728 5gjy

(f

0 f 2 3 5g 7 g J 2 3 5 g 7 g 2Ъ S870123l 5B7

rg pr TgTg|gl Tgfglg gTgIgFr

rfTgRM|g|g|g|f|o|g|o|g|g|gm

S 910H1Z131if151617i819 1ZZ23,S 91Bm2131 1S1S 7181320Zi2ZZ

2 25y27гyf yз/52JJ3 35yз7д зy g«y гy y g 7 г JJg /g J5 5f

gy 2 3 t g6 j8 g g///Z/3%5-/5,7%j2g2/2Z232 525 2 j j/

5 иг.2

/(Kl

«I (/ | /f|

Kl

K Ki

f f ffi « « /S

21 22 г 2S 27 29 31

I

«3

3

«

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный коммутатор | 1986 |

|

SU1381565A1 |

| Устройство для опроса информационных каналов | 1985 |

|

SU1297092A1 |

| Многоканальный коммутатор | 1985 |

|

SU1305749A2 |

| Устройство для выбора и переадресации каналов | 1985 |

|

SU1341729A1 |

| Многоканальный коммутатор | 1979 |

|

SU809291A1 |

| Ассоциативное оперативное запоминающее устройство | 1987 |

|

SU1462420A1 |

| Устройство контроля микропроцессорных блоков | 1986 |

|

SU1332320A2 |

| Устройство для выбора информационных каналов | 1976 |

|

SU651489A1 |

| Устройство центрального управления процессора | 1983 |

|

SU1136177A1 |

| АВТОМАТИЗИРОВАННАЯ РЕЗЕРВИРОВАННАЯ СИСТЕМА УПРАВЛЕНИЯ ЗАПРАВКОЙ КРИОГЕННОГО РАЗГОННОГО БЛОКА | 2001 |

|

RU2216760C2 |

Изобретение относится к области телемеханики и может использоваться в автоматизированных системах контроля и управления многопараметрическими объектами. Цель изобретения - упрощение и повышение быстродействия. Это достигается новым способом представления исходных данных в блоке памяти. С этой целью все коммутируемые каналы с одинаковой частотой опроса объединены в группы, каждая из которых формирует соответствующий ей под- кадр информации, повторяющийся с частотой опроса этой группы. Каждой структуре подкадра ставится в соответствие код маски, причем число кодов масок равно количеству различных частот опроса. Коды всех масок записываются в блок памяти. Поиск опрашиваемого канала для каждой позиции кадра заключается в последовательном считывании разрядов масок, соответствующих этой позиции. I з.п. ф-лы, 6 ил. $ ю о со со оо

| Многоканальный коммутатор | 1979 |

|

SU809291A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Устройство опроса телеметрических каналов | 1976 |

|

SU612406A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

Авторы

Даты

1986-09-30—Публикация

1985-03-15—Подача