сл

со оо

сл

О5 СЛ

N)

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный коммутатор | 1985 |

|

SU1260993A1 |

| Многоканальный коммутатор | 1985 |

|

SU1305749A2 |

| Буферное запоминающее устройство | 1985 |

|

SU1264239A1 |

| Устройство для опроса информационных каналов | 1985 |

|

SU1297092A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1304079A1 |

| Устройство центрального управления процессора | 1983 |

|

SU1136177A1 |

| Устройство управления для памяти на цилиндрических магнитных доменах | 1984 |

|

SU1265855A1 |

| Вычислительное устройство | 1986 |

|

SU1432510A1 |

| Устройство для сопряжения телеграфных линий связи с ЦВМ | 1988 |

|

SU1603392A1 |

| Многоканальный коммутатор | 1979 |

|

SU809291A1 |

Изобретение относится к телемеханике и может быть использовано в автоматизированных системах контроля и управления многопараметрическими объектами, а также в средствах программного опроса каналов с автоматическим выбором порядка опроса. Цель изобретения - упрощение и повышение быстродействий коммутатора. Коммутатор содержит счетчик 1, блок 2 памяти, регистр 3 сдвига, группу элементов И 4, сумматор 5, элемент И 6, дешифратор 7, блок 8 управления, содержащий элемент НЕ 9, элементы И 10 и 11, элементы задержки 12, 13 и триггер 14. Коммутатор также содержит элемент ИЛИ 15 и элемент 16 задержки. Сущность изобретения заключается в том, что формирование сигнала на разрешение спроса каналов низкой опросности происходит в том случае, когда содержимое всех масок для каналов более высокой опросности. 3 ил. 3

cfJuP.Z

Изобретение отнисится к телемеханике, может быть ис1К)Л1)Зовано в автоматизированных системах контроля и управления многопараметрическими объектами, а также в системах программного опроса каналов и является усоверп енствованием изобретения по авт. св. № 1260993.

Цель изобретения - упрощение и повы шение быстродействия коммутатора.

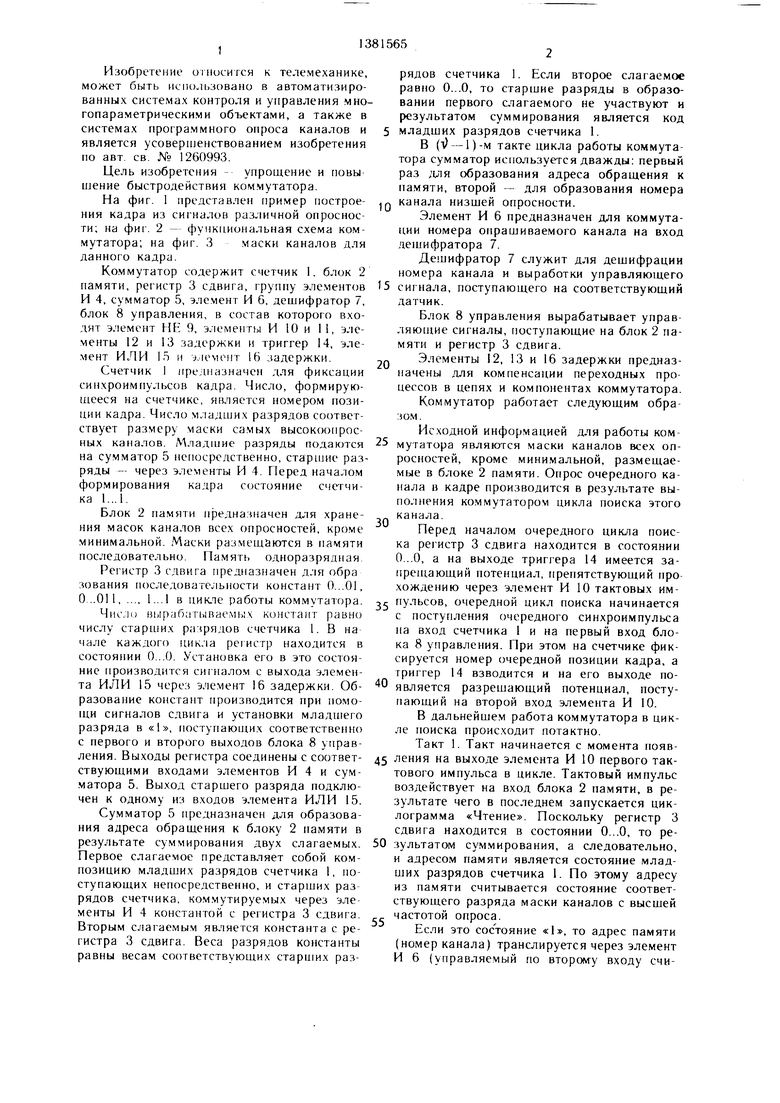

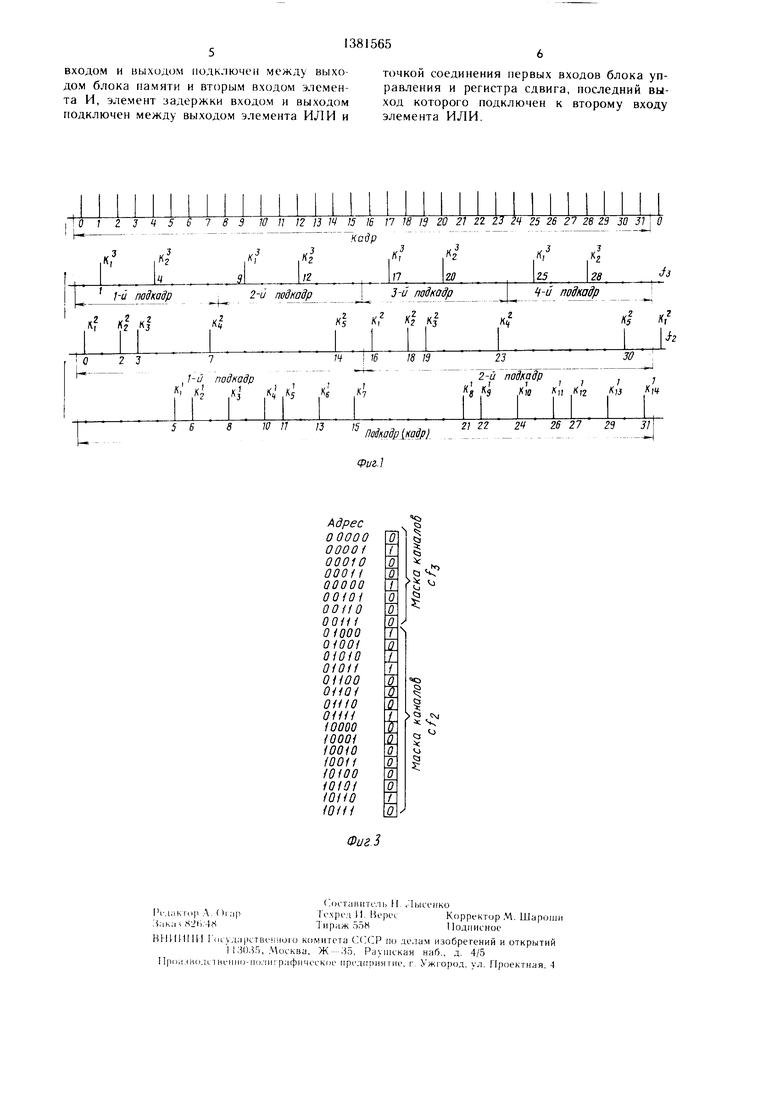

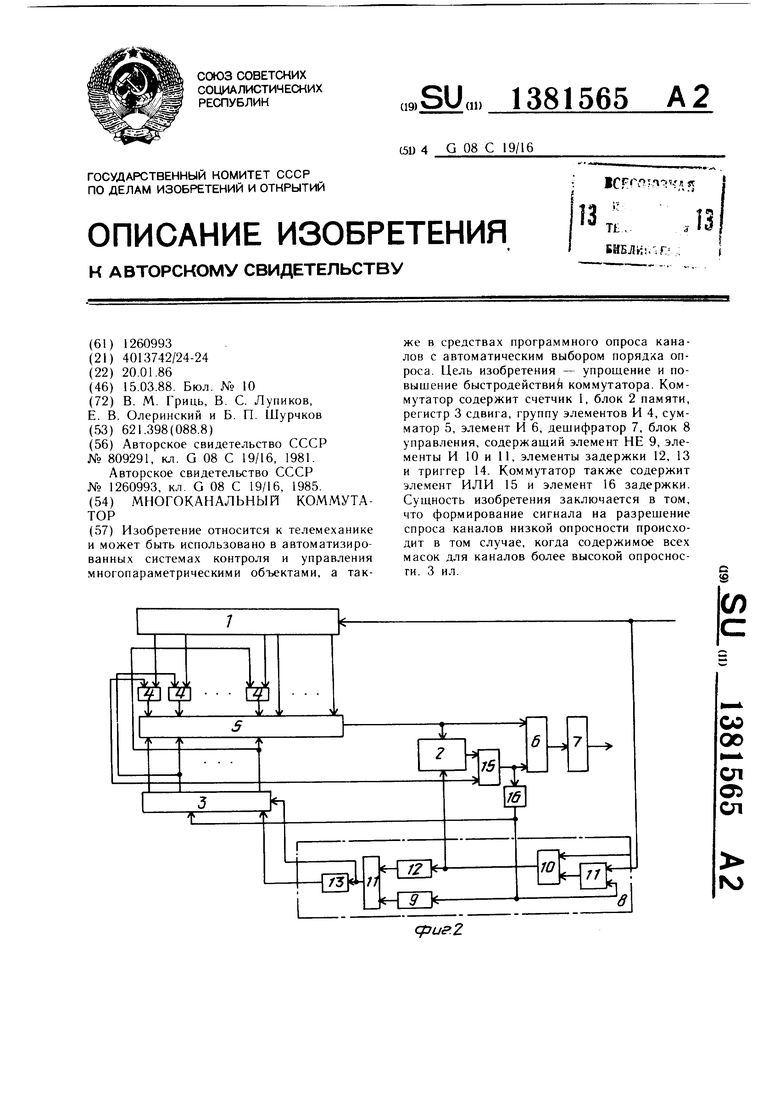

На фиг. 1 представлен пример построения кадра из сигналов различной опроснос- ти; на фиг. 2 - функциональная схема коммутатора; на фиг. 3 маски каналов для данного кадра.

Ко.ммутатор содержит счетчик 1, блок 2 памяти, регистр 3 сдвига, группу элементов И 4, сумматор 5, элемент И 6, дешифратор 7, блок 8 управления, в состав которого входят элемент НЕ 9, элементы И 10 и 11, элементы 12 и 13 задержки и триггер 14, элемент ИЛИ 15 и элемент 16 задержки.

Счетчик 1 предназначен для фиксации синхроимпульсов кадра. Число, формирующееся на счетчике, я 5ляется номером позиции кадра. Число младших разрядов соответствует размеру маски самых высокоонрос- ных каналов. Младп ие разряды подаются на су.мматор 5 непосредственно, старшие разряды - через элементы И 4. Перед началом формирования кадра состояние счетчика 1...1.

Блок 2 памяти предназначен для хранения масок каналов всех опросностей, кроме минимальной. Маски размещаются в памяти последовательно. Память одноразрядная

Регистр 3 сдвига предназначен для обра зования 11оследовате;1ьности констант 0...01, О ..011 1...1 в цикле работы коммутатора.

Чис .И) В1)фабатываемы констант равно числу старших разрядов счетчика 1. В на чале каждого цикла ре1истр находится в состоянии 0...0. Установка его в это состояние нроизводится сигналом с выхода элемента ИЛИ 15 через элемент 16 задержки. Образование констант производится при помощи сигналов сдвига и установки младшего разряда в «I, поступающих соответственно с первого и второго выходов блока 8 управления. Выходы регистра соединены с соответствующими входами элементов И 4 и сумматора 5. Выход старщего разряда подключен к одному из входов элемента ИЛИ 15.

Сумматор 5 предназначен для образования адреса обращения к блоку 2 памяти в результате суммирования двух слагаемых. Первое слагаемое представляет собой композицию младших разрядов счетчика 1, поступающих непосредственно, и старших разрядов счетчика, коммутируемых через элементы И 4 константой с регистра 3 сдвига. Вторым слагаемым является константа с регистра 3 сдвига. Веса разрядов константы равны весам соответствующих старших раз5

рядов счетчика 1. Если второе слагаемое равно 0...0, то старшие разряды в образовании первого слагаемого не участвуют и результатом суммирования яв-тяется код младших разрядов счетчика 1.

В (V - 1)-м такте цикла работы коммутатора сумматор используется дважды: первый раз ;ця образования адреса обращения к памяти, второй - для образования номера Q канала низшей опросности.

Элемент И 6 предназначен для коммутации номера опрашиваемого канала на вход дешифратора 7.

Дешифратор 7 служит для дешифрации номера канала и выработки управляющего 5 сигнала, поступающего на соответствующий датчик.

Блок 8 управления вырабатывает управляющие сигналы, поступающие на блок 2 памяти и регистр 3 сдвига.

Элементы 12, 13 и 16 задержки предназначены для компенсации переходных процессов в цепях и компонентах коммутатора.

Коммутатор работает следующим образом.

Исходной информацией для работы коммутатора являются маски каналов всех опросностей, кроме минимальной, размещаемые в блоке 2 памяти. Опрос очередного канала в кадре производится в результате выполнения коммутатором цикла поиска этого канала.

Перед началом очередного цикла поиска регистр 3 сдвига находится в состоянии 0...0, а на выходе триггера 14 имеется запрещающий потенциал, препятствующий про хождению через элемент И 10 тактовых им- 5 пульсов, очередной цикл поиска начинается с поступления очередного синхроимпульса на вход счетчика 1 и на первый вход блока 8 управления. При этом на счетчике фиксируется номер очередной позиции кадра, а триггер 14 взводится и на его выходе появляется разрешающий потенциал, поступающий на второй вход элемента И 10.

В дальнейшем работа коммутатора в цикле поиска происходит потактно.

Такт 1. Такт начинается с момента появ- 5 ления на выходе элемента И 10 первого тактового импульса в цикле. Тактовый импульс воздействует на вход блока 2 памяти, в результате чего в последнем запускается циклограмма «Чтение. Поскольку регистр 3 сдвига находится в состоянии 0...0, то ре- 0 зультатом суммирования, а следовательно, и адресом памяти является состояние младших разрядов счетчика 1. По этому адресу из памяти считывается состояние соответствующего разряда маски каналов с высшей частотой опроса.

Если это сос тояние «1, то адрес памяти (номер канала) транслируется через элемент И 6 (управляемый по второму входу счи0

танной «I с выхода элемента ИЛИ 15), фиксируется и дешифруется дешифратором 7 Через время lj сигналом «1 подтверждается состояние «О регистра 3 сдвига и восстанавливается исходное состояние триггера 14, запирающего элемент И 10. Поскольку сигнал на выходе блока 2 памяти присутствует длительное время, то появление разрешающего сигнала с выхода элемента 12 задержки не приводит к срабатыванию элемента И 11, поскольку на другом входе этого элемента присутствует запрещающий потенциал с элемента НЕ 9. На этом выполнение цикла поиска канала заканчивается.

Если состояние считанного разряда маски равно «О, то выдача адреса памяти не производится, триггер 14 состояние не меняет, а на выходе элемента НЕ 9 появляется разрешающий потенциал. Спустя время С, с момента обращения к памяти тактовый имвает. На этом выполнение цикла поиска канала заканчивается.

Если состояние считанного разряда «О, выдача номера канала не производится, 5 триггер 14 состояния не меняет, а на выходе элемента НЕ 9 сохраняется разрешающий потенциал. При появлении разрешающего потенциала на выходе элемента 12 задержки срабатывает элемент И 11, в результате чего на сдвигающий вход регистра 3 сдвига поступает сигнал и его состояние становится 0...010. Однако через время ii сигнал с выхода элемента 13 задержки изменяет его на 0...011. В соответствии с новой константой через соответствующие элементы И 4 транслируется значение первого и второго правых из старших разрядов счетчика 1. Поскольку слагаемыми стали числа O...0bjb, а„...а и 0...011, результатом суммирования стал адрес необходимого раз10

15

пульс появляется на выходе элемента 12 за- ., ряда следующей (третьей) маски. На этом

держки, в результате чего срабатывает элемент И 11. Сигнал с выхода этого элемента действует на сдвигающий вход регистра 3 сдвига. Но поскольку состояние регистра 0...0, то после действия сдвигающего сигнала его состояние не меняется. Спустя время TI появ-тяется сигнал на выходе элемента 13 задержки, в результате действия которого правый (младший) разряд регистра 3 сдвига принимает состояние «1. В соответствии с новым состоянием 0...01 сдвигающего регистра через соответствующий элемент И 4 транслируется состояние первого (младшего) из старших разрядов счетчика 1 на соответствующий вход сумматора 5. Поскольку первым слагаемым стало число О...ОЬ., а...а, , где а...а - значения младщих разрядов; Ц - значение правого из старших разрядов счетчика 1, а вторым слагаемым - константа 0...01, на выходе сумматора 5 образуется адрес соответствующего разряда маски каналов следующей по величине опросности, по которому следует провести обращение к памяти. На этом первый такт цикла поиска кончается.

Такт 2. Такт начинается с момента появления на выходе элемента И 10 второго тактового импульса, в результате чего из блока 2 памяти по адресу (0...0,Ь, а...а) +

30

второй такт цикла поиска кончается.

Выполнение последующих тактов вплоть до (v) - 1)-го аналогично.

Последний (V - 1)-й такт. Такт начинается с момента появления на выходе эле25 мента И 10 (т)-1)-го тактового импульса в цикле. Если в результате воздействия этого импульса из памяти считывается «I, то на выход коммутатора поступает номер канала опросности f, а регистр 3 сдвига и триггер 14 сбрасываются в «О. На этом выполнение цикла поиска канала заканчивается.

Однако в случае, если из памяти считывается «О, коммутатор выполняет действия по формированию и опросу канала низшей

25 опросности. Когда состояние регистра 3 сдвига в результате воздействия сигналов с блока 8 управления становится 1...1 и на сумматоре 5 фор.мируется номер канала низшей опросности, выдача этого номера производится при помощи потенциала «1 со стар шего разряда регистра 3 сдвига (действительно, «1 в старшем разряде регистра сдвига появляется только при поиске канала низшей опросности). Этим же потенциалом «1 коммутатор сбрасывается в исходное состояние.

45

Как видно, в этом такте работы коммутатора может произойти опрос как канала опросности f 2 (при считывании «1 из памяти), так и канала опросности f 1 (при

+ (0... 0....О.,) производится считывание необходимого разряда второй маски.

Если состояние считанного разряда «1, то номер канала транслируется на дешифра- 50 считывании из памяти «О), тор 7, где дешифруется. Считанным сигналом «1 регистр 3 сдвига сбрасывается в состояние 0...0, а триггер 14 принимает исходное состояние, запирая элемент И 10. Поскольку на выходе элемента НЕ 9 и.меет место запрещающий потенциал, то при появлении разрешающего сигнала на выходе элемента 12 задержки элемент И 11 не срабатыФормула изобретения

55

Многоканальный коммутатор по авт. св. № 1260993, отличающийся тем, что, с целью упрощения и повышения быстродействия коммутатора, в него введены элемент задержки и элемент ИЛИ, который первым

вает. На этом выполнение цикла поиска канала заканчивается.

Если состояние считанного разряда «О, выдача номера канала не производится, триггер 14 состояния не меняет, а на выходе элемента НЕ 9 сохраняется разрешающий потенциал. При появлении разрешающего потенциала на выходе элемента 12 задержки срабатывает элемент И 11, в результате чего на сдвигающий вход регистра 3 сдвига поступает сигнал и его состояние становится 0...010. Однако через время ii сигнал с выхода элемента 13 задержки изменяет его на 0...011. В соответствии с новой константой через соответствующие элементы И 4 транслируется значение первого и второго правых из старших разрядов счетчика 1. Поскольку слагаемыми стали числа O...0bjb, а„...а и 0...011, результатом суммирования стал адрес необходимого раз

ряда следующей (третьей) маски. На этом

второй такт цикла поиска кончается.

Выполнение последующих тактов вплоть до (v) - 1)-го аналогично.

Последний (V - 1)-й такт. Такт начинается с момента появления на выходе элемента И 10 (т)-1)-го тактового импульса в цикле. Если в результате воздействия этого импульса из памяти считывается «I, то на выход коммутатора поступает номер канала опросности f, а регистр 3 сдвига и триггер 14 сбрасываются в «О. На этом выполнение цикла поиска канала заканчивается.

Однако в случае, если из памяти считывается «О, коммутатор выполняет действия по формированию и опросу канала низшей

опросности. Когда состояние регистра 3 сдвига в результате воздействия сигналов с блока 8 управления становится 1...1 и на сумматоре 5 фор.мируется номер канала низшей опросности, выдача этого номера производится при помощи потенциала «1 со старшего разряда регистра 3 сдвига (действительно, «1 в старшем разряде регистра сдвига появляется только при поиске канала низшей опросности). Этим же потенциалом «1 коммутатор сбрасывается в исходное состояние.

Как видно, в этом такте работы коммутатора может произойти опрос как канала опросности f 2 (при считывании «1 из памяти), так и канала опросности f 1 (при

считывании из памяти «О),

из памяти «О),

Формула изобретения

50 считывании из памяти «О),

55

Многоканальный коммутатор по авт. св. № 1260993, отличающийся тем, что, с целью упрощения и повышения быстродействия коммутатора, в него введены элемент задержки и элемент ИЛИ, который первым

входом и выходом подключен между выходом блока памяти и вторым входом элемента И, элемент задержки входом и выходом подключен между выходом элемента ИЛИ и

точкой соединения первых входов блока управления и регистра сдвига, последний выход которого подключен к второму входу элемента ИЛИ.

| Многоканальный коммутатор | 1979 |

|

SU809291A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Многоканальный коммутатор | 1985 |

|

SU1260993A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1988-03-15—Публикация

1986-01-20—Подача