от блока генератора 9 псевдослучайны тестов и очередного кода марковской последовательности - из формирователя 7. Необходимый источник подключается к блоку 6 обработки информации через блок 8 мультиплексоров. При суперпозиции выбор соответствующих полей задается масками из блока 5 сверхоперативной памяти. Входные воздействия подаются на объект контроля 3 и эталон 2 (при выполнении

1

Изобретение относится к вычислительной технике, в частности к средствам автоматического контроля цифро- объектов, может быть использовано для высокочастотной функциональной проверки микропроцессоров, блоков ЭВМ, построенных на основе микропроцессоров и других схем большой степени интеграции, целых микроЭВМ и прочих сложных устройств в процессе их производства и является усовершенствованием изобретения по авт.св. № 1042023..

Цель изобретения - повышение полноты и эффективности контроля.

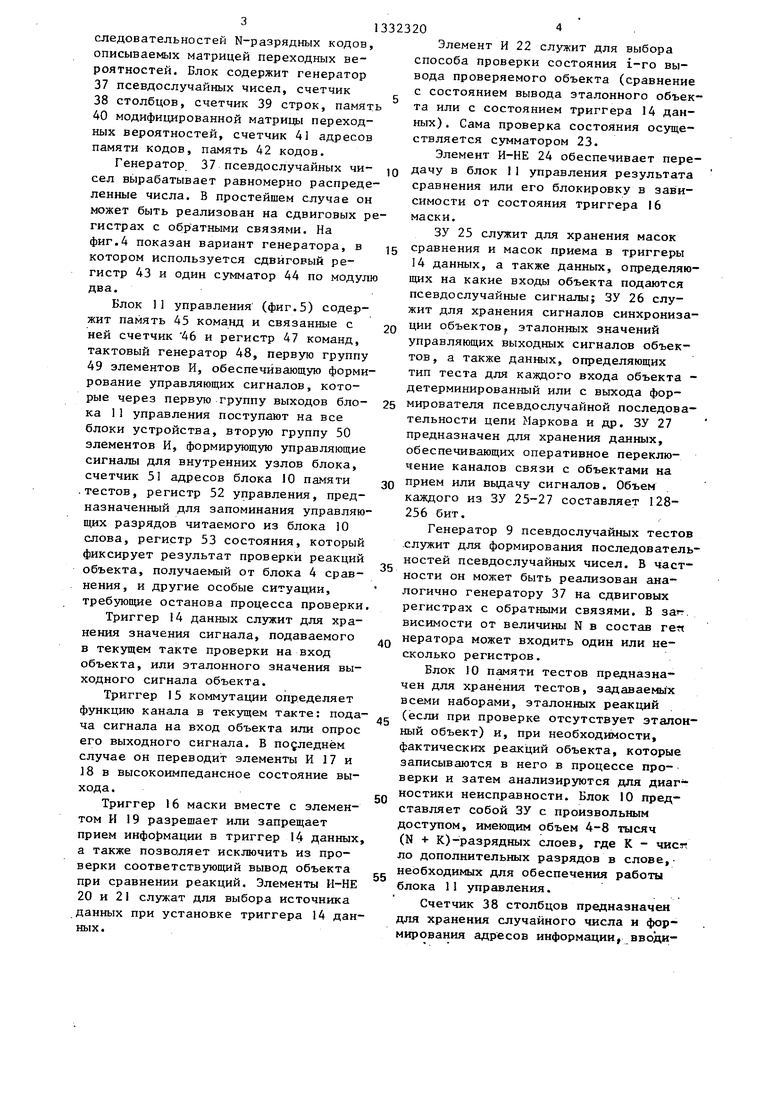

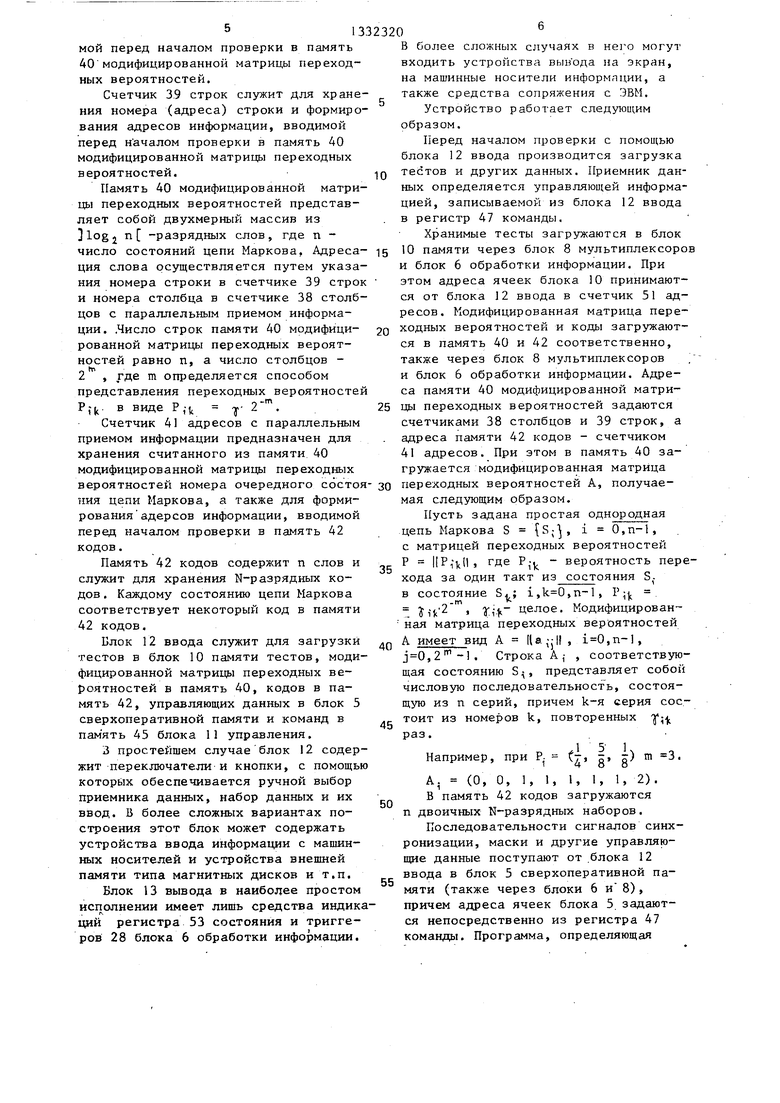

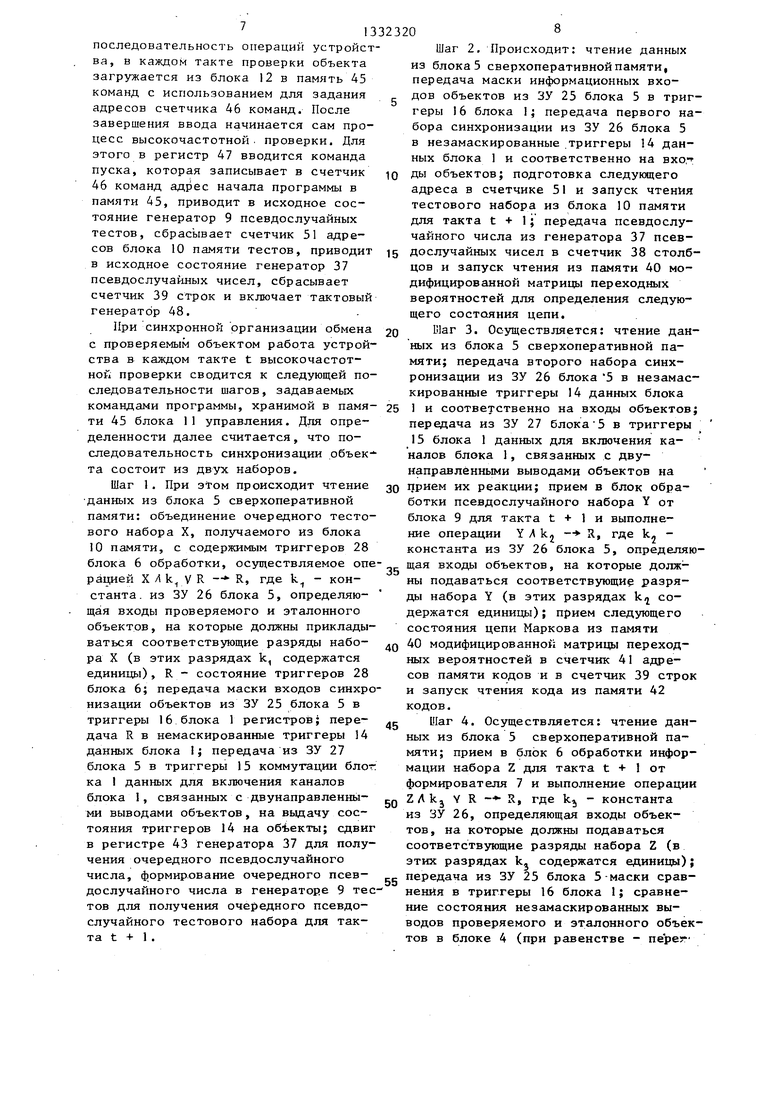

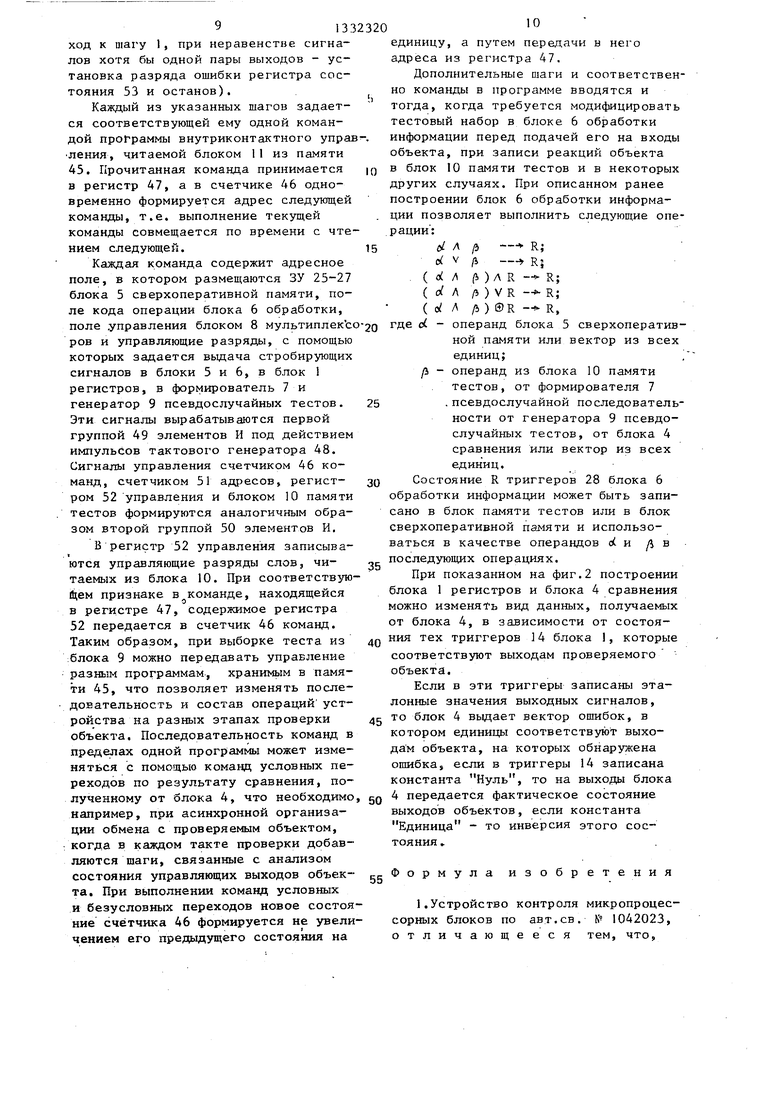

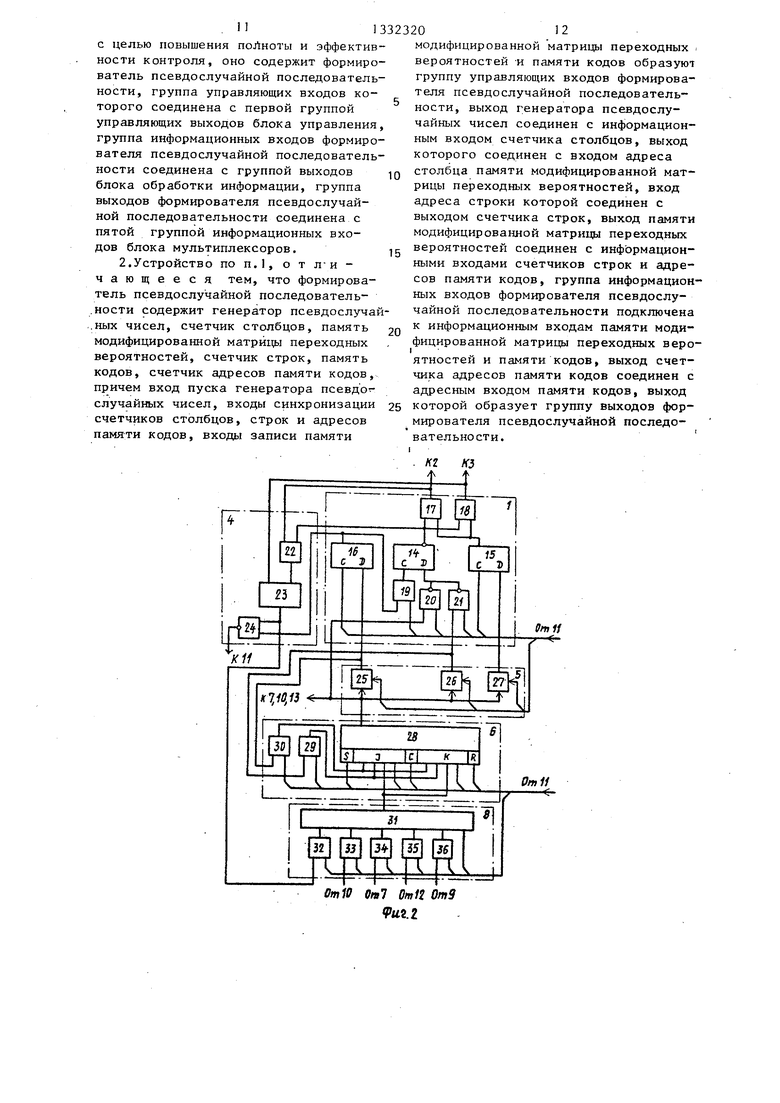

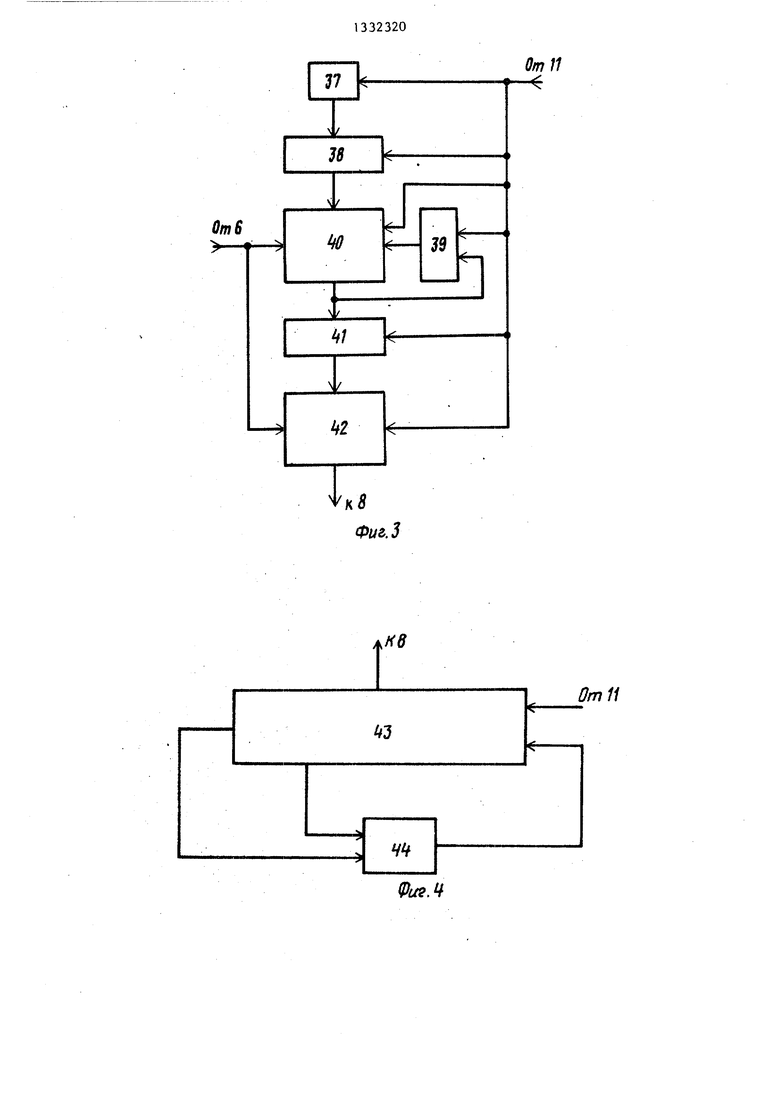

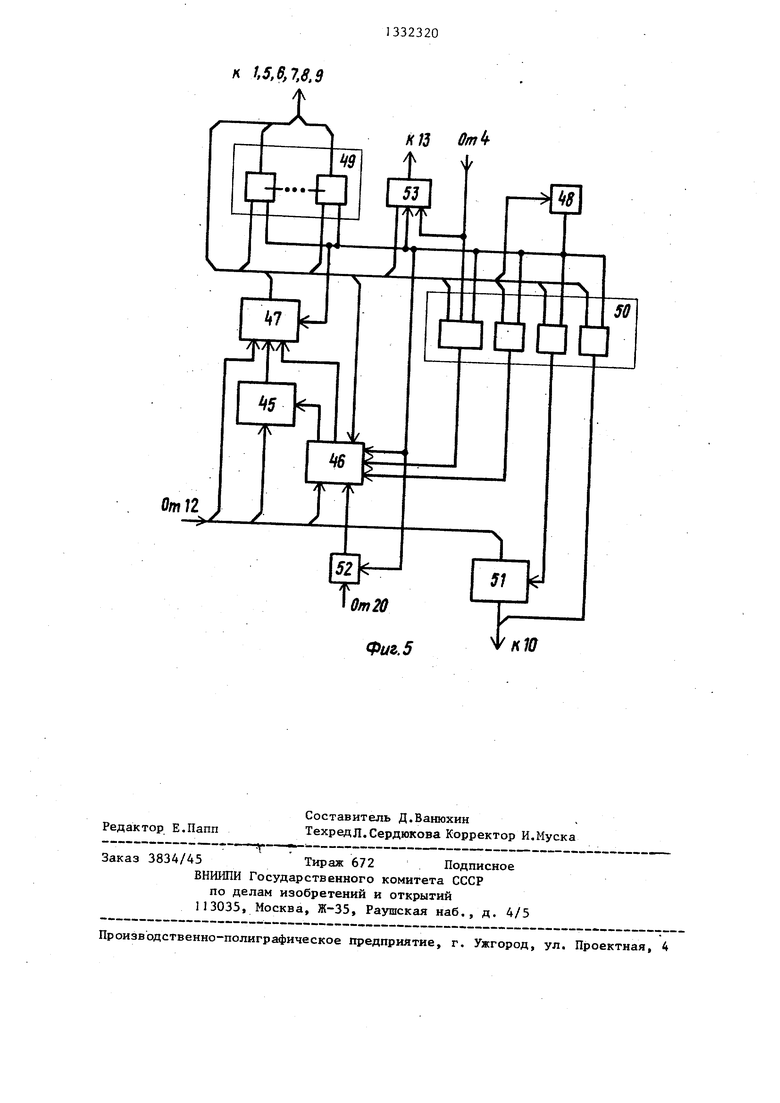

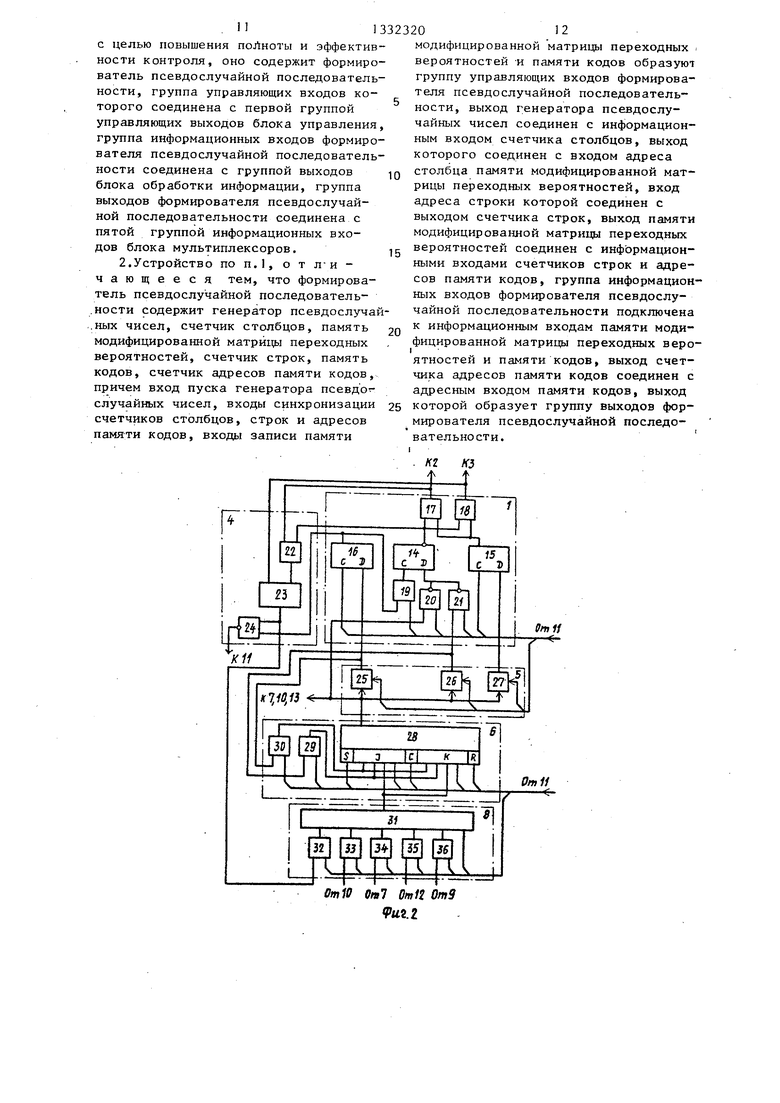

На фиг.1 представлена структурная схема устройства; на фиг.2 - принципиальные схемы одного разряда блока регистров, блока сравнения, блока сверхоперативной памяти, блока обработки информации и блока мультиплексоров; на фиг.З - схема формирователя псевдослучайной последовательности; на фиг.4 - схема генератора псевдослучайных чисел; на фиг.З - схема блока управления.

В состав устройства входят блок 1 регистров, эталонный 2 и проверяемый 3 объекты, блок 4 сравнения, блок 5 сверхоперативной памяти, блок 6 обработки информации, формирователь 7 псевдослучайной последовательности, блок 8 мультиплексоров, генератор 9 псевдослучайных тестов, блок 10 памяти тестов, блок 11 управления, блок 12 ввода, блок 13 вывода.

Каждый из блоков 1, 4-6 и ,8 состоит из N идентичных схем (разрядов).

проверки с помощью эталона) через блок 1 регистров. Блок 4 сравнения выполняет сравнение откликов объекта контроля 3 и эталона 2, а при его отсутствии - с предварительно вычисленными откликами, подготовленными в блоке 1 регистров, и выдает через блок 8 мультиплексоров и через блок 6 ббработки информации результаты сравнения на блок 13 вывода и блок 11 управления. 1 з.п. ф-лы, 5 ил.

0

5

с

35

0

0

каждая из которых соответствует одному выводу проверяемого и эталонного объектов. Величина N определяется числом-выводов у объектов, для большинства микропроцессорных блоков достаточно N 256.

Схема любого i-ro разряда блока 1 регистров содержит триггер 14 данных и триггер 15 коммутации, триггер 16 маски, элементы И 17-19 и два элемента И-НЕ 20 и 21.

В i-й разряд блока 4 сравнения входят последовательно соединенные элемент . И 22, сумматор 23 по модулю два и элемент И-НЕ 24.

В состав . i-ro разряда блока; 5 сверхоперативной памяти входят три одноразрядных запоминающих устройства (ЗУ)- 25-27 с независимым управлением.

Любой i-й разряд блока 6 обработки информаи 1И в простейшем случае содержит 1К-триггер 28, совмещающий функции одноразрядного регистра-накопителя и схемы логического преобразования данных, и элементы ИЛИ 29 и 30, с помощью которых в некоторых операциях обеспечивается отключение выходов ЗУ 25 и 26 от входов триггера 28.

В каждый i-й разряд блока 8 мультиплексоров входят элемент ИЛИ 31 и связанные с ним пять элементов И 32-36, с помощью которых производится выбор источников данных для блока 6 обработки информации.

Формирователь 7 псевдослучайной последовательности (фиг.З) служит для формирования псевдослучайных по

следовательностей N-разрядных кодов, описываемых матрицей переходных вероятностей. Блок содержит генератор

37псевдослучайных чисел, счетчик

38столбцов, счетчик 39 строк, памят 40 модифицированной матрицы переходных вероятностей, счетчик 41 адресов памяти кодов, память 42 кодов.

Генератор 37 псевдослучайных чи- сел вырабатывает равномерно распределенные числа. В простейшем случае он может быть реализован на сдвиговых ргистрах с обр атными связями. На фиг.4 показан вариант генератора, в котором используется сдвиговый регистр 43 и один сумматор 44 по модул два.

Блок 11 управления (фиг.5) содержит память 45 команд и связанные с ней счетчик 46 и регистр 47 команд, тактовый генератор 48, первую группу 49 элементов И, обеспечивающую формирование управляющих сигналов, которые через первую группу выходов блока 11 управления поступают на все блоки устройства, вторую группу 50 элементов И, формирующую управляющие сигналы для внутренних узлов блока, счетчик 51 адресов блока 10 памяти .тестов, регистр 52 управления, предназначенный для запоминания управляющих разрядов читаемого из блока 10 слова, регистр 53 состояния, который фиксирует результат проверки реакций объекта, получаемый от блока 4 сравнения, и другие особые ситуации, требующие останова процесса проверки

Триггер 14 данных сл5 жит для хранения значения сигнала, подаваемого в текущем такте проверки на вход объекта, или эталонного значения выходного сигнала объекта.

Триггер 15 коммутации определяет функцию канала в текущем такте: подача сигнала на вход объекта или опрос его выходного сигнала. В последнем случае он переводит элементы И 17 и J8 в высокоимпедансное состояние выхода .

Триггер 16 маски вместе с элементом И 19 разрешает или запрещает прием инфо)мации в триггер 14 данных а также позволяет исключить из проверки соответствующий вывод объекта при сравнении реакций. Элементы И-НЕ 20 и 21 служат для выбора источника данных при установке триггера 14 данных .

5

0

5

0

5

0

5

0

5

Элемент И 22 служит для выбора способа проверки состояния i-ro вывода проверяемого объекта (сравнение с состоянием вывода эталонного объекта или с состоянием триггера 14 данных) . Сама проверка состояния осуществляется сумматором 23.

Элемент И-НЕ 24 обеспечивает передачу в блок 11 управления результата сравнения или его блокировку в зависимости от состояния триггера 16 маски.

ЗУ 25 служит для хранения масок сравнения и масок приема в триггеры 14 данных, а также данных, определяющих на какие входы объекта подаются псевдослучайные сигналы; ЗУ 26 служит для хранения сигналов синхронизации объектов, эталонных значений управляющих выходных сигналов объектов, а также данных, определяющих тип теста для каждого входа объекта - детерминированный или с выхода формирователя псевдослучайной последовательности цепи Маркова и др. ЗУ 27 предназначен для хранения данных, обеспечивающих оперативное переключение каналов связи с объектами на прием или выдачу сигналов. Объем каждого из ЗУ 25-27 составляет 128- 256 бит.

Генератор 9 псевдослучайных тестов .служит для формирования последовательностей псевдослучайных чисел. В частности он может быть реализован аналогично генератору 37 на сдвиговых регистрах с обратными связями. Б заг. висимости от величины N в состав гегт нератора может входить один или несколько регистров.

Блок 10 памяти тестов предназначен для хранения тестов, задаваемых всеми наборами, эталонных реакций (если при проверке отсутствует эталонный объект) и, при необходш ости, фактических реакций объекта, которые записываются в него в процессе проверки и затем анализируются для диагностики неисправности. Блок 10 представляет собой ЗУ с произвольным доступом, имеющим объем 4-8 тысяч (N + К)-разрядных слоев, где К - чисг ло дополнительных разрядов в слове,- необходимых для обеспечения работы блока 1 управления.

Счетчик 38 столбцов предназначен для хранения случайного числа и формирования адресов информации, вводимой перед началом проверки в память 40 модифицированной матрицы переходных вероятностей.

Счетчик 3.9 строк служит для хранения номера (адреса) строки и формирования адресов информации, вводимой перед началом проверки в память 40 модифицированной матрицы переходных вероятностей.

Память 40 модифицированной матрицы переходных вероятностей представляет собой двухмерный массив из 3logj п -разрядных слов, где п - число состояний цепи Маркова, Адреса- ция слова осуществляется путем указания номера строки в счетчике 39 строк и номера столбца в счетчике 38 столбцов с параллельным приемом информации. .Число строк памяти 40 модифици- рованной матрицы переходных вероятностей равно п, а число столбцов - 2 , где m определяется способом представления переходных вероятностей Р,-((. в виде Р,-,, - 2.

Счетчик 41 адресов с параллельным приемом информации предназначен для хранения считанного из памяти 40 модифицированной матрицы переходных

вероятностей номера очередного состоя- зо переходных вероятностей А, получаения цепи Маркова, а также для формирования адерсов информации, вводимой перед началом проверки в память 42 кодов.

Память 42 кодов содержит п слов и служит для хранения N-разрядньгх кодов . Каждому состоянию цепи Маркова соответствует некоторый код в памяти 42 кодов.

Блок 12 ввода служит для загрузки тестов в блок 10 памяти тестов, модифицированной матрицы переходных вероятностей в память 40, кодов в память 42, управляющих данных в блок 5 сверхоперативной памяти и команд в память 45 блока 11 управления.

3 простейшем случае блок 12 содержит переключатели и кнопки, с помощью которых обеспечивается ручной выбор приемника данных, набор данных и их ввод. В более сложных вариантах построения этот блок может содержать устройства ввода информации с машинных носителей и устройства внешней памяти типа магнитных дисков и т.п.

Блок 13 вывода в наиболее простом исполнении имеет лишь средства индикаций регистра 53 состояния и триггеров 28 блока 6 обработки информации.

В более сложных случаях в него могут входить устройства выв ода на экран, на машинные носители информпции, а также средства сопряжения с ЭВМ.

Устройство работает следующим образом.

Перед началом проверки с помощью блока 12 ввода производится загрузка тестов и других данных. Приемник данных определяется управляющей информацией, записываемой из блока 12 ввода в регистр 47 команды.

Хранимые тесты загружаются в блок 10 памяти через блок 8 мультиплексоро и блок 6 обработки информации. При этом адреса ячеек блока 10 принимаются от блока 12 ввода в счетчик 51 адресов. Модифицированная матрица переходных вероятностей и коды загружаются в память 40 и 42 соответственно, также через блок В мультиплексоров и блок 6 обработки информации. Адреса памяти 40 модифицированной матрицы переходных вероятностей задаются счетчиками 38 столбцов и 39 строк, а адреса памяти 42 кодов - счетчиком 41 адресов. При зтом в память 40 загружается модифицированная матрица

мая следующим образом.

Пусть задана простая однородная цепь Маркова S {S;l| , i 0,n-l, с матрицей переходных вероятностей Р IIPivll, где Р,-, - вероятность перехода за один такт из состояния S. в состояние i,,n-l, Р-, ,, Y-Mi целое. Модифицирован- нал матрица переходных вероятностей А имеет вид А Ца j|| , ,n-, 0,. Строка А,- , соответствующая состоянию S, представляет собой числовую последовательность, состоящую из п серий, причем k-я серия состоит из номеров k, повторенных j ; раз.

t- -) Ч 8 8

m 3.

0

5

Например, при Р.

А, (О, О, 1, 1, 1, 1, 1, 2).

В память 42 кодов загружаются п двоичных N-разрядных наборов.

Последовательности сигналов синхронизации, маски и другие управляю- щяе данные поступают от блока 12 ввода в блок 5 сверхоперативной памяти (также через блоки 6 и 8), причем адреса ячеек блока 5. задаются непосредственно из регистра 47 команды. Программа, определяющая

последовательность операций устройства, в каждой такте проверки объекта загружается из блока 12 в память 45 команд с использованием для задания адресов счетчика 46 команд. После завершения ввода начинается сам процесс высокочастотной, проверки. Для этого в регистр 47 вводится команда пуска, которая записывает в счетчик 46 команд адрес начала программы в памяти 45, приводит в исходное состояние генератор 9 псевдослучайных тестов, сбрасывает счетчик 51 адресов блока 10 памяти тестов, приводит в исходное состояние генератор 37 псевдослучайных чисел, сбрасывает счетчик 39 строк и включает тактовый генератор 48.

При синхронной организации обмена с проверяемым объектом работа устройства в каждом такте t высокочастотной проверки сводится к следующей последовательности шагов, задаваемых командами программы, хранимой в памяти 45 блока 11 управления. Для определенности далее считается, что последовательность синхронизации рбъек- та состоит из двух наборов.

Шаг 1. При эТом происходит чтение данных из блока 5 сверхоперативной памяти: объединение очередного тестового набора X, получаемого из блока 10 памяти, с содержимым триггеров 28

блока 6 обработки, осуществляемое one- щая входы объектов, на которые долж- рацией X/( k V R - R, где k - кон- ны подаваться соответствующие разрястанта. из ЗУ 26 блока 5, определяющая входы проверяемого и эталонного объектов, на которые должны прикладываться соответствующие разряды набора X (в этих разрядах k, содержатся единицы), R - состояние триггеров 28 блока 6; передача маски входов синхронизации объектов из ЗУ 25 блока 5 в триггеры 16 блока 1 регистров; передача R в немаскированные триггеры 14 данных блока 1; передача из ЗУ 27 блока 5 в триггеры 15 коммутации блог ка 1 данных для включения каналов блока 1, связанных с двунаправленными выводами объектов, на выдачу состояния триггеров 14 на обЬекты; сдвиг в регистре 43 генератора 37 для получения очередного псевдослучайного

ДЫ набора Y (в этих разрядах k содержатся единицы); прием следующего состояния цепи Маркова из памяти

40 40 модифицированной матрицы переходных вероятностей в счетчик 41 адресов памяти кодов и в счетчик 39 строк и запуск чтения кода из памяти 42 кодов.

Шаг 4. Осуществляется: чтение данных из блока 5 сверхоперативной памяти; прием в блок 6 обработки информации набора Z для такта t + 1 от формирователя 7 и выполнение операции

5Q ZAkj Y R , где k - константа из ЗУ 26, определяющая входы объектов, на которые должны подаваться соответствующие разряды набора Z (в этих разрядах k. содержатся единицы);

45

числа, формирование очередного псев- передача из ЗУ 25 блока 5-маски срав дослучайного числа в генераторе 9 тес- нения в триггеры 16 блока 1; сравне- тов для получения очередного псевдослучайного тестового набора для такта t + 1 .

ние состояния незамаскированных выводов проверяемого и эталонного объек тов в блоке 4 (при равенстве - пе рег

Шаг 2, Происходит: чтение данных из блока 5 сверхоперативной памяти, передача маски информационных вхо- дов объектов из ЗУ 25 блока 5 в триггеры 16 блока I; передача первого набора синхронизации из ЗУ 26 блока 5 в незамаскированные .триггеры 14 данных блока 1 и соответственно на вхог

Ды объектов; подготовка следующего адреса в счетчике 51 и запуск чтения тестового набора из блока 10 памяти для такта t + 1; передача псевдослучайного числа из генератора 37 псевдослучайных чисел в счетчик 38 столбцов и запуск чтения из памяти 40 модифицированной матрицы переходных вероятностей для определения следующего состояния цепи.

I lar 3. Осуществляется: чтение данных из блока 5 сверхоперативной памяти; передача второго набора синхронизации из ЗУ 26 блока 5 в незамаскированные триггеры 14 данных блока

1 и соответственно на входы объектов; передача из ЗУ 27 блока 5 в триггеры 15 блока 1 данных для включения ка- налов блока 1, связанных с двунаправленными выводами объектов на

прием их реакции; прием в блок обработки псевдослучайного набора Y от блока 9 для такта t + 1 и выполнение операции Y Л kj R, где k - константа из ЗУ 26 блока 5, определяю-

ДЫ набора Y (в этих разрядах k содержатся единицы); прием следующего состояния цепи Маркова из памяти

40 модифицированной матрицы переходных вероятностей в счетчик 41 адресов памяти кодов и в счетчик 39 строк и запуск чтения кода из памяти 42 кодов.

Шаг 4. Осуществляется: чтение данных из блока 5 сверхоперативной памяти; прием в блок 6 обработки инфорации набора Z для такта t + 1 от формирователя 7 и выполнение операции

ZAkj Y R , где k - константа из ЗУ 26, определяющая входы объектов, на которые должны подаваться соответствующие разряды набора Z (в этих разрядах k. содержатся единицы);

передача из ЗУ 25 блока 5-маски срав нения в триггеры 16 блока 1; сравне-

ние состояния незамаскированных выводов проверяемого и эталонного объектов в блоке 4 (при равенстве - пе рег

ход к Diai-y 1, при неравенстве сигналов хотя бы одной пары выходов - установка разряда ошибки регистра состояния 53 и останов).

Каждый из указанных шагов задается соответствующей ему одной командой программы внутриконтактного управ ления, читаемой блоком 11 из памяти 45. Прочитанная команда принимается в регистр 47, а в счетчике 46 одновременно формируется адрес следующей команды, т.е. выполнение текущей команды совмещается по времени с чтением следующей.

Каждая команда содержит адресное поле, в котором размещаются ЗУ 25-27

блока 5 сверхоперативной памяти, поле кода операции блока 6 обработки, поле управления блоком 8 мультиплек с ров и управляющие разряды, с помощью которых задается вьщача стробирующих сигналов в блоки 5 и 6, в блок 1 регистров, в формирователь 7 и генератор 9 псевдослучайных тестов. Эти сигналы вырабатываются первой группой 49 элементов И под действием импульсов тактового генератора 48. Сигналы управления счетчиком 46 команд, счетчиком 51 адресов, регистром 52 управления и блоком 10 памяти тестов формируются аналогичным образом второй группой 50 элементов И.

В регистр 52 управления записываются управляющие разряды слов, читаемых из блока 10. При соответствзпо Щем признаке в команде, находящейся в регистре 47, Содержимое регистра 52 передается в счетчик 46 команд. Таким образом, при выборке теста из ;блока 9 можно передавать управление разным программам, хранимьм в памяти 45, что позволяет изменять последовательность и состав операций устройства на разных этапах проверки объекта. Последовательность команд, в пределах одной программы может изменяться с помощью команд условных переходов по результату сравнения, полученному от блока 4, что необходимо например, при асинхронной организации обмена с проверяемым объектом, когда в каждом такте проверки добавляются шаги, связанные с анализом состояния управляющих выходов объекта. При выполнении команд условных и безусловных переходов новое состояние счётчика 46 формируется не увеличением его предыдущего состояния на

Q 5

соответственВБОДЯТСЯ и

5

0

5

о где d

0

45

0

единицу, а путем передачи н него адреса из регистра 47.

Дополнительные шаги и но команды в программе тогда, когда требуется модифицировать тестовый набор в блоке 6 обработки информации перед подачей его на входы объекта, при записи реакций объекта в блок 10 памяти тестов и в некоторых других случаях. При описанном ранее построении блок 6 обработки информации позволяет выполнить следующие операции :

6i Л ft -- Rj о( V /i - RJ

d А (1 )Л R -- R; cf Л Л ) V R R; 0 А ) ®R -. R,

- операнд блока 5 сверхоперативной памяти или вектор из всех единиц;;

/5 - операнд из блока 10 памяти тестов, от формирователя 7 .псевдослучайной последовательности от генератора 9 псевдослучайных тестов, от блока 4 сравнения или вектор из всех единиц.

Состояние R триггеров 28 блока 6 обработки информации может быть записано в блок пгшяти тестов или в блок сверхоперативной и использоваться в качестве операндов ct. и ft в последующих операциях.

При показанном на фиг.2 построении блока 1 регистров и блока 4 сравнения можно изменять вид данных, получаемых от блока 4, в зависимости от состояния тех триггеров J 4 блока 1, которые соответствуют выходам проверяемого объекта.

Если в эти триггеры записаны эталонные значения выходных сигналов, то блок 4 выдает вектор ошибок, в котором единигды соответствуют выходам объекта, на которых обнаружена ошибка, если в триггеры 14 записана константа Нуль, то на выходы блока 4 передается фактическое состояние выходов объектов, если константа Единица - то инверсия этого состояния ..

55

Формула изобр

1.Устройство контроля сорных блоков по авт.св. отличающееся

11

с целью повышения поЛноты и эффективности контроля, оно содержит формирователь псевдослучайной последовательности, группа управляющих входов ко- торого соединена с первой группой управляющих выходов блока управления группа информационных входов формирователя псевдослучайной последовательности соединена с группой выходов блока обработки информации, группа выходов формирователя псевдослучайной последовательности соединена с пятой группой информационных входов блока мультиплексоров.

2.Устройство по п., о т л-и - чающееся тем, что формирователь псевдослучайной последователь- .ности содержит генератор псевдослуча -.ных чисел, счетчик столбцов, память модифицированной матрицы переходных вероятностей, счетчик строк, память кодов, счетчик адресов памяти кодов, причем вход пуска генератора псевдо случайных чисел, входы синхронизации счетчиков столбцов, строк и адресов памяти кодов, входы записи памяти

32320

12

ю15

- 20 25

модифицированной матрицы переходных вероятностей -и памяти кодов образуют группу управляющих входов формирователя псевдослучайной последовательности, выход генератора псевдослучайных чисел соединен с информационным входом счетчика столбцов, выход которого соединен с входом адреса столбца памяти модифицированной матрицы переходных вероятностей, вход адреса строки которой соединен с выходом счетчика строк, выход памяти модифицированной матрицы переходных вероятностей соединен с информационными входами счетчиков строк и адресов памяти кодов, группа информационных входов формирователя псевдослучайной последовательности подключена к информационным входам памяти модифицированной матрицы переходных вероятностей и памяти кодов, выход счетчика адресов памяти кодов соединен с адресным входом памяти кодов, выход которой образует группу выходов формирователя псевдослучайной последовательности.

От 10 OaJ ОтП От9 VuZ.l

77

От 6 -f

к5 Фи&.З

J9

I

/fff

Z7m//

/.

Л 1.5.6,7.8.9

От 12

/r/J От

К10

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля микропроцессорных блоков | 1988 |

|

SU1531099A1 |

| Устройство контроля микропроцессорных блоков | 1982 |

|

SU1042023A1 |

| ФОРМИРОВАТЕЛЬ ТЕСТОВ | 1991 |

|

RU2010316C1 |

| Формирователь тестов | 1987 |

|

SU1552185A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1260961A1 |

| Устройство микропрограммного управления | 1988 |

|

SU1667070A1 |

| Генератор испытательных последовательностей | 1987 |

|

SU1543396A1 |

| Формирователь тестов | 1989 |

|

SU1661769A1 |

| Устройство для формирования тестов | 1987 |

|

SU1429121A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1383368A1 |

Изобретение относится к вычислительной технике, в частности к средствам контроля цифровых объектов. Изобретение позволяет повысить полноту и эффективность контроля микропроцессорных блоков. Перед началом проверки с помощью блока 12 ввода производится загрузка хранимых тестов в блок 10 памяти, модифицированной матрицы переходных вероятностей и кодов, из которых генерируется марковская последовательность - в память формирователя 7 псевдослучайной последовательности, сигналов синхронизации и масок - в блок 5 сверхоперативной памяти, программы проверки объекта контроля - в память блока 1I управления. В процессе высокочастотной проверки в блоке 6 обработки ин формации осуществляется формирование очередного входного воздействия путем суперпозиции хранимого теста из блока 10 памяти, псевдослучайного теста(Л С kirt Г-л Ч. JOO Ьо to Од ND 1Ч

Редактор Е.Папп

Составитель Д.Ванюхин ТехредЛ.Сердюкова Корректор И.Муска

Заказ 3834/45Тираж 672 Подписное

ВНШШИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г, Ужгород, ул. Проектная, 4

| Устройство контроля микропроцессорных блоков | 1982 |

|

SU1042023A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-08-23—Публикация

1986-04-03—Подача