ня, отличающееся тем,что, с целью повьппенйя быстродействия, в него введены селекторы первого, второго и третьего уровней, первый селектор адреса команды, второй селектор адреса команды, селектор третьего слагаемого, блок связи с операционным устройством и блок .связи с устрой ством управления памятью, выход запро са которого соединен с первым запросным входом устройства, а вход адреса с первым информационным входом второго селектора адреса команд и выходом сумматора адреса, третий вход которого соединен с выходом селектора третьего слагаемого, вход абсолютного адреса которого соединен с входами абсолютного адреса блока связи с операционнь1м устройством и блока связи с устройством управления памятью и подключен к выходу /абсолютного адреса, блока транслшГйи адреса, информационный вход которого соединен с информационным входом блока связи с устройством управления памятью, вторым информационным входом второго селектора адреса команд, и информационным входом блока связи с операционным устройством, выход которого соединен с вторым запросным выходом устройства, а вход управляющей информации соединен с выходом регистра командной информации второго урйв ня, первыми информационными входами селекторов первого, второго и третьего уровней, вторые информационные входы этих селекторов соединены с выходом регистра командной информации третьего уровня, вход которого соединен с выходом селектора третьего, уровня, выход селектора второго уровня соединен с входом регистра командной информации второго уровня, третий информационный вход которого соединен с выходом регистра командной информации первого уровня и входом управляющей информации селектора третьего слагаемого, первый информационный вход которого соединен с выходом счетчика предварительной накачки блока счетчиков, выход идентиЛикатора которого соединен с первым информационньп входом селектора первого .уровня, выход которого соединен с входом регистра командной информации первого уровня, а второй информационный вход - с информационным выходом блока буЛрризации команд, выход первого

селектора адреса команды соединен с входами адреса команды блока буеризации команд и блока локальной памяти, вход адреса которого соедиен с первым входом первого селектора адреса команды, второй вход которого соединен с выходом адреса команды блока счетчиков, выходы нкроприказов блока микропрограммного управления подключены к соответствуюим входам управления селекторов первого, второго и третьего Уровней, второго селектора адреса команд, сеектора третьего слагаемого, блока связи с операционным устройством и блока связи с устройством управления памятью, выход признака ветвления которого соединен с входом признака ветвления блока микропрограммного управления, а выход маркера записи операнда два соединен с входом маркера записи операнда два блока Локальной памяти.

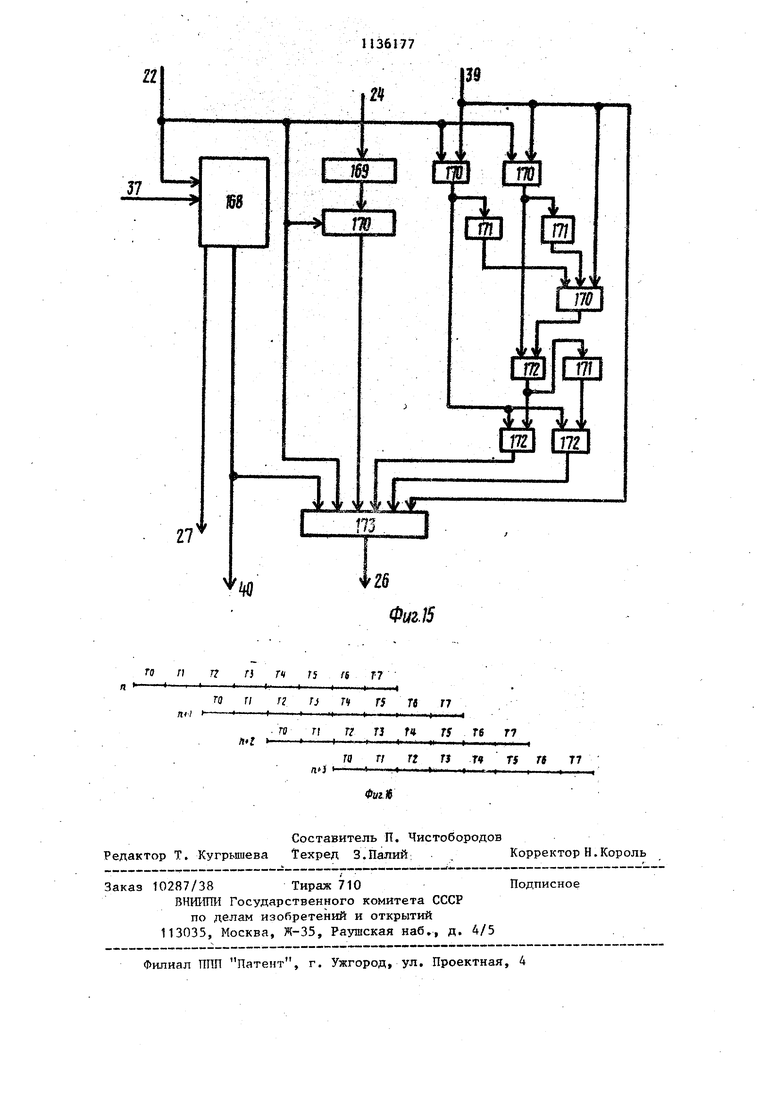

2,Устройство по п. 1, о т л ич а ю.щ е е с я тем, что блок С1аязи с операционным устройством содержит регистр маски программы слова состояния программы и регистр запросного слова в операционное устройство, выход которого является выходом блока, а вход управления соединен с вхо-дом управления регистра маски и входом управления блока, информационный вход регистра маски соединен с информационньм входом блока, а выход - с входом маски регистра запросного слова в операционное устройство, вход абсолютного адреса которого соеинен с входом абсолютного адреса бло ка.

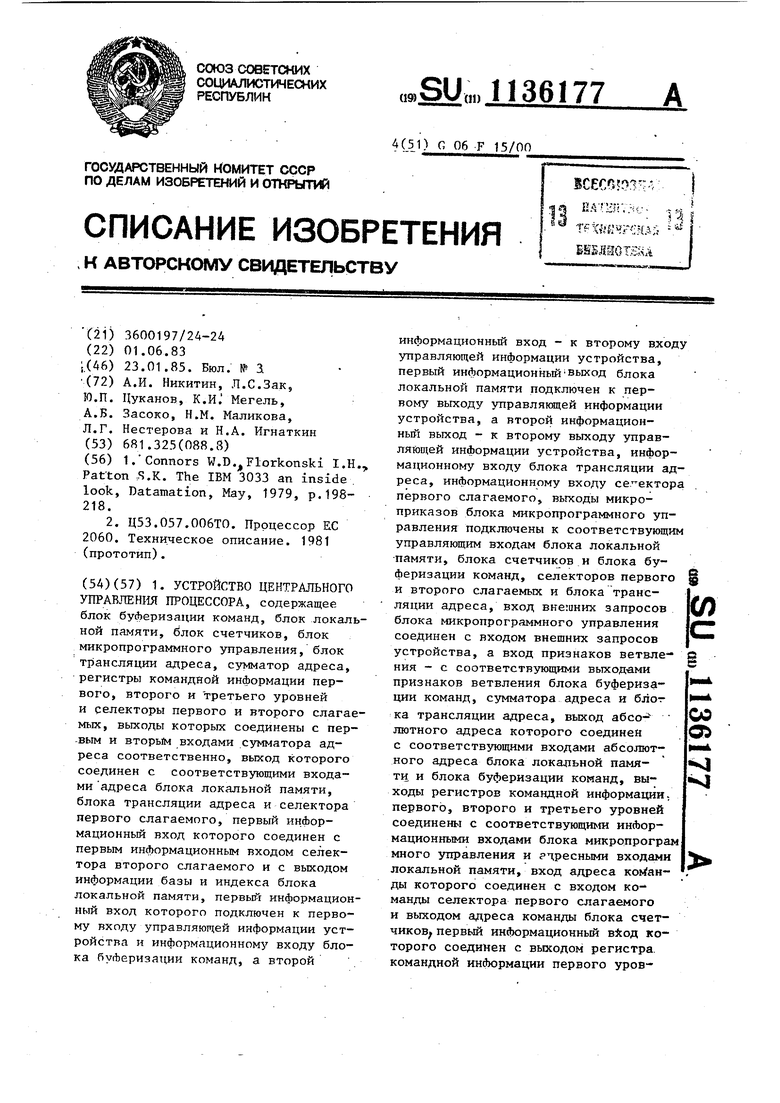

3,Устройство по п. 1, о т л и- чающееся тем, что блок связи с устройством управления памятью содержит блок памяти маркеров, регистр ключа защиты из слова состояния программы, четыре элемента И, три элемента НЕ, три элемента ИЛИ и регистр запросного слова в устройство управления памятью, выход которого является выходом запроса блока, а вход абсолютного адреса подключен к входу абсолютного адреса блока, первому бходу первого элемента И, первому входу второго элемента И;И первому входу третьего элемента И, второй вход которого соединен с втоым входом второго элемента И, первым входом четвертого элемента И, управляющим входом блока памяти мар-j

керов, управляющим входом регистра запросного слова в устройство управления памятью и управляющим входом блока, вход адреса блока соединен с входом адреса блока памяти маркеров, выход маркера которого соединен с выходом маркера записи два блока и входом маркера регистра запросного слова в устройство управления памятью, вход защиты которого соединен с выходом четвертого элемента И, второй вход доторого соединен с выходом регистра ключа защиты из слова состояния программы, вход которого соединен с информационным входом блока, выход ветвления которого соединен с выходом приз наков блока памяти маркеров, выход

6177

третьего элемента И соединен с входом первого элемента НЕ и с первыми входами первого и второго элементов ИЛИ, выходы которых подключены к первому и второму кодовым входам регистра запросного слова в устройство упр:авления памятью соот- . ветственно, второй вход первого элемента ИЛИ соединен с выходом третьего элемента ИЛИ и входом второго элемента НЕ, выход которого соединен с . вторым входом второго элемента ИЛИ, выход первого элемента НЕ соединен с вторым входом первого элемента И, третий вход которого соединен с выходом третьего элемента НЕ, вход которого соединен с выходом второго элемента И и вторым входом третьего элемента ИЛИ,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство буферизации команд процессора | 1983 |

|

SU1092506A1 |

| Устройство для сопряжения памяти с процессором | 1982 |

|

SU1136176A1 |

| Арифметическо-логическое устройство для обработки десятичных данных | 1984 |

|

SU1244660A1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Процессор с совмещением операций | 1982 |

|

SU1138805A1 |

| Процессор с микропрограммным управлением | 1975 |

|

SU525956A1 |

| Устройство для сопряжения каналов ввода-вывода с устройством управления оперативной памятью | 1984 |

|

SU1265788A1 |

| Имитатор канала | 1991 |

|

SU1839250A2 |

| Устройство для буферизации команд | 1991 |

|

SU1789982A1 |

| Многоуровневое устройство для коммутации процессоров в многопроцессорной вычислительной системе | 1984 |

|

SU1187174A1 |

1. УСТРОЙСТВО ЦЕНТРАЛЬНОГО УПРАВЛЕНИЯ ПРОЦЕССОРА, содержащее блок буферизации команд, блок локальной памяти, блок счетчиков, блок микропрограммного управления, блок трансляции адреса, сумматор адреса, регистры командной информации первого, второго и третьего уровней и селекторы первого и второго слагаемых, выходы которых соединены с пер-вым и вторым входами сумматора адреса соответственно, выход которого соединен с соответствующими входами адреса блока локальной памяти, блока трансляции адреса и селектора первого слагаемого, первый информационньй вход которого соединен с первым информационным входом селектора второго слагаемого и с выходом информации базы и индекса блока локальной памяти, первый информационный вход которого подключен к первому входу управляющей информации устройства и информационному входу блока буферизации команд, а второй информационный вход - к второму входу управляющей информации устройства, первый информационныйВЫХОД блока локально памяти подключен к первому выходу управляющей информации устройства, а второй информационный выход - к второму выходу управляющей информации устройства, информационному входу блока трансляции адреса, информационному входу сегектора первого слагаемого, выходы микроприказов блока микропрограммного управления подключены к соответствующим управляющим входам блока локальной памяти, блока счетчиков и блока буферизации команд, селекторов первого и второго слагаемых и блока трансляции адреса, вход внешних запросов блока микропрограммного управления соединен с входом внешних запросов устройства, а вход признаков ветвления - с соответствующими выход-ами признаков ветвления блока буферизации команд, сзжматора адреса и блоСО ка трансляции адреса, выход абсо- ф лютного адреса которого соединен с соответствующими входами абсолют J ного адреса блока локальной памяти и блока буферизации команд, выходы регистров командной информации, первого, второго и третьего уровней соединены с соответствующими инАормационными входами блока микропрограм много з правления и чресными входами локальной памяти, вход адреса кo aнды которого соединен с входом команды селектора первого слагаемого и выходом адреса команды блока счетчиков; первый информационный которого соединен с выходом регистра командной информации первого уров

Изобретение относится к области вычислительной техники и предназначено для работы в составе мультипроцессора быстродействующих ЭВМ.

Известно устройство центрального управления процессора .с несколькими уровнями совмещения, содержащее блок выборки команд, регистр команд дешифратор команд, буферы очереди команд, буферы адресов операндов, блок управления выборкой команд и сумматор РЗ .

Связь между блоками асинхронная, управление блоками схемное. Асинхронность связей и схемное управление приводят к усложнению аппаратуры Блок выборки команд содержит три группы по четьфе регистра в каждой, что недостаточно для хранения команд программных циклов и поэтому приводит к уменьшению быстродействия при вьтолнении программных циклов.

Наиболее близким к предлагаемому по технической сущности является устройство центрального управления процессора цифровой вычислительной системы, содержащее буфер команд, регистры команд первого, второго и третьего уровней, блок местной памяти, регистры операндов, двухвходовой сумматор, счетчик команд, регистр адреса операндов, блок

микропрограммного управления и блок блокировки уровней совмещения, причем вход буфера команд является входом устройства, а выход соединен с входом регистра команд первого уровня, второй - к входу двухвходового сумматора, а третий к входу регистра команд второго уров ня, выход которого соединен с входом регистра команд третьего уровня, выход которого является выходом устройства, адресные входы блока местной памяти соединены с выхода-ми регистров команд первого и третьего уровней, управляющий вход - с выходом блока микропрограммного управления, а выход - с входами регистров операндов, выходы которых являются выходами информации устройства и подключены к входам двухдходового сумматора, выход которого подключен к входу регистра адреса операндов, выход которого является выходом устройства, вход блока блокировки уровней совмещения является входом устройства, а выход соединен с входом. блока микpoпpoгpa мнoгo управления, выходы которого соединены с управляющими входами соответстве1тно регистра адреса операндов, буфера команд, регистров первого, второго и третьего уровней, регистров one-.

рандов, двухвходового сумматора и счетчика команд, выход которого является вькодом устройствй QjJ .

Однако для модификации адреса используется двухвходовой сумматор вместо трехвходового, что увеличивает время выполнения модификации адреса в командах RX формата (типа принятых в ЕС ЭВМ), Отсутствне буфера командных слоев достаточной емкоети приводит к потере времени при выполнении команд передачи управления.

Целью изобретения является повышение быстродействия процессора,

Цель достигается тем, что в устройстве центрального управления процессора, содержащем блок буферизации

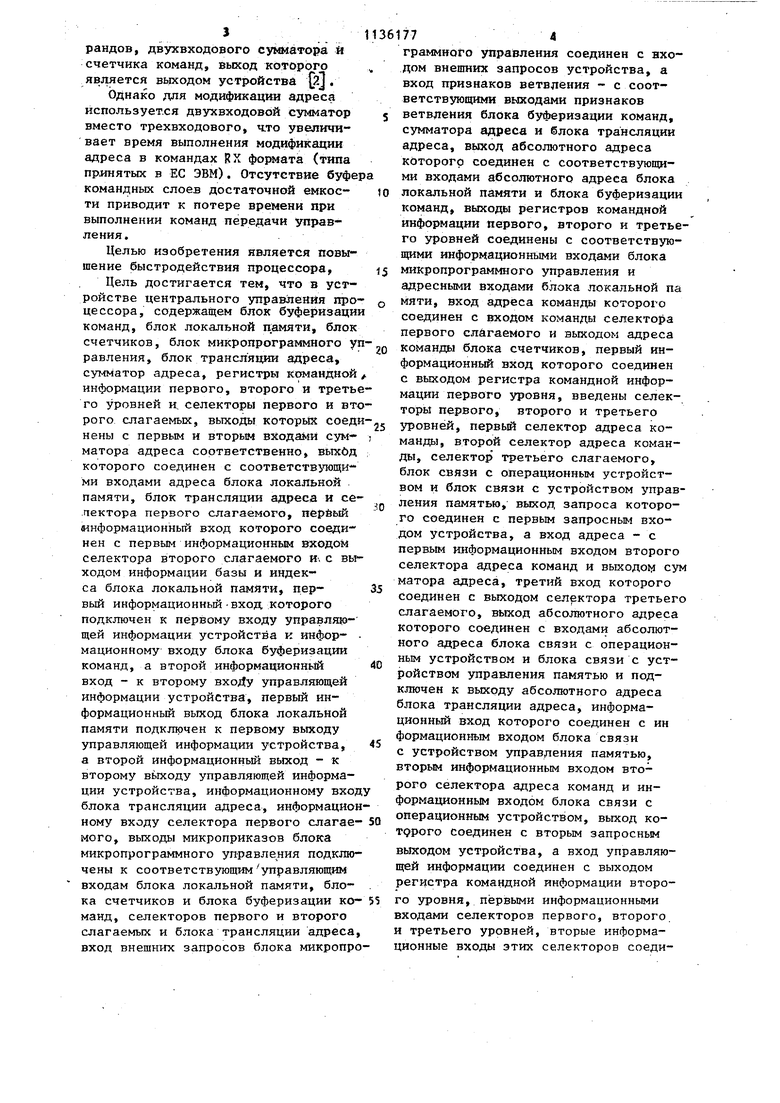

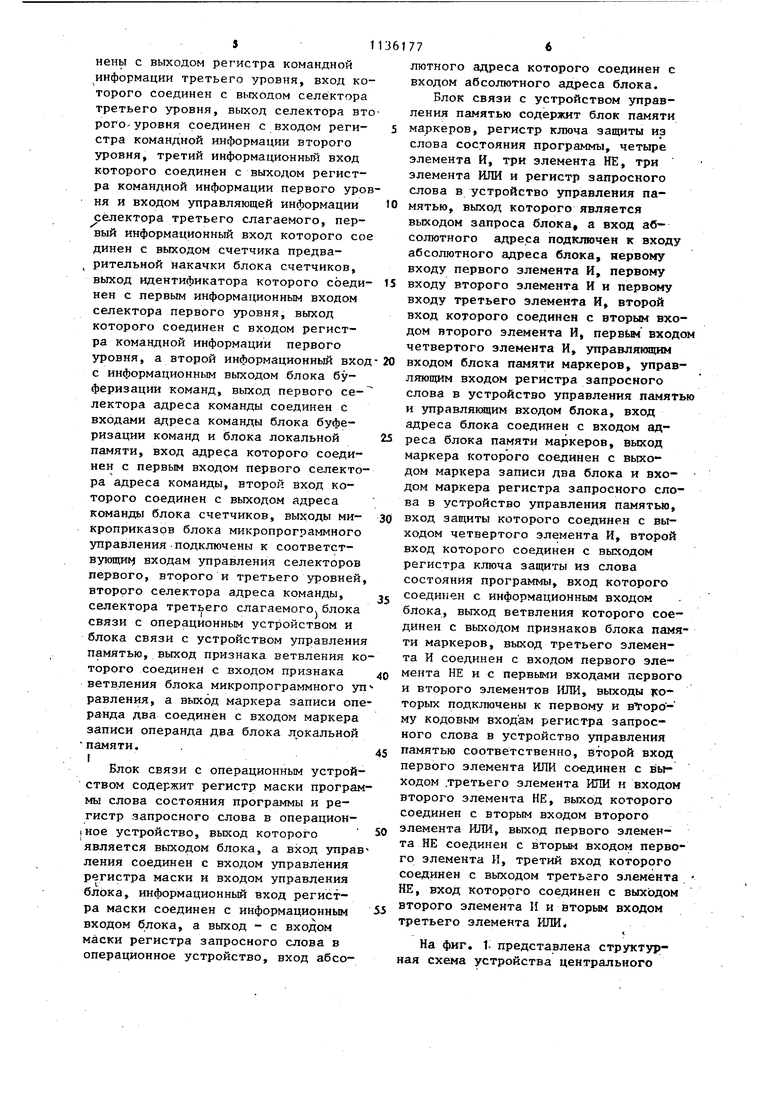

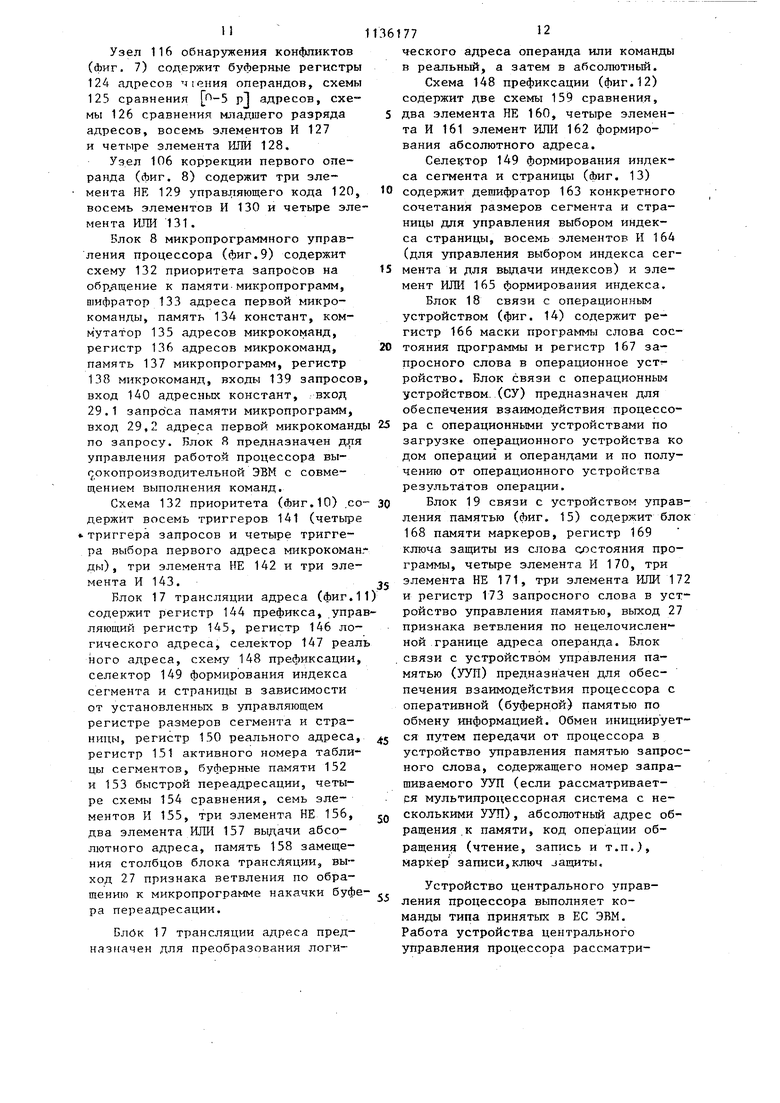

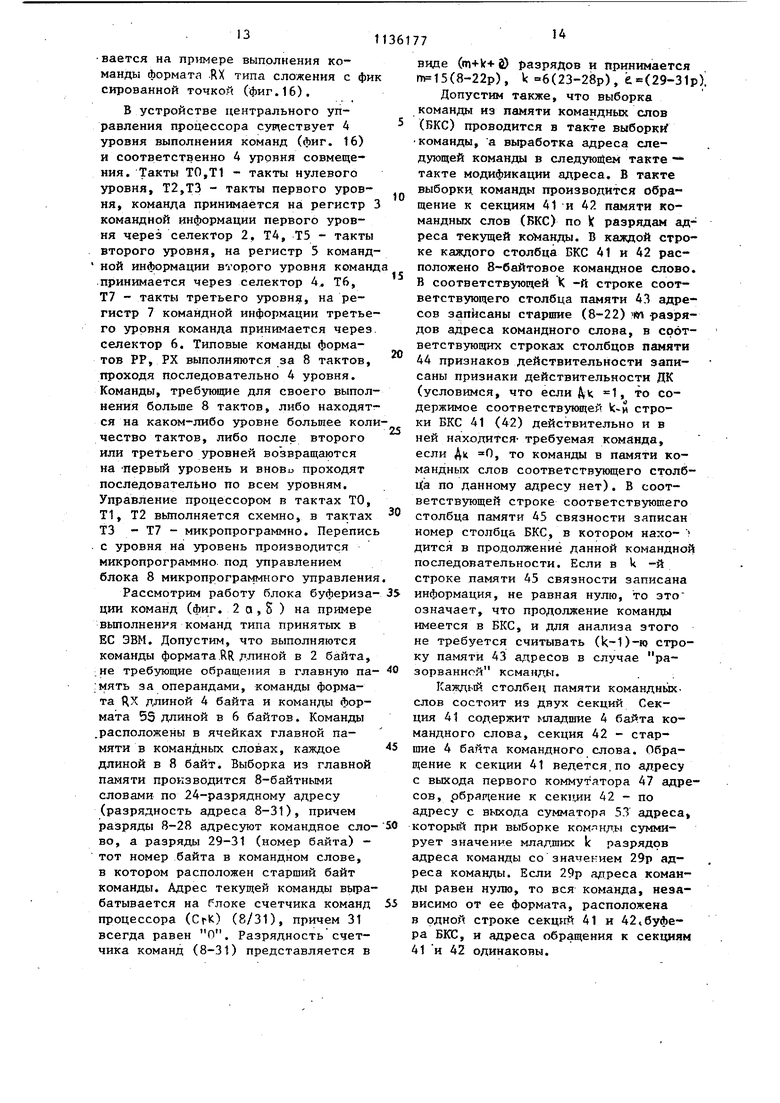

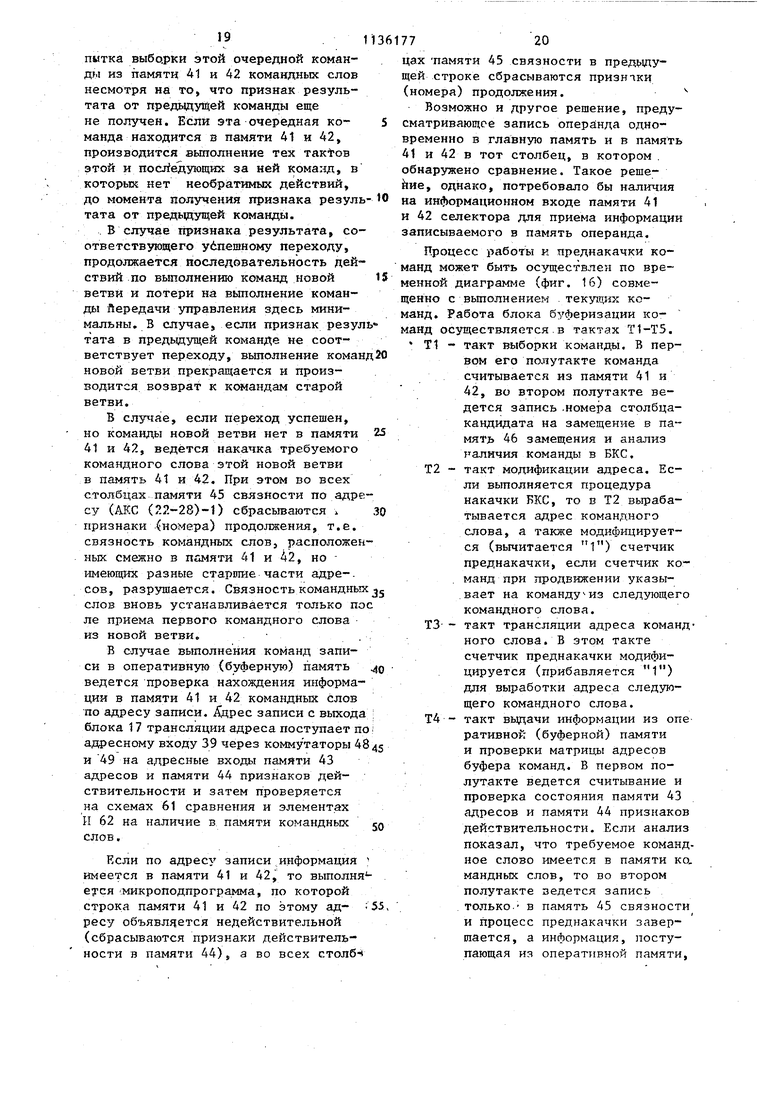

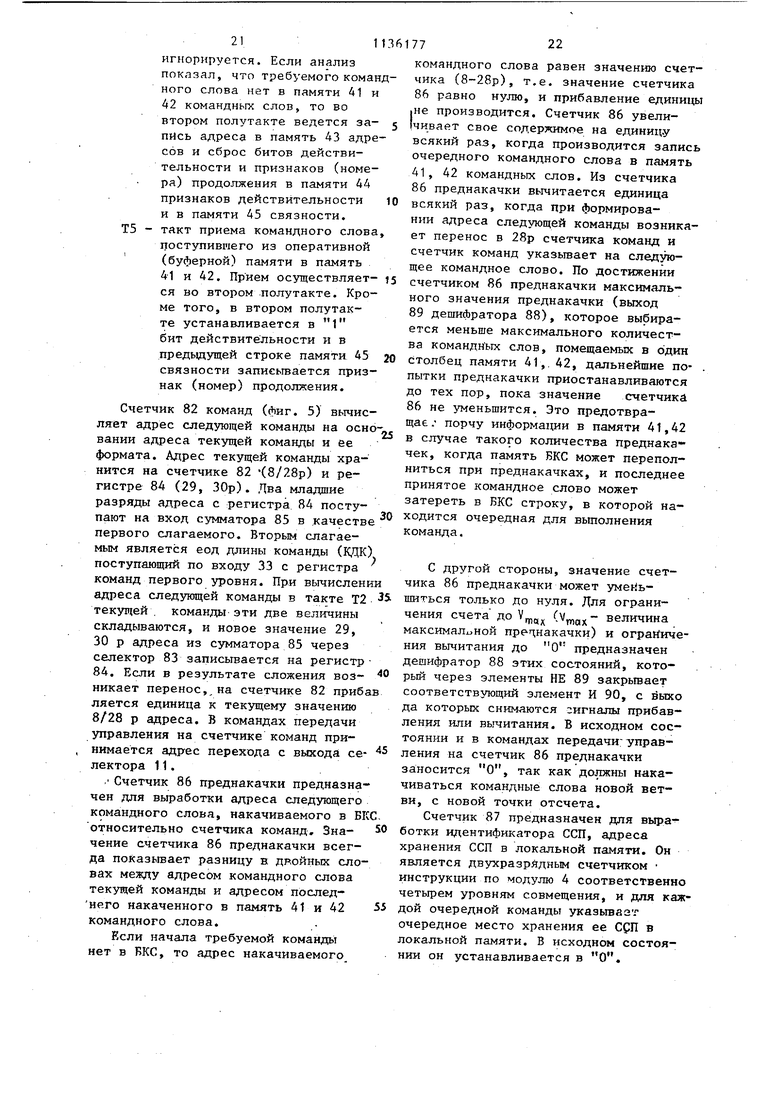

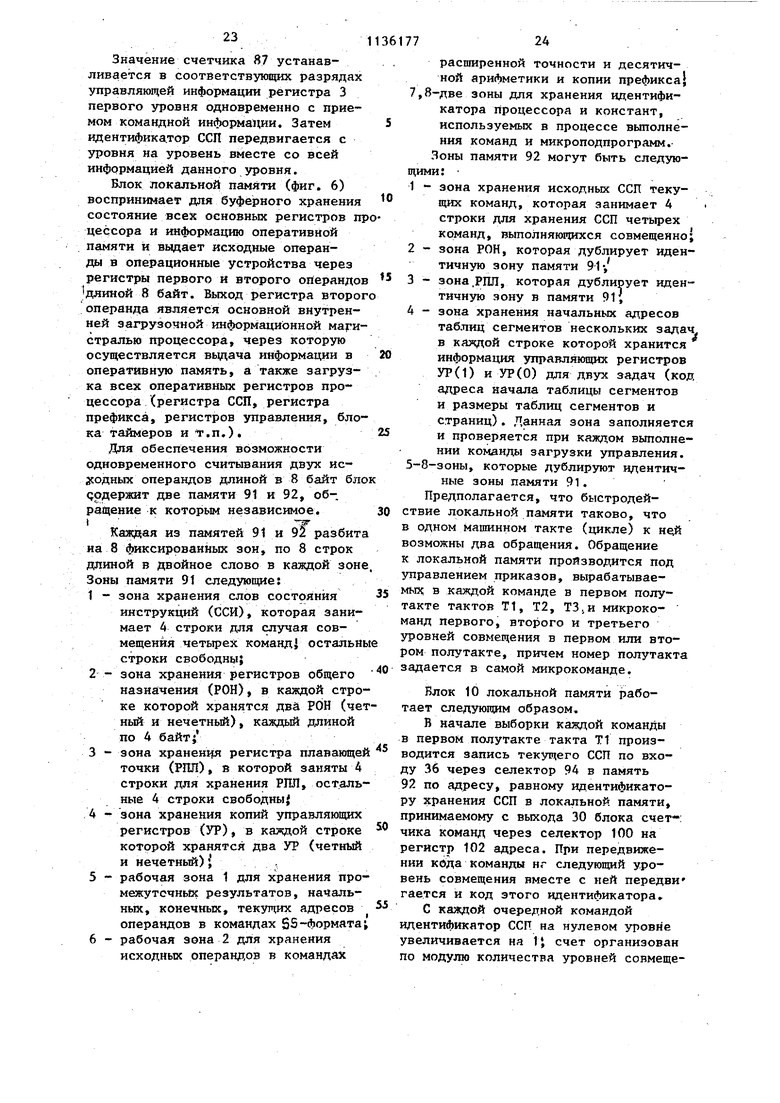

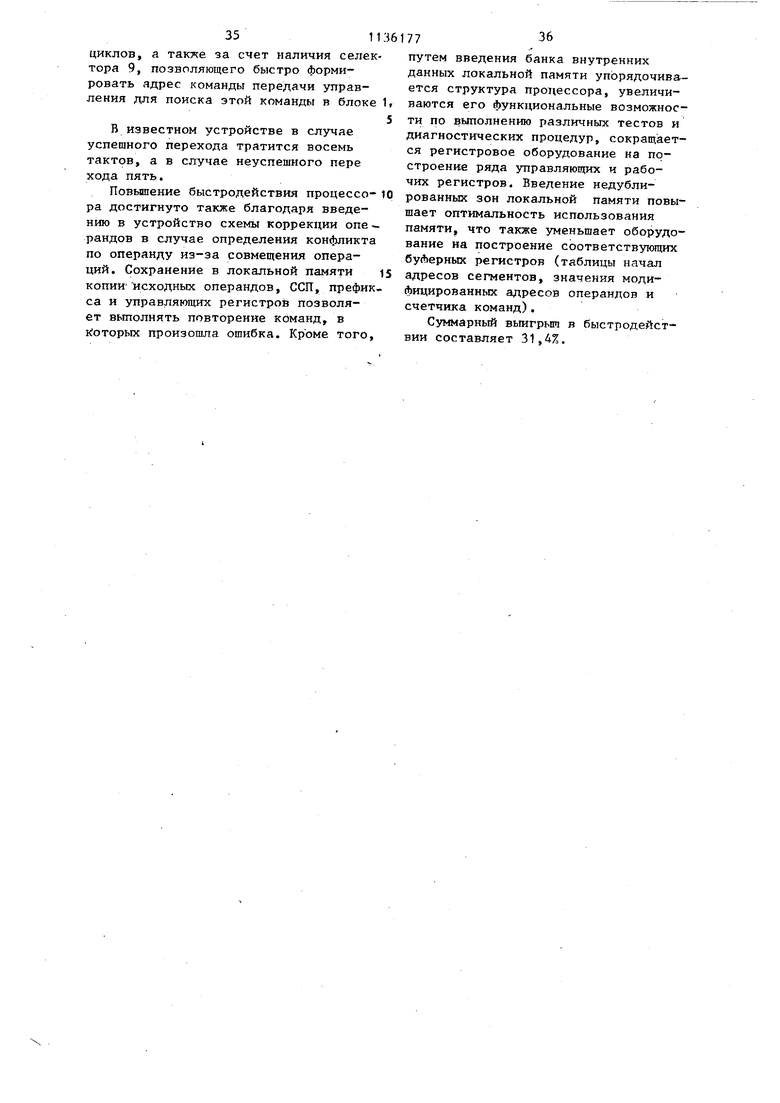

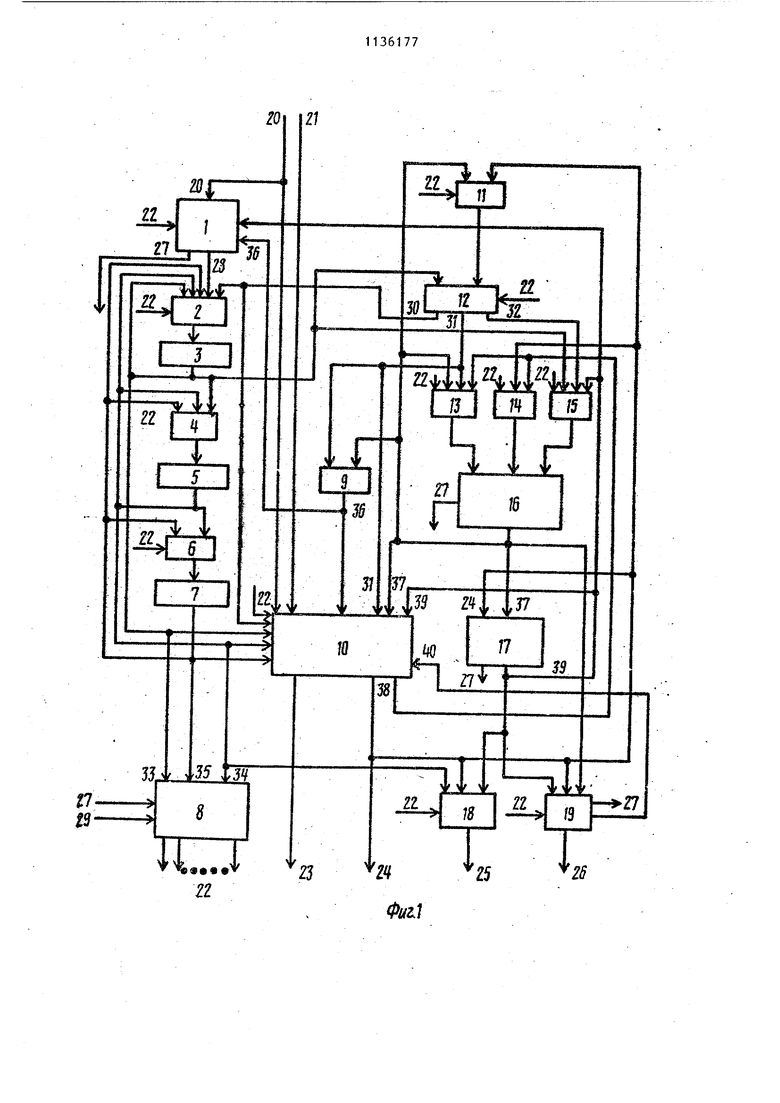

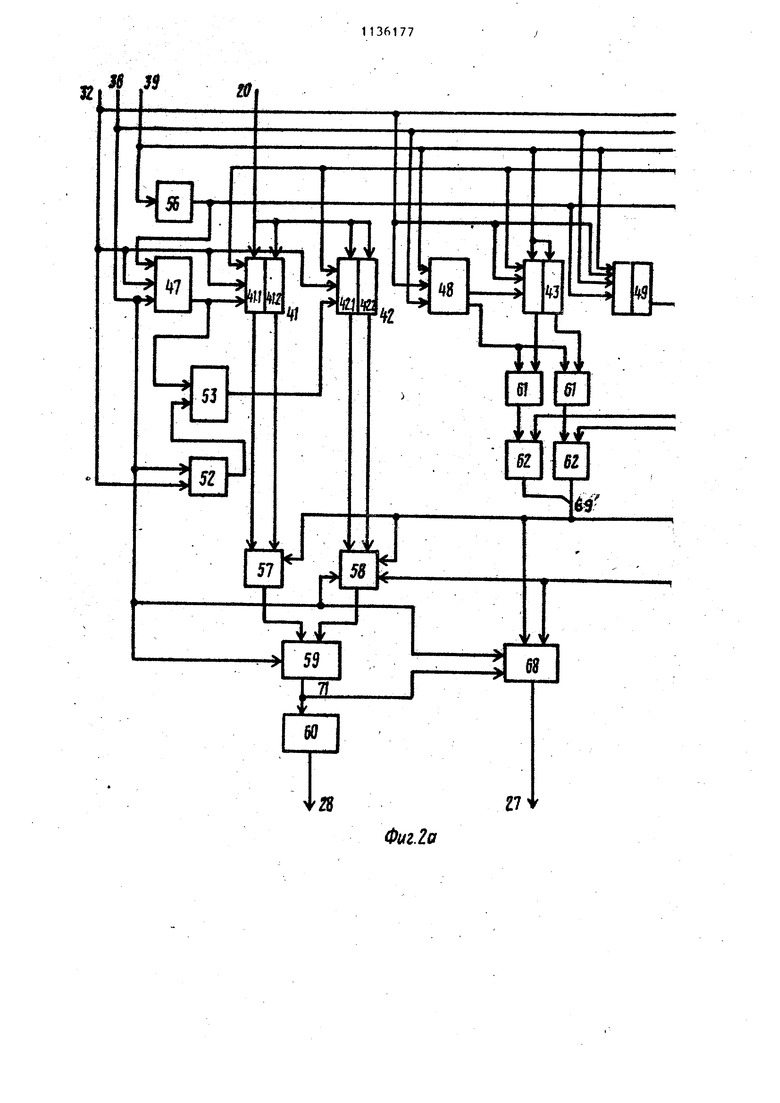

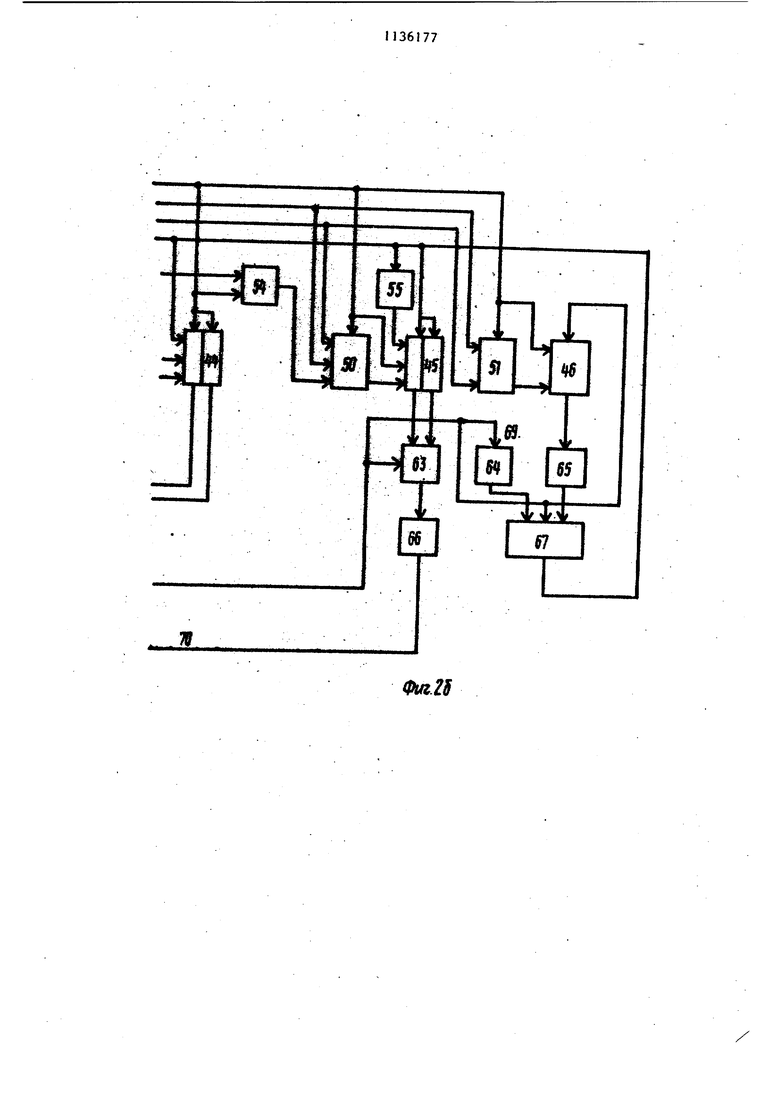

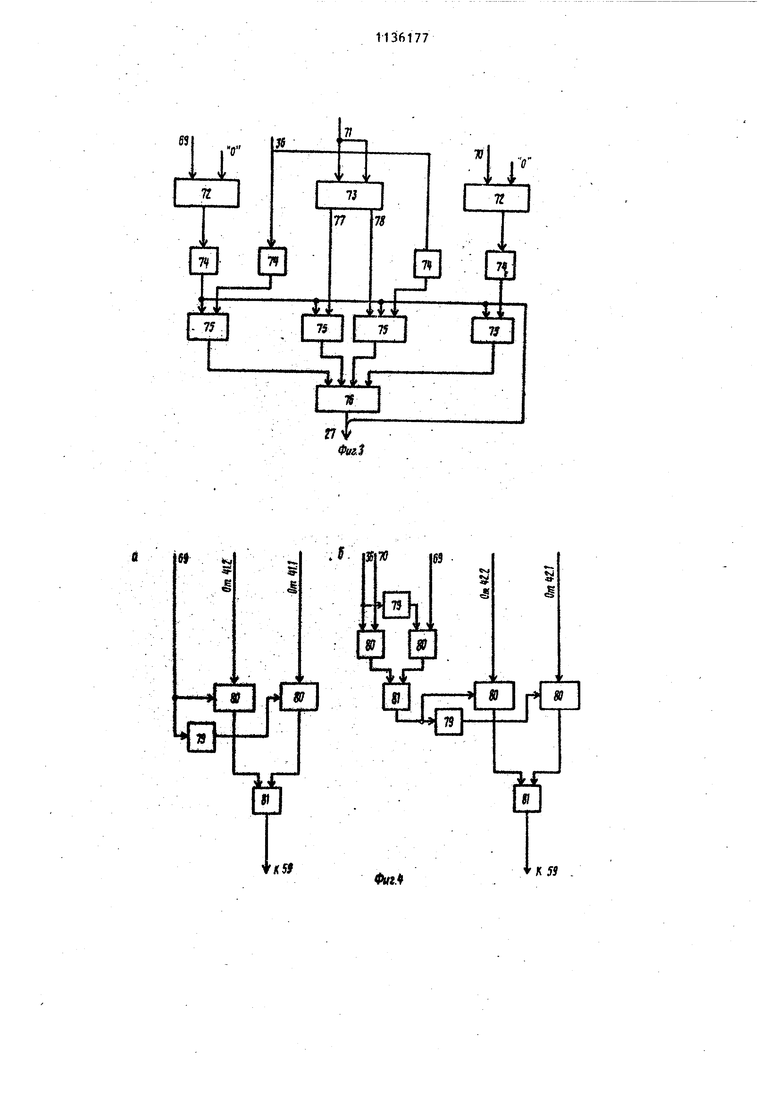

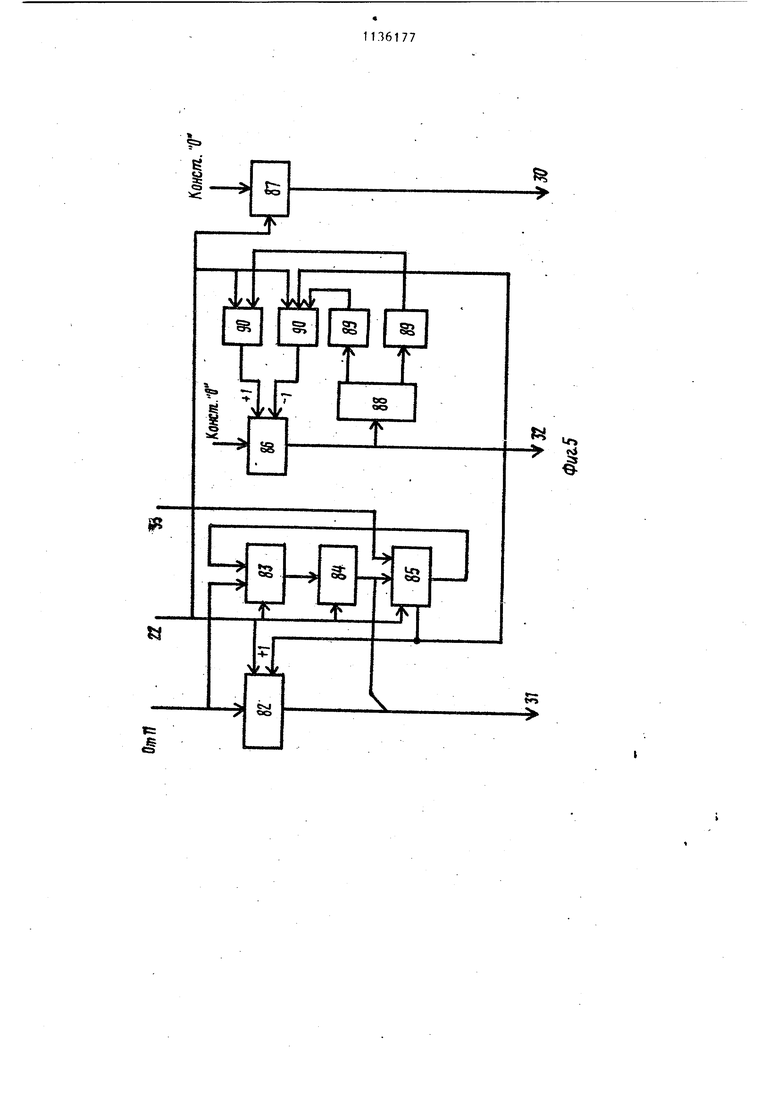

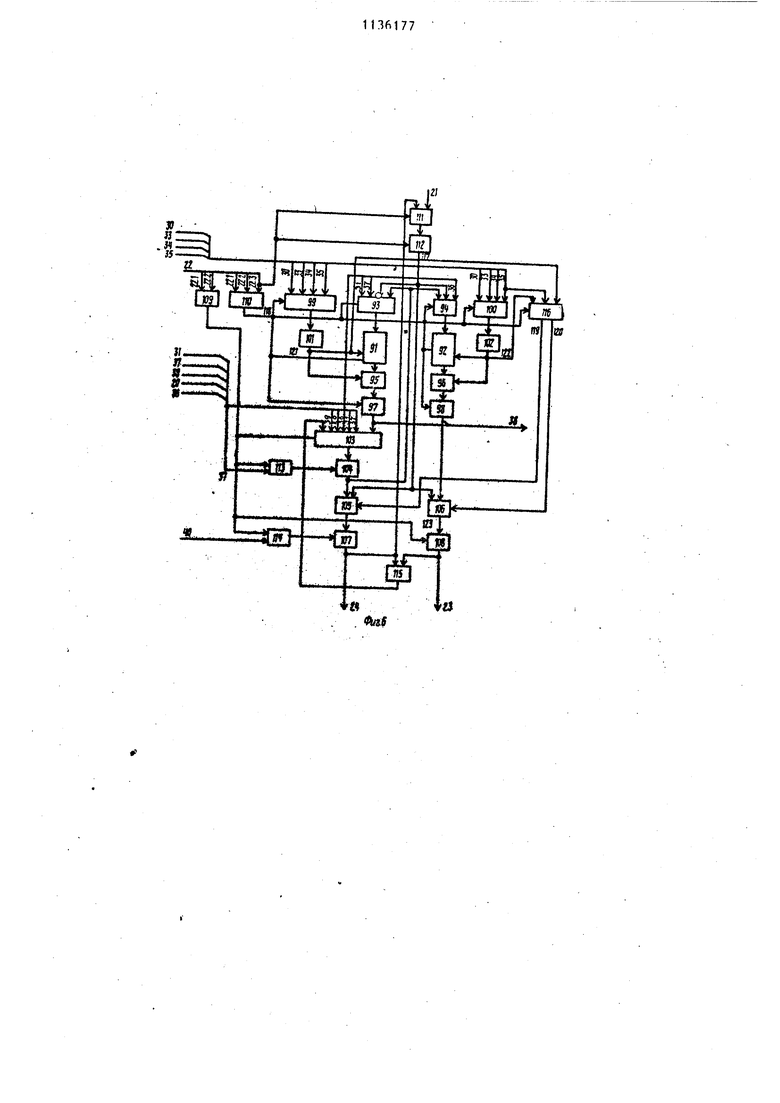

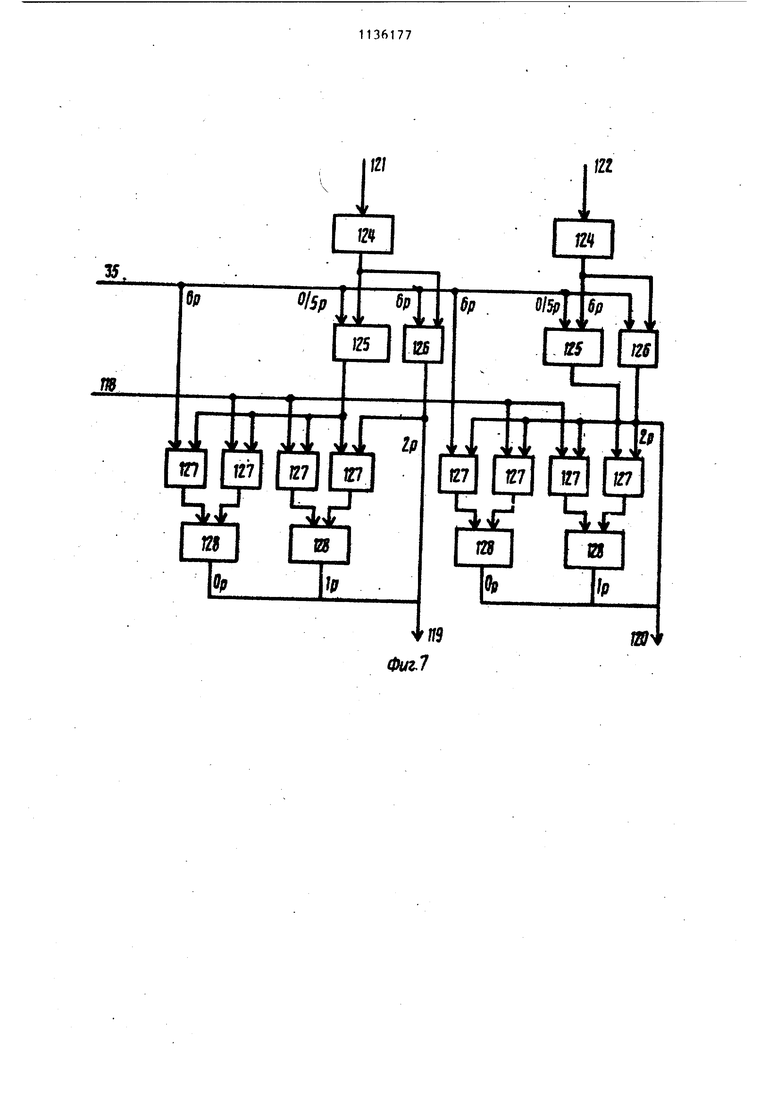

команд, блок локальной п.амяти, блок счетчиков, блок микропрограммного управления, блок трансляции адреса, сумматор адреса, регистры командной /, информации первого, второго и третьего уровней и, селекторы первого и второго слагаемых, выходы которых соединены с первым и вторым входами сумматора адреса соответственно, вьпсбд которого соединен с соответствующими входами адреса блока локальной памяти, блок трансляции адреса и селектора первого слагаемого, пёрбый «информационный вход которого соединен с первым информационным входом селектора второго слагаемого и-, с выходом информации базы и индекса блока локальной памяти, первый информационныйвход которого подключен к первому входу управляющей информации устройства к инфор- мационному входу блока буферизации команд, а второй информационньй вход - к второму вхоДу управляющей информации устройства, первый информационный выход блока локальной памяти подключен к первому выходу управляющей информации устройства, а второй информационный выход - к второму вьтходу управляющей информации устройства, информационному входу блока трансляции адреса, информационному входу селектора первого слагаемого, выходы микроприказов блока микропрограммного управления подключены к соответствзпощимуправляющим входам блока локальной памяти, блока счетчиков и блока буферизации команд, селекторов первого и второго слагаемых и бопока трансляции адреса, вход внешних запросов блока микропрограммного управления соединен с нходом внешних запросов устройства, а вход признаков ветвления - с соответствующими выходами признаков ветвления блока буферизации команд, сумматора адреса и блока трансляции адреса, выход абсолютного адреса которого соединен с соответствующими входами абсолютного адреса блока локальной памяти и блока буферизации команд, выходы регистров командной информации первого, второго и третьего уровней соединены с соответствующими информационными входами блока микропрограммного управления и адресными входами блока локальной па Мяти, вход адреса команды которого соединен с входом команды селектора первого слагаемого и выходом адреса команды блока счетчиков, первый информационный вход которого соединен с выходом регистра командной информации первого уровня, введены селекторы первого, второго и третьего уровней, первый селектор адреса команда, второй селектор адреса команды, селектор третьего слагаемого, блок связи с операционным устройством и блок связи с устройством управления памятью, выход запроса которого соединен с первым запросным входом устройства, а вход адреса - с первым информационным входом второго селектора адреса команд и выходом су матора адреса, третий вход которого Соединен с выходом селектора третьег слагаемого, выход абсолютного адреса которого соединен с входами абсолютного адреса блока связи с операционных устройством и блока связи с устройством управления памятью и подключен к выходу абсолютного адреса блока трансляции адреса, информационный вход которого соединен с ин формационмым входом блока связи с устройством управления памятью, вторым информационным входом второго селектора адреса команд и информационным входом блока связи с операционным устройством, выход коTQporo соединен с вторым запросньм выходом устройства, а вход управляющей информации соединен с выходом регистра командной информации второго уровня, пёрвь&1И информационными входами селекторов первого, второго. и третьего уровней, вторые информационные входы этих селекторов соеди5йены с выходом регистра командной информации третьего уровня, вход ко торого соединен с выходом селектора третьего уровня, выход селектора вт рогОуровня соединен с входом регистра командной информации второго уровня, третий информационный вход которого соединен с выходом регистра командной информации первого уро ня и входом управляющей информации селектора третьего слагаемого, первый информационный вход которого со динен с выходом счетчика предварительной накачки блока счетчиков, выход идентификатора которого соеди иен с первым информационным входом селектора первого уровня, выход которого соединен с входом регистра командной информации первого уровня, а второй информационный вхо с информационным выходом блока буферизации команд, выход первого селектора адреса команды соединен с входами адреса команды блока буферизации команд и блока локальной памяти, вход адреса которого соединен с первым входом первого селекто ра адреса команды, второй вход которого соединен с выходом адреса команды блока счетчиков, выходы микроприказрв блока микропрограммного управления-подключены к соответствующин входам управления селекторов первого, второго и третьего уровней второго селектора адреса команды, селектора третьего слагаемого блока связи с операционным устройством и блока связи с устройством управлени памятью, выход признака ветвления к торого соединен с входом признака ветвления блока микропрограммного у равления, а выход маркера записи оп ранда два соединен с входом маркера записи операнда два блока локальной памяти. . Блок связи с операционным устрой ством содержит регистр маски програ мы слова состояния программы и регистр запросного слова в операционj нов устройство, выход которого является выходом блока, а вход упра ления соединен с входом управления регистра маски и входом управления блока, информационный вход регистра маски соединен с информационным входом блока, а выход - с входом маски регистра запросного слова в операционное устройство, вход абсо77«лютного адреса которого соединен с входом абсолютного адреса блока. Блок связи с устройством управления памятью содержит блок памяти маркеров, регистр ключа защиты из слова состояния программы, четыре элемента И, три элемента НЕ, три элемента ИЛИ и регистр запросного слова в устройство управления памятью, выход которого является выходом запроса блока а вход абсолютного адреса подключен к входу абсолютного адреса блока, нервому входу первого элемента И, первому входу второго элемента И и первому входу третьего элемента И, второй вход которого соединен с вторым входом второго элемента И, первьм входом четвертого элемента И, управлякяцим входом блока памяти маркеров, управляющим входом регистра запросного слова в устройство управления памятью и управлякщим входом блока, вход адреса блока соединен с входом адреса блока памяти маркеров, выход маркера которого соединен с выходом маркера записи два блока и входом маркера регистра запросного слова в устройство управления памятью, вход защиты которого соединен с выходом четвертого элемента И, второй вход которого соединен с выходом регистра ключа защиты из слова состояния программы, вход которого соединен с информационным входом блока, выход ветвления которого соединен с вькодом признаков блока памяти маркеров, выход третьего элемента И соединен с входом первого элемента НЕ и с первыми входами первого и второго элементов ИЛИ, выходы которых подключены к первому и второму кодовым входам регистра запросного слова в устройство управления памятью соответственно, второй вход первого элемента ИЛИ соединен с выходом .третьего элемента ИЛИ и входом второго элемента НЕ, выход которого соединен с вторым входом второго элемента ИЛИ, выход первого элемента НЕ соединен с вторым входом первого элемента И третий вход которого соединен с выходом третьего элемента НЕ, вход которого соединен с выходом второго элемента И и вторьм входом третьего элемента ИЛИ. На фиг. 1- представлена структурная схема устройства центрального управления на фиг, . а , 6 - структурная схема блока буферизации команд (буфера команд)i на фиг. 3 структурная схема узла анализа нахождения команды в буфере команд на Лиг. 4 а,6 - структурные схемы первого и второго коммутаторов выходной информации столбцов буфера командJ на фиг. 5 - структурная схема блока счетчиков} на фиг. 6 - структурная схема блока локальной памяти на фиг. 7 -.струк турная схема узла обнаружения конфликтов по использованию первого и второго операндов на Лиг. 8 - стру турная схема узла коррекции первого операнда при конЛпиктах (схема узла коррекции второго операнда идентичн на фиг. 9 - структурная схема блока микропрограммного управления процессора; на фиг. 10 - структурная . схеме приоритета , 11 - стру турная схема блока трансляции адрес на фиг. 12 - структурная схема префиксации реального адреса при преоб разовании его в абсолютный адресу на фиг. 13 - схема селектора формирования индекса сегмента и страницы зависимости от установленных в управляющем регистре размеров сегмента и странищ 1; на фиг. 14 - структурная схема блока связи с операцио ным устройством; на фиг. 15 - струк турная схема блока связи с устройством управления памятью , на фиг,6 временная диаграмма работы устройст центрального управления для совмещенного выполнения четырех команд. Устройство центрального управлеНИН процессора (фиг. 1) содержит блок 1 буферизации команд (буфер команд), селектор 2 первого уровня, регистр 3 командной информации первого уровняfуправляющая информация может устанавливаться на уровне одновременно с командной: идентифика тор слова состояния программы, код длины команды, признаки, характерны для команды, сигналы программных и схемных ошибок, сигналы сравнения по адресу и т.п.), селектор 4 второ го уровня, регистр 5 командной инфо мации второго уровня, селектор 6 третьего уровня, регистр 7 командно информации третьего уровня, блок 8 микропрограммного управления, первый селектор 9 адреса команд, блок 10 локальной памяти,второй селектор 11 адреса команд, блок 12 счетчиков, селекторы 13 - 15 первого, второго и третьего слага емых, сумматор 16 адреса, блок 17 трансляции адреса, блок 18 связи с операционным устройством, блок 19 связи с устройством управления памятью, первьп вход 20 управления (из устройства управления памятью), второй вход 21 управляющей информации 21 (из операционного устройства), выходы 22 микроприказов, перпый выход 23 управляющей информации в операционное устройство I , второй выход 24 управляющей информации /в операционное устройство и уст.. k.. ройство управления памятью , второй запросный выход 25 (в операционное устройство), первый запросный выход 26 (в устройство управления памятью) , выходы 27 признаков ветвления, информационный выход 28 буфера команд, вход 29 внешних запросов, зыходы 30 вдентификатора 31, адреса команды, 32 счетчика предварительной накачки блока счетчиков, выходы 33 --35 регистров первого, второго и третьего уровней, выход 36 первого селектора адреса комацд, выход 37 сумматора адреса, вы- ход ЗВ информации базы и индекса, выход 39 абсолютного адреса блока . трансляции адреса, выход 40 маркера записи операнда дваТ Блок 1 буферизации команд (фиг. 2в,о) содержит первую и вторую секции 41 и 42 памяти командных слов (БКС) (41.1,42,1 первые столбцы секций, 41,2, 42.2 - вторые столбцы секций) , память 43 адресов командных слов, память 44 признаков действительности каждой строки памяти командных слов, память 45 связностей строк, память 46 замещения, коммутаторы 47-51 адресов строк, первый элемент И 52, сумматор 53 адреса строки при выборке разорванной (расположенной в двух смежных словах) команды, сумматор 54 связности для выработ ки адреса строки памяти связности при внесении в нее номера столбца продолжения, буферньп регистр 55 связностей для указания столбца памяти связности, в котором делается отметка о продолжении, буферный регистр 56 адреса для проверки наличия команды в памяти 41 и 42 при преднакачке и в команде записи, коммутаторы 57 и 58 выходной информации столбцов памяти 91командных слов, сдвигатель 59, на выходе которого; Лормируется выбираемая команда, регистр 60,команды, схе ма 61 сравнения адресов, эторой и третий элементы И 62, коммутатор 63 выходной инАормации столбцов памяти связности, регистр 64 номера столбца в котором обнаружена команда при ее выборке, элементы НЕ 65 для определе ния столбца-кандидата на эамешение, регистр 66 номера столбца продолжения, элемент ИЛИ 67, узел 68 анализа наличия команды в секциях 41 и 42 выход 69 номера столбца сравнения, выход 70 номера столбца продолжения., выход 71 формата команды. Блок 1 буферизации команд предразначен для заблаговременного накоп ления и сохранения команд, вьтолняемых процессором по программе, и, таким образом, для сокращения потерь (времени процессора на выборку команд из оперативной (буферной) памяти как при последовательном выполнении команд, так и при передачах управ- Ленин. .В предлагаемом устройстве выбран двухстолбцовый вариант буфера команд. Узел 68 анализа наличия команды в буфере (фиг. 3) содержит две схемы 72 сравнения, дешифратор 73, четыре элемента НЕ 74, четыре элемента И 75 и элемент ИЛИ 76, выход 77, соответствующий командам R9-Лормата, выход 78, соответствующий командам .RX -Лормата. Кол1мутатор 57 выходной информации столбцов памяти командных слов (фиг. 4а) содержит элемент НЕ 79, два элемента И 80 для приема информации 4-7 байт от первой секции буфе ра команд и элемент 1ШИ 81. Коммутатор 58 выходной информации столбцов .памяти командных слов (фиг. 48) содержит два элемента НЕ 79, четыре элемента И 80 (два из них - для приема информации 0-3 байт от второй секции буфера команд) и элемент ИЛИ 81. Блок 12 счетчиков (фиг. 5) содержит счетчик 82 команд, селектор 83, регистр Я4, сумматор 85 для 29, 30 разрядов адреса команды, счетчик 86 предварительной накачки, счетчик 87 идентификатора хранения ССП (слово состояния программы) в локальной памяти, дешифратор 8В, два элемента НЕ 89 и два элемента И 90 -(прибавления и вычитания единицы на счетчике преднакачек). Блок 10 локальной памяти (фиг.6) .процессора содержит две памяти 91 и 92 (каждая из которых имеет 64 строч ки по 8 байт для хранения информации) , селекторы 93 и 94 входной информации памяти, сдвигатели 95 и 96 выходной информации памяти (на О или 4 байта влево), регистры 97 и 98 выходной информации памяти,селекторы 99 и 100 адресов памяти, регистры 101 и 102 адресов памяти, селектор 103 входной информации блока, сдвигатель 104 входной информации, узлы 105 и 106 коррекции второго и первого-операндов, регистры 10.7 и 108 второго и первого операндов, селектор 109 микрокоманд первого и второго уровней совмещения, селектор 110 микрокоманд трех уровней совмещения, селектор 111 приёма результата операционного устройства, буферный регистр 112, сумматор 113 кода сдвига, селек- тор 114 маркера второго операнда, регистр 115 восстановления операнда, узел 116 обнаружения конфликтов (по использованию операндов) , вход 117 узлов 105 и 106 коррекции, выход 118 селектора 11 Г- микрокоманд, выходы 119 и.120 узла обнаружения конфликтов (выходы кода управления коррекцией второго и первого операнда), информационные входы адресов чтения операндов 121 и 122 узла обнаружения конфликтов, выход 123 узла 106 коррекции первого операнда входы 22.1-22.3 микрокоманд трех уровней совмещения. Блок локальной памяти процессора предназначен для приема, хранений,.модификации и выдачи (в процессе выполнения команд с совмещением операций) значений РОН, РПЛ, копий управляющих регистров (УР), копий префикса, копий исходных ССП (слово состояния программно и ССИ (слово состояния инструкции) для каждой из одновременно вьтолняющихся команд, исходных операндов в командах плавающей точки с повьппенной точностью,исходных операндов в командах десятичной арифметики, начальных, текущих и конеч,ных адресов операндов в командах 55 формата, различных констант, начальных адресов таблиц сегментов для 15 задач, идентификатора процессора.

1 i

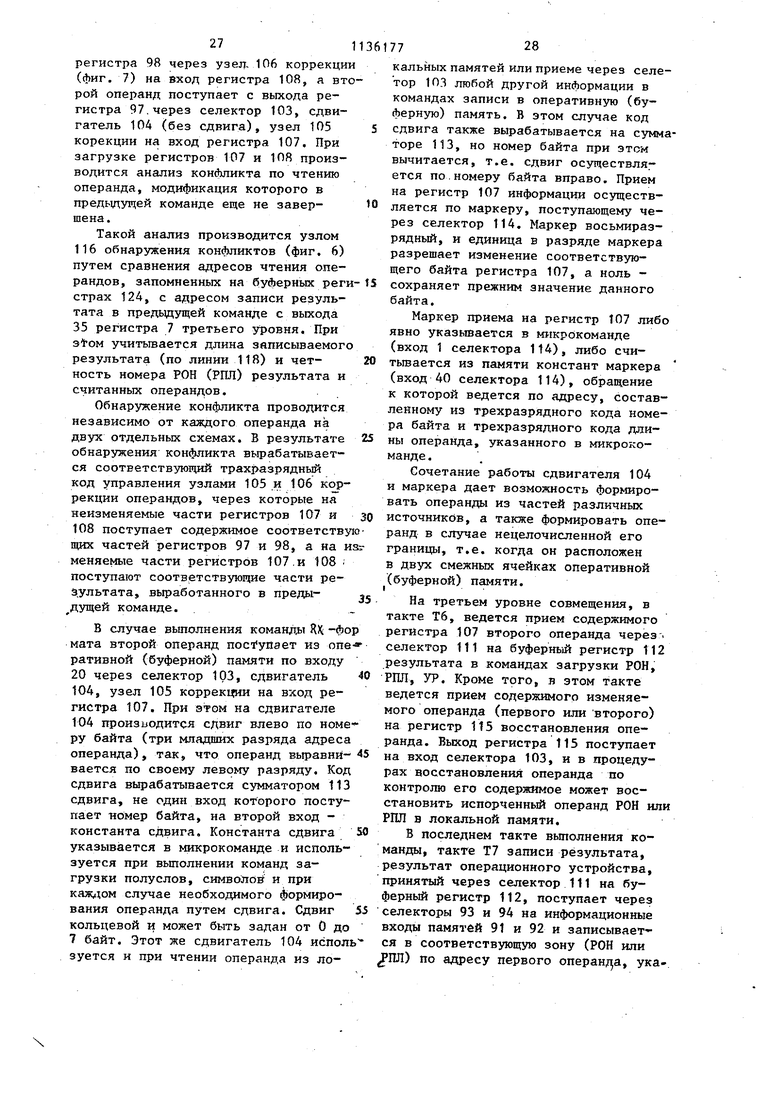

Узел 116 обнаружения конфликтов (фиг. 7) содержит буферные регистры

124адресов операндов, схемы

125сравнения pj адресов, схемы 126 сравнения младшего разряда адресов, восемь элементов И 127

и четыре элемента РШИ 128.

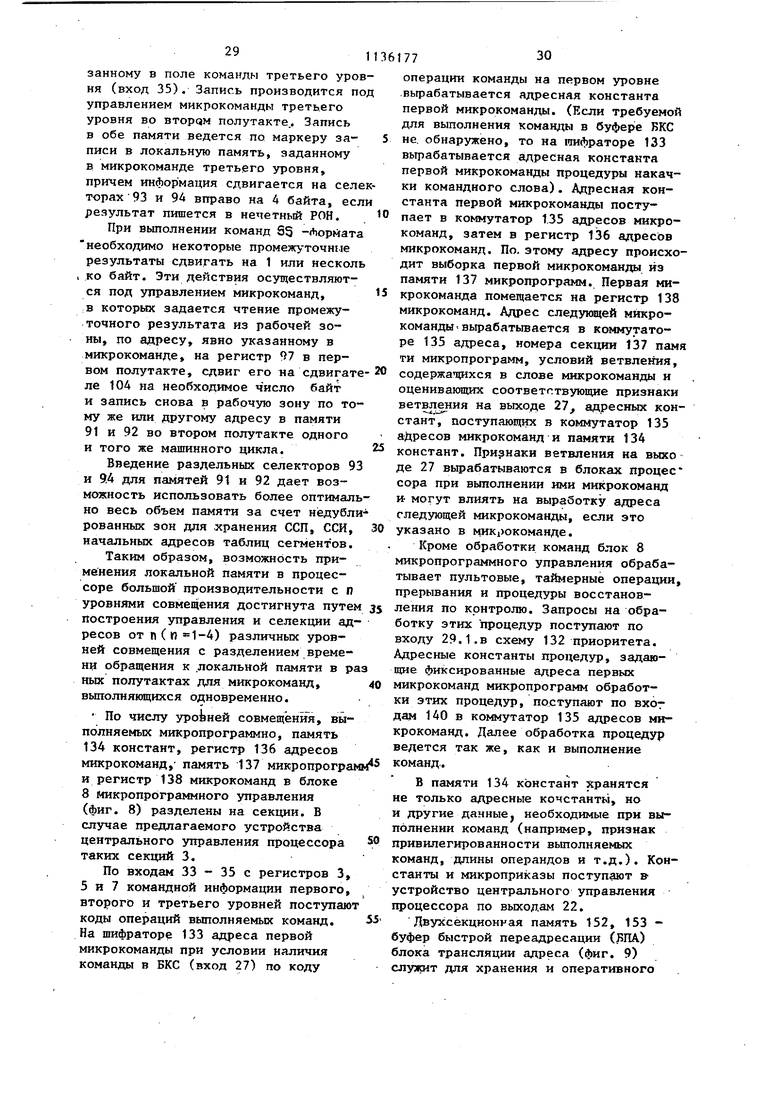

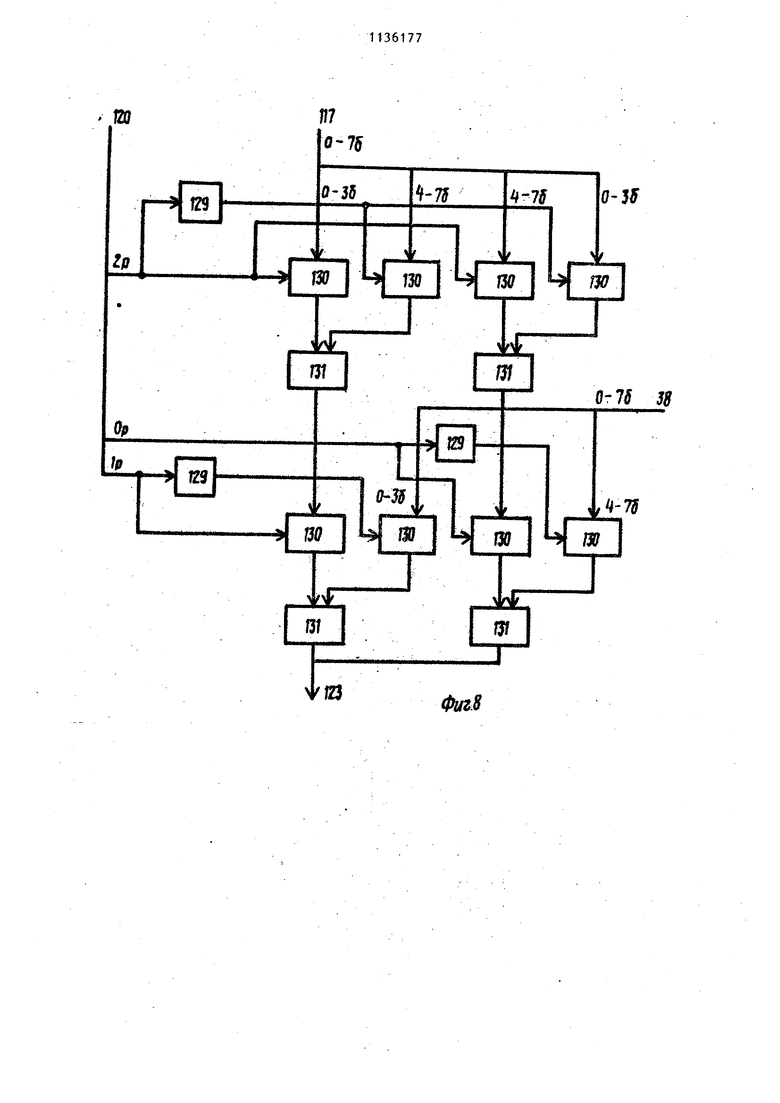

Узел 106 коррекции первого операнда (фиг. 8) содержит три элемента НЕ 129 управляющего кода 120, восемь элементов И 130 и четыре элемента И,ПИ 131.

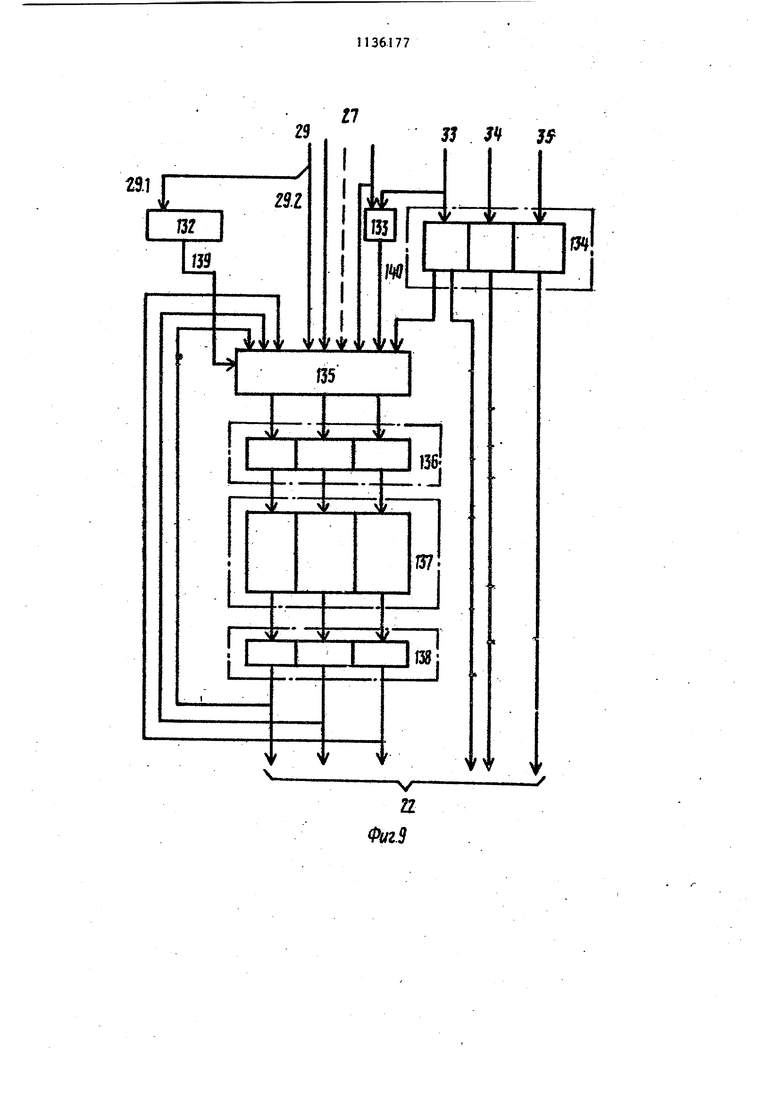

Влок 8 микропрограммного управления процессора (фиг.9) содержит схему 132 приоритета запросов на обращение к памяти микропрограмм, шифратор 133 адреса первой микрокоманды, память 134 констант, коммутатор 135 адресов микрокоманд, регистр 136 адресов микрокоманд, память 137 микропрограмм, регистр 138 микрокоманд, входы 139 запросов вход 140 адресных констант, вход 29.1 запроса памяти микропрограмм, вход 29,2 адреса первой микрокоманд по запросу. Блок 8 предназначен для управления работой процессора вы(окопроизводительной ЭВМ с совмещением выполнения команд.

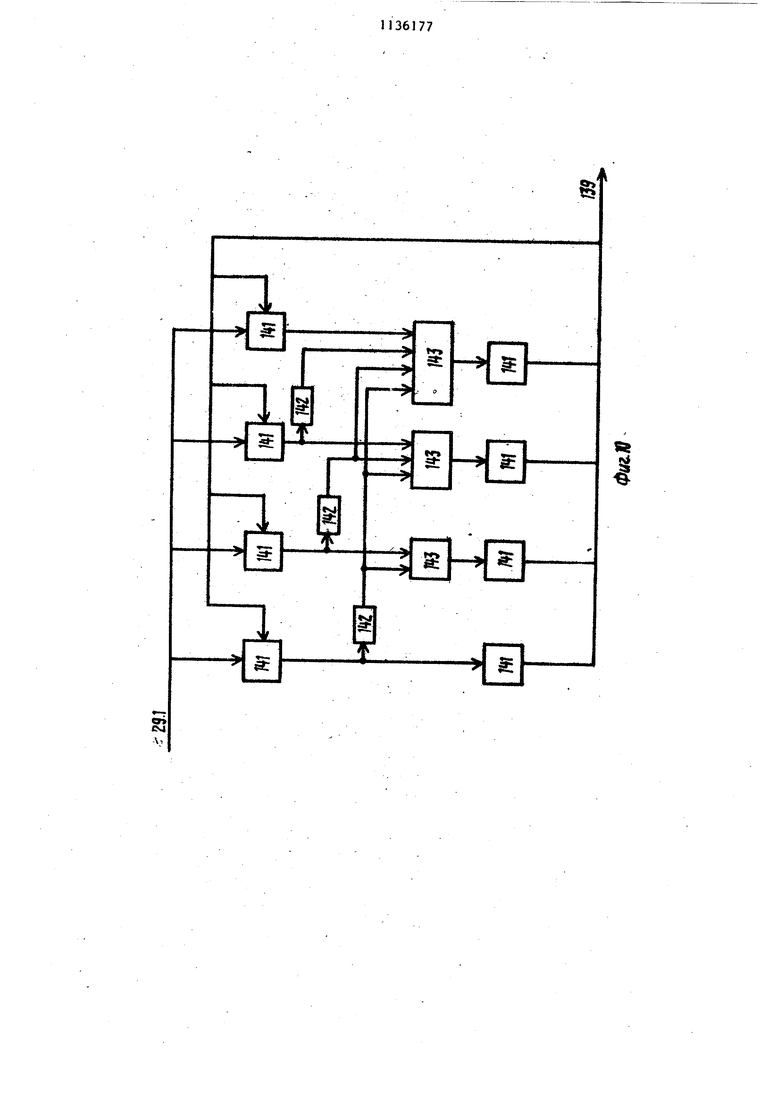

Схема 132 приоритета (фиг.10) .со держит восемь триггеров 141 (четьфе триггера запросов и четыре триггера выбора первого адреса микрокоман ды), три элемента НЕ 142 и три элемента И 143.

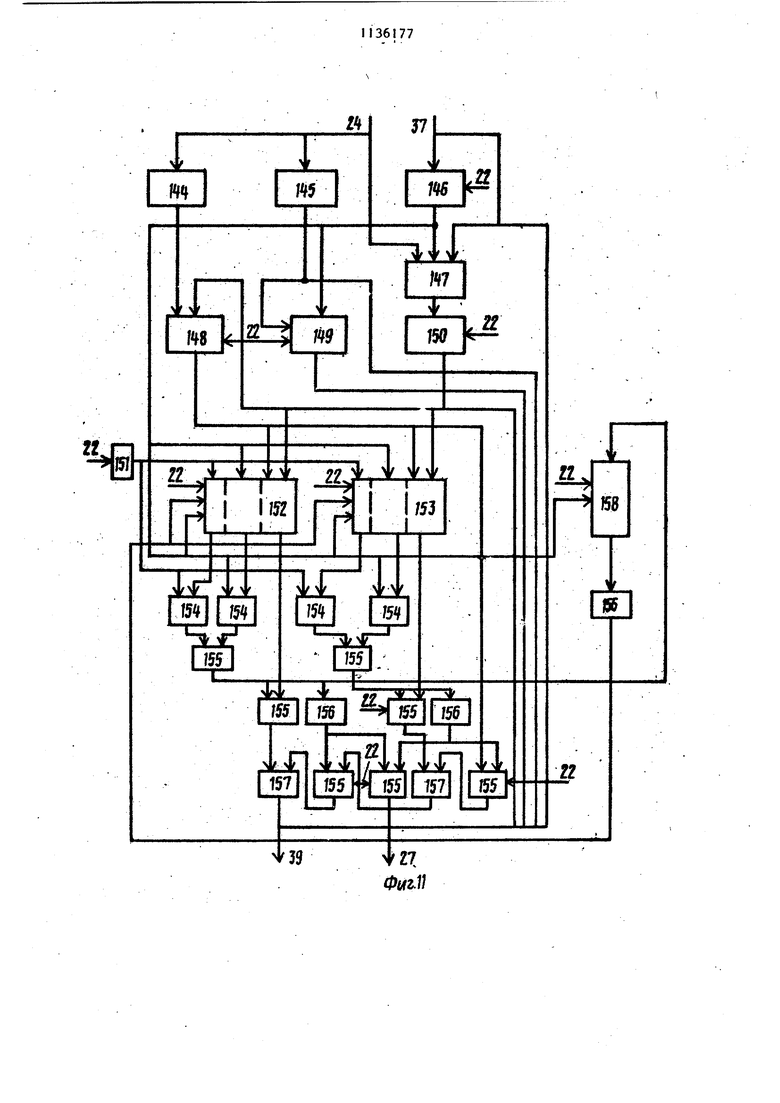

Блок 17 трансляции адреса (фиг.1 содержит регистр 144 префикса, упраляющий регистр 145, регистр 146 логического адреса, селектор 147 реал ного адреса, схему 148 префиксации, селектор 149 формирования индекса сегмента и страницы в зависимости от установленных в управляющем регистре размеров сегмента и страницы, регистр 150 реального адреса, регистр 151 активного номера таблицы сегментов, буферные памяти 152 и 153 быстрой переадресации, четыре схемы 154 сравнения, семь элементов И 155, три элемента НЕ 156, два элемента ИЛИ 157 выдачи абсолютного адреса, память 158 замещения столбцов блока трансляции, выход 27 признака ветвления по обращению к микропрограмме накачки буфера переадресации.

Блок 17 трансляции адреса предназначен для преобразования логи12

177

ческого адреса операнда или команды в реальный, а затем в абсолютный.

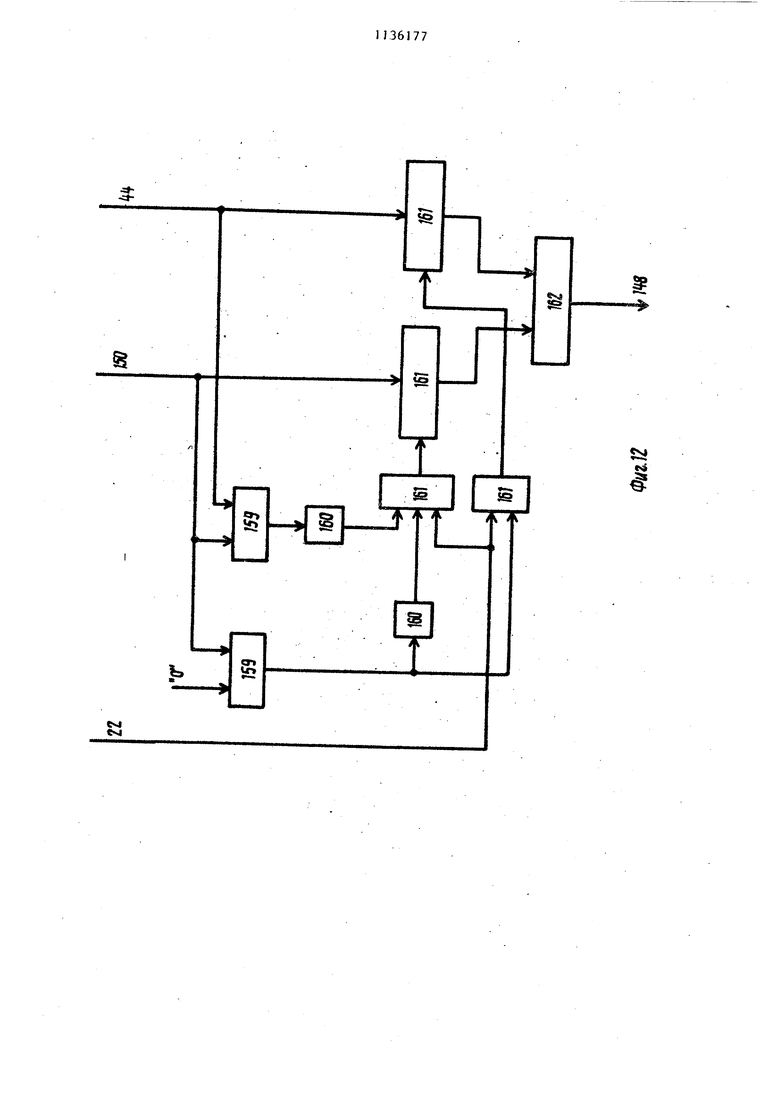

Схема 148 префиксации (фиг.12) содержит две схемы 159 сравнения, два элемента НЕ 160, четыре элемента И 161 элемент ИЛИ 162 формирования абсолютного адреса.

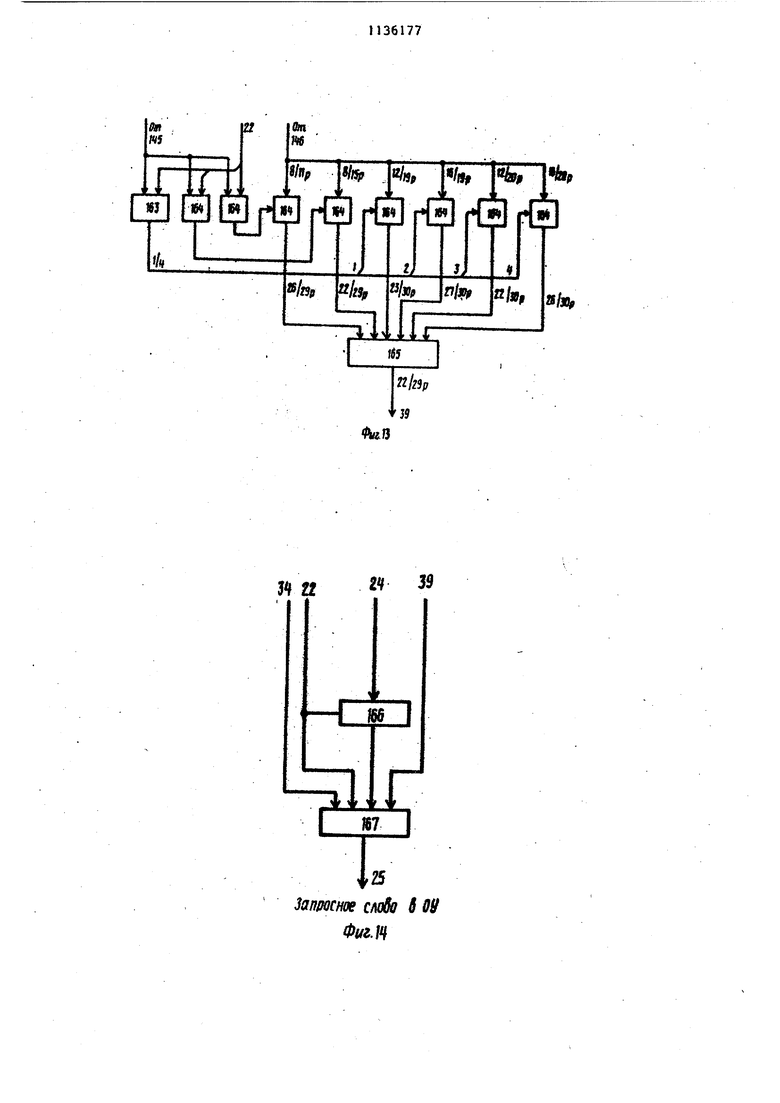

Селектор 149 формирования индекса сегмента и страницы (фиг. 13) содержит дешифратор 163 конкретного сочетания размеров сегмента и страницы для управления выбором индекса страницы, восемь элементов И 164 (для управления выбором индекса сегмента и для выдачи индексов) и элемент ИЛИ 165 формирования индекса.

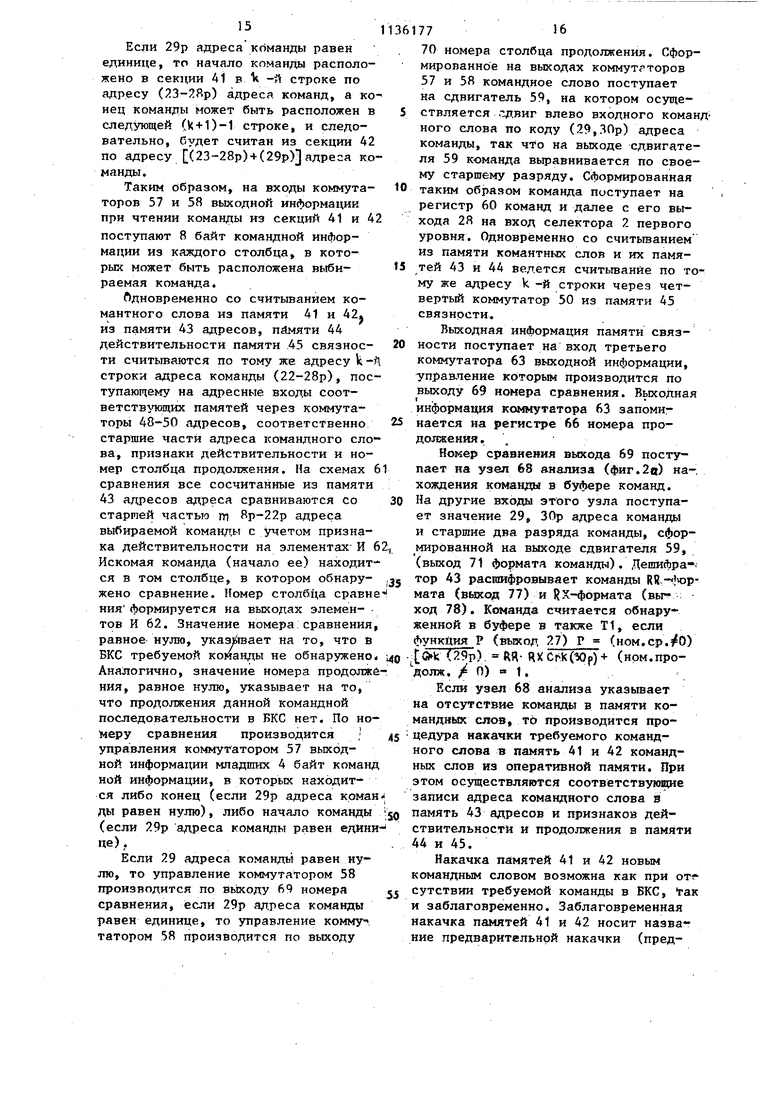

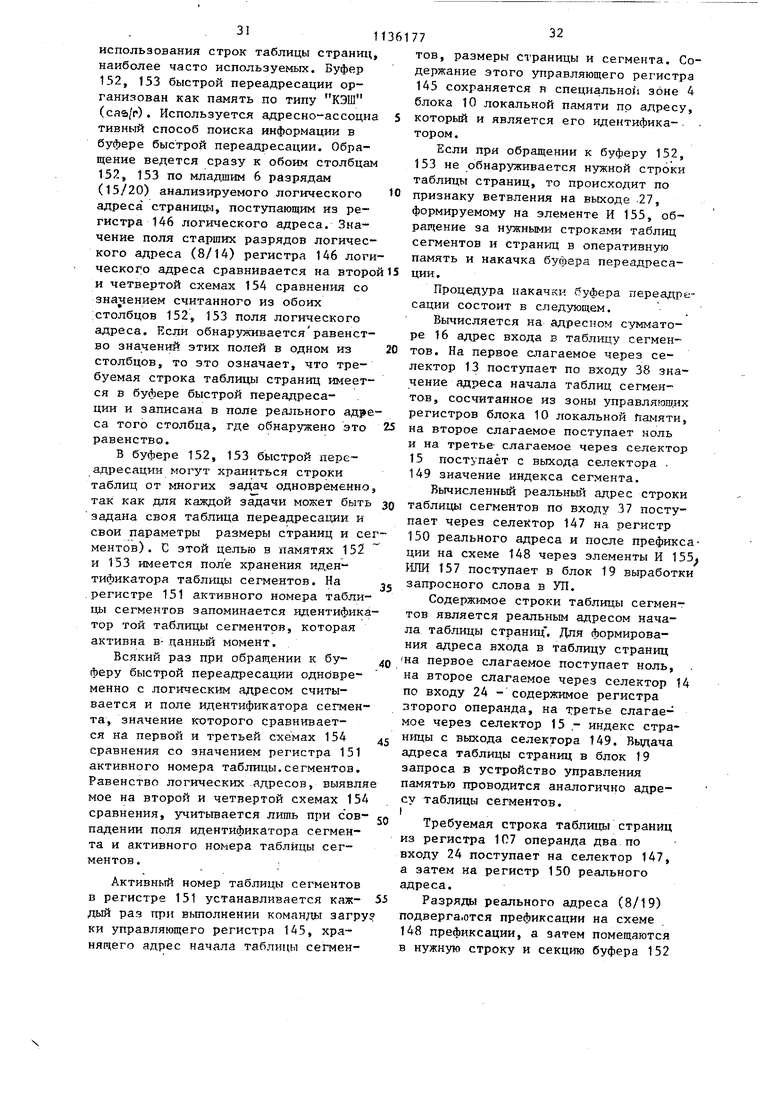

Блок 18 связи с операционным устройством (фиг. 14) содержит регистр 166 маски программы слова состояния программы и регистр 167 зацросного слова в операционное уст ройство. Блок связи с операционным устройством. (СУ) предназначен для обеспечения взаимодействия процессора с операционными устройствами по загрузке операционного устройства ко дом операции и операндами и по получению от операционного устройства результатов операции.

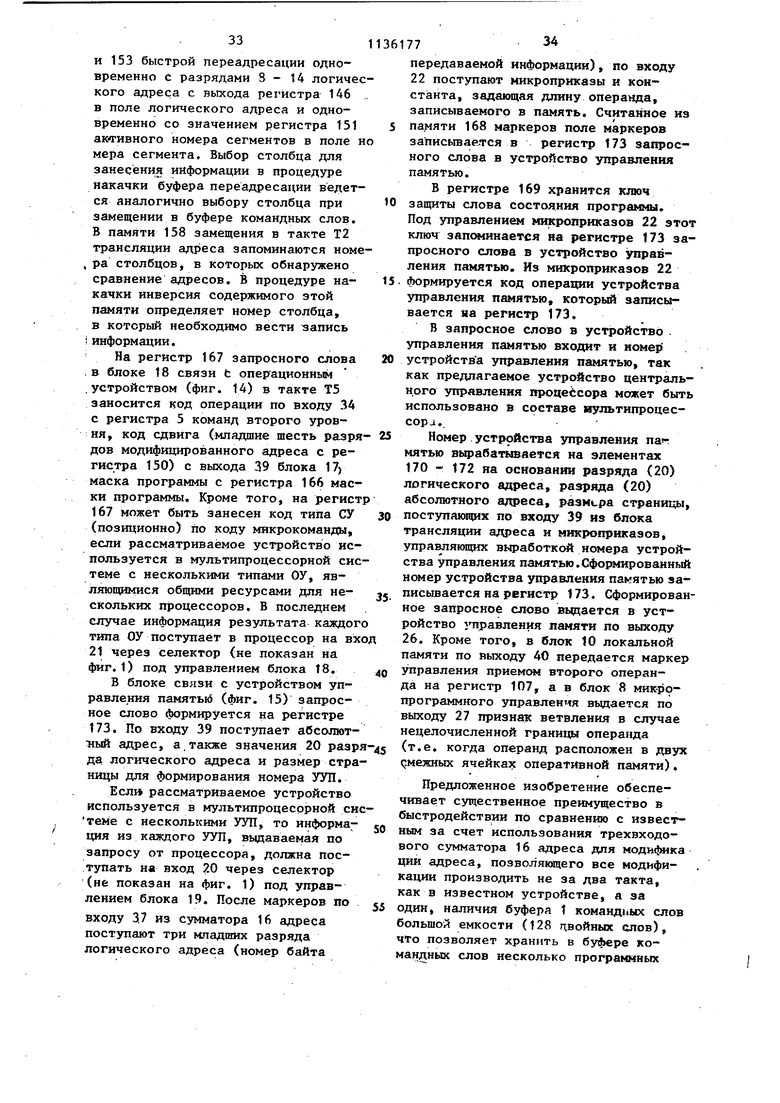

Блок 19 связи с устройством управления памятью (фиг. 15) содержит бло 168 памяти маркеров, регистр 169 ключа защиты из слова состояния программы, четьфе элемента И 170, три элемента НЕ 171, три элемента ИЛИ 17 и регистр 173 запросного слова в устройство управления памятью, выход 27 признака ветвления по нецелочисленной границе адреса операнда. Блок связи с устройством управления памятью (УУП) предназначен для обеспечения взаимодейстбия процессора с оперативной (буферной) памятью по обмену информацией. Обмен инициируется путем передачи от процессора в устройство управления памятью запросного слова, содержащего номер запрашиваемого УУП (если рассматривается мультипроцессорная система с несколькими УУП), абсолютньй адрес обращения.к памяти, код операции обращения (чтение, запись и т.п.), маркер записи, ключ защиты.

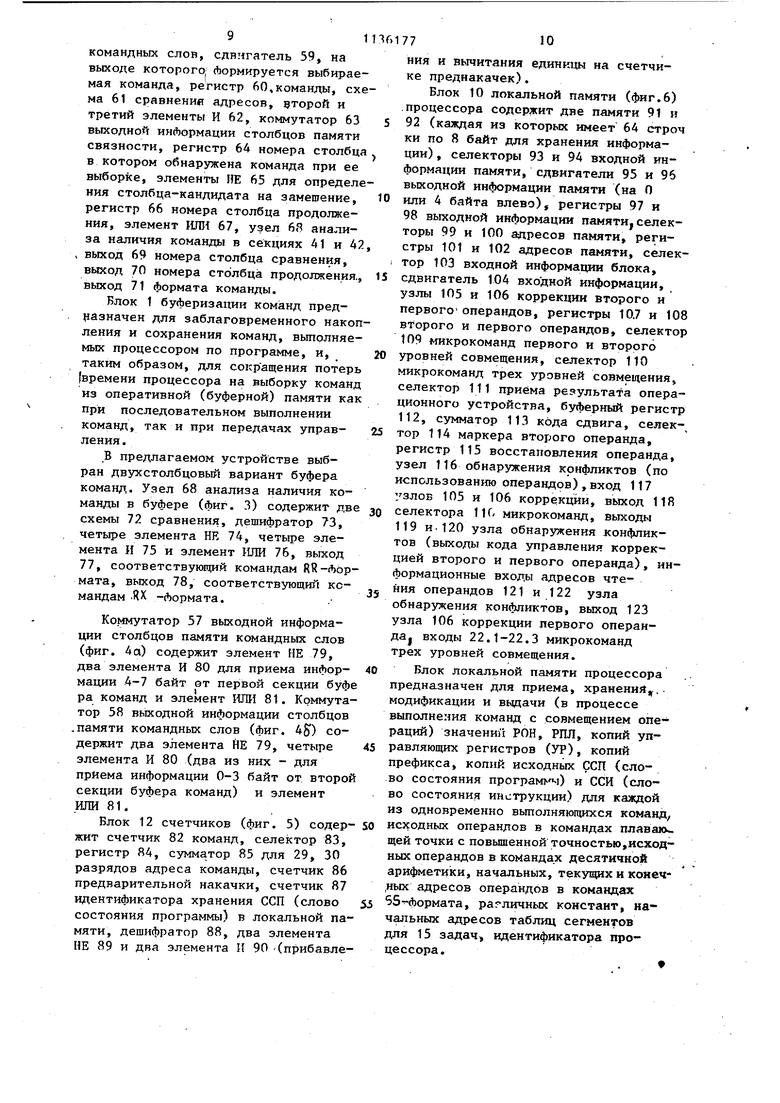

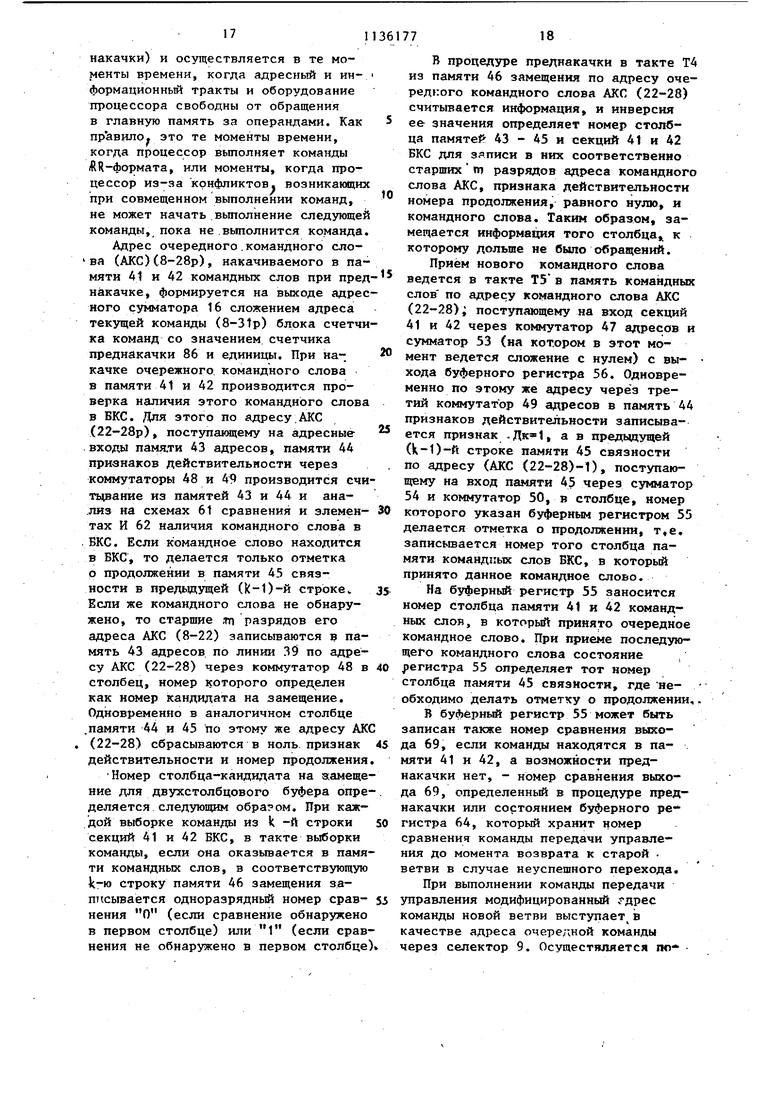

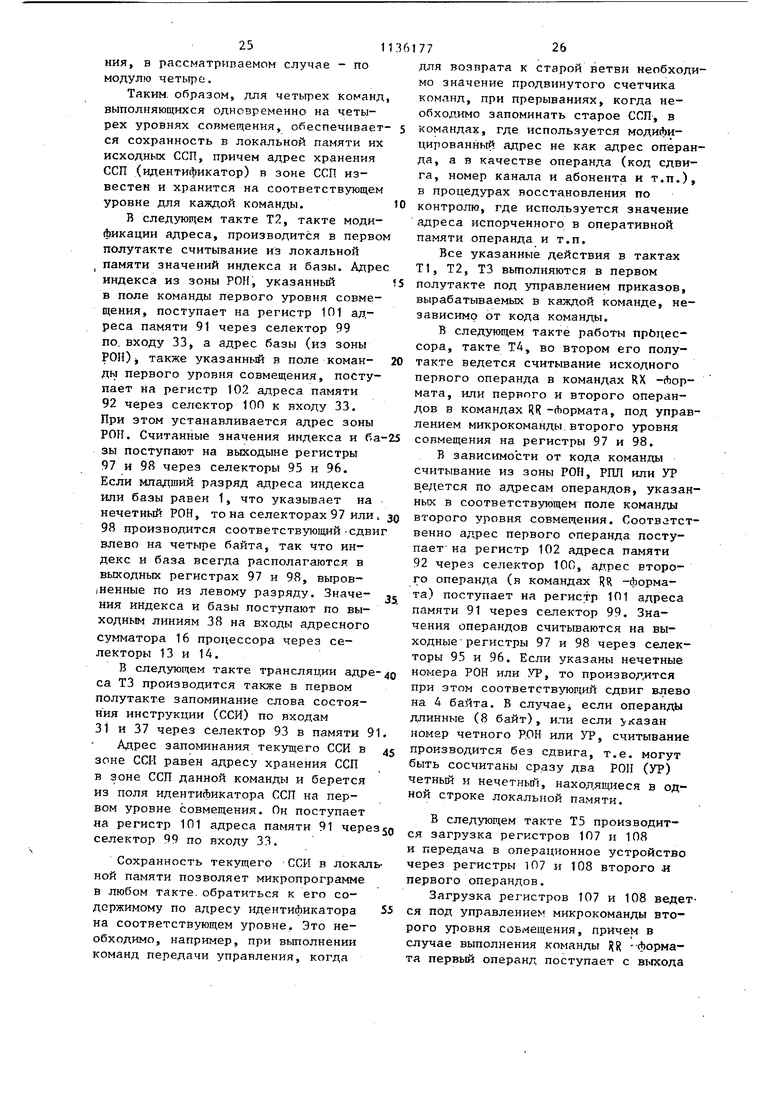

Устройство центрального управления процессора выполняет команды типа принятых в ЕС ЭВМ. Работа устройства центрального управления процессора рассматривается на примере выполнения команды формата .RX типа сложения с фик сированной точкой (фиг.16). В устройстве центрального управления процессора сур ествует 4 уровня выполнения команд (фиг. 16) и соответственно 4 уровня совмещения. Такты ТО,Т1 - такты нулевого уровня, Т2,ТЗ - такты первого уровня, команда принимается на регистр 3 командной информации первого уровня через селектор 2, Т4, Т5 - такты . второго уровня, на регистр 5 командной информации второго уровня команд .принимается через селектор 4. Т6, Т7 - такты третьего уровня, на регистр 7 командной информации третьего уровня команда принимается через селектор 6. Типовые команды форматов РР, РХ выполняются за 8 тактов, проходя последовательно 4 уровня. Команды, требующие для своего выполнения больше 8 тактов, либо находятся на каком-либо уровне большее коли чество тактов, либо после второго или третьего уровней возвращаются на Первый уровень и внови проходят последовательно по всем уровням. Управление процессором в тактах ТО, Т1, Т2 вьтолняется схемно, в тактах ТЗ - Т7 - микропрограммно. Перепись . с уровня на уровень производится микропрограммно, под управлением блока 8 микропрограммного управления Рассмотрим работу блока буферизаЦИК команд (фиг. 2 а,S ) на примере вьшолнения команд типа принятых в ЕС ЭВМ. Допустим, что выполняются команды формата.RR длиной в 2 байта, :не требующие обращения в главную па- :мять за операндами, команды формата ЯХ длиной 4 байта и команды формата 55 длиной в 6 байтов. Команды .расположены в ячейках главной па- мяти в командных словах, каждое ДЛИНОЙ в 8 байт. Выборка из главной памяти производится 8-байтными словами по 24-разрядному адресу (разрядность адреса 8-31), причем разряды 8-28 адресуют командное елово, а разряды 29-31 (номер байта) - тот номер байта в командном слове, в котором расположен старший байт команды. Адрес текущей команды вырабатывается на Рлоке счетчика команд процессора (СгК) (8/31), причем 31 всегда равен О. Разрядность счетчика команд (8-31) представляется в виде («n+k+ И) разрядов и принимается (8-22р), k 6(23-28р), (29-31р); Допустим также, что выборка команды из памяти командных слов (БКС) проводится в такте выборк команды, а вьфаботка адреса следующей команды в следую14ем такте такте модификации адреса. В такте выборки, команды производится обращение к секциям 41 и 42 памяти командных слов (БКС) по разрядам адреса текущей команды. В каждой строке каждого столбца БКС 41 и 42 расположено 8-байтовое командное слово. В соответствующей К -и строке соответствующего столбца памяти 43 адресов записаны старшие (8-22) чу раэрядов адреса командного слова, в соответствующих строках столбцов памяти 44 признаков действительности записаны признаки действительности ДК (условимся, что если 1, то содержимое соответствукчцей строки БКС 41 (42) действительно и в ней находится- требуемая команда, если Дк 0, то команды в памяти командных слов соответствующего столби(а по данному адресу нет) . В соответствующей строке соответствующего столбца памяти 45 связности записан номер столбца БКС, в котором нахо- дится в продолжение данной командной последовательности. Если в U -и строке памяти 45 связности записана информация, не равная нулю, то это означает, что продолжение команды имеется в БКС, и для анализа зтого не требуется считывать ()-ю строку памяти 43 адресов в случае разорванной команды. Каждый столбец памяти командныхслов состоит из двух секций Секция 41 содержит младшие 4 байта командного слова, секция 42 - старшие 4 байта командного слова. Обращение к секции 41 ведется,по адресу с выхода первого коммутатора 47 адресов, рбрар1ение к секции 42 - по адресу с выхода сумматора 53 адреса, который при выборке команды суммирует значение младших Ic разрядов адреса команды со значением 29р адреса команды. Если 29р ад.реса команды равен нулю, то вся команда, независимо от ее формата, расположена в одной строке секций 41 и 42tбуфера БКС, и адреса обращения к секциям 41 и 42 одинаковы. Если 29p адреса команды равен единице, то начало команды расположено в секции 41 в V -и строке по адресу (.3-2Яр) адреса команд, а ко нец команды может быть расположен в следующей (k+1)-1 строке, и следовательно, будет считан из секции 42 по адресу (23-28р) + (29р) адреса ко мандь. Таким образом, на входы коммутаторов 57 и 58 выходной информации при чтении команды из секций 41 и 4 поступают 8 байт командной информации из каждого столбца, в которых может быть расположена выбираемая команда. Одновременно со считыванием комантного слова из памяти 41 и 42 из памяти 43 адресов, пймяти 44 действительности памяти .45 связности считьтаются по тому же адресу kстроки адреса команды {22-28р), пос тупающему на адресные входы соответствующих памятей через коммутаторы 48-50 адресов, соответственно старшие части адреса командного сло ва, признаки действительности и номер столбца продолжения. На схемах сравнения все сосчитанные из памяти 43 адресов адреса сравниваются со старшей частью т Яр-22р адреса выбираемой команды с учетом признака действительности на элементах- И Искомая команда (начало ее) находит ся в том столбце, в котором обнаружено сравнение. омер столбца сравн ния формируется на выходах элементов И 62. Значение номера сравнения равное нулю, указывает на то, что в ВКС требуемой команды не обнаружено Аналогично, значение номера продолж ния, равное нулю, указывает на то, что продолжения данной командной последовательности в БКС нет. По но меру сравнения производится ; управления коммутатором 57 выходной информации младших 4 байт коман ной информации, в которых находится либо конец (если 29р адреса кома ды равен нулю), либо начало команды (если 29р адреса команды равен един це) . Если 29 адреса команды равен нулю, то управление коммутатором 58 производится по вьЬсоду 69 номера сравнения, если 29р ад.реса команды равен единице, то управление комму татором 58 производится по выходу 7716 70 номера столбца продолжения. Сформированное на выходах коммутаторов 57 и 58 командное слово поступает на сдвигатель 59, на котором осуществляется .двиг влево входного командного слова по коду (29,ЗОр) адреса команды, так чТо на выходе сдвигателя 59 команда выравнивается по своему старшему разряду. Сформированная таким образом команда поступает на регистр 60 команд и далее с его выхода 2Я на вход селектора 2 первого уровня. Одновременно со считьтанием из памяти комантных слов и их памятей 43 и 44 ведется считывание по тому же адресу k -и строки через четвертый коммутатор 50 из памяти 45 связности Выходная информация памяти связности поступает на вход третьего коммутатора 63 выходной информации, управление которым производится по выходу 69 номера сравнения. ВькоДная информация коммутатора 63 запоминается на регистре 66 номера продолжен11я. Номер сравнения выхода 69 поступает на узел 68 анализа (фиг.2а) на-, хождения команды в буфере команд. На другие входы этого узла поступает значение 29, ЗОр адреса команды и старшие два разряда команды, сформированной на выходе сдвигателя 59, (выход 71 формата команды). Дешифра-. тор 43 расшифровывает команды RR -« чэрмата (выход 77) и Rx-формата (вьг ход 78). Команда считается обнаруженной в буфере в также Т1, если функЦия Р (выход 27) Р (ном.ср.0) Ok (29р) R4-ЦХСгКСЭДр) (нрм.продолж. / П) 1. Если узел 68 анализа укаэьюает на отсутствие команды в памяти командных слов, то производится процедура иакачки требуемого командного слова в память 41 и 42 командных слов из оперативной памяти. При этом осуществляются соответствующие записи адреса командного слова В память 43 адресов и признаков действительности и продолжения в памяти 44 и 45. Накачка памятей 41 и 42 новым командным словом возможна как при отг сутствии требуемой команды в БКС, гак и заблаговременно. Заблаговременная накачка памятей 41 и 42 носит название предварительной накачки (преднакачки) и осуществляется в те моменты времени, когда адрес гый и информационньй тракты и оборудование процессора свободны от обращения в главную память за операндами. Как 5 правило. это те моменты времени, когда процессор вьтолняет команды iRR-формата, или моменты, когда процессор из-за конфликтов, возникающих при совмещенном выполнении команд, не может начать вьтолнение следующей команды, пока не вьтолнится команда. Адрес очередного.командного слона (АКС)(8-28р), накачиваемого в памяти 41 и 42 командных слов при пред- накачке, формируется на выходе адресного сумматора 16 сложением адреса текущей команды (8-31р) блока счетчика команд со значением счетчика преднакачки 86 и единицы. При на- 20 качке очережного командного слова в памяти 41 и 42 производится проверка наличия этого командного слова в БКС. Для этого по адресу АКС (22-28р), постзшающему на адресные

, входы памя.ти 43 адресов, памяти 44 признаков действительности через коммутаторы 48 и 49 производится считьдвание из памятей 43 и 44 и анализ на схемах 61 сравнения и элемен- 30 тах И 62 наличия командного слова в

БКС. Если командное слово находится в БКС, то делается только отметка о продолжении в памяти 45 связности в предьщущей (К-О-й строке 35 Если же командного слова не обнаружено, то старщие ,тп разрядов его адреса АКС (8-22) записываются в память 43 адресов по линии 39 по адресу АКС (22-28) через коммутатор 48 в 40 столбец, номер которого определен как номер кандидата на замещение. Одновременно в аналогичном столбце .памяти 44 и 45 по этому же адресу АКС (22-28) сбрасываются в ноль признак 4S действительности и номер продолжения. Номер столбца-кандидата на замещение для двухстолбцового буфера опре-. деляется следующим . При каждой выборке команды из k -и строки 50 секций 41 и 42 БКС, в такте выборки команды, если она оказьгоается в памяти командных слов, в соответствующую k-ю строку памяти 46 замещения заппсывается одноразрядный номер срав- 55 нения О (если сравнение обнаружено в первом столбце) или 1 (если сравнения не обнаружено в первом столбце).

В процедуре преднакачки в такте Т4 из памяти 46 замещения по адресу очередного командного слова АКС (22-28) считывается информация, и инверсия ее значения определяет номер столбца памятей 43 - 45 и секций 41 и 42 БКС для зяписи в них соответственно старшихm разрядов адреса командного слова АКС, признака действительности номера продолжения, равного нулю, и командного слова. Таким образом, замещается информация того столбца,, к которому дольше не было обращений.

Приём нового командного слова ведется в такте Т5в память командных слов по адресу командного слова АКС (22-28)i поступающему на вход секций 41 и 42 через коммутатор 47 адресов и сумматор 53 (на котором в этот момент ведется сложение с нулем) с выхода буферного регистра 56. Одновременно по этому же адресу через третий коммутатор 49 адресов в память 44 признаков действительности записывается признак ., а в предыдущей (К-1)-й строке памяти 45 связности по адресу (АКС (22-28)-1), поступающему на вход памятк 45 через сумматор 54 и коммутатор 50, в столбце, номер которого указан буферным регистром 55 делается отметка о продолжении, т,е, записьшается номер того столбца памяти командных слов БКС, в который принято данное командное слово.

На буферный регистр 55 заносится нсмер столбца памяти 41 и 42 командных слов, в которьй принято очередное командное слово. При приеме последующего командного слова состояние , регистра 55 определяет тот номер столбца памяти 45 связности, где необходимо делать отметку о продолжении

В буферный регистр 55 может быть записан также номер сравнения выхода 69, если команды находятся в памяти 41 и 42, а возможности преднакачки нет, - номер сравнения выхода 69, определенньй в процедуре преднакачки или состоянием буферного регистра 64, который хранит номер сравнения команды передачи управления до момента возврата к старой ветви в случае неуспешного перехода.

При выполнении команды передачи управления модифицированный дрес команды новой ветви выступает в качестве адреса очередной команды через селектор 9. Осуществляется по

19П36

пытка выборки этой очередной командь1 из памяти 41 и 42 командных слов несмотря на то, что признак результата от предыдущей команды еще не получен. Если эта очередная ко- 5 манда находится в памяти 41 и 42, производится аьшолнение тех такТов этой и последующих за ней команд, в которых нет необратимых действий, до момента получения признака резуль- О тата от предьщущей команды.

В случае признака результата, соответствующего убпешному переходу, продолжается последовательность действий по выполнению команд новой 15 ветви и потери на выполнение команды йередачи управления здесь минимальны. В случае, если признак результата в предьздущей команде не соответствует переходу, вьшолнение командЗО новой ветви прекращается и производится возврат к командам старой ветви.

В случае, если переход успешен, но команды новой ветви нет в памяти 25 41 и 42, ведётся накачка требуемого командного слова этой новой ветви в память 4t и 42. При этом во всех столбцах памяти 45 связности по адресу (АКС (2.-28)-1) сбрасываются 30 признаки (номера) продолжения, т.е. связность командных слов, расположенных смежно в памяти 41 и 42, но имеющих разные старшие части адре-. сов, разрушается. Связность командных jj слов вновь устанавливается только пос ле приема первого командного слова из новой ветви.. ;

В слут1ае выполнения команд записи в оперативную (буферную) память Q ведется проверка нахождения информации в памяти 41 и 42 командных слов по адресу записи, рес записи с выхода ; блока 17 трансляции адреса постзшает по адресному входу 39 через коммутаторы 4845 и 49 на адресные входы памяти 43 адресов и памяти 44 признаков действительности и затем проверяется на схемах 61 сравнения и элементах И 62 на наличие в памяти командных 50 слов.

Если по адресу записи информация имеется в памяти 41 и 42, то выполняеуся :микроподпрогра,мма, по которой строка памяти 41 и 42 по этому ад- 55 ресу объявляется недействительной (сбрасываются признаки действительности в памяти 44), а во всех столб-н

7720

цах памяти 45 связности в предьщущей строке сбрасываются признпки (номера) продолжения.

Возможно и другое решение, предусматривающее запись операнда одновременно в главную память и в память 41 и 42 в тот столбец, в котором . обнаружено сравнение. Такое решейие, однако, потребовало бы наличия на информационном входе памяти 41 и 42 селектора для приема информации записываемого в память операнда.

Процесс работы к преднакачки команд может быть осуществлен по временной диаграмме (фиг. 16) совмещенно с вьтолнением . текугцнх команд. Работа блока буферизации команд осуществляется,в тактах Т1-Т5. Т1 - такт выборки команды. В первом его полутакте команда считывается из памяти 41 и 42, во втором полутакте ведется запись .номера столбцакандидата на замещение в память 46 замещения и анализ наличия команды в ВКС. Т2 - такт модификации адреса. Если вьтолняется процедура накачки БКС, то в Т2 вьфаба- тывается адрес командного слова, а также модифицируется (вычитается 1) счетчик преднакачки, если счетчик команд при продвижении указывает на командую из следующего командного слова.

ТЗ- - такт трансляции адреса командного слова. В этом такте счетчик преднакачки модифицируется (прибавляется 1) для вьфаботки адреса следзтощего командного слова. Т4 - такт выдачи информации из one ративной (буферной) памяти и проверки матрицы адресов буфера команд. В первом полутакте ведется считывание и проверка состояния памяти 43 адресов и памяти 44 признаков действительности. Если анализ показал, что требуемое командное слово имеется в памяти ко мандных слов, то во втором полутакте ведется запись только. в память 45 связности и процесс преднакачки заверщается, а информация, поступающая на оперативной памяти. 211 игнорируется. Если анализ показал, что требуемого коман ного слова нет в памяти 41 и 42 командных слов, то во втором полутакте ведется запйсь адреса в память 43 адре сов и сброс битов действительности и признаков (номера) продолжения в памяти 44 признаков действительности и в памяти 45 связности. Т5 - такт приема командного слова поступившего из оперативной (буферной) памяти в память 41 и 42. Прием осуществляется во втором полутакте. Кроме того, в втором полутакте устанавливается в 1 бит действительности и в предьщущей строке памяти 45 связности записьгеается признак (номер) продолжения. Счетчик 82 команд (фиг. 5) вычисляет адрес следующей команды на осно вании адреса текущей команды и ее формата. Адрес текущей команды хранится на счетчике 82 (8/28р) и регистре 84 (29, ЗОр). Два младшие разряды адреса с регистра 84 поступают на вход сумматора 85 в качестве первого слагаемого. Вторым слагаемым является еод длины команды (К,ЦК) поступающий по входу 33 с регистра команд первого уровня. При вычислени адреса следующей команды в такте Т2 теку1чей . команды эти две величины складываются, и новое значение 29, 30 р адреса из сумматора 85 через селектор 83 записывается на регистр 84. Если в результате сложения возникает пареное,на счетчике 82 приба ляется единица к текущему значению 8/28 р адреса. В командах передачи управления на счетчике команд принимается адрес перехода с выхода селектора 11. . Счетчик 86 преднакачки предназначен для вьфаботки адреса следующего командного слова, накачиваемого в БК относительно счетчика команд, Значение счетчика 86 преднакачки всегда показывает разницу в двойных словах межлу адресом командного слова текущей команды и адресом последнего накаченного в память 41 и 42 командного слова. Если начала требуемой команды нет в БКС, то адрес накачиваемого командного слова равен значению счетчика (8-28р), т.е. значение счетчика 86 равно нулю, и прибавление единицы .не производится. Счетчик 86 увели(чивает свое содерз«симое на единицу всякий раз, когда производится запись очередного командного слова в память 41, 42 командных слов. Из счетчика 86 преднакачки вычитается единица всякий раз, когда при формировании адреса следующей команды возникает перенос в 28р счетчика команд и счетчик команд указьгоает на следующее командное слово. По достижении счетчиком 86 преднакачки максимального значения преднакачки (выход 89 дешифратора 88), которое выбирается меньше максимального количества командных слов, помещаемых в один столбец памяти 41,. 42, дальнейшие по- . пытки преднакачки приостанавливаются до тех пор, пока значение счетчики 86 не уменьшится. Это предотвращав / порчу информации в памяти 41,42 в случае такого количества преднака чек, когда память БКС может переполниться при преднакачках, и последнее принятое командное слово может затереть в БКС строку, в которой находится очередная для выполнения команда. С другой стороны, значение счетчика 86 преднакачки может умейьшиться только до нуля. Для ограничения счета до величина максимал ной преднакачки) и ограйичения вычитания до О предназначен дешифратор 88 этих состояний, который через элементы НЕ 89 закрьгеает соответствующий злемент И 90, с выхо да которых снимаются сигналы прибавления или вычитания. В исходном состоянии и в командах передачи: управления на счетчик 86 преднакачки за:носится О, так как должны накачиваться командные слова новой ветви, с новой точки отсчета. Счетчик 87 предназначен для выработки идентификатора ССП, адреса хранения ССП в локальной памяти. Он является двухразрядным счетчиком инструкции по модулю 4 соответственно четьфем уровням совмещения, и для каждой очередной команды указыввэт очередное место хранения ее С(П в локальной памяти. В исходном состоянии он устанавливается в О. Значение счетчика 87 устанавливается в соотйетствующих разрядах управляющей информации регистра 3 первого уровня одновременно с приемом командной информации. Затем идентификатор ССП передвигается с уровня на уровень вместе со всей информацией данного уровня. Блок локальной памяти (фиг. 6) воспринимает для буферного хранения состояние всех основных регистров пр цессора и информацию оперативной памяти и В1адает исходные операнда в операционные устройства через регистры первого И второго операндов 1длиной 8 байт. Выход регистра второг операнда является основной внутренней загрузочной информационной маристралью процессора, через которую осуществляется вьщача информации в оперативную память, а также загрузка всех оперативных регистров процессора (регистра ССП, регистра префикса, регистров управления, блока таймеров и Т.п.). Для обеспечения возможности одновременного считывания двух исЗсодньгх операндов длиной в 8 байт бло додержит две памяти 91 и 92, об-, ращение к которым независимое. I . Каждая из памятей 91 и 92 разбит на 8 фиксированных зон, по 8 строк длиной в двойное слово в каждой зон Зоны памяти 91 следзтощие: 1- зона хранения слов состояния инструкций (сои), которая занимает 4 строки для случая совмещения четьфех команд остальн строки свободны 2- зона хранения регистров общего назначения (РОН), в каждой стро ке которой хранятся два РОН (че ный и нечетный), каждый длиной по 4 байт; - 3 - зона хранения регистра плавающе точки (РПЛ), в которой заняты 4 строки для хранения РПЛ, ост.аль ные 4 строки свободныJ 4- зона хранения копий управляющих регистров (ЗТ), в каждой строке которой хранятся два УР (четный и нечетный)i , 5- рабочая зона 1 для хранения про межуточных результатов, начальных, конечных, текущих адресов операндов в командах SS-формата 6- рабочая зона 2 для хранения исходных операндов в командах расширенной точности и десятичной арифметики и копии префикса} 7,8-две зоны для хранения идентификатора процессора и констант, используемых в процессе выполнения команд и микроподпрограмм. Зоны памяти 92 могут быть следующими:1- зона хранения исходных ССП текущих команд, которая занимает 4 строки для хранения ССП четьфех команд, выполняющихся совмещенно; 2- зона РОН, которая дублирует идентичную зону памяти 91-, 3- зона,РИЛ, которая дублирует идентичную зону в памяти 91; 4- зона хранения начальных адресов таблиц сегментов нескольких задач. в кякдой строке которой хранится информация управляющих регистров УР(1) и УР(0) для двух задач (код адреса начала таблицы сегментов и размеры таблиц сегментов и страниц). Данная зона заполняется и проверяется при каждом выполнении команды загрузки управления. 5-8-зоны, которые дублируют идентичные зоны памяти 91. Предполагается, что быстродействие локальной памяти таково, что в одном машинном такте (цикле) к возможны два обращения. Обращение к локальной памяти производится под управлением приказов, вырабатываемых в каждой команде в первом полутакте тактов Т1, Т2, ТЗ,, и микрокоманд первого, второго и третьего уровней совмещения в первом или втором полутакте, причем номер полутакта задается в самой микрокоманде. Влок 10 локальной памяти работает следующим образом, В начале выборки каждой команды в первом полутакте такта Т1 производится запись текущего ССП по входу 36 через селектор 94 в память 92 по адресу, равному идентификатору хранения ССП в локальной памяти, принимаемому с выхода 30 блока счет-: чика команд через селектор 100 на регистр 102 адреса. При передвижении кода команды нг следующий уровень совмещения вместе с ней передви гается и код этого идентификатора.. С каждой очередной командой идентификатор ССП на нулевом уровНе увеличивается на 1J счет организован по модулю количества уровней совмеще251

ния, в рассматриваемом случае - по модулю четыре.

Таким, образом, для четырех команд выполняющихся одновременно на четырех уровнях совмещения, обеспечивает ся сохранность в локальной памяти их исходных ССП, причем адрес хранения ССП (идентификатор) в зоне ССП известен и хранится на соответствующем уровне для каждой команды.

В следующем такте Т2, такте модификации адреса, производится в перво полутакте считывание из локальной памяти значений индекса и базы. Адре индекса из зоны РОН, указанный в поле команды первого уровня совмещения, поступает на регистр 101 адреса памяти 91 через селектор 99 по. входу 33, а адрес базы (из зоны РОИ) также указанный в поле команды первого уровня совмещения, поступает на регистр 102 адреса памяти 92 через селектор 100 к входу 33. При этом устанавливается адрес зоны РОН. Считанные значения индекса и ба зы поступают на выходыне регистры

97и 98 через селекторы 95 и 96. Если младший разряд адреса индекса или базы равен 1, что указывает на нечетный РОН, то на селекторах 97 или.

98производится соответствующий-сдви влево на четыре байта, так что индекс и база всегда располагаются в выходных регистрах 97 и 98, выров(Ненные по из левому разряду. Значения индекса и базы поступают по выходным линиям 38 на входы адресного сумматора 16 процессора через селекторы 13 и 14.

В следующем такте трансляции адре са ТЗ производится также в первом полутакте запоминание слова состояния инструкции (ССИ) по входам 31 и 37 через селектор 93 в памяти 9

Адрес запоминания текущего ССИ в зоне ССИ равен адресу хранения ССП в зоне ССП данной команды и берется из поля идентификатора ССП на первом уровне совмещения. Он поступает на регистр 101 адреса памяти 91 чере селектор 99 по входу 33.

Сохранность текущего ССИ в локалной памяти позволяет микропрограмме в любом такте.обратиться к его содержимому по адресу идентификатора на соответствующем уровне. Это необходимо, например, при выполнении команд передачи управления, когда

7726

для возпрата к старой ветви необходимо значение продвинутого счетчика команд, при прерываниях, когда не- o6xoAiiMo запоминать старое ССП, в командах, где используется модифицированный адрес не как адрес операнда, а в качестве операнда (код сдвига, номер канала и абонента и т.н.) в процедурах восстановления по контролю, где используется значение адреса испорченного в оперативной памяти операнда и т.п.

Все указанные действия в тактах Т1, Т2, ТЗ вьтолняются в первом полутакте под управлением приказов, вырабатываемых в каждой команде, независимо от кода команды.

В следующем такте работы прЬцессора, такте Т4, во втором его полутакте ведется считывание исходного первого операнда в командах RX -Лормата, или первого и второго операндов в командах RR -Лормата, под управлением микрокоманды.второго уровня совмещения на регистры 97 и 98.

В зависимости от кода команды считывание из зоны РОН, РГШ или УР в едется по адресам операндов, указанных в соответствующем поле команды второго уровня совмещения. Соотватственно адрес первого операнда поступает на регистр 102 адреса памяти 92 через селектор 100, адрес второго операнда (в командах RR -формата) поступает на регистр 101 адреса памяти 91 через селектор 99. Значения операндов считываются на выходные регистры 97 и 98 через селекторы 95 и 96. Если указаны нечетные номера РОН или УР, то производится при этом соответствующий сдвиг влево на 4 байта. В случаеj если операнды длинные (8 байт), или если указан номер четного РОН или УР, считывание производится без сдвига, т.е. могут быть сосчитаны сразу два РОП (УР) четньй и нечетнь01, находящиеся в одной строке локальной памяти.

В следующем такте Т5 производитя загрузка регистров 107 и 108 передача в операционное устройство ерез регистры 107 и 108 второго и ервого операндов.

Загрузка регистров 107 и 108 ведется под управлением микрокоманды втоого уровня совмещения, причем в случае выполнения команды i{R --формаа первый операнд поступает с выхода

271

регистра 98 через узел. 106 коррекции (фиг. 7) на вхол регистра 108, а второй операнд поступает с выхода регистра 97.через селектор 103, сдвигатель 104 (без сдвига), узел 105 корекции на вход регистра 107, При загрузке регистров 107 и 108 производится анализ конфликта по чтению операнда, модификация которого в предыдущей команде еще не завершена.

Такой анализ производится узлом 116 обнаружения конфликтов (фиг. 6) путем сравнения адресов чтения операндов, запомненных на буферных регистрах 124, с адресом записи результата в предыдущей команде с выхода 35 регистра 7 третьего уровня. При учитывается длина записываемого результата (по линии 118) и четность номера РОН (РПЛ) результата и считанных операндов.

Обнарз/жение конфликта проводится независимо от каждого операнда на двух отдельных схемах. В результате обнаружения конфликта вьфабатывается соответствующий трах1 азрядный код управления узлами 105 и 106 ксфрекции операндов, через которые на неизменяемые части регистров 107 и 108 поступает содержимое cooTBeTCTBjTщих частей регистров 97 и 98, а на из меняемые части регистров 107.и 108 ; поступают соответствующие части результата, выработанного в преды дущей команде.

В случае вьтолнения команды RX; -фор мата второй операнд nociynaer из one ративной (буферной) памяти по входу 20 через селектор 103, сдвигатель 104, узел 105 коррекции на вход регистра 107. При этом на сдвигателе 104 производится сдвиг влево по номе ру байта (три младших разряда адреса операнда), так, что операнд вьфавнйвается по своему левому разряду. Код сдвига вырабатывается сумматором 113 сдвига, не один вход которого поступает номер байта, на второй вход константа сдвига. Константа сдвига указывается в юпсрокоманде и используется при вьшолнении команд загрузки полуслов, символов и при случае необходимого формирования операнда путем сдвига. Сдвиг кольцевой и может быть задан от О до 7 байт. Этот же сдвигатель 104 испол зуется и при чтении операнда из ло28

кальных памятей или приеме через селетор ЮЗ любой другой информации в командах записи в оперативную (буферную) память. В этом случае код сдвига также вырабатывается на сумматоре 113, но номер байта при этом вычитается, т.е. сдвиг осуществляв ется по.номеру байта вправо. Прием на регистр 107 информации осуществляется по маркеру, поступающему через селектор 114. Маркер восьмиразрядный, и единица в разряде маркера разрешает изменение соответствующего байта регистра 107, а ноль сохраняет прежним значение данного байта.

Маркер приема на регистр 107 либо явно указьшается в микрокоманде (вход 1 селектора 114), либо считывается из памяти констант маркера (вход 40 селектора 114), обращение к которой ведется по адресу, составленному из трехразрядного кода номера байта и трехразрядного кода длины операнда, указанного в микрокоманде.

Сочетание работы сдвигателя 104 и маркера дает возможность формировать операнды из частей различных источников, а также формировать операнд в случае нецелочисленной его границы, т.е. когда он расположен в двух смежных ячейках оперативной (буферной) памяти.

На третьем уровне совмещения, в такте Т6, ведется прием содержимого регистра 107 второго операнда через селектор 111 на буферный регистр 112 результата в командах загрузки РОН, РПЛ, УР. Кроме того, в этом такте ведется прием содержимого изменяемого операнда (первого или второго) на регистр 115 восстановления операнда. Выход регистра 115 поступает на вход селектора 103, и в процедурах восстановления операнда по контролю его содержимое может восстановить испорченный операнд РОН ил РПЛ в локальной памяти.

В последнем такте вьтолнения команды, такте Т7 записи результата, результат операционного устройства, принятый через селектор 111 на буферный регистр 112, поступает через селекторы 93 и 94 на информационные входы памятей 91 и 92 и записывается в соответствующую зону (РОН или ПЛ) по адресу первого операндов, указанному в поле команды третьего уров ня (вход 35). Запись производится по управлением микрокоманды третьего уровня во BTopQM полутакте.. Запись в обе памяти ведется по маркеру записи в локальную память, заданному в микрокоманде третьего уровня, причем информация сдвигается на селе торах 93 и 94 вправо на 4 байта, есл результат пишется в нечетный РОН. При выполнении команд 65 -Лормата необходимо некоторые промежуточнме результаты сдвигать на 1 или нескол ко байт. Эти действия осуществляются под управлением микрокоманд, в которых задается чтение промежуточного результата из рабочей зоны, по адресу, явно указанному в микрокоманде, на регистр 97 в первом полутакте, сдвиг его на сдвигат ле 104 на необходимое число байт и запись снова в рабочую зону по то му же или другому адресу в памяти 91 и 92 во втором полутакте одного и того же машинного цикла. Введение раздельных селекторов 9 и 94 для памятей 9t и 92 дает возможность использовать более оптимал но весь объем памяти за счет нёдубл рованных зон для хранения ССП, ССИ, начальных адресов таблиц сегментов. Таким образом, возможность применения локальной памяти в процессоре большой производительности с п уровнями совмещения достигнута путем построения управления и селекции ад ресов от п() различных уровней совмещения с разделением времени обращения к локальной памяти в р ных полутактах для микрокоманд, вьпюлняницихся одновременно. По числу совмещения, выполняемых микропрограммно, память 134 констант, регистр 136 адресов микрокоманд,- память 137 микропрогра и регистр 138 микрокоманд в блоке 8 микропрограммного управления (фиг. 8) разделены на секции. В случае предлагаемого устройства центрального управления процессора таких секций 3. По входам 33 - 35 с регистров 3, 5 и 7 командной информации первого, второго и третьего уровней поступаю коды операций выполняемых команд. На шифраторе 133 адреса первой микрокоманды при условии наличия команды в ВКС (вход 27) по коду операции команды на первом уровне вырабатывается адресная константа первой микрокоманды. (Если требуемой для выполнения команды в буфер е БКС не. обнаружено, то на тсфраторе 133 вьфабатывается адресная константа первой микрокоманды процедуры накачки командного слова). Адресная константа первой микрокоманды поступает в коммутатор 1.35 адресов микрокоманд, затем в регистр 136 адресов микрокоманд. По. этому адресу происходит выборка первой микрокоманды из памяти 137 микропрограмм. Первая микрокоманда помещается на регистр 138 микрокоманд. Адрес следующей микрокоманды -вырабатывается в коммутаторе 135 адреса, номера секции 137 памя ти микропрограмм, условий ветвления, содержащихся в слове микрокоманды и оценивающих соответствующие признаки ветвления на выходе 27 адресных констант, поступающих в коммутатор 135 айресов микрокоманд и памяти 134 констант. Признаки ветвления на выхо де 27 вырабатываются в блоках процес сора при выполнении нми микрокоманд и- могут влиять на выработку адреса следующей микрокоманды, если это указано в микрокоманде. Кроме обработки команд блок 8 микропрограммного управления обрабатывает пультовые, таймерные операции, прерывания и процедзфы восстановления по контролю. Запросы на обработку этих процедур поступают по входу 29.1.в схему 132 приоритета. Адресные константы процедур, задающие фиксированные адреса первых микрокоманд микропрограмм обработки этих процедур, поступают по вхог дал 140 в коммутатор 135 адресов микрокоманд. Далее обработка процедур ведется так же, как и выполнение команд. В памяти 134 констант хранятся не только адресные константы, но и другие данные, необходимые при выполнении команд (например, признак привилегированности вьшолняемых команд, длины операндов и т.д.). Константы и микроприказы поступают В устройство центрального управления процессора по выходам 22. Двухсекционная память 152, 153 буфер быстрой переадресации (БПЛ) блока трансляции адреса (фиг. 9) служит для хранения и оперативного

3111361

использования строк таблицы страниц, наиболее часто используемых. Буфер 152, 153 быстрой переадресации организован как память по типу КЭШ (саа/р). Используется адресно-ассоциа 5 тивный способ поиска информации в буфере быстрой переадресации. Обраение ведется сразу к обоим столбцам 152, 153 по младшим 6 разрядам (15/20) анализируемого логического Ю адреса страницы, поступающим из регистра 146 логического адреса. Значение поля старших разрядов логичесого адреса (8/14) регистра 146 логиеского адреса сравнивается на второй 15 четвертой схемах 154 сравнения со зна 1ением считанного из обоих столбцов 152, 153 поля логического ащреса. Если обнаруживается равенство значений этих полей в одном из 20 столбцов, то это означает, что требуемая строка таблицы страниц имеется в буфере быстрой переадресации и записана в поле реального адреса того столбца, где обнарзгжено это 25 равенство.

В буфере 152, 153 быстрой переадресации foryт храниться строки аблиц от многих задач одновременно, ак как для каждой задачи может быть зо адана своя таблица переадресации и вои параметры размеры страниц и сегентов) . С этой целью в памятях 152 и 153 имеется поле хранения идентификатора таблицы сегментов. На . регистре 151 активного номера таблицы сегментов запоминается идентификатор той таблицы сегментов, которая активна в- данньй момент.

Всякий раз при обращении к бу- Q феру быстрой переадресации одновременно с логическим адресом считывается и поле идентификатора сегмента, значение которого сравнивается Ни первой и третьей схемах 154 j сравнения со значением регистра 151 активного номера таблицы.сегментов. Равенство логических адресов, выявляе мое на второй и четвертой схемах 154 сравнения, учитывается лить при сов- JQ падении поля идентификатора сегмента и активного номера таблицы сегментов .

Активный номер таблицы сегментов в регистре 151 устанавливается каж- 55 дый раз при вьтолнении комащда загру ки управляющего регистра 145, хра нящего адрес начала таблицы сегмен32

77

тов, размеры страницы и сегмента. Содержание этого управляющего регистра 145 сохраняется в специальной зоне 4 блока 10 локальной памяти по адресу, который и является его идеитификатором.

Если при обращении к буферу 152, 153 не обнаруживается нужной строки таблицы страниц, то происходит по признаку ветвления на вьосоде .27, формируемому на элементе И 155, обращение за нужными строками таблиц сегментов и страниц в оперативную память и накачка буфера переадресации.

Процедура накачки буфера переадресации состоит в следующем.

Вычисляется на адресном сумматоре 16 адрес входа в таблицу сегментов. На первое слагаемое через селектор 13 постзшает по входу 38 значение адреса начала таблиц сегментов, сосчитанное из зоны управляющих регистров блока 10 локальной Памяти, на второе слагаемое поступает ноль и на третье- слагаемое через селектор 15 поступает с выхода селектора .

149значение индекса сегмента. Вычисленный реальный адрес строки

таблицы сегментов по входу 37 поступает через селектор 147 на регистр

150реального адреса и после префиксции на схеме 148 через элементы И 15 Ifflli 157 поступает в блок 19 выработки запросного слова в УП.

Содержимое строки таблицы сегментов является реальным адресом начала таблицы страниц . Для формирования адреса входа в таблицу страниц на первое слагаемое поступает ноль, на второе слагаемое через селектор 14 по входу 24 - содержимое регистра второго операнда, на третье слагаемое через селектор 15 - индекс страницы с выхода селектора 149. Выдача адреса таблицы страниц в блок 19 запроса в устройство управления памятью проводится аналогично адресу таблицы сегментов. I

Требуемая строка таблицы страниц

из регистра 107 операнда два по входу 24 поступает на селектор 147, а затем на регистр 150 реального адреса.

Разряды реального ал,реса (8/19) подверга.отся префиксации на схеме 148 префиксации, а зятем помещаются в нужну строку и секцию буфера 152 33 и 153 быстрой переадресации одновременно с разрядами 8-14 логичес кого адреса с выхода регистра 146 в поле логического адреса и одновременно со значением регистра 151 ак-тивного номера сегментов в поле н мера сегмента. Выбор столбца для занесения информации в процедуре накачки буфера переадресации ведется аналогично выбору столбца при замещении в буфере командных слов. В памяти 158 замещения в такте Т2 трансляции адреса запоминаются номе ра столбцов, в которых обнаружено сравнение адресов, В процедуре накачки инверсия содержимого этой памяти определяет номер столбца, в который необходимо вести запись i информации. На регистр 167 запросного слова ,в блоке 18 связи t операционным .устройством (фиг. 14) в такте Т5 заносится код операции по входу 34 с регистра 5 команд второго уровня, код сдвига (младшие шесть разря дов модифицированного адреса с регистра 150) с выхода 39 блока 17) маска программы с регистра 166 маски программы. Кроме того, на регист 167 может быть занесен код типа СУ (позиционно) по коду микрокоманды, если pacc faтpивaёмoe устройство используется в мультипроцессорной си теме с несколькими типами ОУ, являющимися общими ресурсами для нескольких процессоров, В последнем случае информация результата каждо типа ОУ поступает в процессор на вх 21 через селектор (не показан на фиг,1) под управлением блока 18. В блоке связи с устройством управления памятью (фиг. 15) запросное слово формируется на регистре 173, По входу 39 поступает абсолютный адрес, а.также значения 20 разр да логического адреса и размер стра ницы для формирования номера УУП. Если рассматриваемое устройство используется в мультипроцесорной си теме с несколькими УУП, то информация из каждого ЗТП, выдаваемая по запросу от процессора, должна поступать на вход 20 через селектор (не показан на фиг. 1) под управлением блока 19. После маркеров по входу 37 из сумматора 16 адреса поступают три младших разряда логического адреса (номер байта передаваемой информации), по входу 22 поступают микроприказы и константа, задающая длину операнда, записываемого в память. Считанное из Памяти 168 маркеров поле маркеров записьшается в регистр 173 запросного слова в устройство управления памятыо. В регистре 169 хранится ключ защиты слова состояния программы. Под управлением микроприказов 22 этот ключ запоминается на регистре 173 запросного слова в устройство управления памятью. Из микроприказов 22 формируется код операции устройства управления памятью, который записывается на регистр 173. В запросное слово в устройство . утфавлеиия памятью входит и номер устройства управления памятью, так как предлагаемое устройство центрального управления процессора может быть использовано в составе мультипроцессора. Номер . устройства управления па. мятью вырабатывается иа элементах 170 - 172 на основании разряда (20) логического адреса, разряда (20) абсолютного ащэеса, размера страницы, поступающих по входу 39 из блока трансляции адреса и никроприказов, управляющих выработкой номера устройства управления памятью.Сформированный нсмер устройства управления памятью записывается на регистр 173. Сформированное запросное слово выдается в устройство з правления памяти по выходу 26. Кроме того, в блок 10 локальной памяти по выходу 40 передается маркер управления приемом второго операнда на регистр 107, а в блок 8 микропрограммного управления выдается по выходу 27 признак ветвления в случае нецелочисленной гранихрл операнда (т.е. когда операнд расположен в двух смежных ячейках оперативной памяти). Предложенное изобретение обеспечивает существенное преимущество в быстродействии по сравнению с известным за счет использования трехнходового сумматора 16 адреса для модифика ции адреса, позволяющего все модификации производить не за два такта, как в известном устройстве, а за один, наличия буфера 1 командных слов большой емкости (128 г войных слов), что позволяет хранить в буфере командных слов несколько программных

351136

циклов, а такке за счет наличия селектора 9, позволяющего быстро формировать адрес команды передачи управления для поиска этой команды в блоке Ь

В известном устройстве в случае

успешного перехода тратится восемь тактов, а в случае неуспешного пере хода пять,

Повьшение быстродействия процессо- 10 ра достигнуто также благодаря введению в устройство схемы коррекции one рандов в случае определения конфликта по операнду из-за совмещения операций. Сохранение в локальной памяти ts КОПИИИСХОДНЫХ операндов, ССП, префик. са и управляющих регистро з позволяет вьтолнять повторение команд, в к:оторых произошла ошибка. Кроме того.

36

77

путем введения банка внутренних данных локальной памяти упорядочивается структура процессора, увеличиваются его функциональные возможности по вьтолнению различных тестов и диагностических процедур, сокращается регистровое оборудование на построение ряда управляющих и рабочих регистров. Введение недублированных зон локальной памяти повышает оптимальность использования памяти, что также уменьшает оборудование на построение соответствующих буферных регистров (таблицы начал адресов сегментов, значения модифицированных адресов операндов и счетчика команд).

Суммарный выигрыш в быстродействии составляет 31,Д%.

i6 II

&

п Tl

с

,f

59

E

60

28

6#

Д

f f

n

Фиг.2а 4 gf I jg

Фиг2$

IL

Ф

77

; 1 r

Сл

7Г

7

- 7

I Ж

ггф

Й

/(

/(5J

г.«

да

2J

П

29

33 34 J5

g

I

«SI

g

iS

A k

MM

W 22

Запросное c/wfe i

UI

Zt 35

I Фиг.Щ

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| МАШИНА ДЛЯ ПРЯДЕНИЯ ИСКУССТВЕННОГО ШЕЛКА | 1925 |

|

SU3033A1 |

| look | |||

| Datamation, May, 1979, p.198218 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Веникодробильный станок | 1921 |

|

SU53A1 |

| Регулятор для вертикальных ветряных двигателей | 1925 |

|

SU2060A1 |

| Техническое описание | |||

| Приспособление для изготовления в грунте бетонных свай с употреблением обсадных труб | 1915 |

|

SU1981A1 |

Авторы

Даты

1985-01-23—Публикация

1983-06-01—Подача